2概述

3系统接口信号

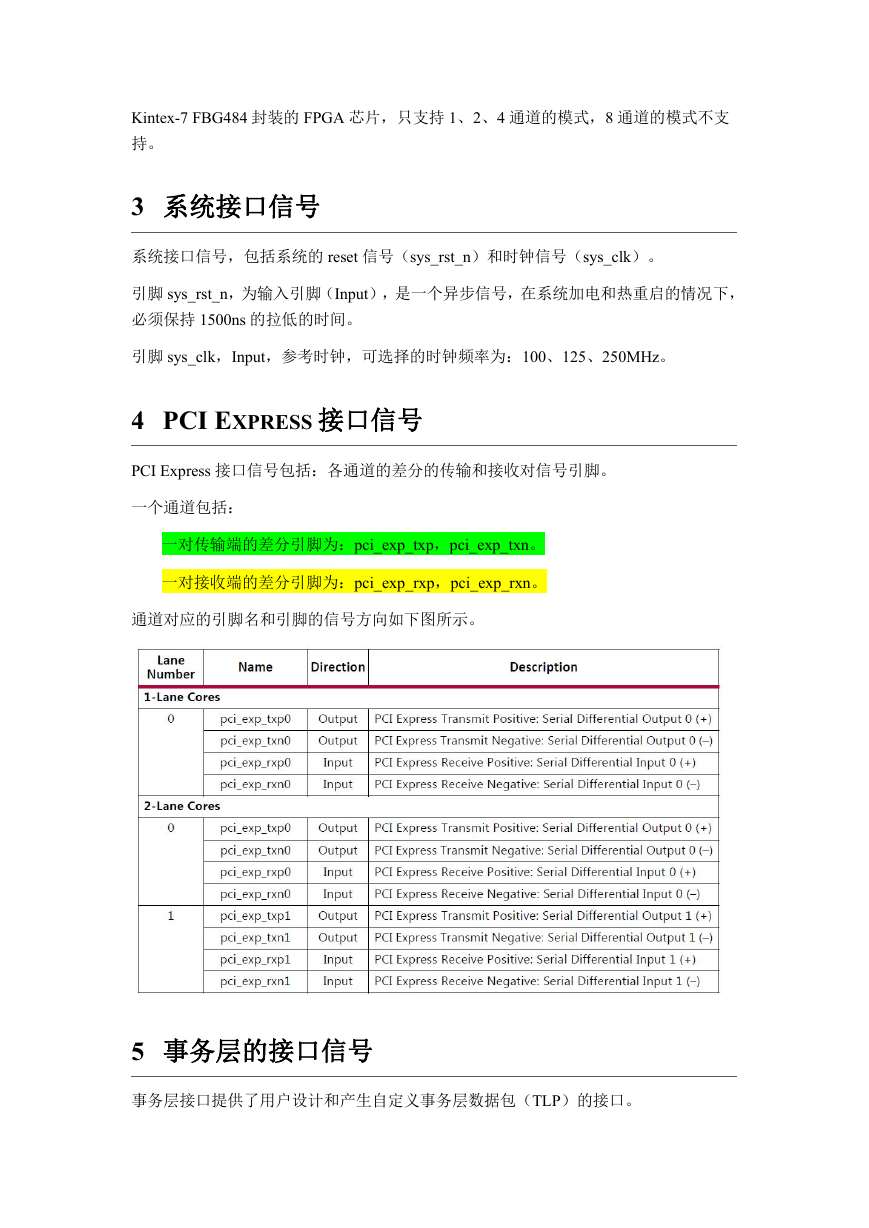

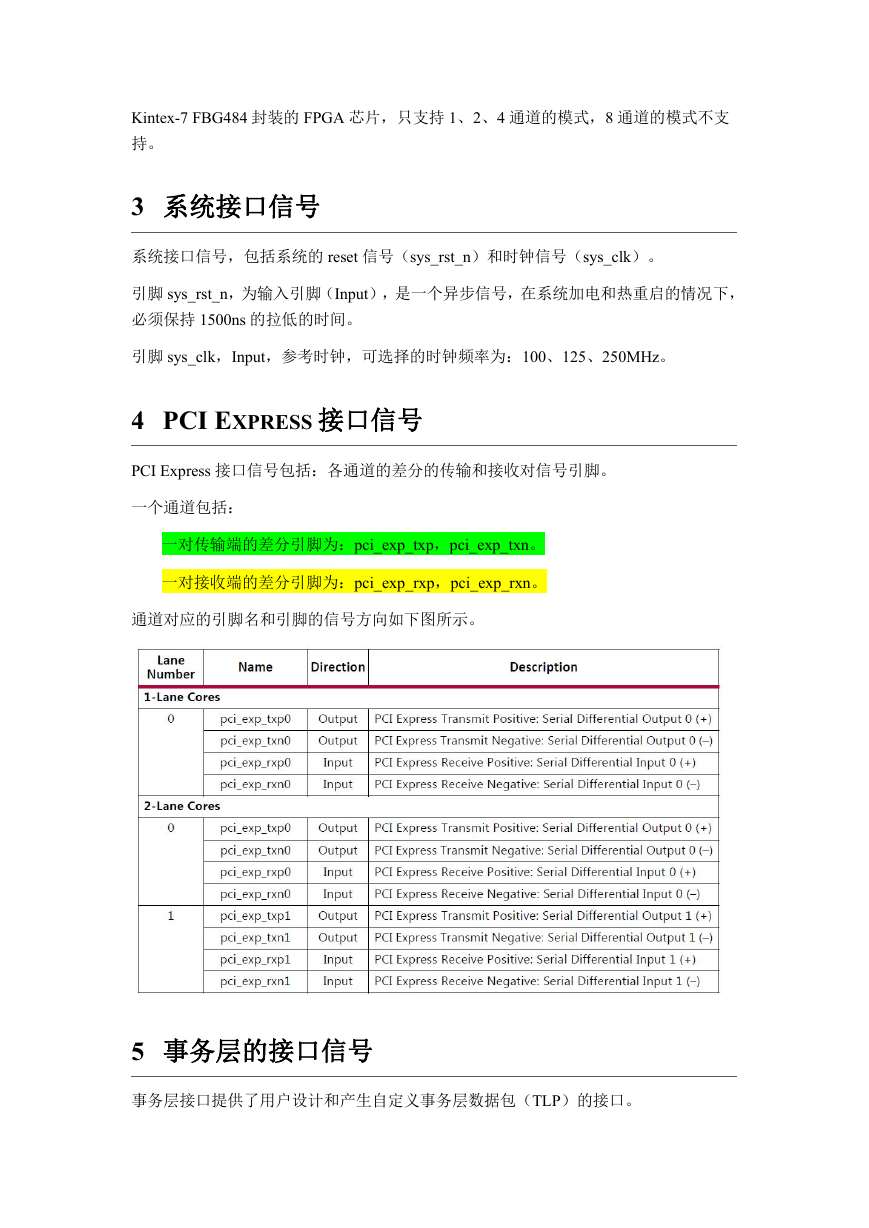

4PCI EXPRESS接口信号

5事务层的接口信号

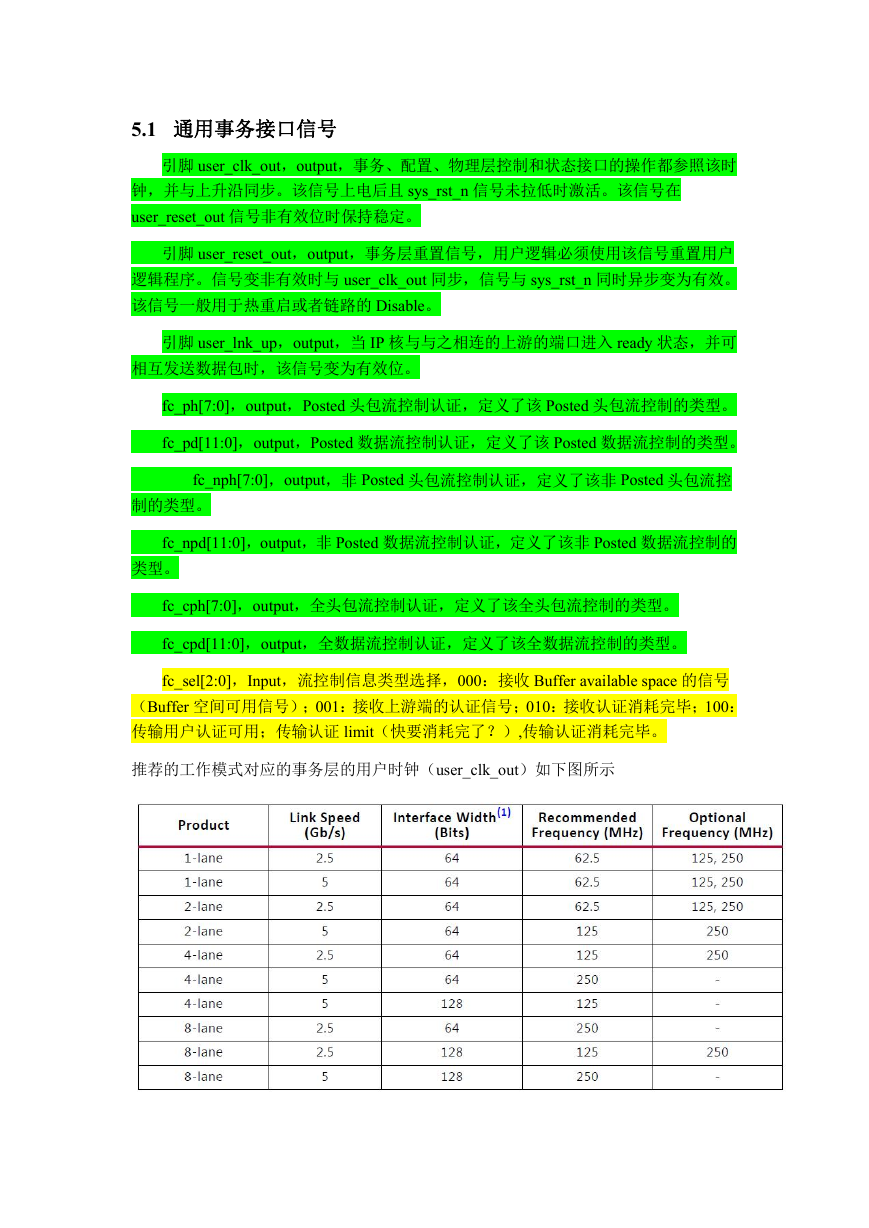

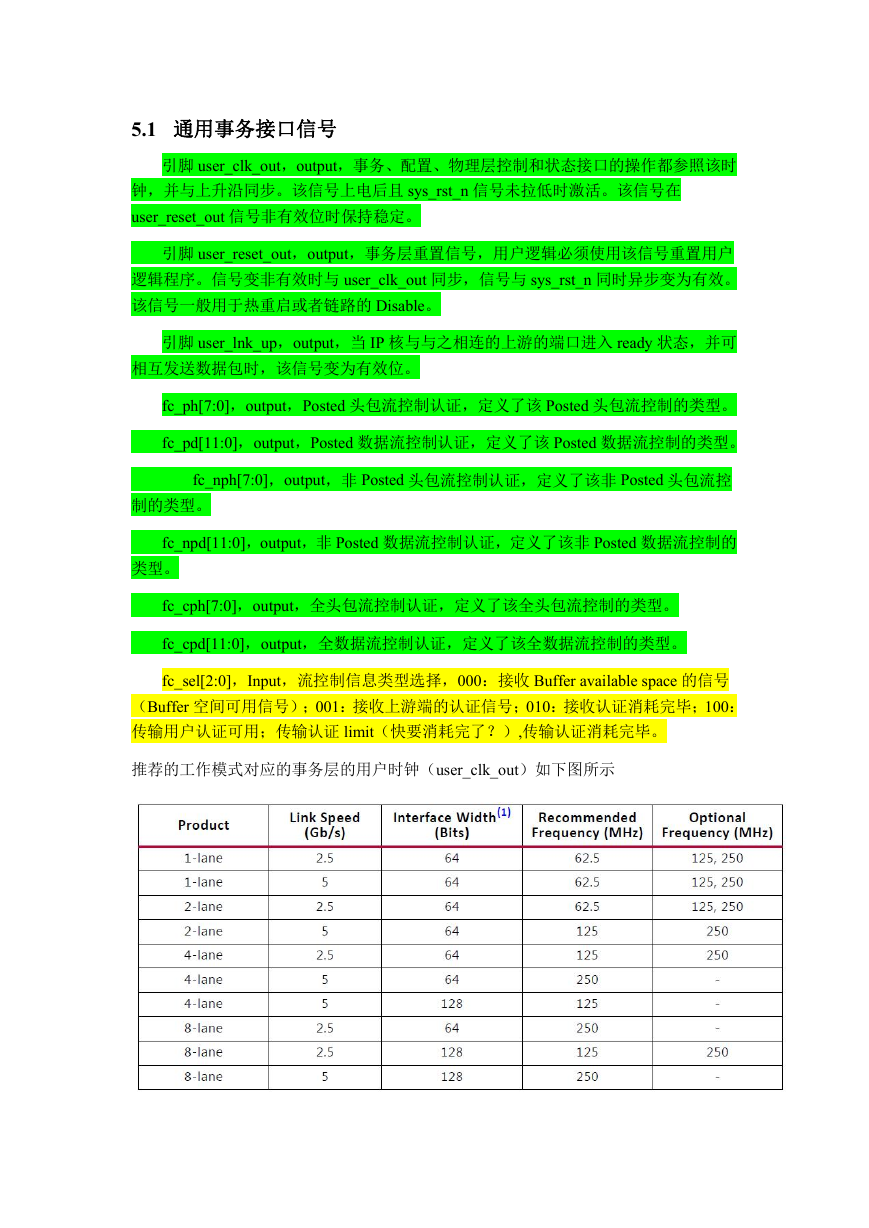

5.1通用事务接口信号

5.2传输接口信号

5.3接收接口信号

5.4物理层接口

5.5配置接口

5.6中断接口信号

5.7错误报告接口

5.8动态配置接口

5.9内部接口

6PCI配置空间

7IP核的设计

7.1总体设计概要

7.1.164Bit事务层接口设计

7.1.1.1基本的TLP包的发送操作

7.1.1.2传输接口流模式下的事务

7.1.1.3使用ECRC机制

7.1.1.4接收流入的包(In-Bound Packets)

7.1.1.5接收接口中包的重排序

7.1.1.6接收包数据损坏(Poisoning)和TLP摘要(Digest)(64Bit AXI-Stream)

7.1.1.7接收包基地址寄存器的识别和处理

7.1.1.8AXI4-Stream接收接口对包传输链路断开的处理

7.1.2128Bit事务层接口设计

7.1.2.1AXI4-Stream接口的TLP包的格式

7.1.2.2发送包(Transmitting Outbound Packets)

7.1.2.3发送接口的Back-To-Back传输模式

7.1.2.4发送数据通道的源限流(Source Throttling)

7.1.2.5发送数据通道的目标限流(Destination Throttling)

7.1.2.6用户暂停TLP事务包的传输

7.1.2.7AXI4-Stream接口的发送端包损坏

7.1.2.8发送端的流模式传输

7.1.2.9发送端启用ECRC(128-Bit接口)

7.1.2.10接收流入的包(In-Bound Packets)

7.1.2.11读TLP包中的SOF和EOF信号

7.1.2.12对AXI4-Stream接口接收到跨开包(Straddled Packet)的处理

7.1.2.13AXI4-Stream接口接收包顺序的重排

7.1.2.14128Bit AXI4-Stream接口接收包的损坏(Poisoning)和TLP摘要(Digest

7.1.2.15接收包的请求访问的基地址寄存器的检测

7.1.2.16AXI4-Stream接口包的不连续传输

7.1.3IP核对事务的处理策略

7.1.4原子操作(Atomic Operations)

7.1.5IP核的Buffer和流控制

7.1.5.1Maximum Payload Size

7.1.5.2Transmit Buffers

7.1.5.3接收流控制的授权机制

7.1.5.4接收端流控制信息

7.1.5.5发送端的流控制信息

7.1.6物理层的控制和状态接口的设计指导

7.1.7配置空间寄存器和配置接口的设置指导

7.1.7.1Device Control and Status寄存器定义

7.1.7.2IP核对命令寄存器设置的响应

7.1.7.3状态寄存器对错误情况的响应

7.1.7.4通过配置接口访问寄存器

7.1.7.5选配的PCI Express扩展功能

7.1.7.6Xilinx定义的供应商特有的功能

7.1.7.7高级的错误报告功能

7.1.7.8可变大小的BAR功能

7.1.7.9用户实现配置空间

7.1.8额外的包处理的要求

7.1.9消息TLPs的处理

7.1.9.1配置Root Port

7.1.10用户错误报告

7.1.10.1错误类型

7.1.10.2Completion(Cpl)超时

7.1.10.3Unexpected Completion包

7.1.10.4完成终止

7.1.10.5不支持的请求

7.1.10.6ECRC错误

7.1.10.7AER要求

7.1.10.8可变尺寸的BAR专用信号(只用于终端模式)

7.1.11错误检测

7.2电源管理

7.2.1活跃状态的电源管理模式(ASPM)

7.2.2可编程的电源管理模式(PPM)

7.2.2.1PPM L0状态

7.2.2.2PPM L1状态

7.2.2.3PPM L3状态

7.3中断请求的产生

7.3.1用户应用对PCI兼容中断模式的处理

7.3.2用户应用对MSI中断模式的处理

7.3.3MSI-X模式

7.42通道、4通道和8通道链路的建立

7.4.1链路远端设备支持的通道数少于本地设备

7.4.2通道存在故障的情况

7.4.3通道逆转

7.5动态重配置接口的使用

7.5.1读写DRP接口

7.5.2DRP接口其它需要注意的事项

7.5.3DRP地址映射

7.6TANDEM配置(搭配配置)

7.6.1支持的设备

7.6.2Tandem工具的工作流程

7.6.3Tandem PROM

7.6.4Tandem PCIe

7.6.5在用户自定义的硬件上使用Tandem

7.6.5.1使用PCIe Example来进行用户设计

7.6.5.2将PCIe Example移植到新的Vivado工程中

7.6.6Tandem配置的RTL设计

7.6.6.1关键的多路复用输入

7.6.6.2Tandem的完成机制

7.6.6.3Tandem的配置逻辑

7.6.6.4用户应用的握手协议

7.6.7Tandem配置细节

7.6.7.1I/O行为

7.6.7.2配置引脚行为

7.6.7.3配置的持续效应(只适用于Tandem PROM模式)

7.6.7.4PROM的选择

7.6.7.5Programming设备

7.6.8Tandem资源限制

7.6.9移动PCIe的复位引脚

7.6.10仿真Tandem IP核

7.6.11计算Tandem bitstream的加载时间

7.6.11.1当没有ATX供电的情况

7.6.11.2有ATX供电的情况

7.6.12Bitstream的大小

7.7时钟

7.7.1同步和非同步的时钟

7.8RESETS

7.9协议层

7.9.1事务层

7.9.2数据链路层

7.9.3物理层

7.9.4配置管理

7.10共享逻辑

7.10.1共享时钟

7.10.2共享GT_COMMON

7.10.3共享GT_COMMON和时钟

7.10.4内部的共享GT_COMMON和时钟

7.10.5时钟接口

7.11FPGA的配置

7.11.1配置术语

7.11.2配置访问时序

7.11.2.1配置访问的规范要求

7.11.2.2实际的板级供电

7.11.2.3热插拔系统

7.11.3推荐配置

7.11.47系列FPGA的配置时序

7.11.5示例分析

7.11.5.1不能识别FPGA的示例

7.11.5.2成功识别FPGA的示例

8设计流程

8.1配置和生成IP核

8.1.1Base模式

8.1.1.1Base

8.1.1.2Identifiers (IDs)

8.1.1.3Base Address Registers (BARs)

8.1.1.4Core Capabilities

8.1.1.5Interrupt

8.1.2Advanced模式

8.1.2.1Basic

8.1.2.2Identifiers (IDs)

8.1.2.3Base Address Registers (BARs)

8.1.2.4Core Capabilities

8.1.2.5Link Registers

8.1.2.6Configuration Register (Only in Root Port Configur

8.1.2.7Interrupts

8.1.2.8Power Management

8.1.2.9Extended Capabilities

8.1.2.10Extended Capabilities 2

8.1.2.11TL Settings

8.1.2.12DL and PL Settings

8.1.2.13Shared Logic

8.1.2.14Core Interface Parameters

8.1.2.15Add. Debug Options

8.1.3生成IP核

8.1.3.1终端模式

8.1.3.2RootPort模式

8.2约束IP核

8.2.1设备,封装和速度级别选择

8.2.1.1用户的时序约束

8.2.1.2用户的物理约束

8.2.1.3IP核的引脚和I/O约束

8.2.1.4IP核的物理约束

8.2.1.5IP核时序约束

8.2.1.6器件选择

8.2.2IP核I/O引脚分配

8.2.3IP核物理约束

8.2.4IP核时序约束

8.2.5重新部署IP核

8.2.6可用的PCIe资源

8.2.7推荐的GT的位置

8.2.7.1Zynq-7000 器件

8.2.7.2Virtex-7 器件

8.2.7.3Kintex-7器件

8.2.7.4Artix-7器件

8.3仿真

8.3.1PIPE Mode Simulation

8.3.2后期综合(Post-Synthesis)网表的功能仿真

9EXAMPLE设计

9.1终端模式的配置概述

9.1.1仿真设计概述

9.1.2设计实现概述

9.1.3Example设计的组成部分

9.2PIO EXAMPLE设计

9.2.1系统概述

9.2.2PIO硬件

9.2.3基地址寄存器的支持

9.2.3.1更改默认的BAR设置

9.2.3.2TLP数据流

9.2.3.3写存储和I/O的TLP包的处理

9.2.3.4读存储和I/O的TLP包的处理

9.2.3.5PIO文件结构

9.2.4PIO应用

9.2.4.1接收路径

9.2.4.2输出路径

9.2.4.3终端存储

9.2.5PIO的操作

9.2.5.1PIO读事务

9.2.5.2PIO写事务

9.2.5.3小结

9.3配置程序的EXAMPLE设计

9.3.1系统概述

9.3.2配置程序Example的硬件设计

9.3.3配置器模块

9.3.4配置器ROM

9.3.5PIO Master(PIO主设备)

9.3.6配置器的文件结构

9.3.7小结

9.4生成IP核

9.5仿真EXAMPLE设计

9.5.1.1终端配置

9.6综合和实现EXAMPLE设计

9.7文件夹和文件的内容

9.7.1终端方案

9.7.2Root Port方案

10TEST BENCH

10.1终端模式IP核的基于ROOT PORT模型的TEST BENCH

10.1.1框架结构

10.1.2可缩放的仿真超时

10.1.3测试选择

10.1.4输出日志

10.1.5并行测试程序

10.1.6测试描述

10.1.7展开Root Port模式

10.1.7.1Root Port模型的 TPI任务列表

10.2ROOT PORT使用的终端模式TEST BENCH

10.2.1结构

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc