Altium Designer

PCB 画板速成教材

软件版本:Altium Designer Summer 09

时 间:2012 年 10 月 22 日

Q Q:1598962879 QQ 群:88107403(技术交流)

E-mail: zheng.zy@foxmail.com

Designer:Zhengzy

第 1 页 共 102 页 By Zhengzy

�

目 录

第一章 原理图的编译与检查„„„„„„„„„„„„„„„„„„„„„„3

1.1、首先应对软件进行相关检查项设置„„„„„„„„„„„„„„„„3

1.2、原理图编译„„„„„„„„„„„„„„„„„„„„„„„„„„4

1.3、检查元件封装是否完整„„„„„„„„„„„„„„„„„„„„„4

1.4、生成网表,导入 PCB„„„„„„„„„„„„„„„„„„„„„„5

第二章 PCB 设计前期处理„„„„„„„„„„„„„„„„„„„„„„„9

2.1、软件通用参数设置„„„„„„„„„„„„„„„„„„„„„„„9

2.2、定义板框„„„„„„„„„„„„„„„„„„„„„„„„„„„12

2.3、叠层的定义„„„„„„„„„„„„„„„„„„„„„„„„„„16

第三章 PCB 布局布线常用命令及快捷键„„„„„„„„„„„„„„„„„17

3.1、布局布线的快捷键认识及创建„„„„„„„„„„„„„„„„„„17

3.2、交互式布局„„„„„„„„„„„„„„„„„„„„„„„„„„23

3.3、模块化布局„„„„„„„„„„„„„„„„„„„„„„„„„„24

第四章 Class、规则的设置及走线优化„„„„„„„„„„„„„„„„„25

4.1、Class 的设置„„„„„„„„„„„„„„„„„„„„„„„„„25

4.2、网络及 class 的颜色管理„„„„„„„„„„„„„„„„„„„„27

4.3、设计规则设置„„„„„„„„„„„„„„„„„„„„„„„„„28

4.4、Room 规则的设置„„„„„„„„„„„„„„„„„„„„„„„„39

4.5、敷铜处理„„„„„„„„„„„„„„„„„„„„„„„„„„„41

4.6、内层分割„„„„„„„„„„„„„„„„„„„„„„„„„„„45

4.7、差分线的设置„„„„„„„„„„„„„„„„„„„„„„„„„46

4.8、等长走线及绕线„„„„„„„„„„„„„„„„„„„„„„„„52

4.9、全局操作的方法„„„„„„„„„„„„„„„„„„„„„„„„57

第五章 PCB 后期处理„„„„„„„„„„„„„„„„„„„„„„„„„59

5.1、丝印调整„„„„„„„„„„„„„„„„„„„„„„„„„„„59

5.2、装配图的打印„„„„„„„„„„„„„„„„„„„„„„„„„62

5.3、尺寸标注„„„„„„„„„„„„„„„„„„„„„„„„„„„68

5.4、DRC 检查„„„„„„„„„„„„„„„„„„„„„„„„„„„70

第六章 生产文件输出„„„„„„„„„„„„„„„„„„„„„„„„„73

附录一 插件的安装方法„„„„„„„„„„„„„„„„„„„„„„„„80

附录二 相同模块布局布线的方法(简称:Copy Room)„„„„„„„„„„„82

附录三 PCB 文件中如何添加 LOGO„„„„„„„„„„„„„„„„„„„„86

附录四 敷铜时如何去掉死铜的方法„„„„„„„„„„„„„„„„„„„90

附录五 检查线间距时差分间距报错的处理方法„„„„„„„„„„„„„„92

附录六 如何创建 3D 模型及设计„„„„„„„„„„„„„„„„„„„„93

第 2 页 共 102 页 By Zhengzy

�

此文主要是针对 Altium designe PCB 设计的一个软件操作介绍,让你快速

掌握此软件的各项基本操作进行 PCB 设计。关于大家关心的 PCB 设计知识由于教

程工作量比较大,在后期分期推出。

第一章 原理图的编译与检查

我们一般拿到原理图之后都应对其进行编译检查,比如检查是否有相同位

号,是否有单端网路等等,具体如何做呢?

1.1、 首先应对软件进行相关检查项设置

点击菜单栏 Project——Project Option,之后弹出如下对话框,这时,

我们可在“Report Mode”栏中选择检查项和报错类型。设置的报告类型,我们

一般选择严重错误类型。

单端网络报告选项及接触不良报告选项如下图:

第 3 页 共 102 页 By Zhengzy

�

1.2、 原理图编译

报告选项设置之后,我们就可以对原理图进行编译了。同样点击 Project

——compile PCB project„,当然只编译当前原理图页的话,可以选择 Project

——compile document„。

编译之后可以点击右下角 system——messages 查看报告信息,如果有可

以双击报告项即可查看错误的位置。

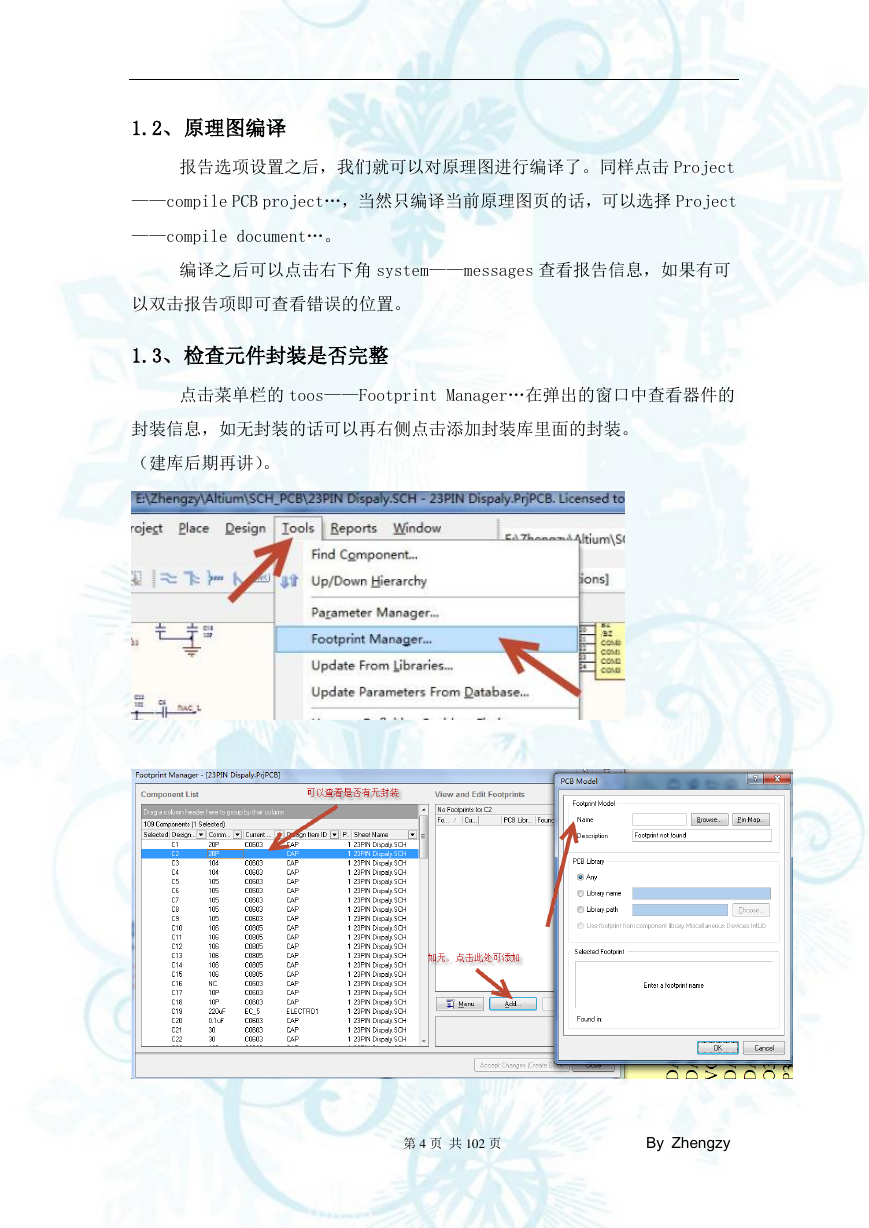

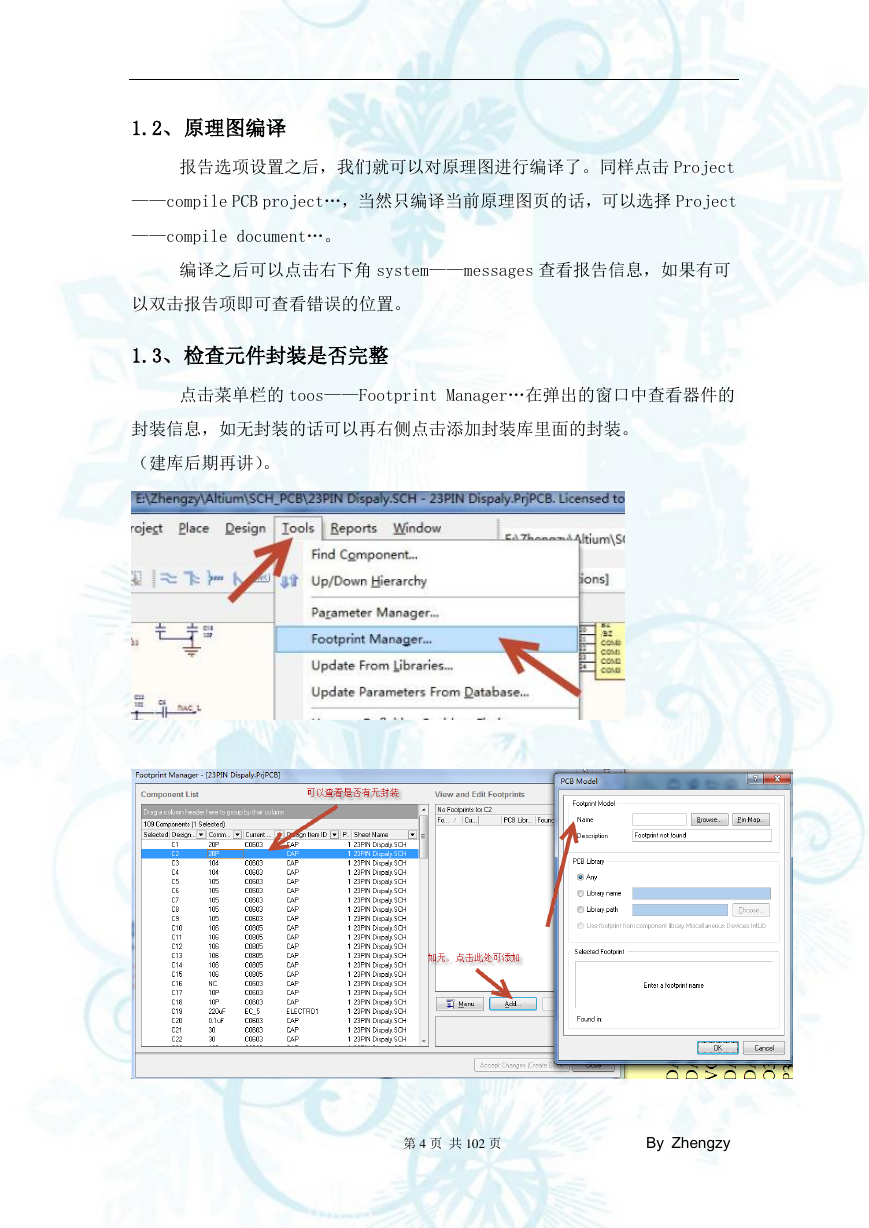

1.3、 检查元件封装是否完整

点击菜单栏的 toos——Footprint Manager„在弹出的窗口中查看器件的

封装信息,如无封装的话可以再右侧点击添加封装库里面的封装。

(建库后期再讲)。

第 4 页 共 102 页 By Zhengzy

�

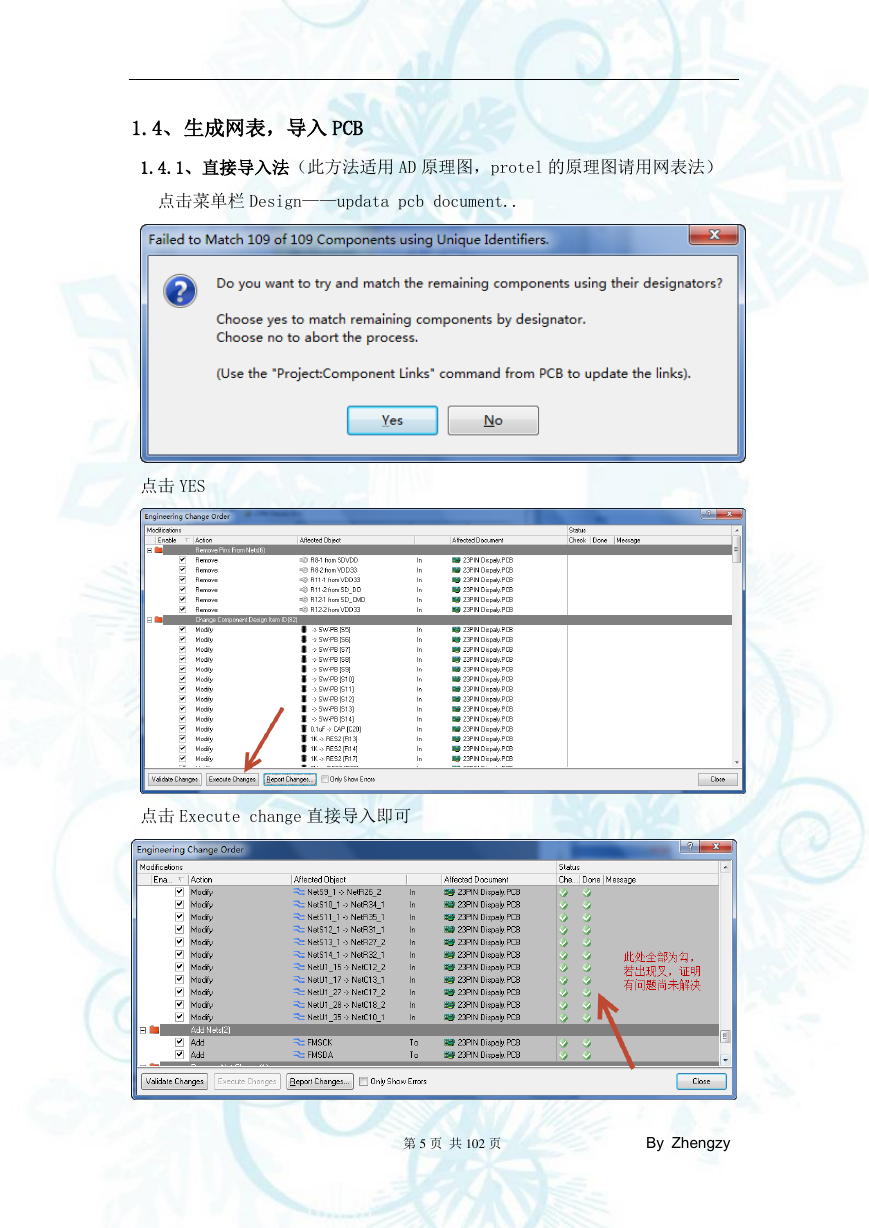

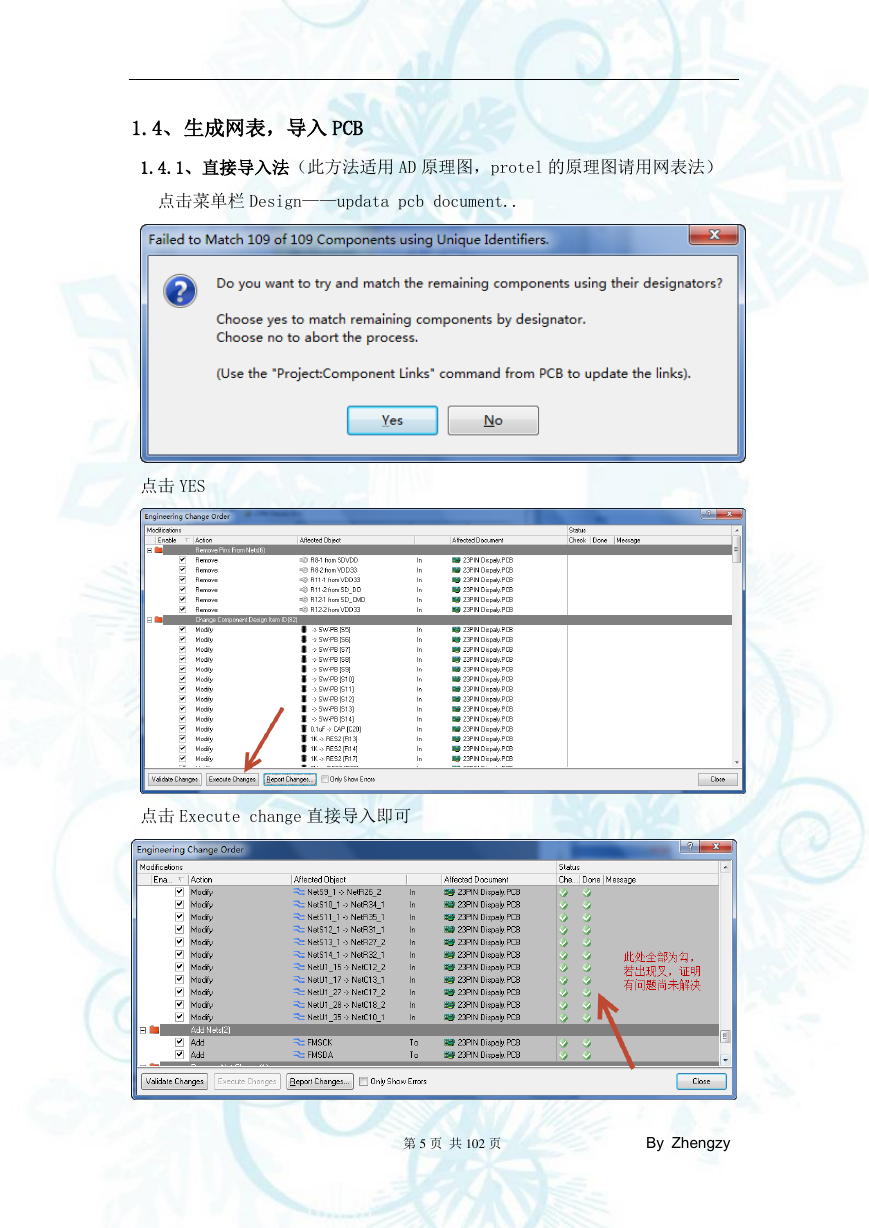

1.4、 生成网表,导入 PCB

1.4.1、直接导入法(此方法适用 AD 原理图,protel 的原理图请用网表法)

点击菜单栏 Design——updata pcb document..

点击 YES

点击 Execute change 直接导入即可

第 5 页 共 102 页 By Zhengzy

�

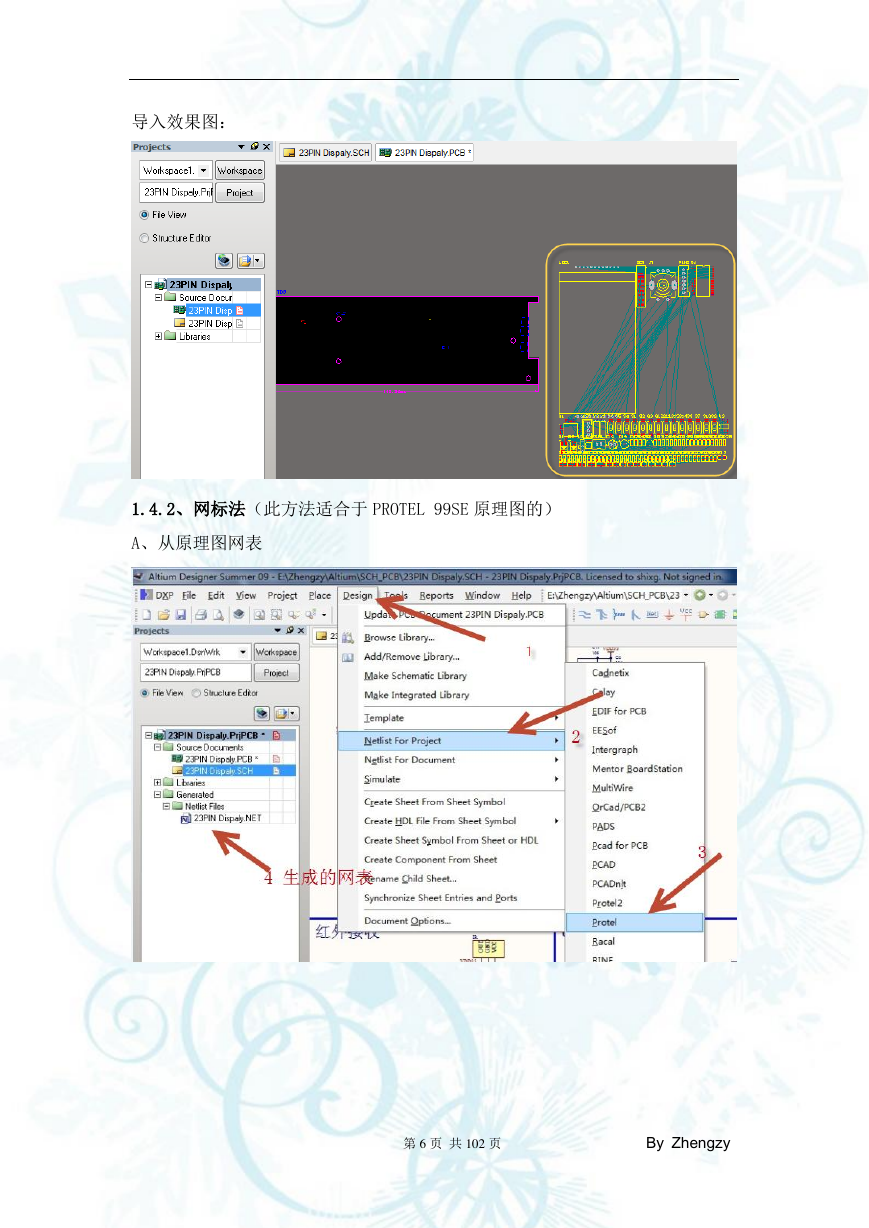

导入效果图:

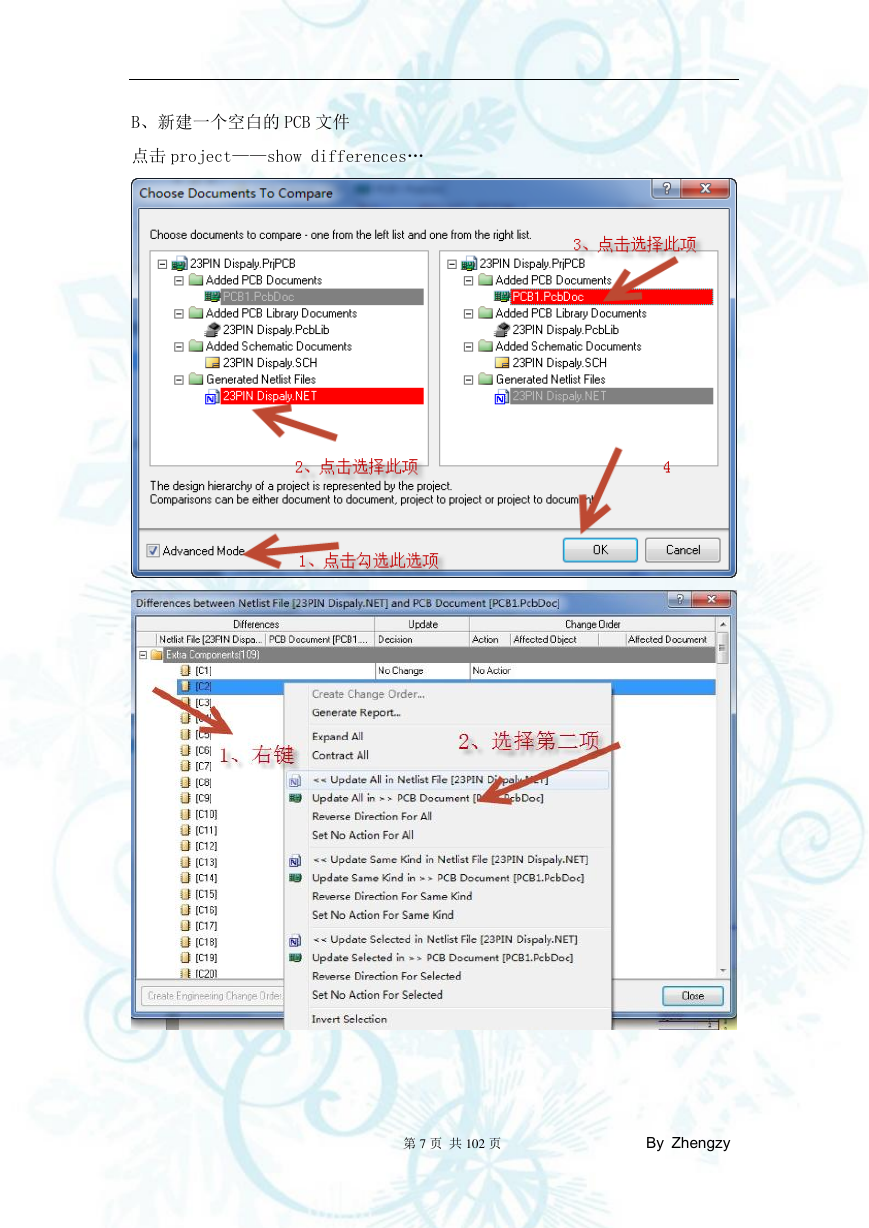

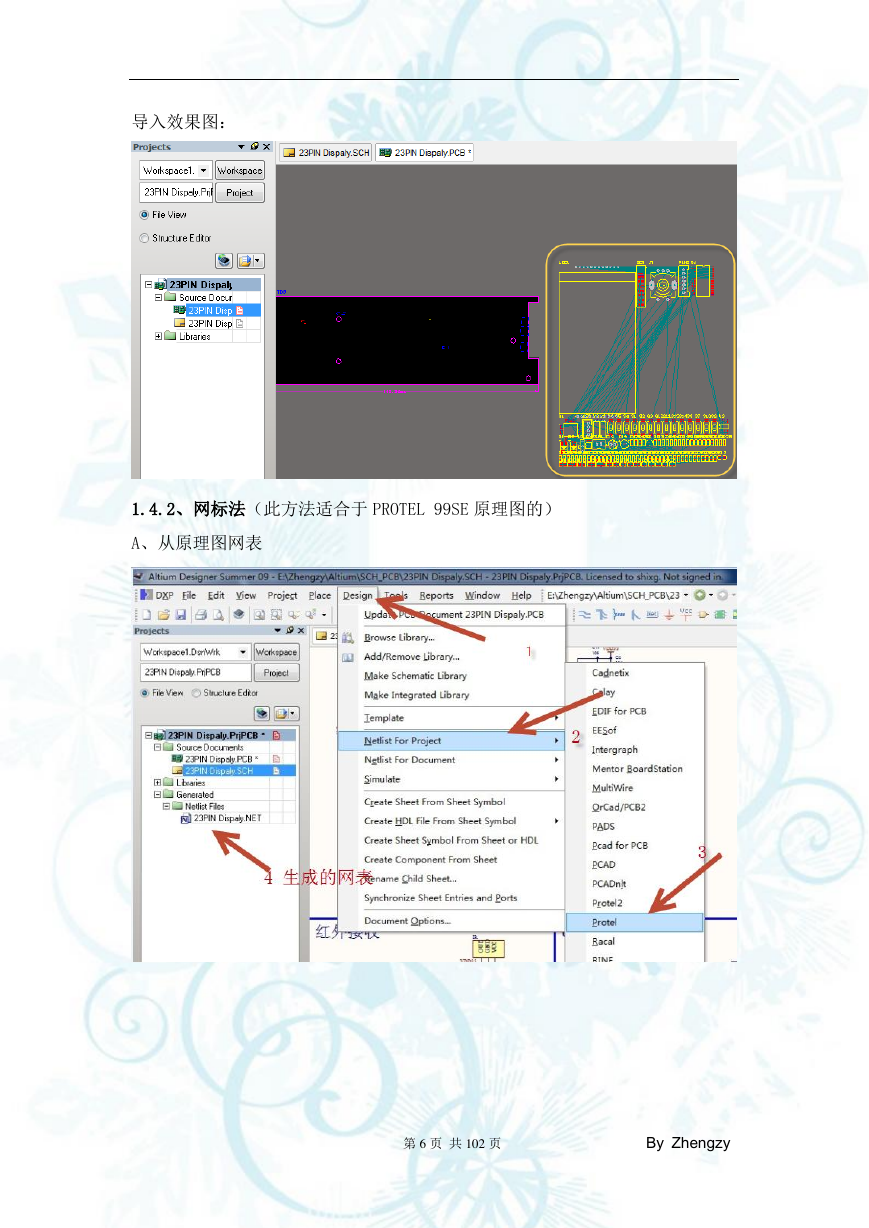

1.4.2、网标法(此方法适合于 PROTEL 99SE 原理图的)

A、从原理图网表

第 6 页 共 102 页 By Zhengzy

�

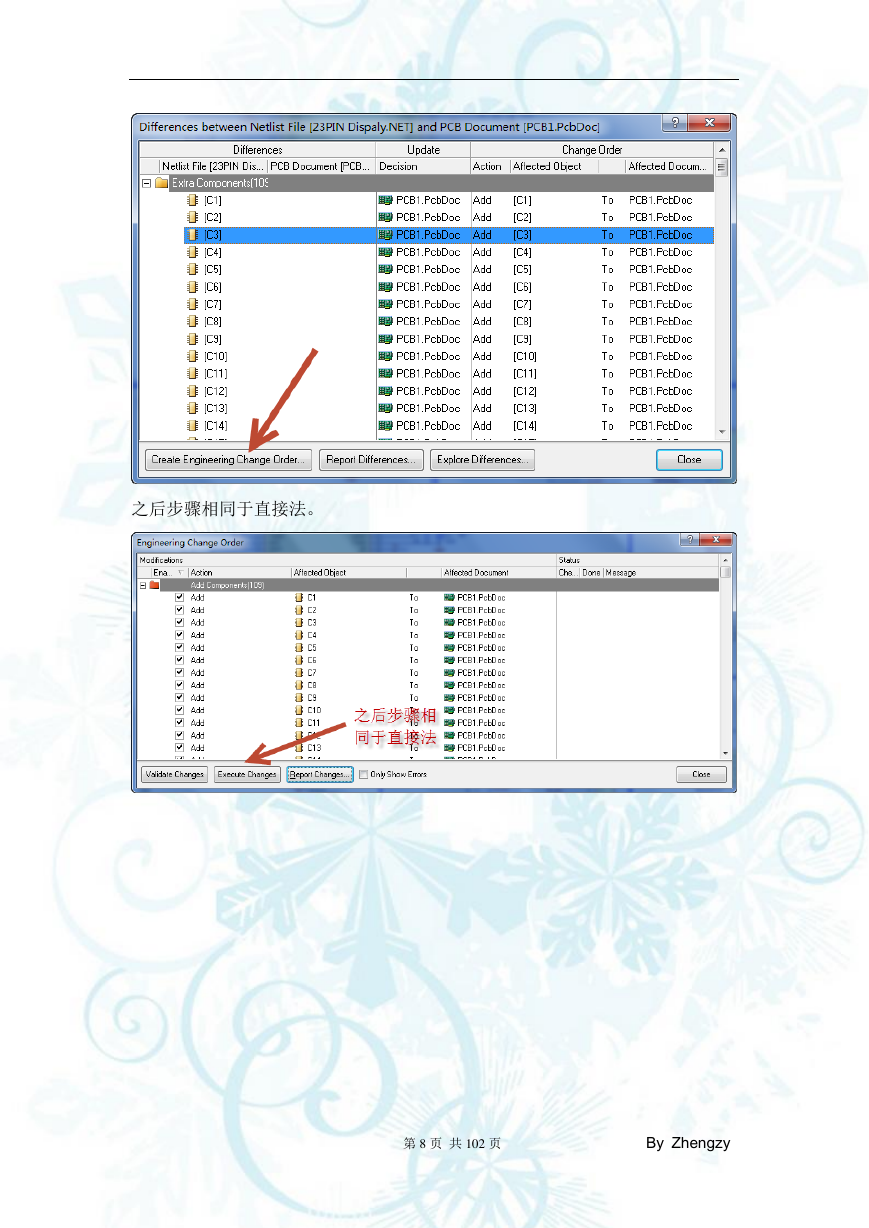

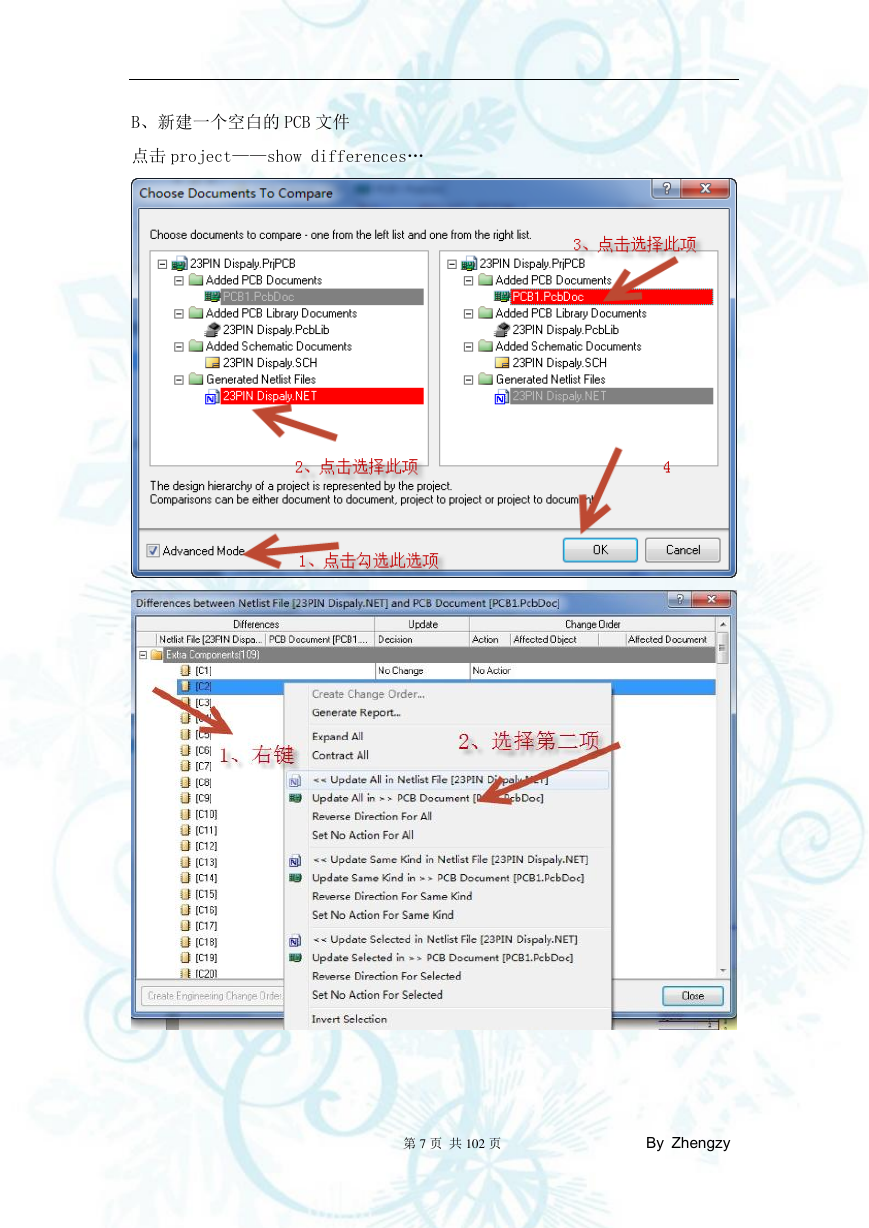

B、新建一个空白的 PCB 文件

点击 project——show differences„

第 7 页 共 102 页 By Zhengzy

�

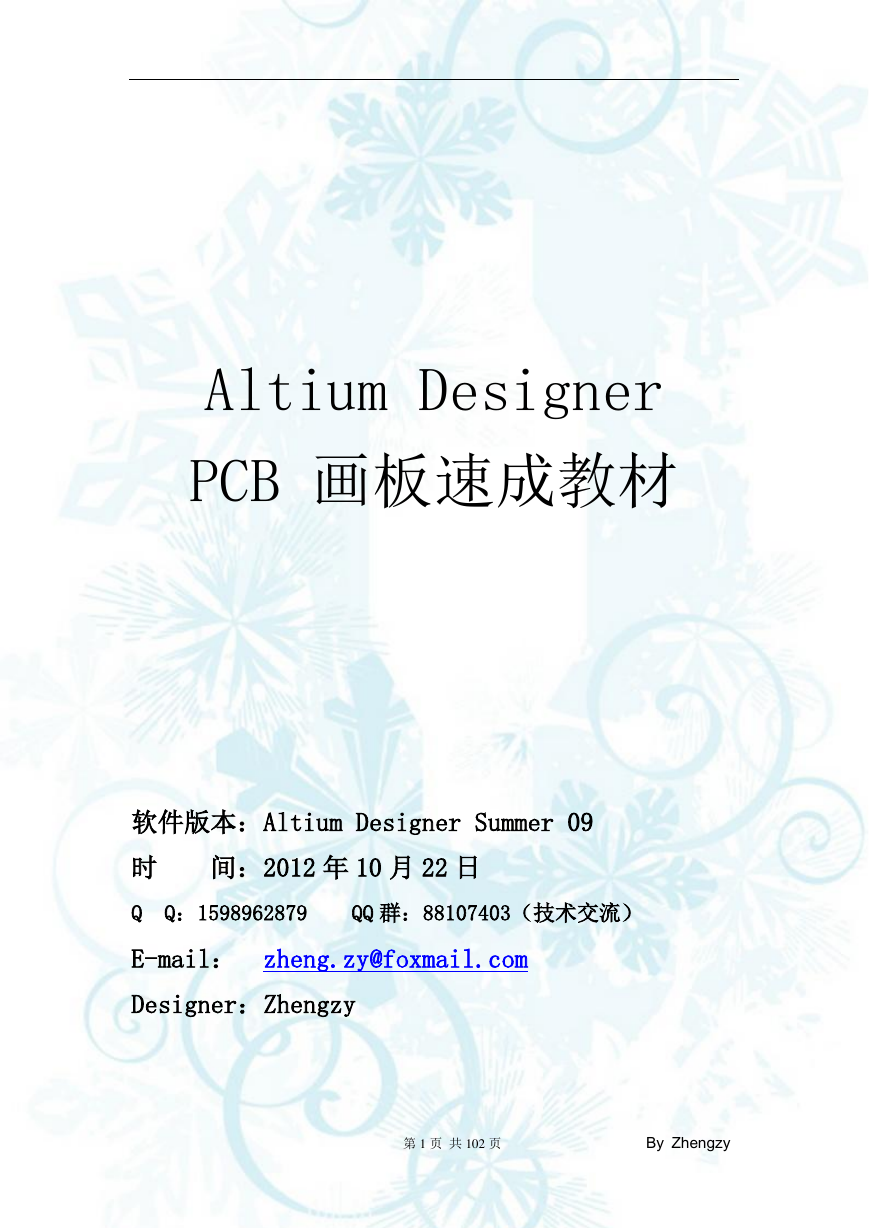

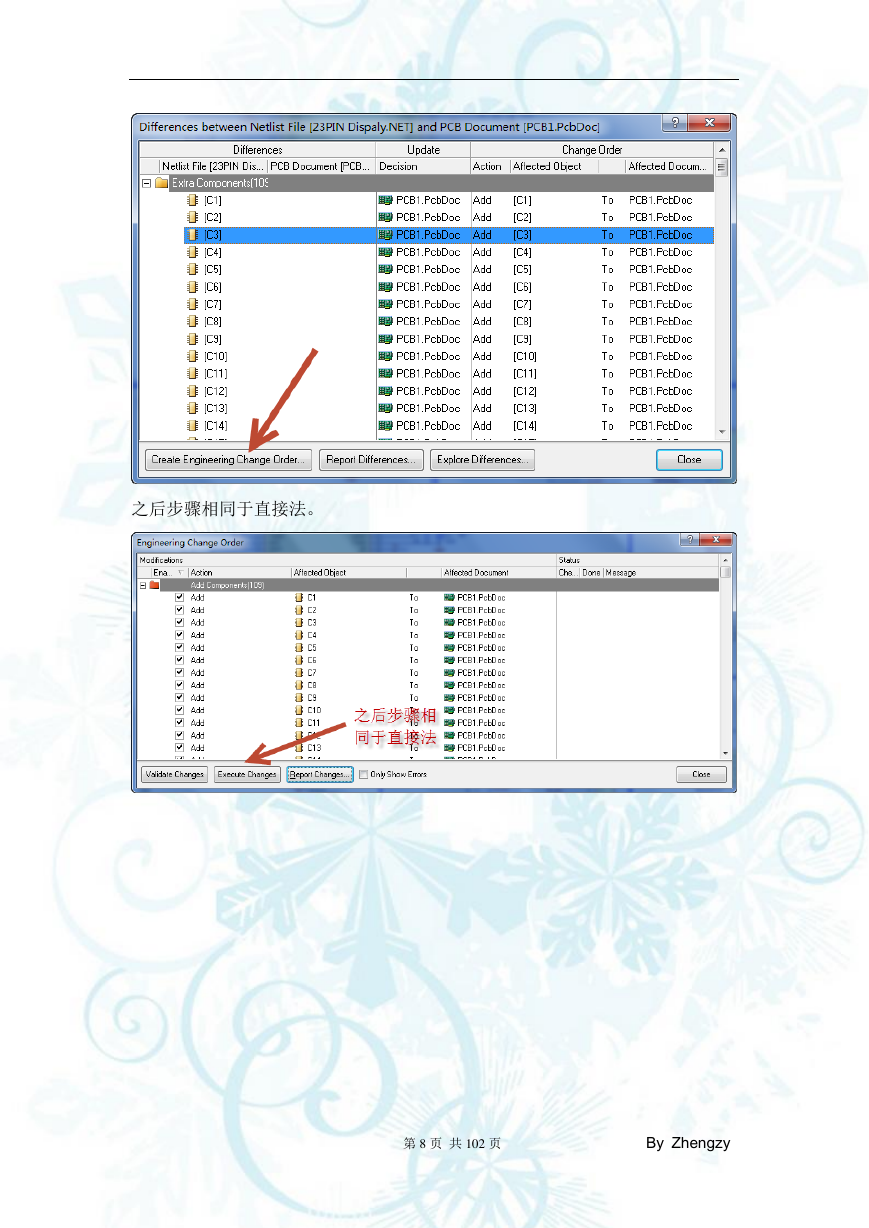

之后步骤相同于直接法。

第 8 页 共 102 页 By Zhengzy

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc