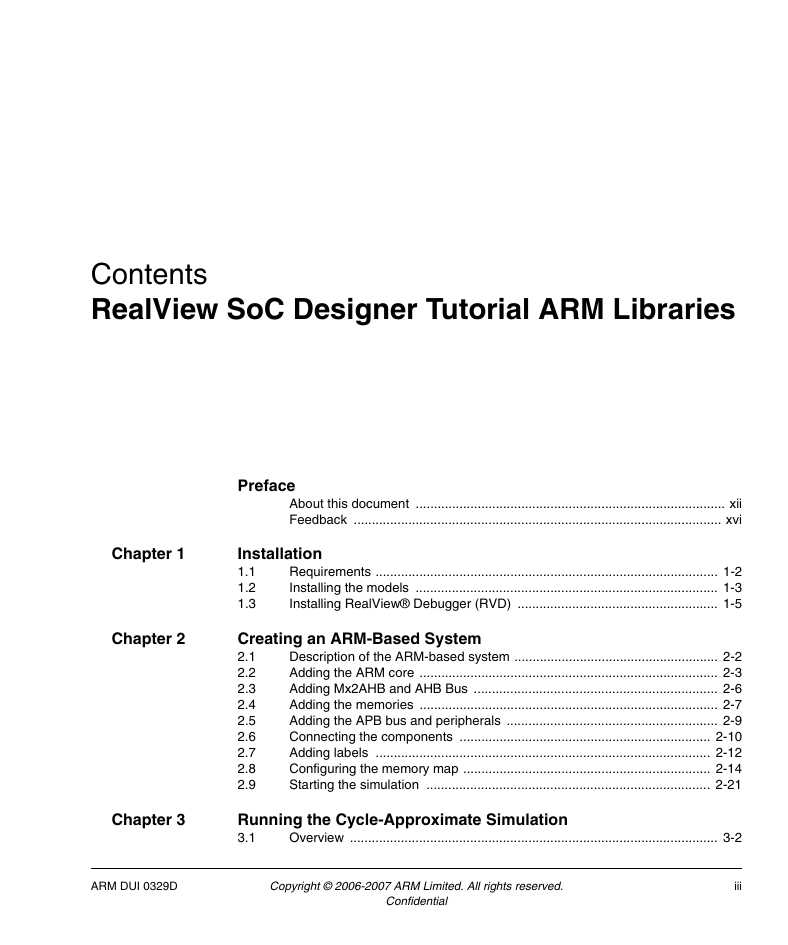

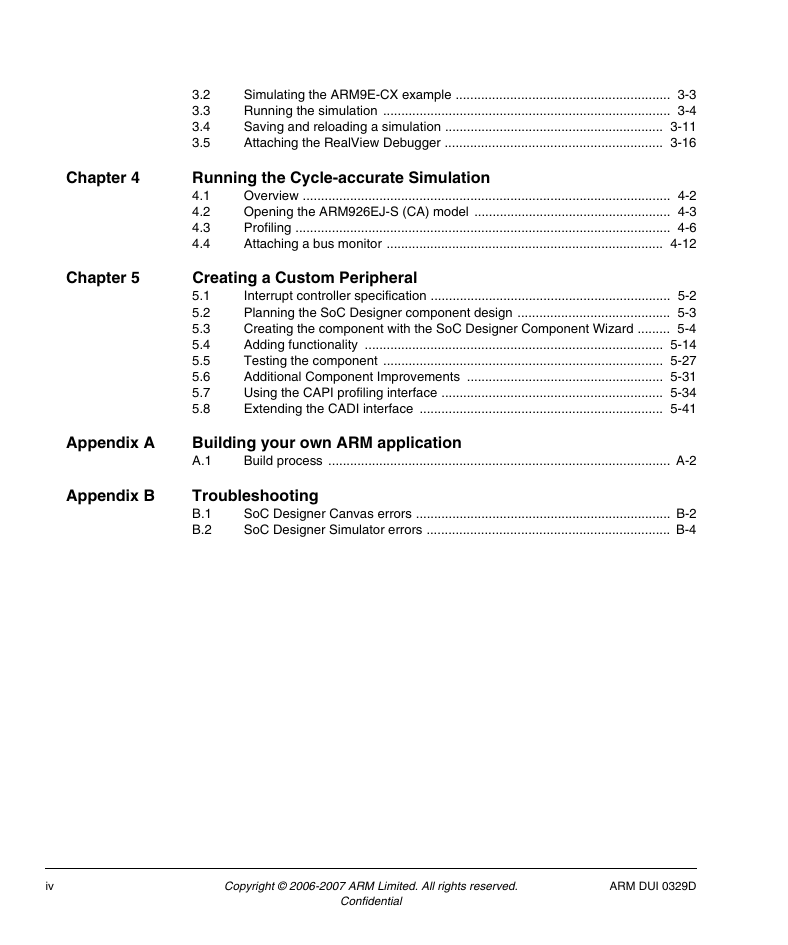

RealView SoC Designer Tutorial ARM Libraries

Contents

List of Tables

List of Figures

Preface

About this document

Intended audience

Organization

Terminology

Further reading

Feedback

Feedback on SoC Designer

Feedback on this document

Installation

1.1 Requirements

1.2 Installing the models

1.3 Installing RealView Debugger (RVD)

Creating an ARM-Based System

2.1 Description of the ARM-based system

2.2 Adding the ARM core

2.3 Adding Mx2AHB and AHB Bus

2.4 Adding the memories

2.5 Adding the APB bus and peripherals

2.6 Connecting the components

2.7 Adding labels

2.8 Configuring the memory map

2.9 Starting the simulation

Running the Cycle-Approximate Simulation

3.1 Overview

3.2 Simulating the ARM9E-CX example

3.3 Running the simulation

3.3.1 Setting a breakpoint

3.3.2 Viewing a signal

3.3.3 Viewing code

3.3.4 Viewing data memory

3.4 Saving and reloading a simulation

3.4.1 Saving a simulation

3.4.2 Opening a saved simulation file

3.5 Attaching the RealView Debugger

Running the Cycle-accurate Simulation

4.1 Overview

4.2 Opening the ARM926EJ-S (CA) model

4.2.1 Basic functionality

4.3 Profiling

4.4 Attaching a bus monitor

Creating a Custom Peripheral

5.1 Interrupt controller specification

5.1.1 Features

5.1.2 Memory-mapped registers

5.2 Planning the SoC Designer component design

5.3 Creating the component with the SoC Designer Component Wizard

5.3.1 Component name and location

5.3.2 Component attributes

5.3.3 Add port definitions

5.3.4 Add parameter definitions

5.3.5 Add CADI registers and memory regions

5.3.6 Generating the component files

5.4 Adding functionality

5.4.1 Variables for the communicate and update phases

5.4.2 Memory mapping

5.4.3 Private variables

5.4.4 Debug access to registers

5.4.5 The interrupt request signal

5.4.6 Reset behavior

5.4.7 Update Phase

5.4.8 Driving the irq output signal

5.4.9 Save and restore

5.4.10 Compiling the finished component code

5.5 Testing the component

5.5.1 Creating a test environment

5.5.2 Writing the script

5.5.3 Configuring the IRQ_ENABLE register

5.5.4 Driving the interrupt sources

5.5.5 Saving the script files

5.5.6 Running the test system

5.6 Additional Component Improvements

5.6.1 SetAddressRegions

5.6.2 GetMappingContraints

5.6.3 Remove unused functions

5.6.4 Cleaning up the ISRC port

5.7 Using the CAPI profiling interface

5.7.1 Implementing the CAPI interface class

5.7.2 Using the CAPI interface in the component

5.7.3 Recording profiling events

5.7.4 Displaying the profiling results

5.8 Extending the CADI interface

5.8.1 Define the new registers

5.8.2 Specifying read/write access behavior

Building your own ARM application

A.1 Build process

A.1.1 Source files

A.1.2 Linking the application

A.1.3 Loading the application

Troubleshooting

B.1 SoC Designer Canvas errors

B.1.1 Library not found

B.1.2 Overlapping regions

B.1.3 Port not connected

B.2 SoC Designer Simulator errors

B.2.1 Cycle counter advances, but no activity in system

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc