基于AD7656的多路并行同步音频数据采集系统设计与实现

李石亮,杨俊安,叶春逢

(电子工程学院安徽合肥230037)

摘 要:针对音频BSS(盲源分离)瞬时模型的多信源多传感器问题,提出一种严格的多路并行同步数据采集的ADC方

案。首先介绍ADC AD7656的性能特点,提出并实现一种并行同步多路音频数据采集的系统方案。着重介绍AD7656周围

电路的设计和控制逻辑的实现,解决多路采集时序及数据分离的难题;设计完成PCI采集系统的数据接口和驱动程序,采用

CPLD作控制核心,简化设计,且方便应用的扩展;最后,给出测试结果。该系统已实际应用于相关课题的研究。

关键词:AD7656;并行同步,$5933;音频数据采集

中图分类号:TP335+.1

文献标识码:B

文章编号:1004—373X(2008)10—167一04

Design and Implementation of Multiple Parallel——sync Audio

Data Acquisition System Based OR AD7656

LI Shiliang,YANG Jun’an,YE Chunfeng

(Electronic Engineering Institute,Hcfei,230037。China)

Abstract:A strict multiple parallel—sync data acquisition program of ADC has extracted tO settle the multi—source and

multi—sensor problem about instantaneous model of Blind Source Separation(BSS)in audio frequency.The features and func—

tions of ADC AD7656 are introduced in this paper firstly,and then a program of the multiple parallel—sync audio data acquisi—

tion is put forward and implemented.The design of AD7656’S around circuits and its control logic are described in detail,the

problem of time sequence and data separation is solved as well.The acquisition system’s design of data interface and the driver

is indicated.The CPI。D is used as control core to simplify the design,also,it is easier to expand the application of the system.

The testing results are given at last.Now。the system has been used in related research subject successfully.

Keywords..AD7656;parallel—sync;$5933laudio data collection

l 引 言

随着媒体技术的发展,对音频数据的采集和处理日趋

一种12路的PcI并行音频数据采集系统。

2 AD7656功能结构与特性

成熟,尤其在消费领域,各种产品层出不穷;然而在信号分

2.1结构与特性

选和处理方面,对音频数据采集提出了新的要求。比如盲

AD7656是基于iCMOS(industrial CMoS)工艺的一

源分离,他要求多路实时并行同步地采集数据。为满足这

款多通道高分辨率模数转换芯片。iCMOS是美国模拟器

些方面的算法应用对音频数据采集的要求,本文对多路并

件公司(ADD发布的一种创新的半导体制造工艺,他是将

行音频数据采集进行研究。对音频信号盲源分离可实现

高电压半导体工艺与亚微米CM()S和互补双极型工艺相

对强噪声背景,复杂信号环境下的特定信号目标的分选和

识别;音频信号盲源分离是在不知道信源数目和混合局,

结合的新技术。与采用传统CMOS制造工艺不同,采用

iCMOS制造工艺的模拟IC能承受高达30 V电源电压,

利用多传感器采集的混合数据,需要并行的采集多路音频

同时能提供突破的性能水平,降低系统设计成本,而且降

信号,且要求各路之间有严格的时间相关性,实现办法是

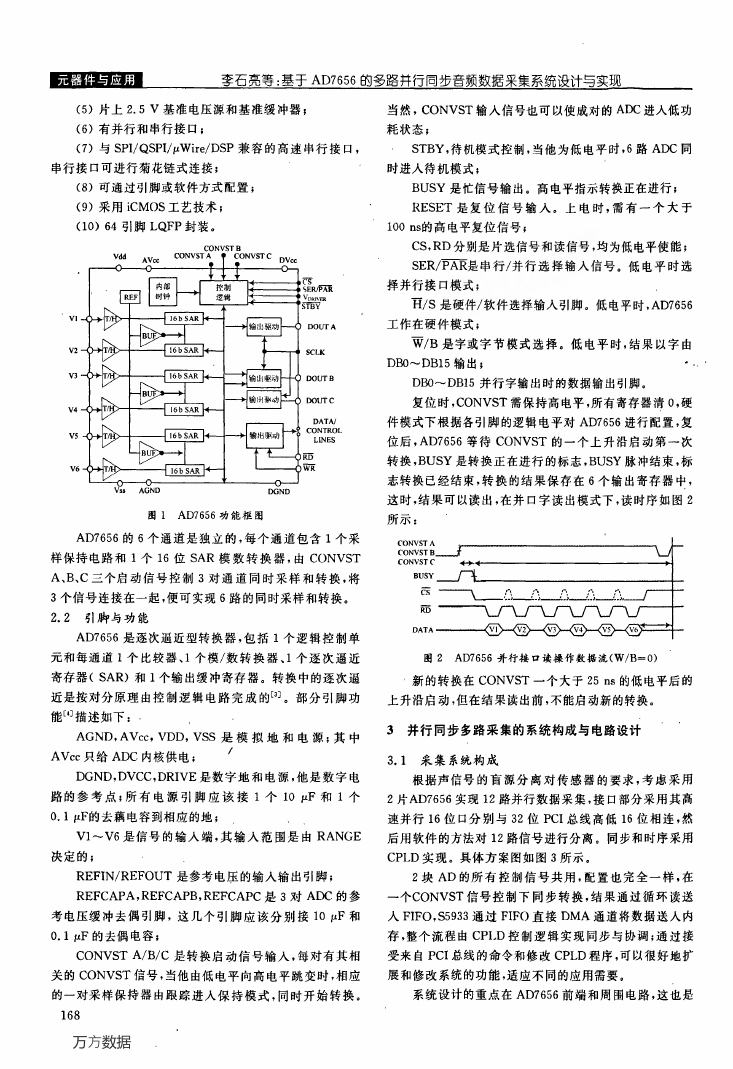

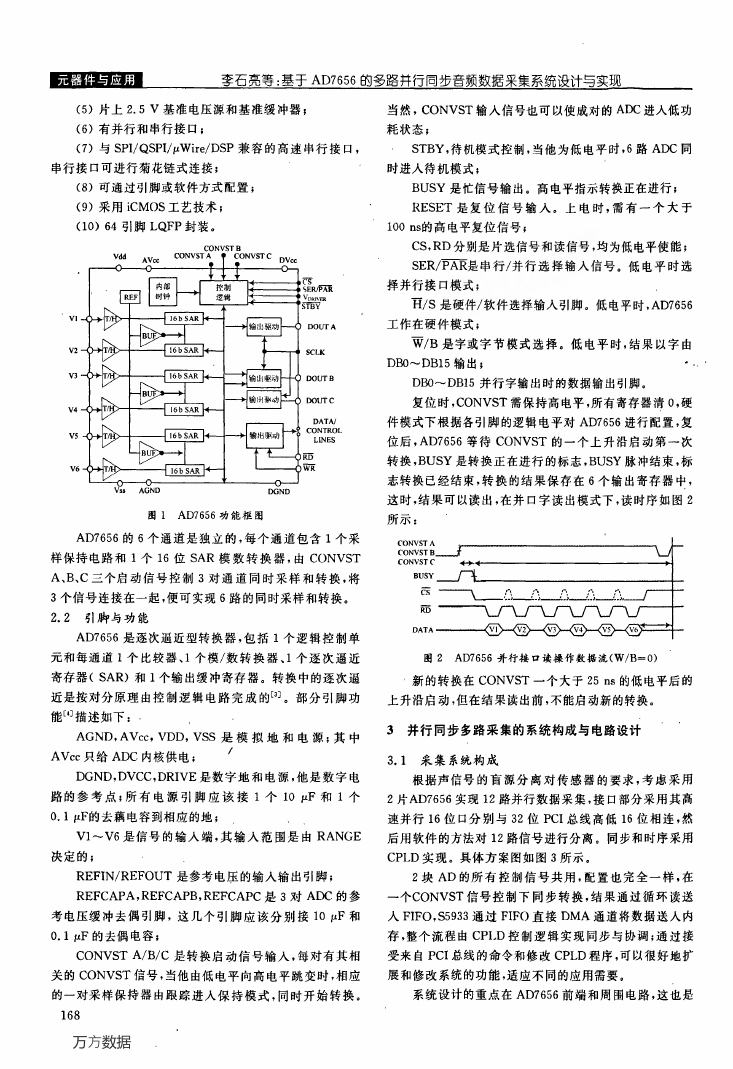

低85%的功耗和减小30%的封装尺寸n’2]。图1给出

各路严格地在同一时刻采样,且各通道在设计和性能上保

AD7656的功能框图。AD7656的主要特性如下:

持一致性。

本文针对盲源分离对音频数据采集的要求,采用模数

转换芯片AD7656及PCI接口芯片$5933设计并实现了

收穑日期:2007—1l—19

(1)6通道16 b逐次逼近型ADCl

(2)最大吞吐率为250 kS/s;

(3)低功耗:在供电电压为5 V、采样速率为250 kS/s

时的功耗仅为160 mW}

(4)宽带宽输入,高信噪比:输入频率为50 kHz时的

基金项目:安徽省自然科学基金资助项目(050420101)

信噪比(SNR)为85 dB,

167

万方数据

�

(5)片上2.5 V基准电压源和基准缓冲器;

当然,CONVST输入信号也可以使成对的ADC进入低功

(6)有并行和串行接口;

耗状态;

(7)与SPI/QSPI/#Wire/DSP兼容的高速串行接口,

STBY,待机模式控制,当他为低电平时,6路ADC同

串行接口可进行菊花链式连接;

时进入待机模式;

(8)可通过引脚或软件方式配置;

BUSY是忙信号输出。高电平指示转换正在进行;

(9)采用iCMOS工艺技术;

(10)64引脚LQFP封装。

Ⅵ

Ⅵ

w

w

w

w

’

RESET是复位信号输入。上电时,需有一个大于

i00 ns的高电平复位信号f

CS,RD分别是片选信号和读信号,均为低电平使能;

SER/—PA—R是串行/并行选择输入信号。低电平时选

择并行接口模式;

霄/S是硬件/软件选择输入引脚。低电平时,AD7656

工作在硬件模式;

W/B是字或字节模式选择。低电平时,结果以字由

DBo~DBl5输出;

‘

DBo~DBl5并行字输出时的数据输出引脚。

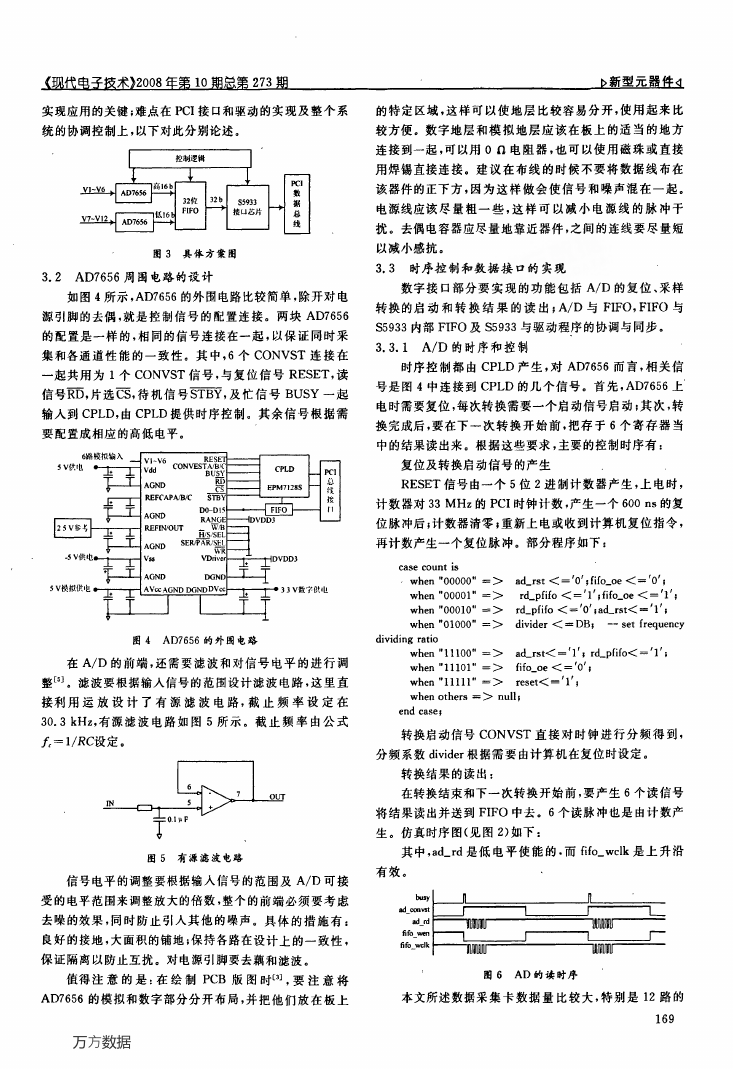

复位时,CONVST需保持高电平,所有寄存器清o,硬

件模式下根据各引脚的逻辑电平对AD7656进行配置,复

位后,AD7656等待CONVST的一个上升沿启动第一次

转换,BUSY是转换正在进行的标志,BUSY脉冲结束,标

志转换已经结束,转换的结果保存在6个输出寄存器中,

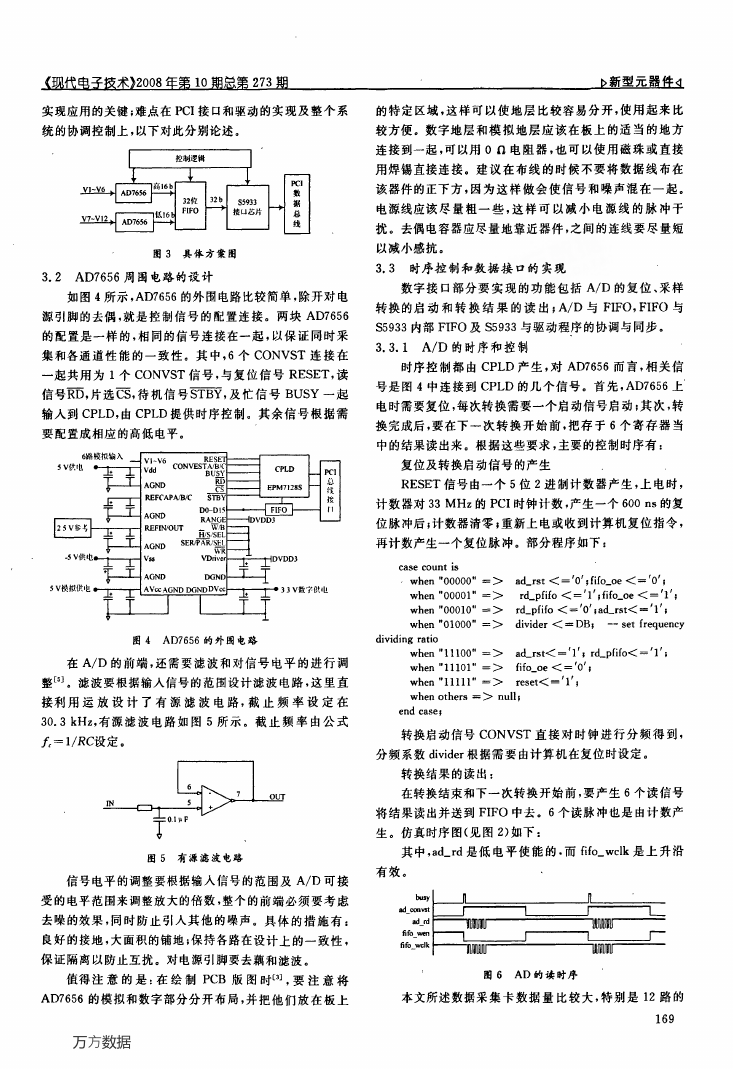

这时,结果可以读出,在并口字读出模式下,读时序如图2

一R

H

B

c

~断略

擎≥=ll|;I蒜

图1

AD7656功能框图

AD7656的6个通道是独立的,每个通道包含1个采

样保持电路和1个16位SAR模数转换器,由CONVST

A、B、C三个启动信号控制3对通道同时采样和转换,将

3个信号连接在一起,便可实现6路的同时采样和转换。

2.2 引脚与功能

AD7656是逐次逼近型转换器,包括1个逻辑控制单

所示:

㈣∞∞

汀盯盯吣一岱

盯瓣=茹一

^

A

B

C

.●

一舡

元和每通道1个比较器、1个模/数转换器、1个逐次逼近

图2 AD7656并行接口读操作数据流(W/B=0)

寄存器(SAR)和1个输出缓冲寄存器。转换中的逐次逼

、新的转换在CoNVST一个大子25 ns的低电平后的

近是按对分原理由控制逻辑电路完成的啪。部分引脚功

上升沿启动,但在结果读出前,不能启动新的转换。

能[43描述如下:,

AGND,AVcc,VDD,VSS是模拟地和电源;其中

3并行同步多路采集的系统构成与电路设计

AVcc只给ADC内核供电;

7

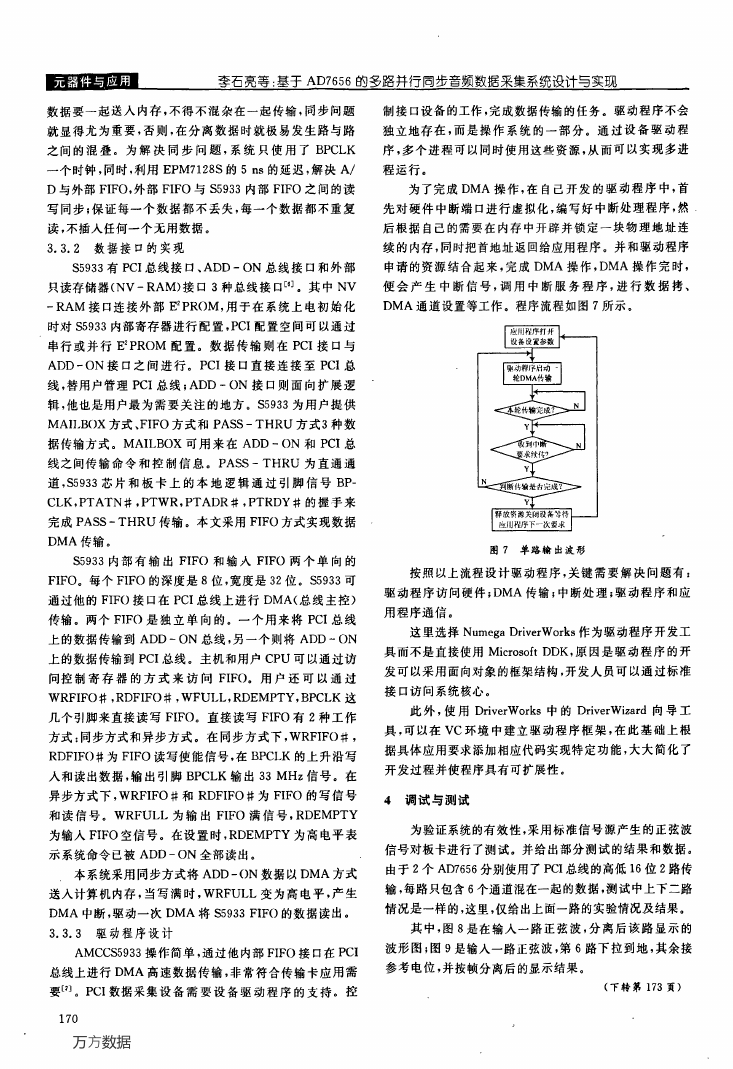

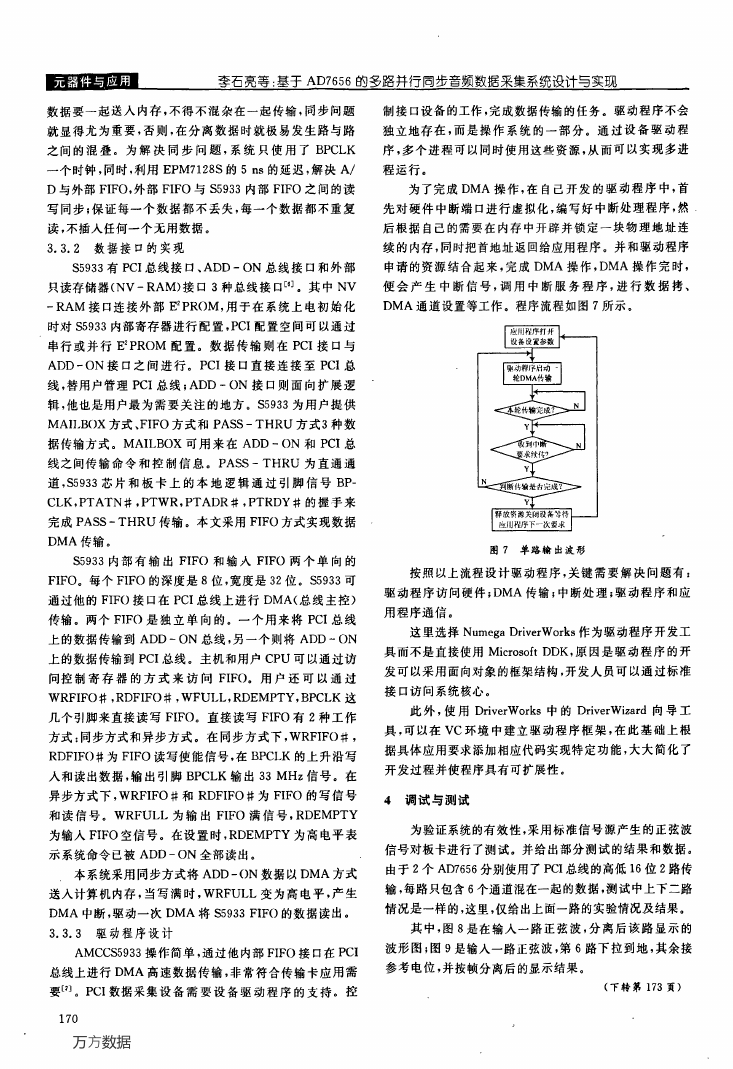

3.1采集系统构成

DGND,DVCC,DRIVE是数字地和电源,他是数字电

根据声信号的盲源分离对传感器的要求,考虑采用

路的参考点;所有电源引脚应该接1个10 pF和1个

2片AD7656实现12路并行数据采集,接口部分采用其高

0.1 pF的去藕电容到相应的地;

V1~V6是信号的输入端,其输入范围是由RANGE

决定的;

速并行16位口分别与32位PCI总线高低16位相连,然

后用软件的方法对12路信号进行分离。同步和时序采用

CPLD实现。具体方案图如图3所示。

REFIN/REFOUT是参考电压的输入输出引脚;

2块AD的所有控制信号共用,配置也完全一样,在

REFCAPA,REFCAPB,REFCAPC是3对ADC的参

一个cONVST信号控制下同步转换,结果通过循环读送

考电压缓冲去偶引脚,这几个引脚应该分别接10 pF和

入FIFO,$5933通过FIFO直接DMA通道将数据送入内

0.1弘F的去偶电容;

存,整个流程由CPI。D控制逻辑实现同步与协调;通过接

CONVST A/B/C是转换启动信号输入,每对有其相

受来自PCI总线的命令和修改CPLD程序,可以很好地扩

关的CONVST信号,当他由低电平向高电平跳变时,相应

展和修改系统的功能,适应不同的应用需要。

的一对采样保持器由跟踪进入保持模式,同时开始转换。

系统设计的重点在AD7656前端和周围电路,这也是

168

万方数据

�

实现应用的关键;难点在PCI接口和驱动的实现及整个系

的特定区域,这样可以使地层比较容易分开,使用起来比

统的协调控制上,以下对此分别论述。

I

控制逻辑

I

叫v,_v12藜妄赫l_7:A周W

—砸蛐m由网

l‘”“卜_H“…。“卜叫“I

图3具体方案图

3.2

AD7656周围电路的设计

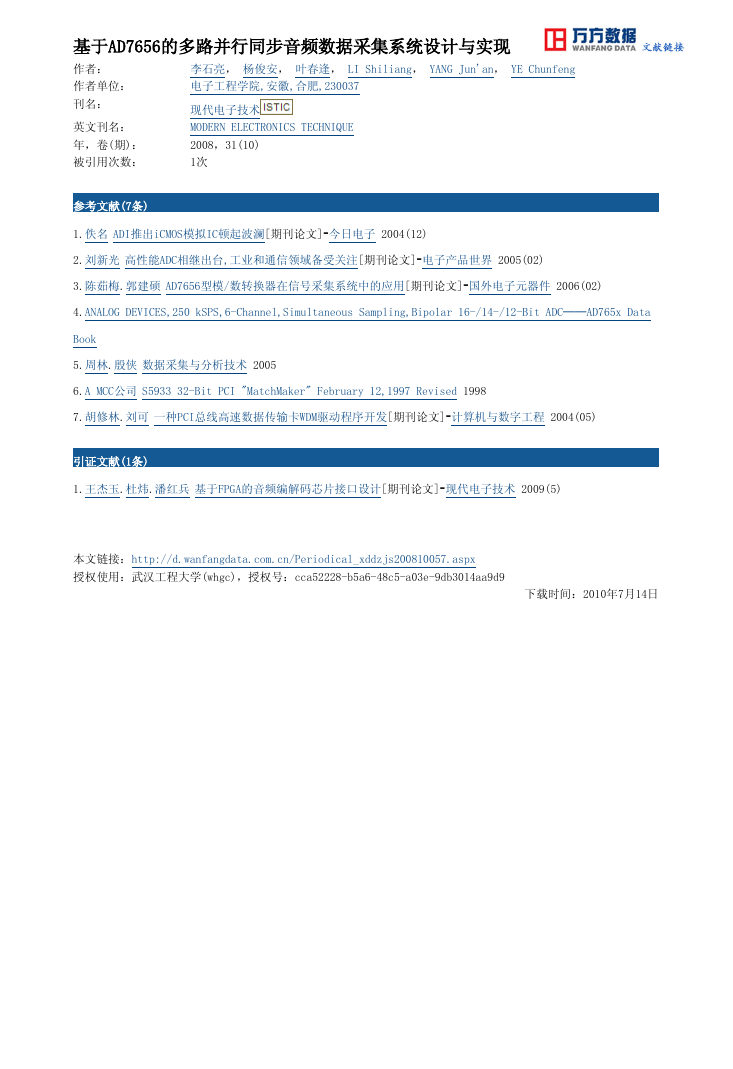

如图4所示,AD7656的外围电路比较简单,除开对电

源引脚的去偶,就是控制信号的配置连接。两块AD7656

的配置是一样的,相同的信号连接在一起,以保证同时采

集和各通道性能的一致性。其中,6个CONVST连接在

一起共用为1个CoNVsT信号,与复位信号RESET,读

信号RD,片选CS,待机信号STBY,及忙信号BUSY一起

输入到CPLD,由CPLD提供时序控制。其余信号根据需

要配置成相应的高低电平。

较方便。数字地层和模拟地层应该在板上的适当的地方

连接到一起,可以用0 1"1电阻器,也可以使用磁珠或直接

用焊锡直接连接。建议在布线的时候不要将数据线布在

该器件的正下方,因为这样做会使信号和噪声混在一起。

电源线应该尽量粗一些,这样可以减小电源线的脉冲干

扰。去偶电容器应尽量地靠近器件,之间的连线要尽量短

以减小感抗。

3.3时序控制和数据接l:J的实现

数字接口部分要实现的功能包括A/D的复位、采样

转换的启动和转换结果的读出;A/D与FIFO,FIFO与

$5933内部FIFO及$5933与驱动程序的协调与同步。

3.3.1

A/D的时序和控制

时序控制都由CPLD产生,对AD7656而言,相关信

号是图4中连接到CPLD的几个信号。首先,AD7656上

电时需要复位,每次转换需要一个启动信号启动;其次,转

换完成后,要在下一次转换开始前,把存于6个寄存器当

中的结果读出来。根据这些要求,主要的控制时序有:

复位及转换启动信号的产生

RESET信号由一个5位2进制计数器产生,上电时,

计数器对33 MHz的PCI时钟计数,产生一个600 us的复

位脉冲后;计数器清零;重新上电或收到计算机复位指令,

再计数产生一个复位脉冲。部分程序如下:

case count is

,when”00000”=>ad_rst<一…0;fifo_oe<=…0 1

when”00001”=>

when”00010”=>rd—pfifo<=70’;ad_rst<=‘1’,

when”01000”=>divider<=DB; 一一set frequency

rd_pfifo<=’1’lfifo_oe<一…1;

图4

AD7656的外围电路

dividing ratio

在A/D的前端,还需要滤波和对信号电平的进行调

整口]。滤波要根据输入信号的范围设计滤波电路,这里直

接利用运放设计了有源滤波电路,截止频率设定在

30.3 kHz,有源滤波电路如图5所示。截止频率由公式

,f一1/RC设定。

图5有源滤波电路

信号电平的调整要根据输入信号的范围及A/D可接

受的电平范围来调整放大的倍数,整个的前端必须要考虑

去噪的效果,同时防止引入其他的噪声。具体的措施有:

良好的接地,大面积的铺地;保持各路在设计上的一致性,

保证隔离以防止互扰。对电源引脚要去藕和滤波。

值得注意的是:在绘制PCB版图时‘“,要注意将

when”11100“=>ad_rst<一…1 l rd_pfifo<一…1;

when”11101”一>fifo_oe<一…0 1

when”11111”一>reset<=71’1

when others=>null;

end case,

转换启动信号CONVST直接对时钟进行分频得到,

分频系数divider根据需要由计算机在复位时设定。

转换结果的读出:

在转换结束和下一次转换开始前,要产生6个读信号

将结果读出并送到FIFO中去。6个读脉冲也是由计数产

生。仿真时序图(见图2)如下:

其中,aQ—rd是低电平使能的.而fifo—wclk是上升沿

有效。

.

busy

ad con%t

ad

rd

6foⅥm

6fo walk

图6

AD的读时序

AD7656的模拟和数字部分分开布局,并把他们放在板上

本文所述数据采集卡数据量比较大,特别是12路的

169

万方数据

�

■蓬疆盈a目盟

妻查塞董i基王垒旦!!i!鲍量墅羞鱼回生童塑麴堡墨塞丞蕴退让皇塞婴

数据要一起送人内存,不得不混杂在一起传输,同步问题

制接口设备的工作,完成数据传输的任务。驱动程序不会

就显得尤为重要,否则,在分离数据时就极易发生路与路

独立地存在,而是操作系统的一部分。通过设备驱动程

之间的混叠。为解决同步问题,系统只使用了BPCLK

序,多个进程可以同时使用这些资源,从而可以实现多进

一个时钟,同时,利用EPM7128S的5 ns的延迟,解决A/

程运行。

D与外部FIFO,外部FIFO与$5933内部FIFO之间的读

为了完成DMA操作,在自己开发的驱动程序中,首

写同步;保证每一个数据都不丢失,每一个数据都不重复

先对硬件中断端口进行虚拟化,编写好中断处理程序,然

读,不插入任何一个无用数据。

3.3.2 数据接口的实现

$5933有PCI总线接口、ADD一0N总线接口和外部

只读存储器(NV—RAM)接口3种总线接口[“。其中NV

后根据自己的需要在内存中开辟并锁定一块物理地址连

续的内存,同时把首地址返回给应用程序。并和驱动程序

申请的资源结合起来,完成DMA操作,DMA操作完时,

便会产生中断信号,调用中断服务程序,进行数据拷、

—RAM接口连接外部E2PROM,用于在系统上电初始化

DMA通道设置等工作。程序流程如图7所示。

时对$5933内部寄存器进行配置,PCI配置空间可以通过

串行或并行E2PROM配置。数据传输则在PCI接口与

ADD—ON接口之间进行。PCI接口直接连接至PCI总

线,替用户管理PCI总线;ADD~ON接口则面向扩展逻

辑,他也是用户最为需要关注的地方。$5933为用户提供

MAIl。BOX方式、FIFO方式和PASS—THRU方式3种数

据传输方式。MAILBOX可用来在ADD—ON和PCI总

线之间传输命令和控制信息。PASS—THRU为直通通

道,$5933芯片和板卡上的本地逻辑通过引脚信号BP—

CLK,PTATN#,PTWR,PTADR#,PTRDY#的握手来

完成PASS—THRU传输。本文采用FIFO方式实现数据

DMA传输。

$5933内部有输出FIFO和输入FIFO两个单向的

FIFO。每个FIFO的深度是8位,宽度是32位。$5933可

通过他的FIFO接口在PCI总线上进行DMA(总线主控)

传输。两个FIFO是独立单向的。一个用来将PCI总线

上的数据传输到ADD—ON总线,另一个则将ADD—ON

上的数据传输到PCI总线。主机和用户CPU可以通过访

问控制寄存器的方式来访问FIFO。用户还可以通过

WRFIF0#,RDFIF0#,WFUI,L,RDEMPTY,BPCLK这

几个引脚来直接读写FIFO。直接读写FIFO有2种工作

方式:同步方式和异步方式。在同步方式下,WRFIFO#,

RDFIFO#为FIFO读写使能信号,在BPCLK的上升沿写

入和读出数据,输出引脚BPCLK输出33 MHz信号。在

应川程序打开

设备设置参数=丁

马|_I动稃序启动

轮DMA传输

霉

释放资源关|=|j敬备*待

应川程序下一次要求

图7单路输出波形

按照以上流程设计驱动程序,关键需要解决问题有:

驱动程序访问硬件;DMA传输;中断处理;驱动程序和应

用程序通信。

这里选择Numega DriverWorks作为驱动程序开发工

具而不是直接使用Microsoft DDK,原因是驱动程序的开

发可以采用面向对象的框架结构,开发人员可以通过标准

接口访问系统核心。

此外,使用DriverWorks中的DriverWizard向导工

具,可以在VC环境中建立驱动程序框架,在此基础上根

据具体应用要求添加相应代码实现特定功能,大大简化了

开发过程并使程序具有可扩展性。

异步方式下,WRFIFO#和RDFIFO#为FIFO的写信号

4调试与测试

和读信号。WRFULL为输出FIFO满信号,RDEMPTY

为输入FIFO空信号。在设置时,RDEMPTY为高电平表

示系统命令已被ADD—oN全部读出。

本系统采用同步方式将ADD—ON数据以DMA方式

送入计算机内存,当写满时,WRFULL变为高电平,产生

DMA中断,驱动一次DMA将$5933 FIFO的数据读出。

3.3.3驱动程序设计

为验证系统的有效性,采用标准信号源产生的正弦波

信号对板卡进行了测试。并给出部分测试的结果和数据。

由于2个AD7656分别使用了PCI总线的高低16位2路传

输,每路只包含6个通道混在一起的数据,测试中上下二路

情况是一样的,这里,仅给出上面一路的实验情况及结果。

其中,图8是在输入一路正弦波,分离后该路显示的

AMCCS5933操作简单,通过他内部FIFO接口在PCI

波形图;图9是输入一路正弦波,第6路下拉到地,其余接

总线上进行DMA高速数据传输,非常符合传输卡应用需

要"3。PCI数据采集设备需要设备驱动程序的支持。控

参考电位,并按帧分离后的显示结果。

(下转第173页)

】70

万方数据

�

设置的实现提供了电路支持。

参考文献

[13颜重光.BL75R06近距离非接触射频识别Ic卡

芯片[J3.电子设计应用,2007,60(4):128—129.

[23 Klause Finkenuller.射倾识别(RFID)技术[M].

北京:电子工业出版社。2001.

[3]北京远兴时代科技有限公司.MTP一125K4 Se-

ries Low Cost Proximity Reader.

[43秦龙.MSP430单片杌常用模块与综合系统实

例精华[M].北京:电子工业出版社,2007.

[5]余永权.FLASH单片机原理及应用[M].北京:

电子工业出版社,1997.

[63赵亮.单片机c语言编程与实例[M].北京:人

民邮电出版社,2003.

[7]李朝青.单片机及DSP外围数字IC技术手册

[z].北京:北京航空航天大学出版社,2002.

[83陈润泰,许琨。检测技术与智能仪表[M].长沙:

中南工业大学出版社,2001.

图3射频卡读卡电路图

4结语

本文采用低功耗MSP430单片机和EM4100只读卡构

京:北京航空航天大学出版社,1990.

成的读卡电路,简单、实用,成本低廉的特点,可实现卡号永

[103胡汉才.单片机原理及其接口技术[M3.北京:清华大学出

[9]沈德金.MCS一51系列单片机接I:1电路与应用实例[M].北

不重复、具有卡号复制困难、安全级别高,为信息查询、参数

版社,1996.

作者简介 刘继平 男,1953年出生,河北大名人,湖南工业职业技术学院副院长,副教授。研究方向为自动控制技术。

(上接第170页)

测试结果表明,数据完全分离开了,各路间没有互扰,信噪

比达到了设计要求系统经过调试,系统已成功应用于基于

盲源分离的战场目标声探测等2个课题研究,实践证明,

该系统稳定可靠。

参考文献

[13佚名.ADI推出iCMOS模拟lc顿起波澜[J].今El电子,

2004(12):135.

图8分离效果图1

[23刘新光.高性能ADC相继出台,工业和通信领域备受关注

[J].电子产品世界.2005(2):92—94.

[33陈茹梅,郭建硕.AD7656型模/数转换器在信号采集系统中

的应用[J].国外电子元器件,2006(2):67—71.

[43 ANALOG DEVICES,250 kSPS,6一Channel,Simultaneous

Sampling.Bipolar 16-/14-/12一Bit ADC——AD765x Da—

ta Book.

[5丁周林。殷侠.数据采集与分析技术[M].西安:西安电子科技

大学出版社,2005.

[6]A MCC公司,S5933 32一Bit PCI“MatchMaker”February

12。1997 Revised October 1998.

[73胡修林,刘可.一种PCI总线高速数据传输卡WDM驱动程

序开发口],计算机与数字工程,2004,33(5):96—99.

173

图9分离效果图2

输入正弦波(V,,一1 V),由实测数据得到输出信噪比为:

60.85 dB。

万方数据

�

基于AD7656的多路并行同步音频数据采集系统设计与实现

作者:

李石亮, 杨俊安, 叶春逢, LI Shiliang, YANG Jun'an, YE Chunfeng

作者单位:

刊名:

电子工程学院,安徽,合肥,230037

现代电子技术

英文刊名:

MODERN ELECTRONICS TECHNIQUE

年,卷(期):

2008,31(10)

1次

被引用次数:

参考文献(7条)

1.佚名 ADI推出iCMOS模拟IC顿起波澜[期刊论文]-今日电子 2004(12)

2.刘新光 高性能ADC相继出台,工业和通信领域备受关注[期刊论文]-电子产品世界 2005(02)

3.陈茹梅.郭建硕 AD7656型模/数转换器在信号采集系统中的应用[期刊论文]-国外电子元器件 2006(02)

4.ANALOG DEVICES,250 kSPS,6-Channel,Simultaneous Sampling,Bipolar 16-/14-/12-Bit ADC──AD765x Data

Book

5.周林.殷侠 数据采集与分析技术 2005

6.A MCC公司 S5933 32-Bit PCI "MatchMaker" February 12,1997 Revised 1998

7.胡修林.刘可 一种PCI总线高速数据传输卡WDM驱动程序开发[期刊论文]-计算机与数字工程 2004(05)

引证文献(1条)

1.王杰玉.杜炜.潘红兵 基于FPGA的音频编解码芯片接口设计[期刊论文]-现代电子技术 2009(5)

本文链接:http://d.wanfangdata.com.cn/Periodical_xddzjs200810057.aspx

授权使用:武汉工程大学(whgc),授权号:cca52228-b5a6-48c5-a03e-9db3014aa9d9

下载时间:2010年7月14日

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc