第 33 卷第 6 期

2012 年 6 月

通 信 学 报

Journal on Communications

Vol.33 No. 6

June 2012

Gardner 定时同步环路参数设计及性能分析

(1. 国防科学技术大学 电子科学与工程学院,湖南 长沙 410073;2. 解放军 61062 部队,北京 100091)

付永明 1,朱江 1,琚瑛珏 1, 2

摘 要:以数字锁相环理论为依据,对 Gardner 定时误差检测器反馈定时环路参数的设计进行了深入研究,基于

MATLAB 对一阶、二阶环路性能进行了仿真,重点分析了环路阶数和等效噪声带宽对系统性能的影响,得到了等

效噪声带宽与定时同步环路性能的关系,为定时同步环路的设计提供了理论依据。

关键词:定时同步;Gardner 定时误差检测器;数字锁相环;环路参数;同步性能

中图分类号:TN911 文献标识码:A 文章编号:1000-436X(2012)06-0191-08

Parameters design and performance analysis of the timing

recovery loop based on Gardner timing detector

FU Yong-ming1, ZHU Jiang1, JU Ying-jue1,2

( 1. School of Electronic Science and Engineering, National University of Defense Technology, Changsha 410073, China;

2. PLA 61062 Troops, Beijing 100091, China)

Abstract: In-depth research was carried out into parameters design in the feedback timing recovery loop based on Gard-

ner timing error detector, according to the theory of digital phase-lock loop. MATLAB based simulation was performed

for both first-order and second-order loop. Comprehensive analysis of the influence from loop order and noise- equiva-

lent bandwidth on synchronization performance indicates the relationship between synchronization performance and

noise-equivalent bandwidth, which provides a theoretic reference for timing recovery loop design.

Key words: timing synchronization; Gardner timing error detector; digital phase-lock loop; loop parameter; synchroniza-

tion performance

1 引言

定时同步环路作为全数字接收机中最重要的

组成部分,对整机系统性能有着重要的影响。定时

同步环路的结构一般分为 2 类:前馈结构和反馈

结构。前馈结构和反馈结构中的定时误差检测器

又有数据辅助和非数据辅助之分[1,2]。其中,基于

反馈结构的 Gardener 定时同步环路由于不需要辅

助数据,每个符号只需要 2 个采样,而且独立于

载波相位,实现复杂度较低等原因,在实际中普遍

使用[3~5]。然而,由于反馈定时环路性能分析较为

复杂[6],目前多数相关文献给出的设计及仿真结果

收稿日期:2011-01-21;修回日期:2011-08-10

都是在给定的环路参数及结构下得到的,而这些参

数选取常常缺乏系统的理论支持,通常是在仿真及

实际应用过程中通过试探不同的取值组合得到的,

至于这些结构和取值是否可以进一步优化并不得

而知[1,2,7~11];而且诸多文献在对 Gardner 定时环路

性能进行考察时多是以一阶环路为基础的,对二阶

环路没有足够的分析及重视[1,2,10,11];另外,文献给

出的仿真结果都只是验证了环路设计在特定参数

选取和应用场景下的有效性,而对环路整体的捕获

及跟踪性能没有进一步的分析及论述[7~11]。本文即

着眼于解决上述问题,利用数字锁相环理论对基于

Gardner 非数据辅助定时误差检测器的反馈定时环

�

·192·

通 信 学 报

第 33 卷

路进行了较为详尽的理论分析,给出了定时同步环

路参数的详细设计及其依据,对 MATLAB 仿真结

果的分析及归纳为在实际应用中进行定时环路的

设计提供了参考依据。

2 系统模型

一个定时误差检测器的特性由其 S 曲线来表

征[6]。S 曲线是相位误差的函数(这里为定时相差),

定义为

1垐

Err k

ˆ

(4)

k

E

S

,

|

k

由文献[1],令 ε=δ/T,则有:

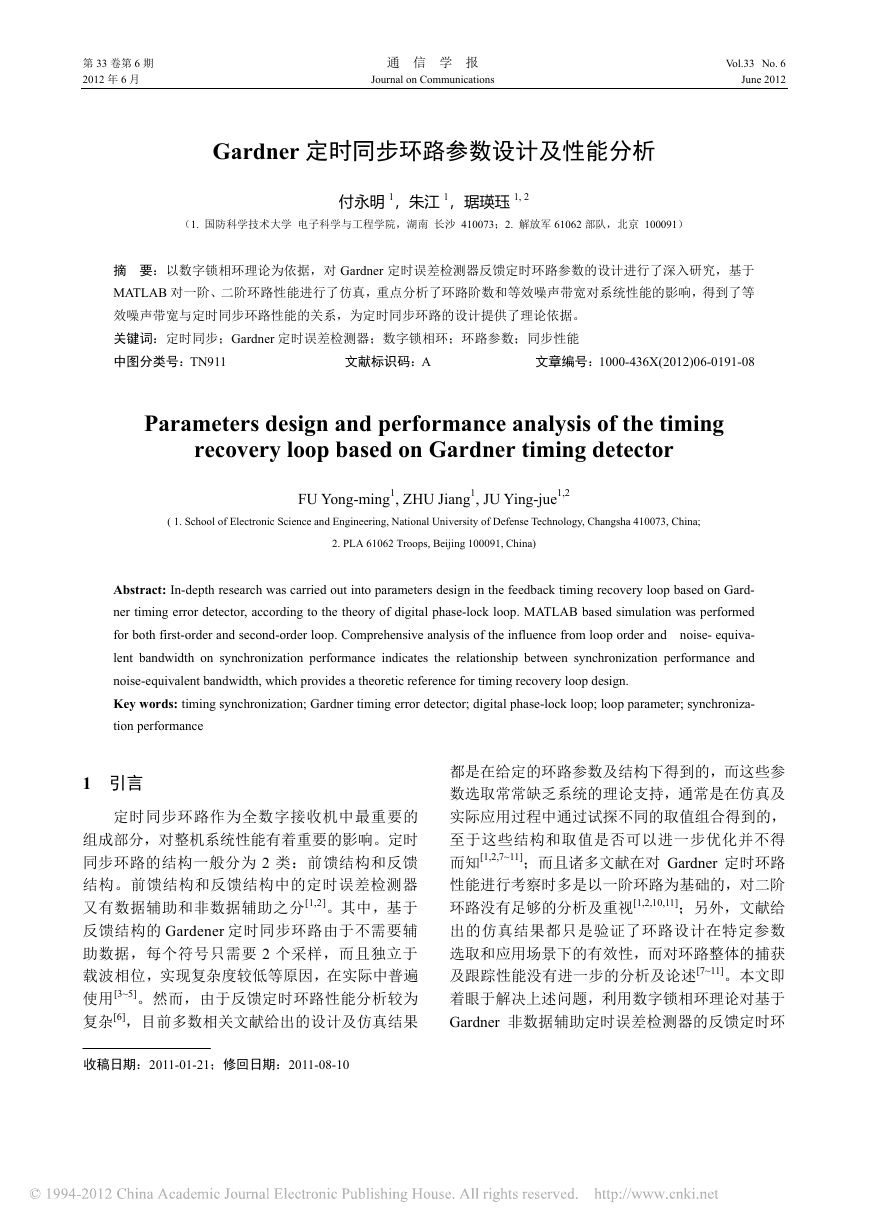

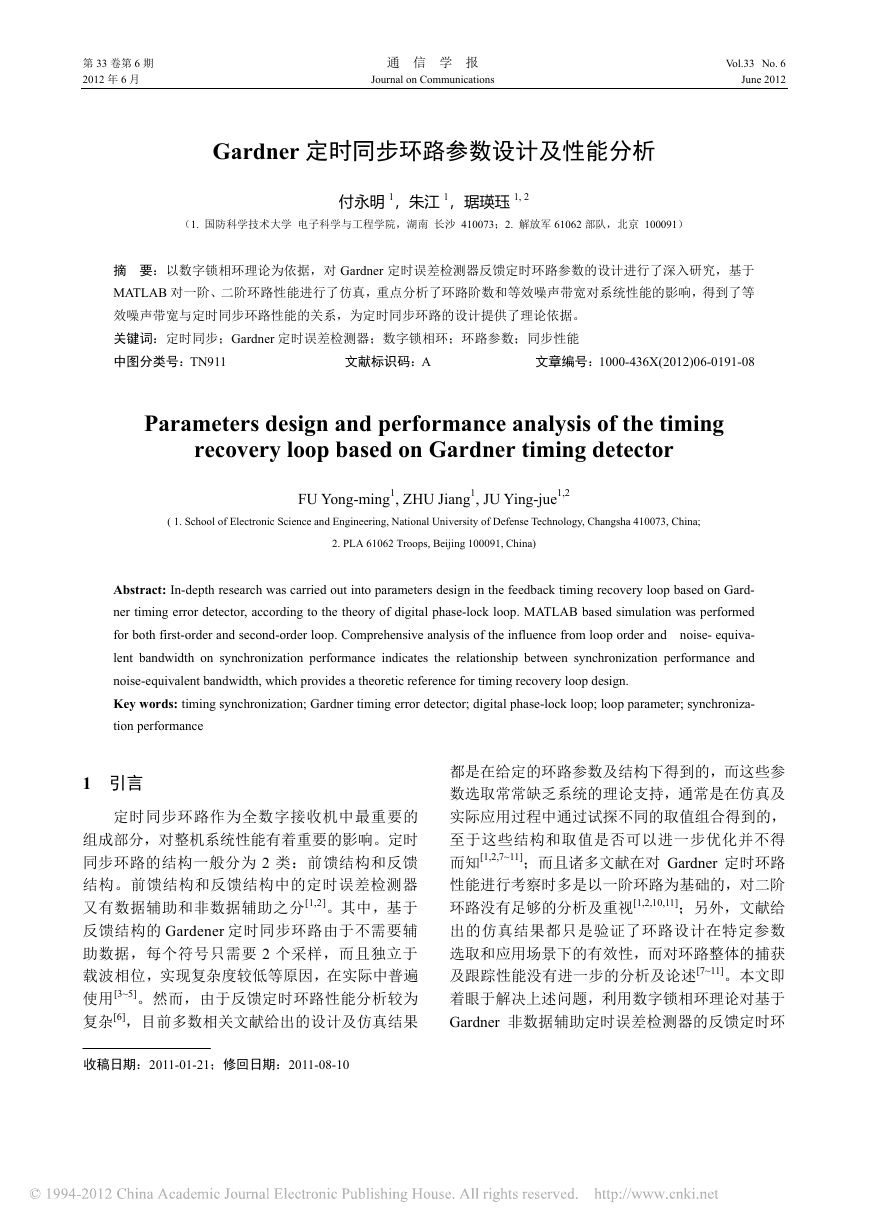

本文采用如图 1 所示的系统模型[10](这里只关

注定时环路部分,其他部分认为是理想的)。假设

接收信号的等效低通形式如下[12]:

S

C

2

sin

2

2

π 1

4

sin 2π

(5)

r t

( )

i

c g t

(

i

T

iT

)

w t

( )

(1)

其中,{ci}为发送符号序列,对于 MPSK,有 ci =ejα,α=

0,2π/M,…2π(M−1)/M,对于 MQAM,有 ci=a+jb, a,

b=±1,±3,…±(M−1);τ 为路径延时,也即需要同步

的参量,这里设τ∈[−T/2,T/2];gT(t)为发送端成型

滤波器,这里选根升余弦滤波器;w(t)为复高斯过

程。

经过匹配滤波器后,

y t

( )

i

c h t

i

iT

n t

( )

(2)

其中,

对于一个定时误差检测器,首先需要确定其误

差检测灵敏度 kd,因为 kd 作为环路增益的一部

分,是后续环路参数计算的先决条件。kd 一般取

误差检测器的 S 曲线在零定时误差附近的斜率[6],

即有:

k

d

S

d ( )

d

0

sin

π

2

C

2

2

2

4

1

C

2

E

E

1

c

k

2

, MQAM

c c

k

k

2

2

M

3

1 , MPSK

由以上关系可以看出,Gardner 定时误差检测

器具有正弦形状的 S 曲线(亦可由下图仿真实例验

证),且对不同的调制方式,检测灵敏度 kd 是不同

的。对于 MPSK,不论 M 取什么值,kd 是一样的,

而对于 MQAM,kd 取值与 M 有关。另外 kd 取值与

成型脉冲的滚降系数是有关系的,随着的减

小,kd 会越来越减小,直到不能够对定时误差进行

有效的检测,也即,Gardner 误差检测器不适合在

(6)

(7)

其中,h(t)=gT(t)*gR(t)为升余弦滤波器;n(t)=w(t)*

gR(t)为窄带高斯过程。Ts 为本地固定采样频率,Ts/T

可能不为整数(即在接收端对发送端的符号速率是

不确知的)。

2.1 定时误差检测器

根据文献[3],Gardner 定时误差检测器可用式

(3)表示:

)

y t

(

)

y t

(

k

)

k

1

k

1/ 2

kT T

/ 2

ˆ

k

1

)

Err k

*

y t

( ) Re

(

{

= Re

y k

(

*

y

(

1ˆ

T

1)

k

y kT

ˆ }k

(3)

图 1 反馈定时环路系统模型

�

第 6 期

付永明等:Gardner 定时同步环路参数设计及性能分析

滚降系数取值较小的情况下应用。

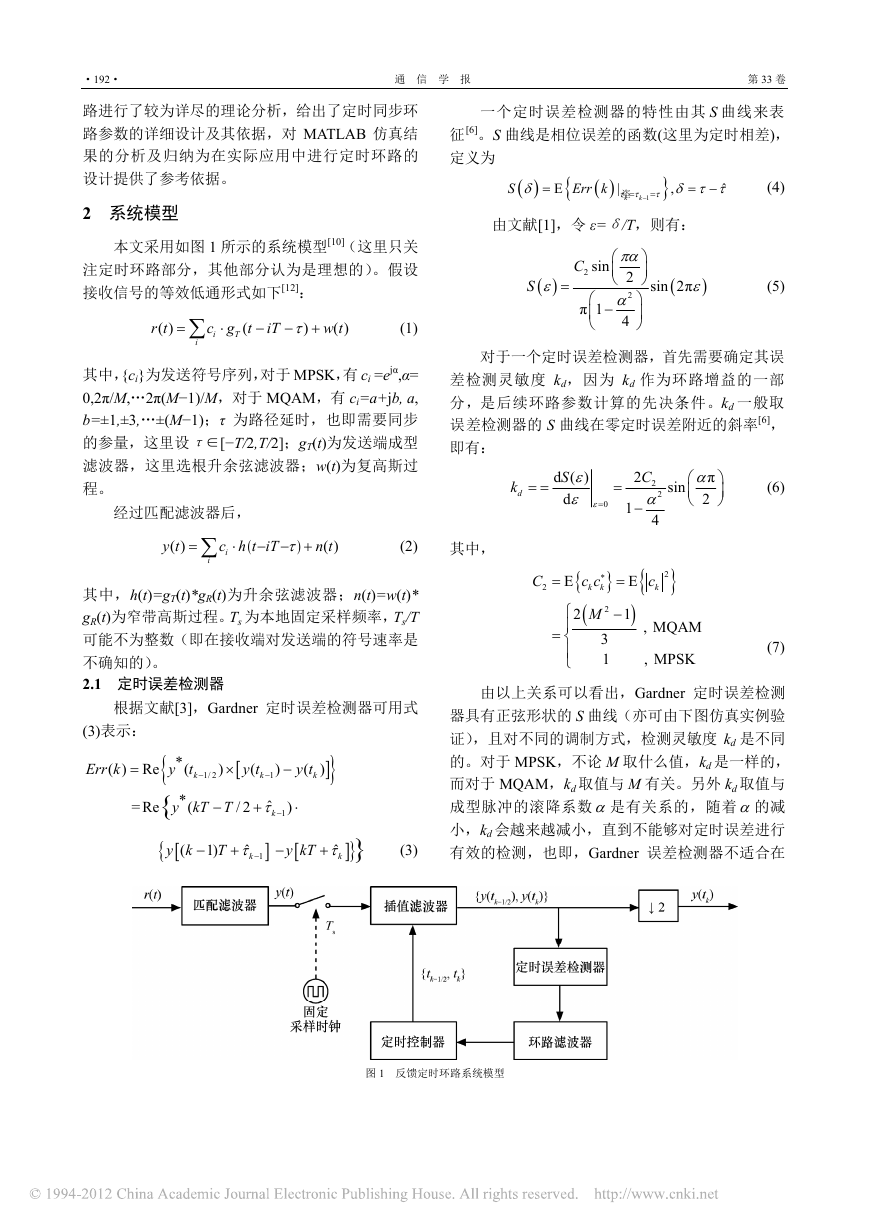

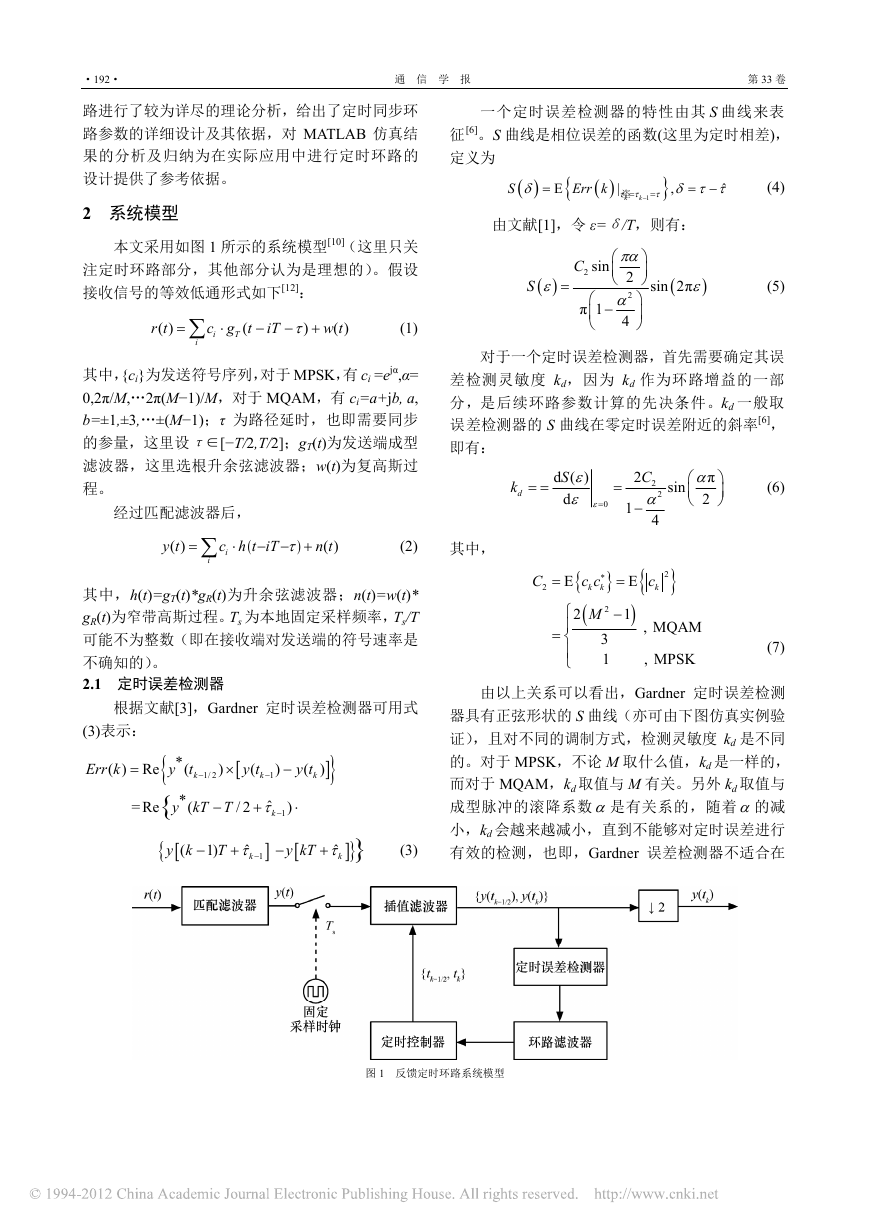

图 2 为使用数据长度为 10 000 个符号的

8PSK 信号在 α=0.5,SNR=30dB 情况下对 S 曲线

的数值仿真,仿真结果与之前的理论推导吻合很

好。

N z

ok z

1

z

1

1

其中,ko=1,推导由附录给出。

2.4 插值滤波器设计

·193·

(9)

为便于实现,插值滤波器一般采用多项式插值

方法[5],即:

C x m i

i

k

1

2

y kT

i

i

C x m

k

C x m

k

2

0

C x m

2

k

1

C x m

1

k

1

1

(10)

这里,完成插值所需要的辅助信息,都包含在定时

控制器所提供的插值位置参数中,其中,取最接近

Interp_Pos 的整数点为 mk,而系数 Ci 由 Interp_Pos

与 mk 的差μk 决定,Ci 与μk 的不同对应关系取决于

不同的插值方法。本设计采用分段抛物线插值,Ci

与μk 的对应关系式(11)给出:

C

C

C

C

1.5

0.5

0.5

0.5

0.5

2

0.5

2

0.5

2

0.5

2

2

1

0

1

1

(11)

图 2 8-PSK S-曲线(α= 0.5,SNR=30dB)

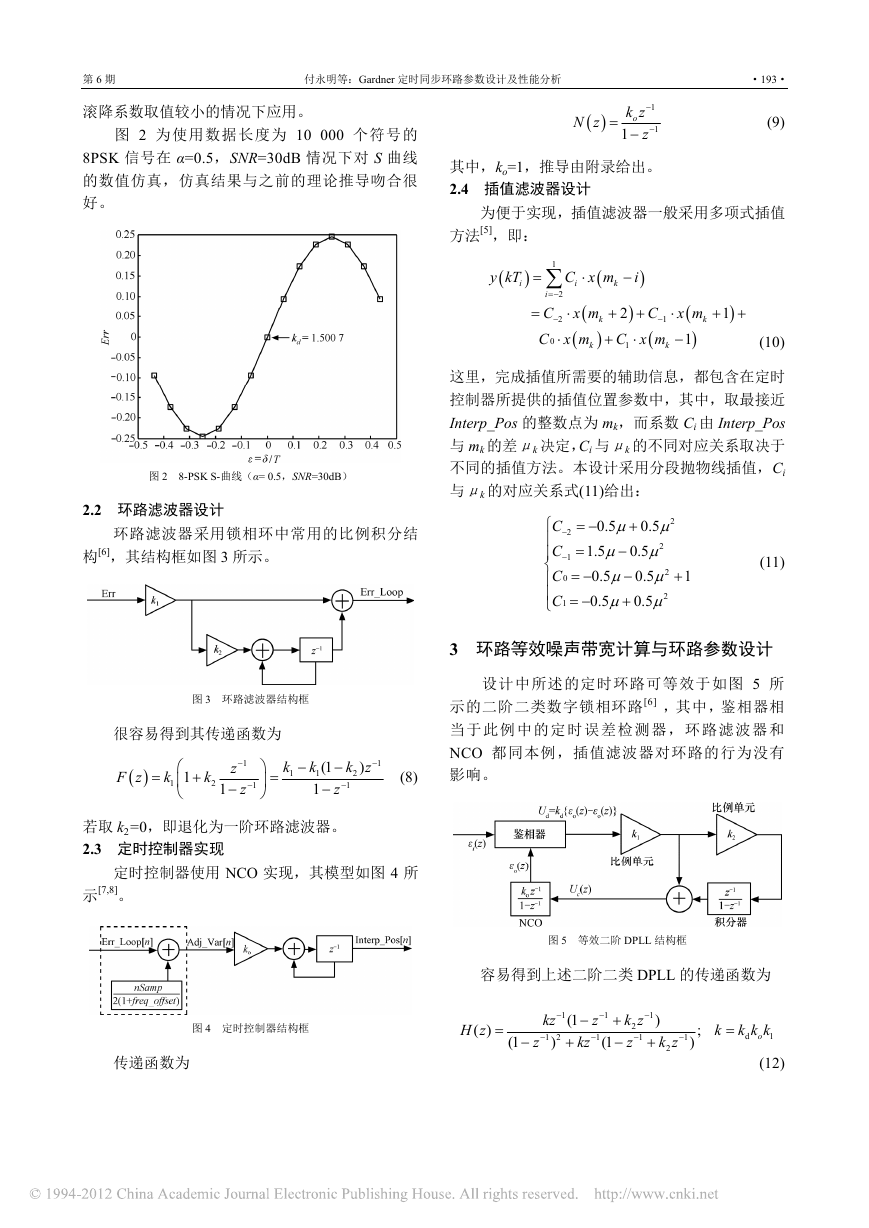

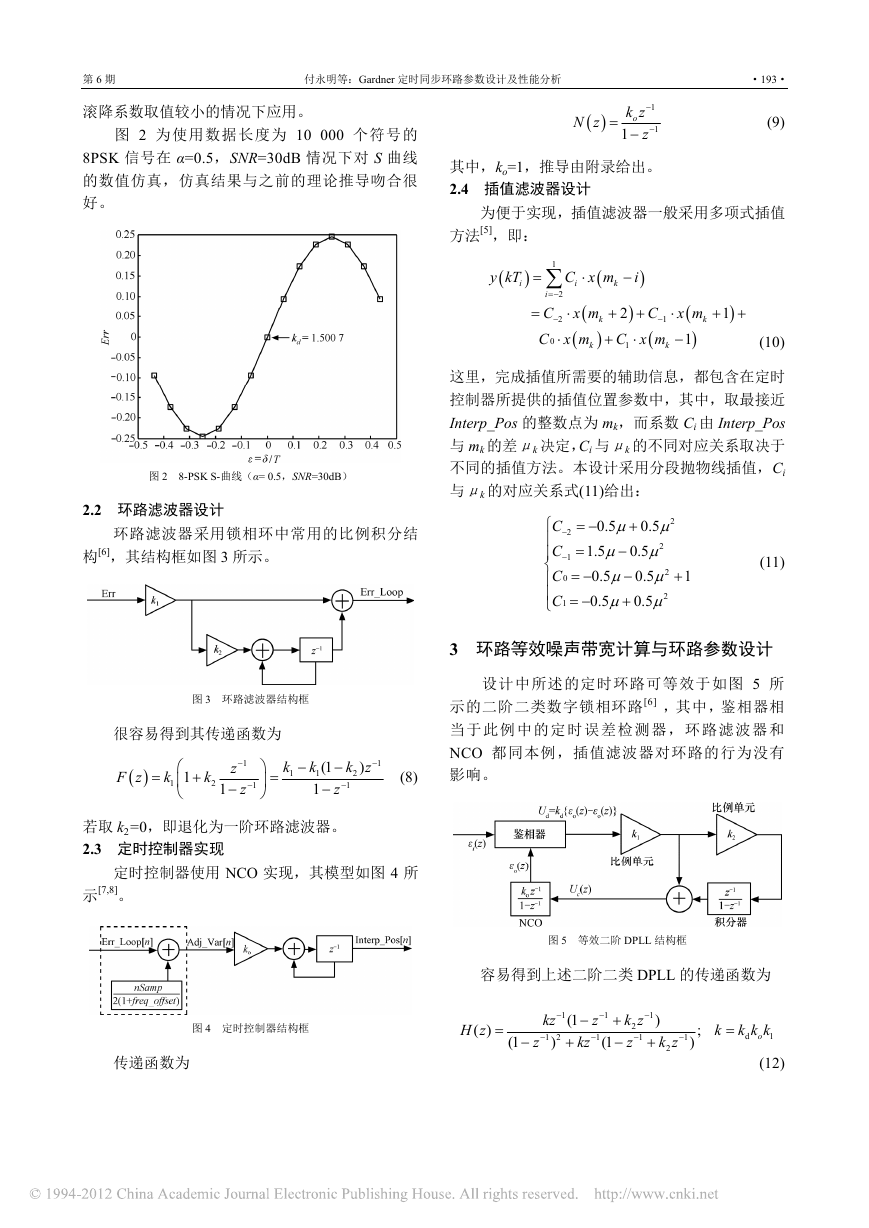

2.2 环路滤波器设计

环路滤波器采用锁相环中常用的比例积分结

构[6],其结构框如图 3 所示。

图 3 环路滤波器结构框

很容易得到其传递函数为

F z

k

1

1

k

z

1

z

1

2

1

k

1

1

k

1

1

(1

k z

)

2

z

1

(8)

若取 k2=0,即退化为一阶环路滤波器。

2.3 定时控制器实现

定时控制器使用 NCO 实现,其模型如图 4 所

示[7,8]。

3 环路等效噪声带宽计算与环路参数设计

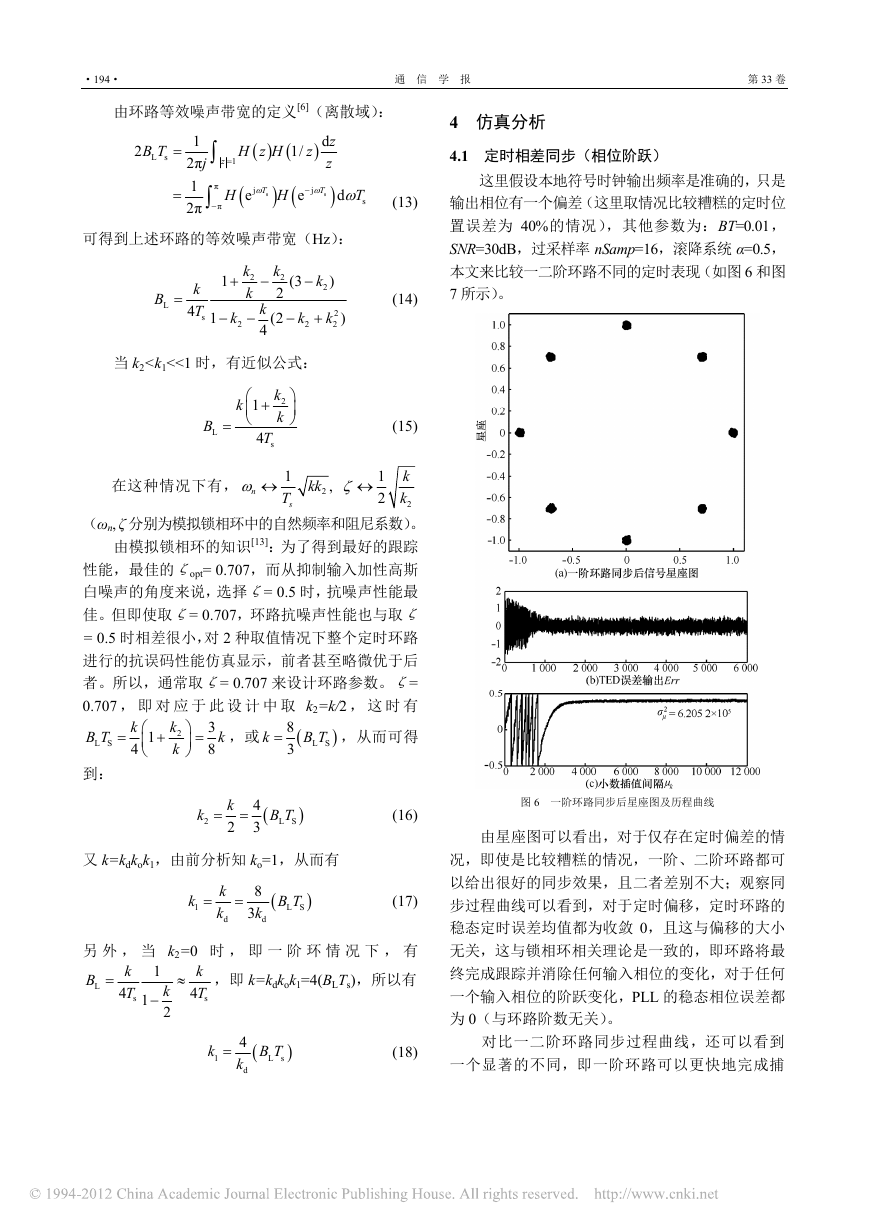

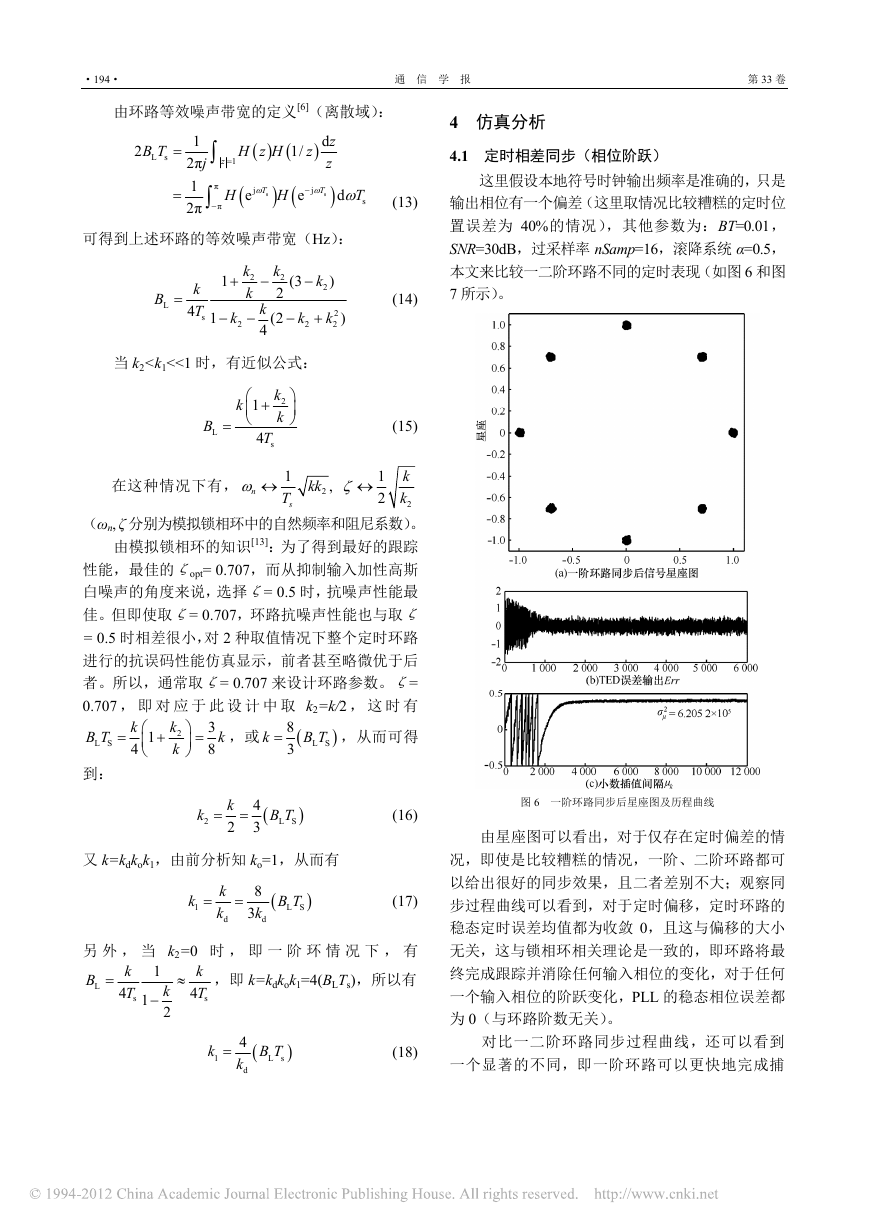

设计中所述的定时环路可等效于如图 5 所

示的二阶二类数字锁相环路[6] ,其中,鉴相器相

当于此例中 的定时误差 检测器,环 路滤波器和

NCO 都同本例,插值滤波器对环路的行为没有

影响。

图 5 等效二阶 DPLL 结构框

容易得到上述二阶二类 DPLL 的传递函数为

图 4 定时控制器结构框

传递函数为

H z

( )

(1

z

1

kz

)

1 2

(1

kz

z

1

1

(1

k z

2

z

1

1

)

k z

2

1

)

;

k

k k k

o

d

1

(12)

�

·194·

通 信 学 报

第 33 卷

由环路等效噪声带宽的定义[6](离散域):

2

B T

L s

1

j

2π

1

2π

π

π

H

e

T

j

s

H

e

T

T

j

s

s

d

(13)

H z H

1/

z

z

1

z

d

z

可得到上述环路的等效噪声带宽(Hz):

B

L

k

T

4 1

s

1

k

2

k

2

k

k

2

2

(2

k

4

(3

k

)

2

k

2

k

2

2

)

(14)

当 k2

第 6 期

付永明等:Gardner 定时同步环路参数设计及性能分析

·195·

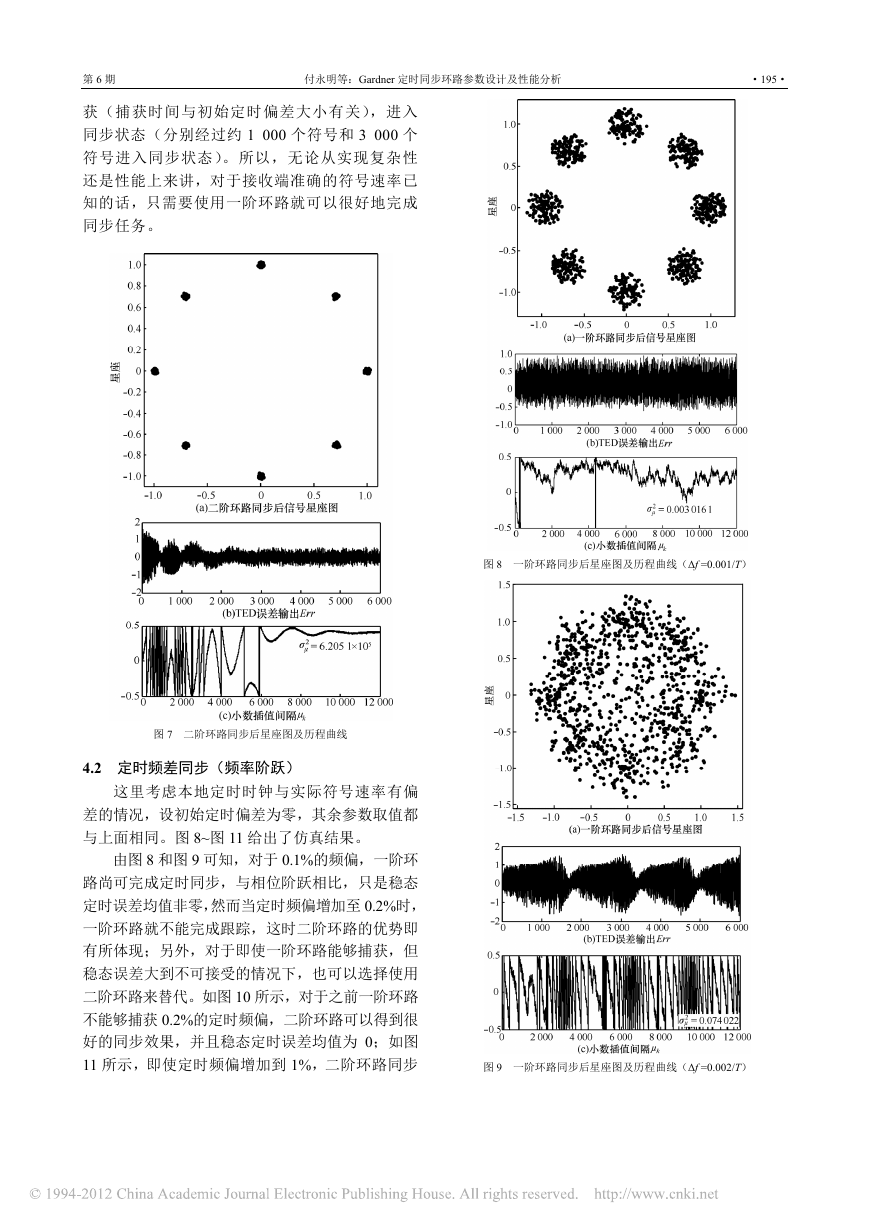

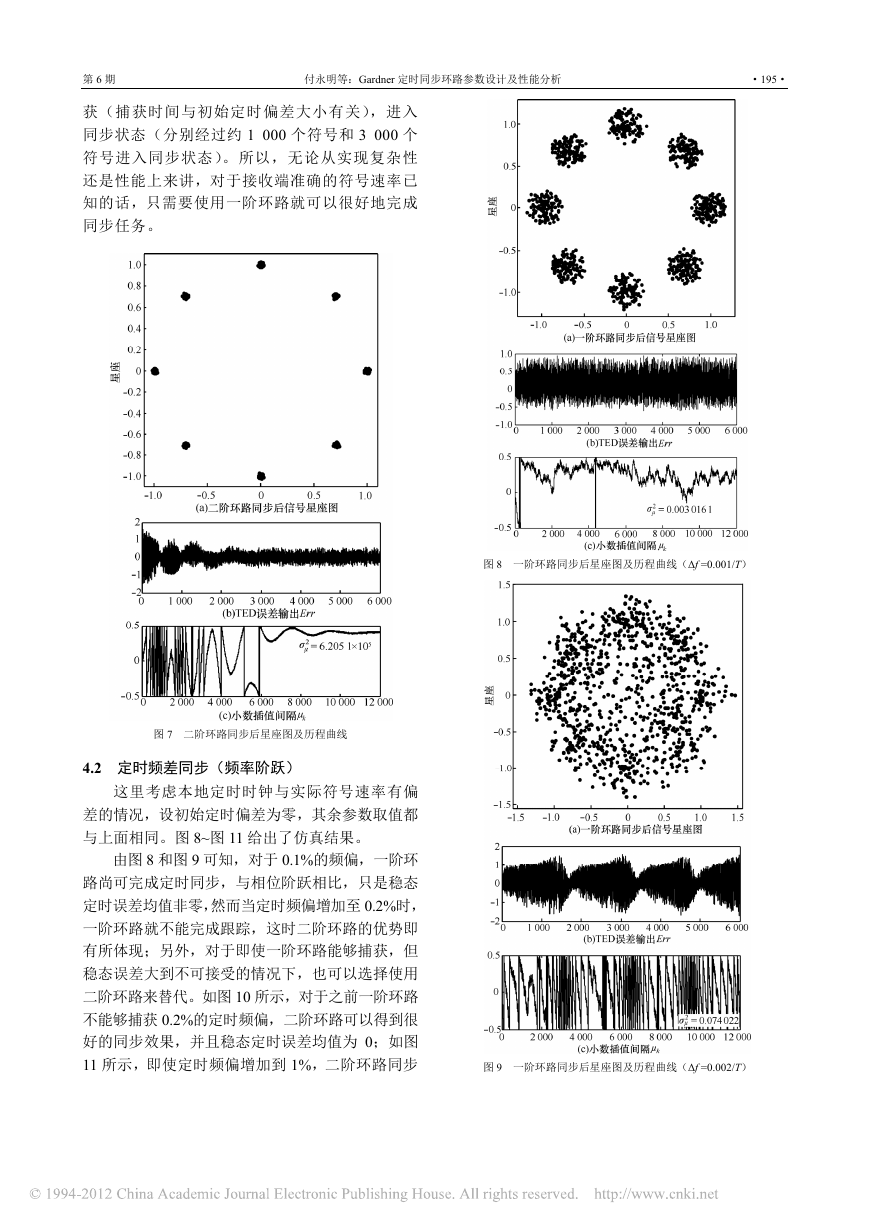

获(捕获时间与初始定时偏差大小有关),进入

同步状态(分别经过约 1 000 个符号和 3 000 个

符号进入同步状态)。所以,无论从实现复杂性

还是性能上来讲,对于接收端准确的符号速率已

知的话,只需要使用一阶环路就可以很好地完成

同步任务。

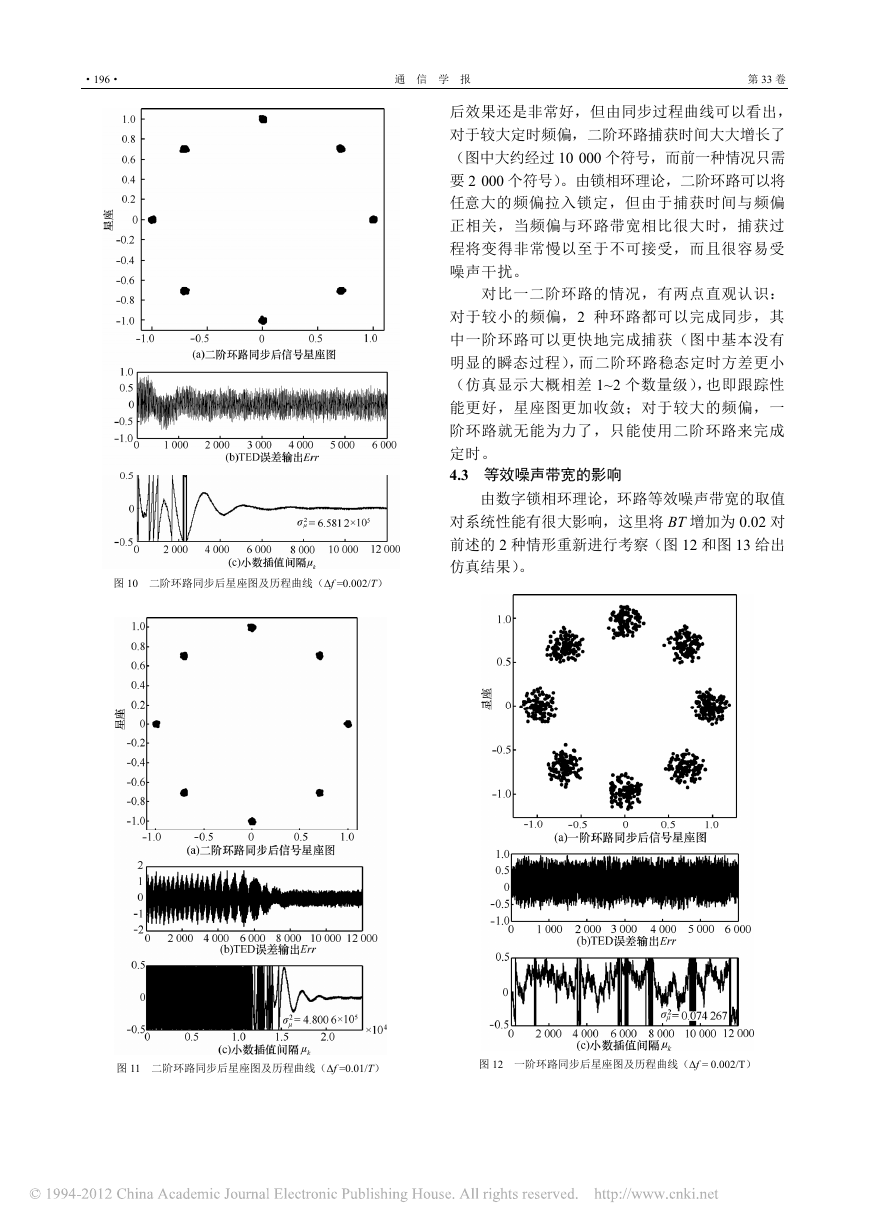

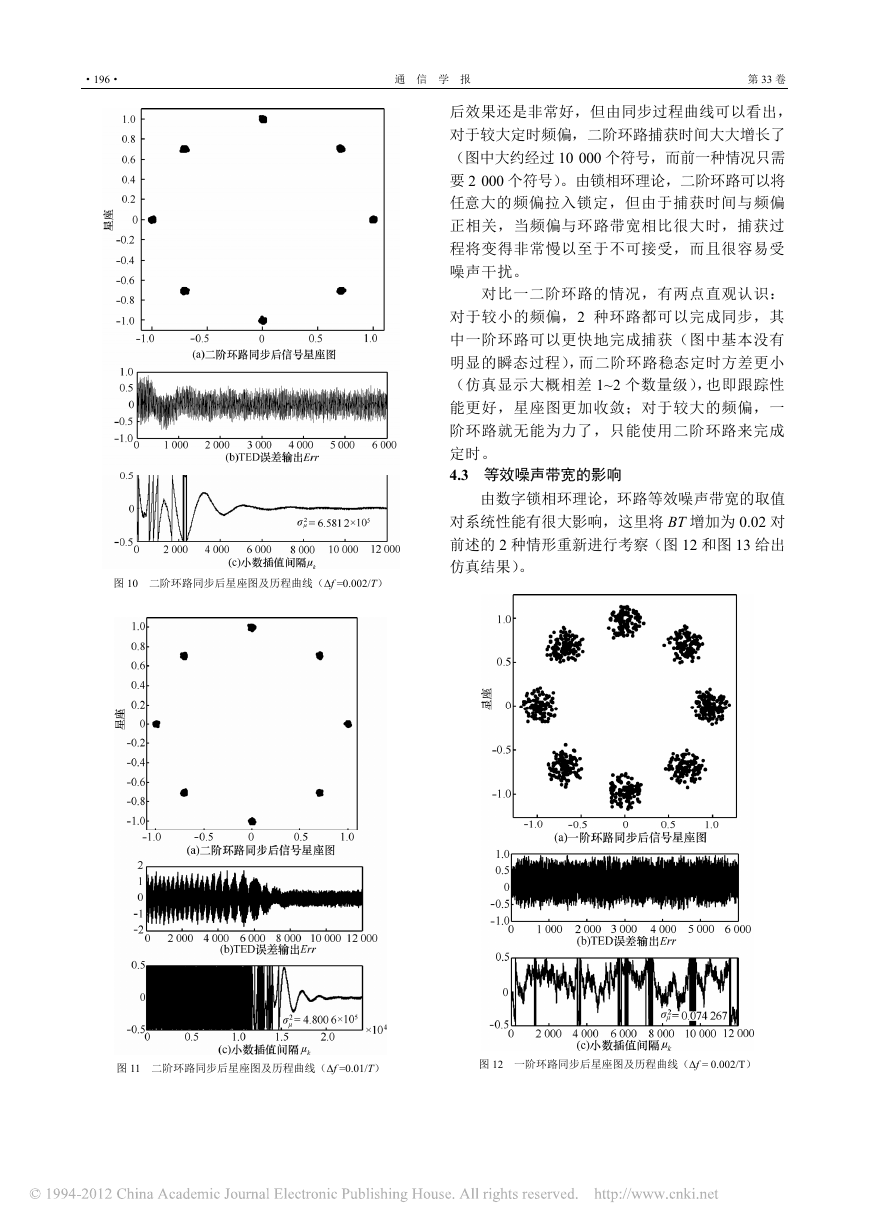

图 8 一阶环路同步后星座图及历程曲线(Δf =0.001/T)

图 7 二阶环路同步后星座图及历程曲线

4.2 定时频差同步(频率阶跃)

这里考虑本地定时时钟与实际符号速率有偏

差的情况,设初始定时偏差为零,其余参数取值都

与上面相同。图 8~图 11 给出了仿真结果。

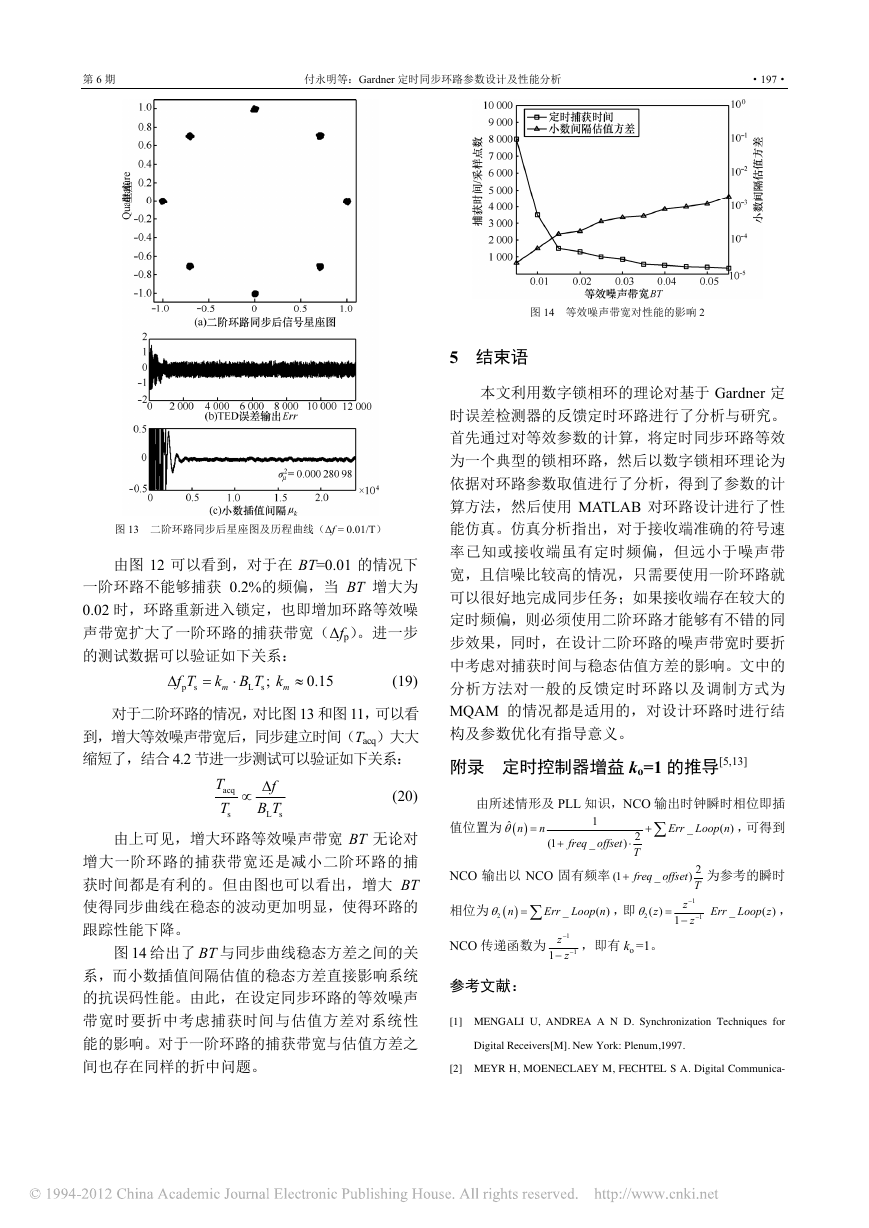

由图 8 和图 9 可知,对于 0.1%的频偏,一阶环

路尚可完成定时同步,与相位阶跃相比,只是稳态

定时误差均值非零,然而当定时频偏增加至 0.2%时,

一阶环路就不能完成跟踪,这时二阶环路的优势即

有所体现;另外,对于即使一阶环路能够捕获,但

稳态误差大到不可接受的情况下,也可以选择使用

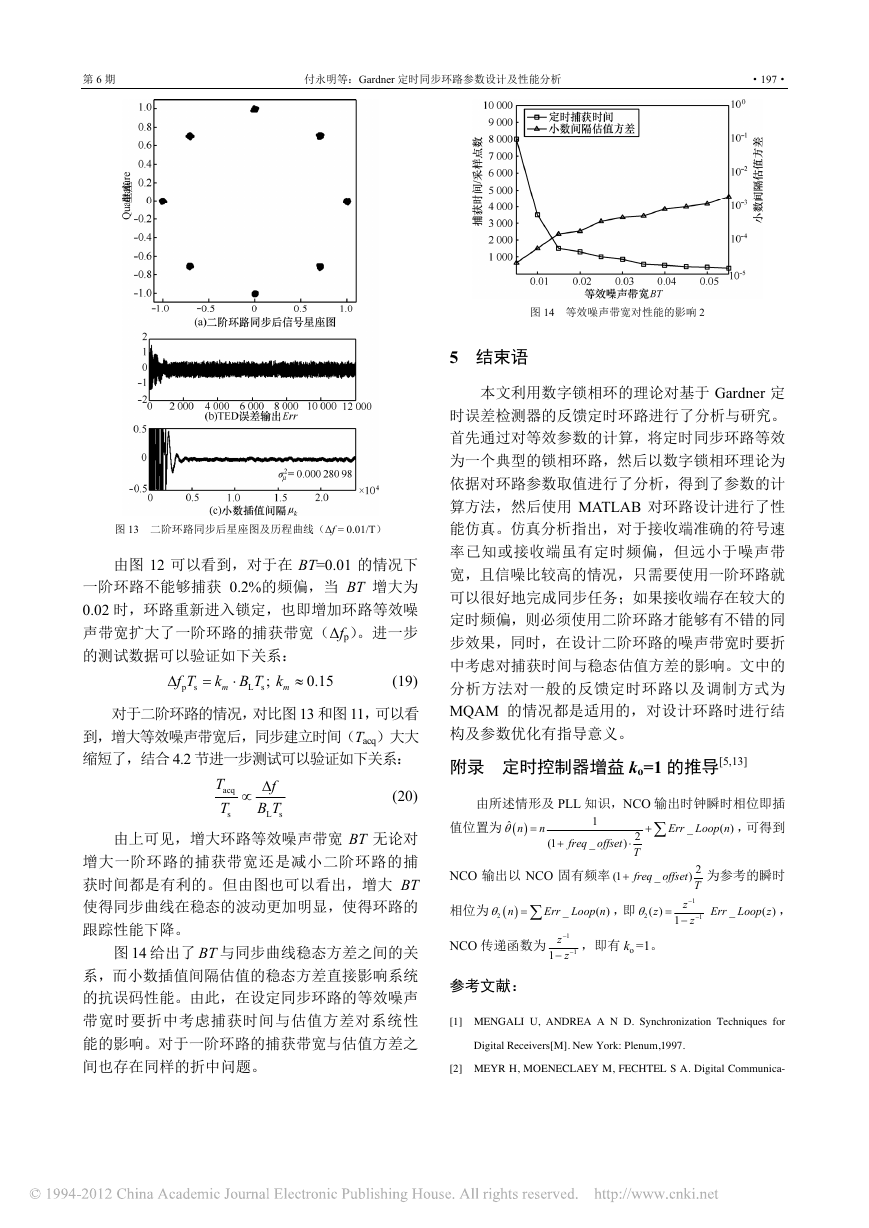

二阶环路来替代。如图 10 所示,对于之前一阶环路

不能够捕获 0.2%的定时频偏,二阶环路可以得到很

好的同步效果,并且稳态定时误差均值为 0;如图

11 所示,即使定时频偏增加到 1%,二阶环路同步

图 9 一阶环路同步后星座图及历程曲线(Δf =0.002/T)

�

·196·

通 信 学 报

第 33 卷

后效果还是非常好,但由同步过程曲线可以看出,

对于较大定时频偏,二阶环路捕获时间大大增长了

(图中大约经过 10 000 个符号,而前一种情况只需

要 2 000 个符号)。由锁相环理论,二阶环路可以将

任意大的频偏拉入锁定,但由于捕获时间与频偏

正相关,当频偏与环路带宽相比很大时,捕获过

程将变得非常慢以至于不可接受,而且很容易受

噪声干扰。

对比一二阶环路的情况,有两点直观认识:

对于较小的频偏,2 种环路都可以完成同步,其

中一阶环路可以更快地完成捕获(图中基本没有

明显的瞬态过程),而二阶环路稳态定时方差更小

(仿真显示大概相差 1~2 个数量级),也即跟踪性

能更好,星座图更加收敛;对于较大的频偏,一

阶环路就无能为力了,只能使用二阶环路来完成

定时。

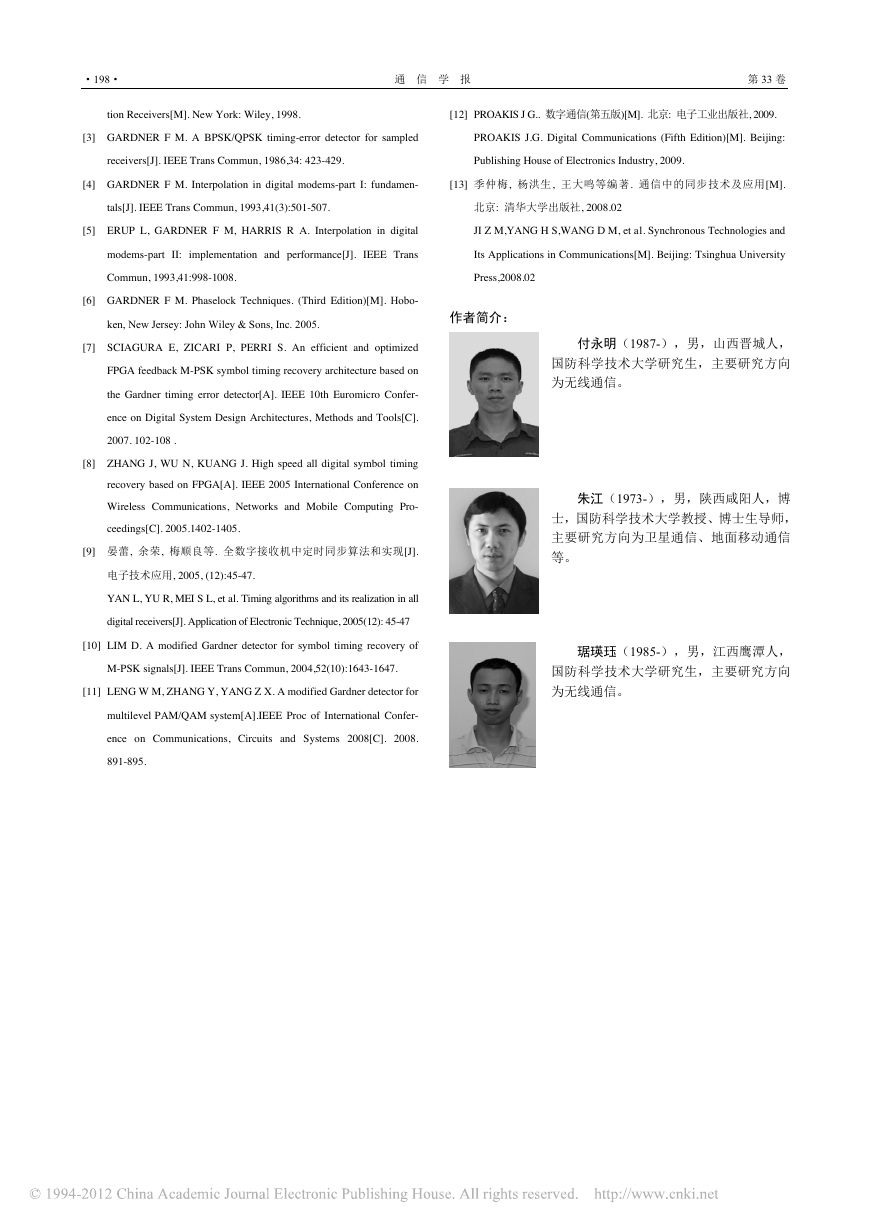

4.3 等效噪声带宽的影响

由数字锁相环理论,环路等效噪声带宽的取值

对系统性能有很大影响,这里将 BT 增加为 0.02 对

前述的 2 种情形重新进行考察(图 12 和图 13 给出

仿真结果)。

图 10 二阶环路同步后星座图及历程曲线(Δf =0.002/T)

图 11 二阶环路同步后星座图及历程曲线(Δf =0.01/T)

图 12 一阶环路同步后星座图及历程曲线(Δf = 0.002/T)

�

第 6 期

付永明等:Gardner 定时同步环路参数设计及性能分析

·197·

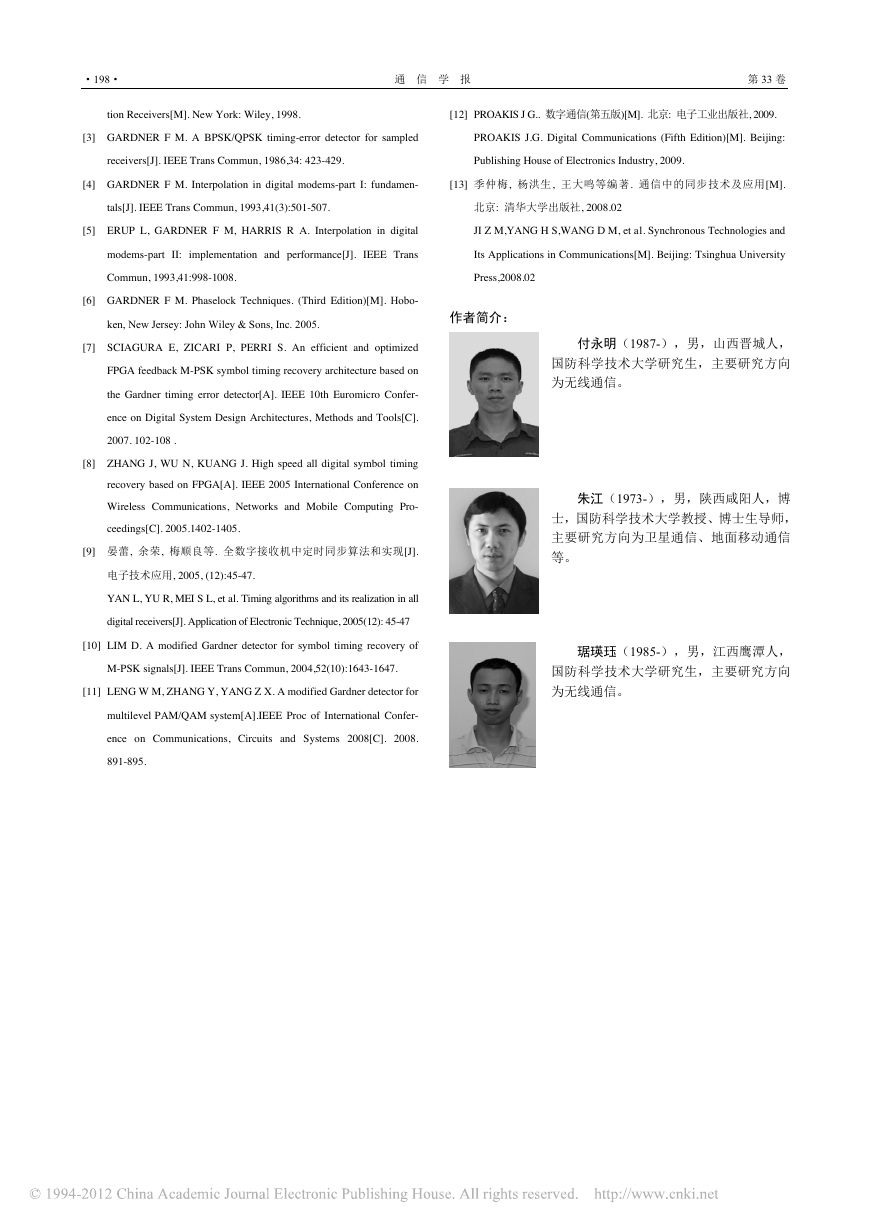

图 14 等效噪声带宽对性能的影响 2

5 结束语

本文利用数字锁相环的理论对基于 Gardner 定

时误差检测器的反馈定时环路进行了分析与研究。

首先通过对等效参数的计算,将定时同步环路等效

为一个典型的锁相环路,然后以数字锁相环理论为

依据对环路参数取值进行了分析,得到了参数的计

算方法,然后使用 MATLAB 对环路设计进行了性

能仿真。仿真分析指出,对于接收端准确的符号速

率已知或接收端虽有定时频偏,但远小于噪声带

宽,且信噪比较高的情况,只需要使用一阶环路就

可以很好地完成同步任务;如果接收端存在较大的

定时频偏,则必须使用二阶环路才能够有不错的同

步效果,同时,在设计二阶环路的噪声带宽时要折

中考虑对捕获时间与稳态估值方差的影响。文中的

分析方法对一般的反馈定时环路以及调制方式为

MQAM 的情况都是适用的,对设计环路时进行结

构及参数优化有指导意义。

附录 定时控制器增益 ko=1 的推导[5,13]

由所述情形及 PLL 知识,NCO 输出时钟瞬时相位即插

ˆ

值位置为

n

n

1

_

freq offset

(1

)

2

T

Err Loop n

( )

_

,可得到

NCO 输出以 NCO 固有频率

(1

freq offset

_

相位为

n

2

Err Loop n

( )

_

,即

2

z

( )

z

1

)

2

T

1

z

1

为参考的瞬时

Err Loop z ,

( )

_

NCO 传递函数为

z

1

z

1

1

,即有 ko =1。

参考文献:

[1] MENGALI U, ANDREA A N D. Synchronization Techniques for

Digital Receivers[M]. New York: Plenum,1997.

[2] MEYR H, MOENECLAEY M, FECHTEL S A. Digital Communica-

图 13 二阶环路同步后星座图及历程曲线(Δf = 0.01/T)

由图 12 可以看到,对于在 BT=0.01 的情况下

一阶环路不能够捕获 0.2%的频偏,当 BT 增大为

0.02 时,环路重新进入锁定,也即增加环路等效噪

声带宽扩大了一阶环路的捕获带宽(Δfp)。进一步

的测试数据可以验证如下关系:

k B T k

L s;

m

f T

p s

0.15

(19)

m

对于二阶环路的情况,对比图 13 和图 11,可以看

到,增大等效噪声带宽后,同步建立时间(Tacq)大大

缩短了,结合 4.2 节进一步测试可以验证如下关系:

T

acq

T

s

f

B T

L s

(20)

由上可见,增大环路等效噪声带宽 BT 无论对

增大一阶环路的捕获带宽还是减小二阶环路的捕

获时间都是有利的。但由图也可以看出,增大 BT

使得同步曲线在稳态的波动更加明显,使得环路的

跟踪性能下降。

图 14 给出了 BT 与同步曲线稳态方差之间的关

系,而小数插值间隔估值的稳态方差直接影响系统

的抗误码性能。由此,在设定同步环路的等效噪声

带宽时要折中考虑捕获时间与估值方差对系统性

能的影响。对于一阶环路的捕获带宽与估值方差之

间也存在同样的折中问题。

�

·198·

通 信 学 报

第 33 卷

tion Receivers[M]. New York: Wiley, 1998.

[12] PROAKIS J G.. 数字通信(第五版)[M]. 北京: 电子工业出版社, 2009.

[3] GARDNER F M. A BPSK/QPSK timing-error detector for sampled

PROAKIS J.G. Digital Communications (Fifth Edition)[M]. Beijing:

receivers[J]. IEEE Trans Commun, 1986,34: 423-429.

Publishing House of Electronics Industry, 2009.

[4] GARDNER F M. Interpolation in digital modems-part I: fundamen-

[13] 季仲梅, 杨洪生, 王大鸣等编著. 通信中的同步技术及应用[M].

tals[J]. IEEE Trans Commun, 1993,41(3):501-507.

北京: 清华大学出版社, 2008.02

[5] ERUP L, GARDNER F M, HARRIS R A. Interpolation in digital

JI Z M,YANG H S,WANG D M, et al. Synchronous Technologies and

modems-part II: implementation and performance[J]. IEEE Trans

Its Applications in Communications[M]. Beijing: Tsinghua University

Commun, 1993,41:998-1008.

[6] GARDNER F M. Phaselock Techniques. (Third Edition)[M]. Hobo-

ken, New Jersey: John Wiley & Sons, Inc. 2005.

[7] SCIAGURA E, ZICARI P, PERRI S. An efficient and optimized

FPGA feedback M-PSK symbol timing recovery architecture based on

the Gardner timing error detector[A]. IEEE 10th Euromicro Confer-

ence on Digital System Design Architectures, Methods and Tools[C].

2007. 102-108 .

[8] ZHANG J, WU N, KUANG J. High speed all digital symbol timing

recovery based on FPGA[A]. IEEE 2005 International Conference on

Wireless Communications, Networks and Mobile Computing Pro-

ceedings[C]. 2005.1402-1405.

[9] 晏蕾, 余荣, 梅顺良等. 全数字接收机中定时同步算法和实现[J].

电子技术应用, 2005, (12):45-47.

YAN L, YU R, MEI S L, et al. Timing algorithms and its realization in all

digital receivers[J]. Application of Electronic Technique, 2005(12): 45-47

[10] LIM D. A modified Gardner detector for symbol timing recovery of

M-PSK signals[J]. IEEE Trans Commun, 2004,52(10):1643-1647.

[11] LENG W M, ZHANG Y, YANG Z X. A modified Gardner detector for

multilevel PAM/QAM system[A].IEEE Proc of International Confer-

ence on Communications, Circuits and Systems 2008[C]. 2008.

891-895.

Press,2008.02

作者简介:

付永明(1987-),男,山西晋城人,

国防科学技术大学研究生,主要研究方向

为无线通信。

朱江(1973-),男,陕西咸阳人,博

士,国防科学技术大学教授、博士生导师,

主要研究方向为卫星通信、地面移动通信

等。

琚瑛珏(1985-),男,江西鹰潭人,

国防科学技术大学研究生,主要研究方向

为无线通信。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc