CY7C68013A, CY7C68014A

CY7C68015A, CY7C68016A

EZ-USB FX2LP (TM) USB 微控制器

高速 USB 外设控制器

1. 特色 (CY7C68013A/14A/15A/16A)

■ USB 2.0 USB IF 高速性能且经过认证 (TID # 40460272)

■ 单芯片集成 USB 2.0 收发器、智能串行接口引擎 (SIE) 和增强

型 8051 微处理器

■ 适用性、外观和功能均与 FX2 兼容

❐ 引脚兼容

❐ 目标代码兼容

❐ 功能兼容 (FX2LP 是超集)

■ 超低功耗:ICC 在任何模式下都不超过 85 mA

❐ 适合总线和电池供电的应用

■ 软件:8051 代码运行介质:

❐ 内部 RAM,通过 USB 下载

❐ 内部 RAM,从 EEPROM 加载

❐ 外部存储设备 (128 引脚封装)

■ 16 K 字节片上代码 / 数据 RAM

■ 四个可编程的 BULK/INTERRUPT/ISOCHRONOUS 端点

❐ 缓冲区大小选项:两倍,三倍,四倍

■ 附加的可编程 (BULK/INTERRUPT) 64 位端点

■ 8 位或 16 位外部数据接口

■ 可生成智能介质标准错误校正码 ECC

■ 通用可编程接口 (General Programmable Interface, GPIF)

❐ 可与大多数并行接口直接连接

❐ 由可编程波形描述符和配置寄存器定义波形

❐ 支持多个 Ready (RDY) 输入和 Control (CTL) 输出

■ 符合行业标准的集成增强型 8051

❐ 48 MHz、 24 MHz 或 12 MHz CPU 操作

❐ 每个指令周期四个时钟

❐ 两个 USART

❐ 三个计数器 / 定时器

❐ 扩展的中断系统

❐ 两个数据指针

■ 3.3V 工作电压,容限输入为 5V

■ 向量化 USB 中断和 GPIF/FIFO 中断

■ 分离的 CONTROL 传输设置部分和数据部分数据缓冲

■ 集成 I2C 控制器,在 100 或 400 kHz 下运行

■ 集成的四个先进先出 (FIFO) 缓冲

❐ 集成胶合逻辑和 FIFO 有助于降低系统成本

❐ 与 16 位总线之间的自动转换

❐ 可主 - 从操作

❐ 使用外部时钟或异步选通脉冲

❐ 易于与 ASIC 和 DSP IC 相连的接口

■ 有商业和工业温度等级供选择 (除 VFBGA 外的所有封装)

Cypress Semiconductor Corporation

文件编号:001-50431 修订版 **

•

198 Champion Court

•

San Jose, CA 95134-1709

408-943-2600

修订时间 2008 年 12 月 11 日

•

[+] Feedback

�

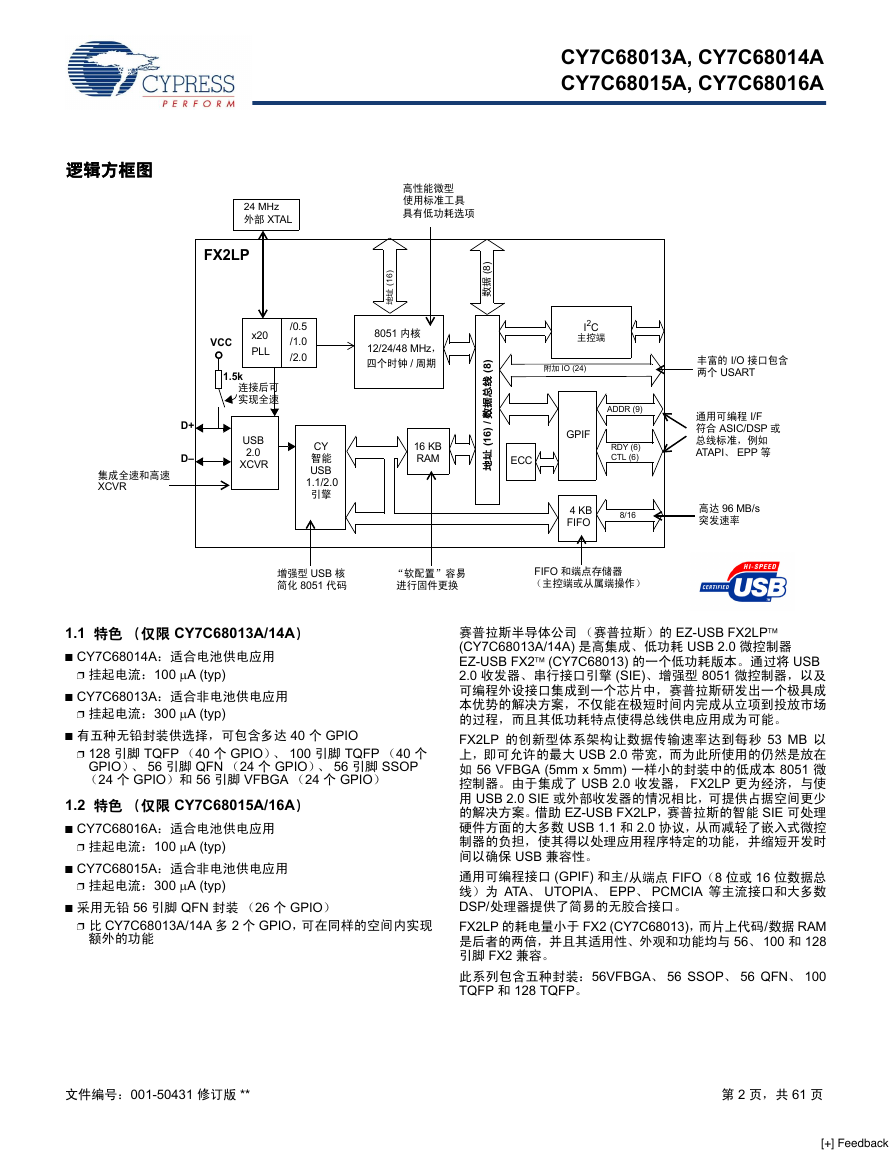

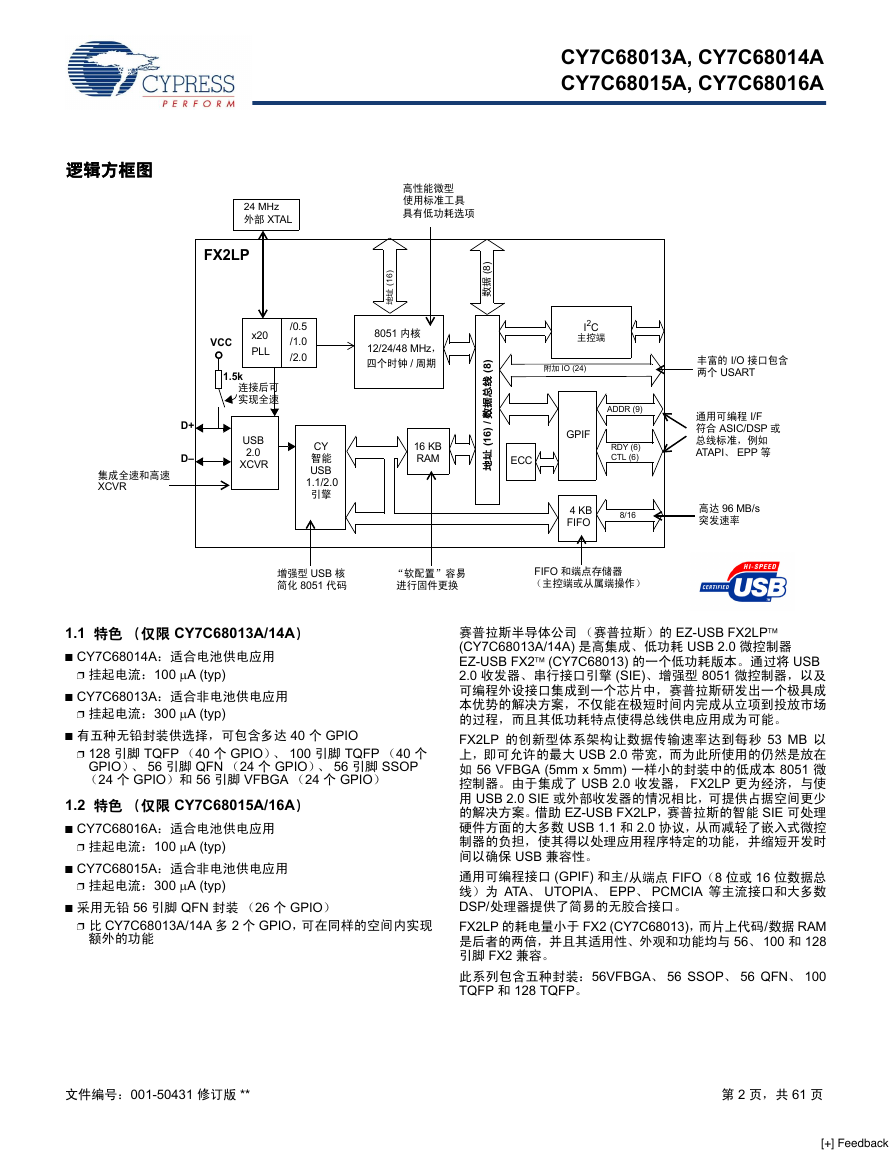

逻辑方框图

逻辑方框图

24 MHz

外部 XTAL

FX2LP

/0.5

/1.0

/2.0

VCC

x20

PLL

1.5k

连接后可

实现全速

高性能微型

使用标准工具

具有低功耗选项

)

6

1

(

址

地

8051 内核

12/24/48 MHz,

四个时钟 / 周期

D+

D–

USB

2.0

XCVR

集成全速和高速

XCVR

CY

智能

USB

1.1/2.0

引擎

16 KB

RAM

CY7C68013A, CY7C68014A

CY7C68015A, CY7C68016A

)

8

(

据

数

)

8

(

线

总

据

数

/

)

6

1

(

址

地

I2C

主控端

附加 IO (24)

GPIF

ADDR (9)

RDY (6)

CTL (6)

ECC

丰富的 I/O 接口包含

两个 USART

通用可编程 I/F

符合 ASIC/DSP 或

总线标准,例如

ATAPI、 EPP 等

4 KB

FIFO

8/16

高达 96 MB/s

突发速率

增强型 USB 核

简化 8051 代码

“软配置”容易

进行固件更换

FIFO 和端点存储器

(主控端或从属端操作)

1.1 特色 (仅限 CY7C68013A/14A)

■ CY7C68014A:适合电池供电应用

❐ 挂起电流:100 μA (typ)

■ CY7C68013A:适合非电池供电应用

❐ 挂起电流:300 μA (typ)

■ 有五种无铅封装供选择,可包含多达 40 个 GPIO

❐ 128 引脚 TQFP (40 个 GPIO)、 100 引脚 TQFP (40 个

GPIO)、 56 引脚 QFN (24 个 GPIO)、 56 引脚 SSOP

(24 个 GPIO)和 56 引脚 VFBGA (24 个 GPIO)

1.2 特色 (仅限 CY7C68015A/16A)

■ CY7C68016A:适合电池供电应用

❐ 挂起电流:100 μA (typ)

■ CY7C68015A:适合非电池供电应用

❐ 挂起电流:300 μA (typ)

■ 采用无铅 56 引脚 QFN 封装 (26 个 GPIO)

❐ 比 CY7C68013A/14A 多 2 个 GPIO,可在同样的空间内实现

额外的功能

赛普拉斯半导体公司 (赛普拉斯)的 EZ-USB FX2LP™

(CY7C68013A/14A) 是高集成、低功耗 USB 2.0 微控制器

EZ-USB FX2™ (CY7C68013) 的一个低功耗版本。通过将 USB

2.0 收发器、串行接口引擎 (SIE)、增强型 8051 微控制器,以及

可编程外设接口集成到一个芯片中,赛普拉斯研发出一个极具成

本优势的解决方案,不仅能在极短时间内完成从立项到投放市场

的过程,而且其低功耗特点使得总线供电应用成为可能。

FX2LP 的创新型体系架构让数据传输速率达到每秒 53 MB 以

上,即可允许的最大 USB 2.0 带宽,而为此所使用的仍然是放在

如 56 VFBGA (5mm x 5mm) 一样小的封装中的低成本 8051 微

控制器。由于集成了 USB 2.0 收发器, FX2LP 更为经济,与使

用 USB 2.0 SIE 或外部收发器的情况相比,可提供占据空间更少

的解决方案。借助 EZ-USB FX2LP,赛普拉斯的智能 SIE 可处理

硬件方面的大多数 USB 1.1 和 2.0 协议,从而减轻了嵌入式微控

制器的负担,使其得以处理应用程序特定的功能,并缩短开发时

间以确保 USB 兼容性。

通用可编程接口 (GPIF) 和主 / 从端点 FIFO(8 位或 16 位数据总

线)为 ATA、 UTOPIA、 EPP、 PCMCIA 等主流接口和大多数

DSP/ 处理器提供了简易的无胶合接口。

FX2LP 的耗电量小于 FX2 (CY7C68013),而片上代码 / 数据 RAM

是后者的两倍,并且其适用性、外观和功能均与 56、100 和 128

引脚 FX2 兼容。

此系列包含五种封装:56VFBGA、 56 SSOP、 56 QFN、 100

TQFP 和 128 TQFP。

文件编号:001-50431 修订版 **

第 2 页,共 61 页

[+] Feedback

�

2. 应用

■ 便携式录像机

■ MPEG/TV 转换

■ DSL 调制解调器

■ ATA 接口

■ 存储器卡读取器

■ 旧式转换设备

■ 照相机

■ 扫描仪

■ 家用 PNA

■ 无线 LAN

■ MP3 播放器

■ 网络设备

赛普拉斯网站的“Reference Designs”(参考设计)部分为 USB2.0

的典型应用提供了附加工具。每个参考设计都包含固件的源代码和

目标代码、原理图以及文档。有关详细信息,请访问赛普拉斯网站。

3. 功能概述

3.1 USB 信号传输速度

FX2LP 按照 2000 年 4 月 27 日发布的 《USB 规范修订版 2.0》

中定义的三种速率中的两种运行:

■ 全速,信号传输比特率为 12 Mbps

■ 高速,信号传输比特率为 480 Mbps

FX2LP 不支持 1.5 Mbps 的低速信号发射模式。

3.2 8051 微处理器

FX2LP 系列中内嵌的 8051 微处理器具有 256 字节的寄存器

RAM、扩展的中断系统、三个定时器/计数器和两个 USART。

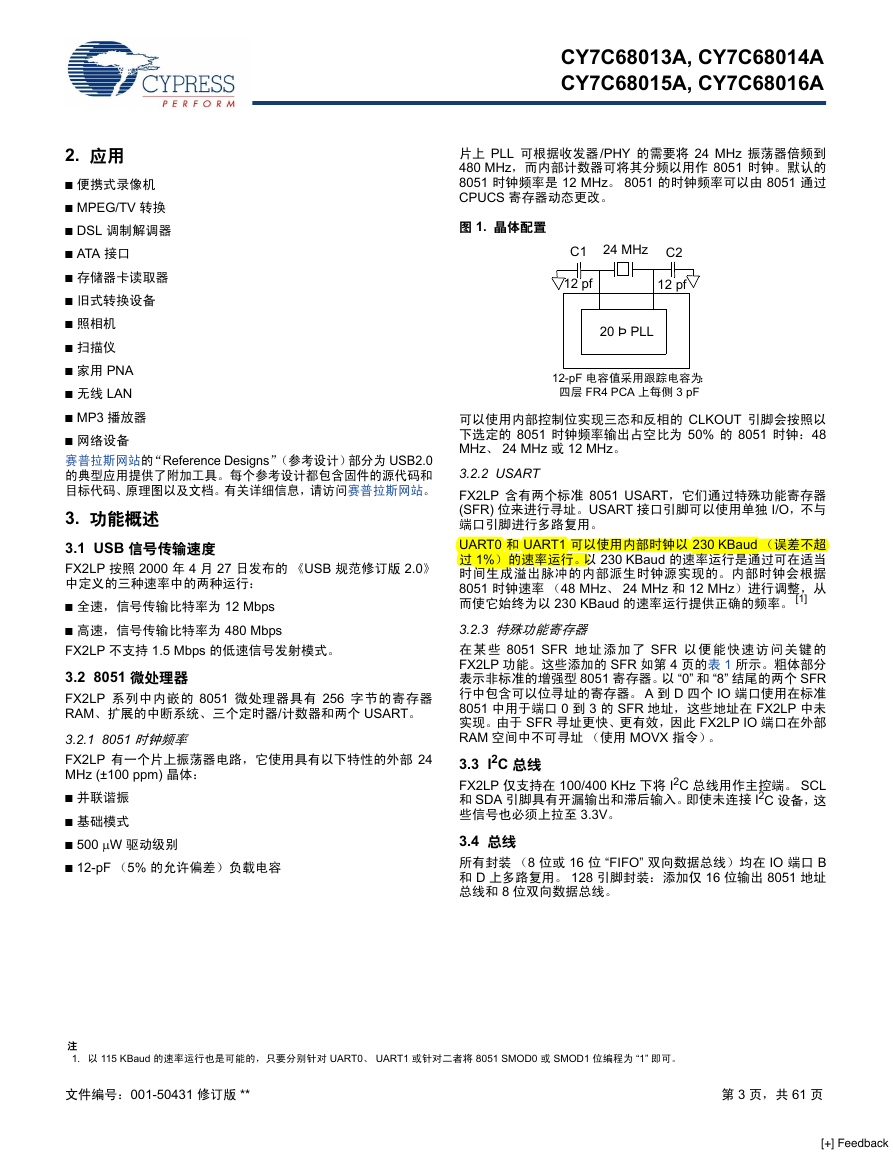

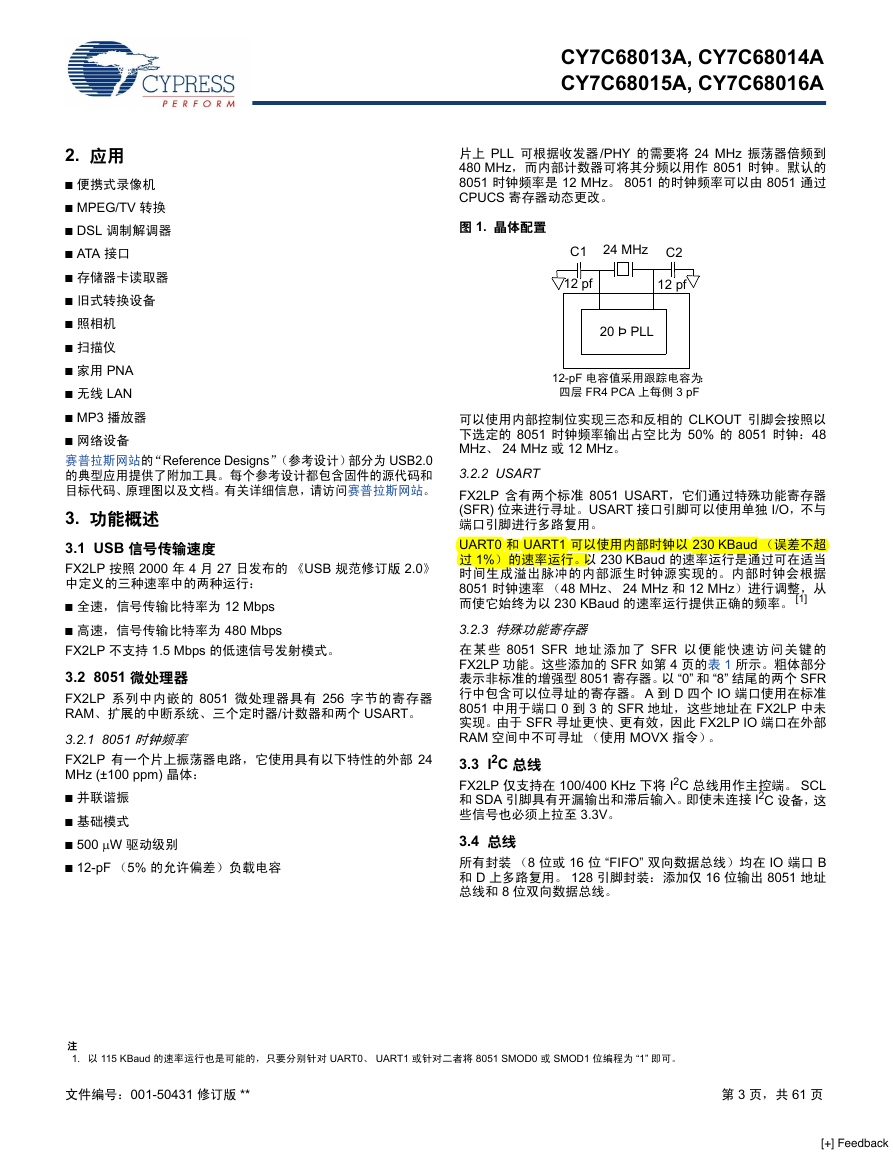

3.2.1 8051 时钟频率

FX2LP 有一个片上振荡器电路,它使用具有以下特性的外部 24

MHz (±100 ppm) 晶体:

■ 并联谐振

■ 基础模式

■ 500 μW 驱动级别

■ 12-pF (5% 的允许偏差)负载电容

CY7C68013A, CY7C68014A

CY7C68015A, CY7C68016A

片上 PLL 可根据收发器 /PHY 的需要将 24 MHz 振荡器倍频到

480 MHz,而内部计数器可将其分频以用作 8051 时钟。默认的

8051 时钟频率是 12 MHz。 8051 的时钟频率可以由 8051 通过

CPUCS 寄存器动态更改。

图 1. 晶体配置

C1

24 MHz

C2

12 pf

12 pf

20 Þ PLL

12-pF 电容值采用跟踪电容为:

四层 FR4 PCA 上每侧 3 pF

可以使用内部控制位实现三态和反相的 CLKOUT 引脚会按照以

下选定的 8051 时钟频率输出占空比为 50% 的 8051 时钟:48

MHz、 24 MHz 或 12 MHz。

3.2.2 USART

FX2LP 含有两个标准 8051 USART,它们通过特殊功能寄存器

(SFR) 位来进行寻址。USART 接口引脚可以使用单独 I/O,不与

端口引脚进行多路复用。

UART0 和 UART1 可以使用内部时钟以 230 KBaud (误差不超

过 1%) 的速率运行。以 230 KBaud 的速率运行是通过可在适当

时间生成溢出脉冲的内部派生时钟源实现的。内部时钟会根据

8051 时钟速率 (48 MHz、 24 MHz 和 12 MHz)进行调整,从

而使它始终为以 230 KBaud 的速率运行提供正确的频率。 [1]

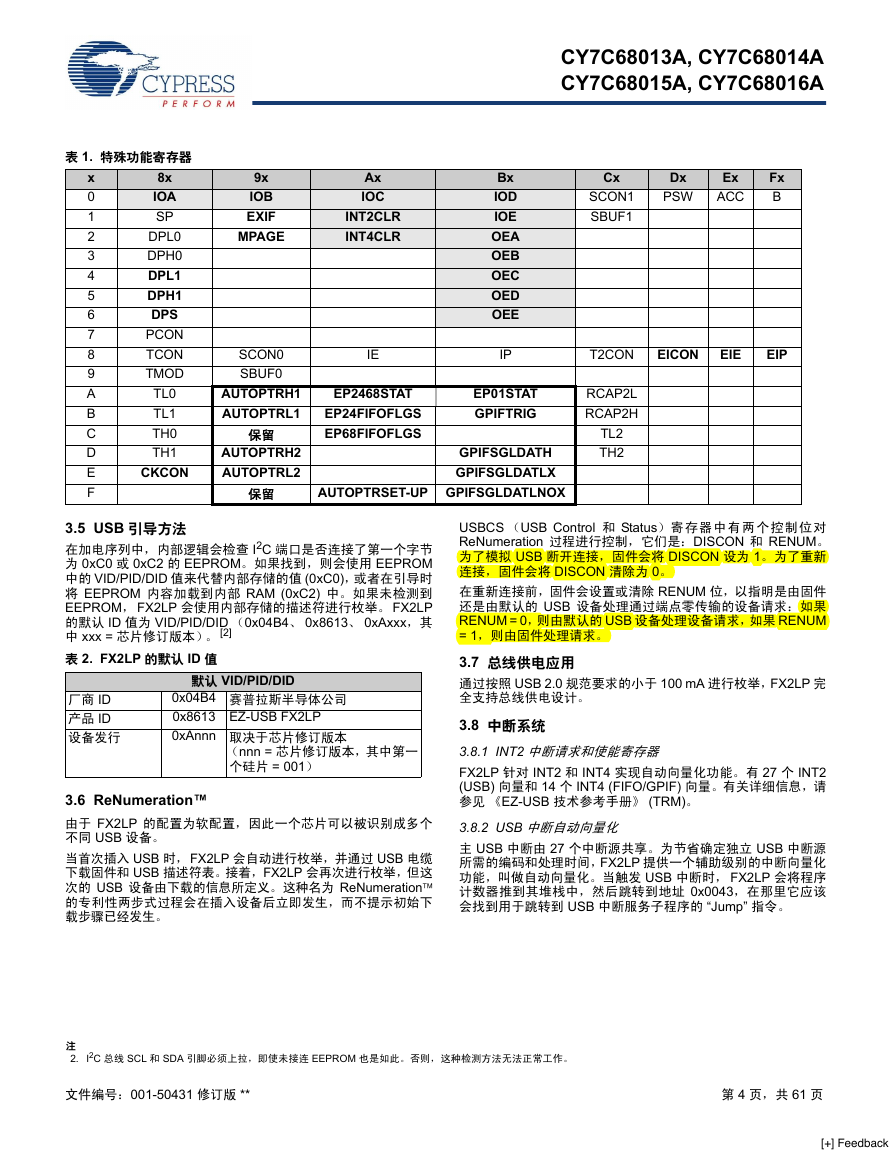

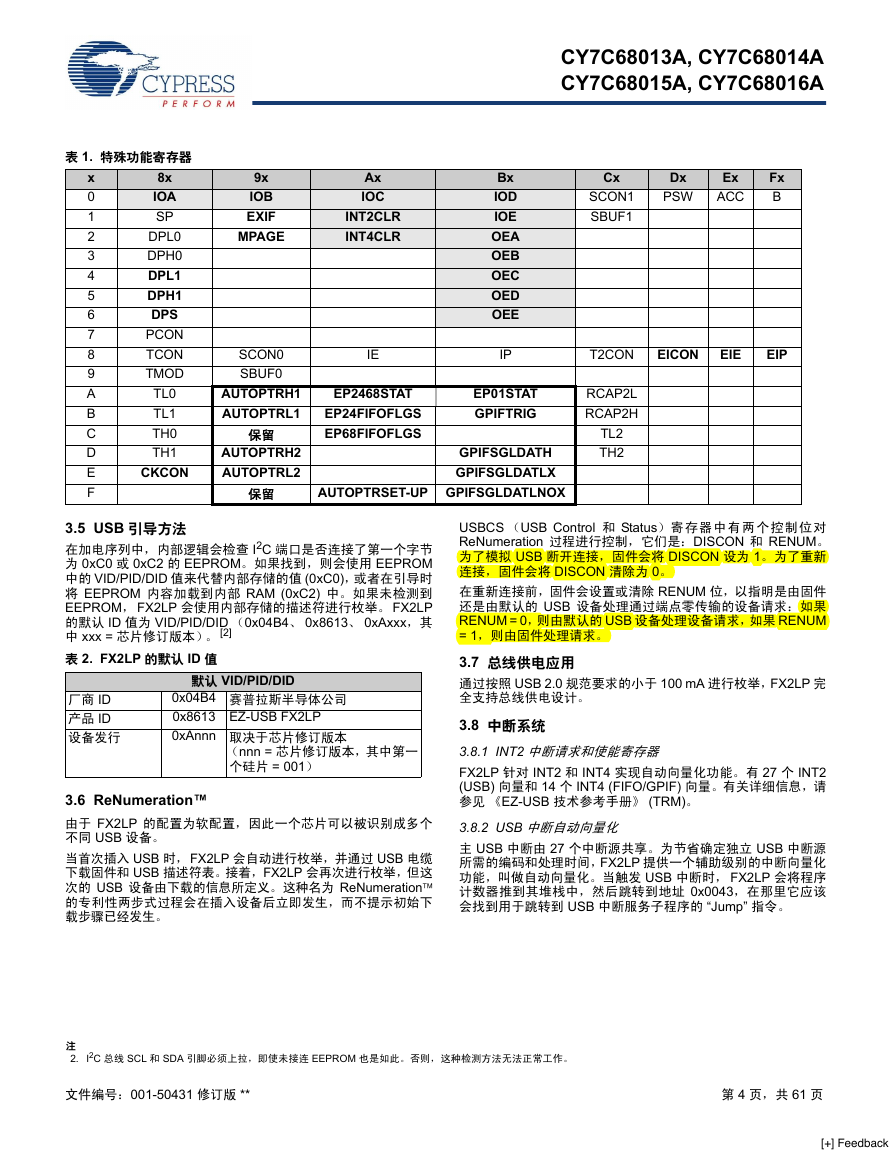

3.2.3 特殊功能寄存器

在某些 8051 SFR 地址 添加了 SFR 以便 能快速访 问关键的

FX2LP 功能。这些添加的 SFR 如第 4 页的表 1 所示。粗体部分

表示非标准的增强型 8051 寄存器。以 “0” 和 “8” 结尾的两个 SFR

行中包含可以位寻址的寄存器。 A 到 D 四个 IO 端口使用在标准

8051 中用于端口 0 到 3 的 SFR 地址,这些地址在 FX2LP 中未

实现。由于 SFR 寻址更快、更有效,因此 FX2LP IO 端口在外部

RAM 空间中不可寻址 (使用 MOVX 指令)。

3.3 I2C 总线

FX2LP 仅支持在 100/400 KHz 下将 I2C 总线用作主控端。 SCL

和 SDA 引脚具有开漏输出和滞后输入。即使未连接 I2C 设备,这

些信号也必须上拉至 3.3V。

3.4 总线

所有封装 (8 位或 16 位 “FIFO” 双向数据总线)均在 IO 端口 B

和 D 上多路复用。 128 引脚封装:添加仅 16 位输出 8051 地址

总线和 8 位双向数据总线。

注

1. 以 115 KBaud 的速率运行也是可能的,只要分别针对 UART0、 UART1 或针对二者将 8051 SMOD0 或 SMOD1 位编程为 “1” 即可。

文件编号:001-50431 修订版 **

第 3 页,共 61 页

[+] Feedback

�

CY7C68013A, CY7C68014A

CY7C68015A, CY7C68016A

Cx

SCON1

SBUF1

Dx

Ex

PSW ACC

Fx

B

T2CON

EICON

EIE

EIP

Bx

IOD

IOE

OEA

OEB

OEC

OED

OEE

IP

EP01STAT

GPIFTRIG

GPIFSGLDATH

GPIFSGLDATLX

RCAP2L

RCAP2H

TL2

TH2

9x

IOB

EXIF

MPAGE

Ax

IOC

INT2CLR

INT4CLR

IE

EP2468STAT

EP24FIFOFLGS

EP68FIFOFLGS

SCON0

SBUF0

AUTOPTRH1

AUTOPTRL1

保留

AUTOPTRH2

AUTOPTRL2

保留

AUTOPTRSET-UP GPIFSGLDATLNOX

表 1. 特殊功能寄存器

8x

IOA

SP

DPL0

DPH0

DPL1

DPH1

DPS

PCON

TCON

TMOD

TL0

TL1

TH0

TH1

CKCON

x

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

3.5 USB 引导方法

在加电序列中,内部逻辑会检查 I2C 端口是否连接了第一个字节

为 0xC0 或 0xC2 的 EEPROM。如果找到,则会使用 EEPROM

中的 VID/PID/DID 值来代替内部存储的值 (0xC0),或者在引导时

将 EEPROM 内容加载到内部 RAM (0xC2) 中。如果未检测到

EEPROM, FX2LP 会使用内部存储的描述符进行枚举。 FX2LP

的默认 ID 值为 VID/PID/DID (0x04B4、 0x8613、 0xAxxx,其

中 xxx = 芯片修订版本)。 [2]

表 2. FX2LP 的默认 ID 值

厂商 ID

产品 ID

设备发行

默认 VID/PID/DID

0x04B4 赛普拉斯半导体公司

0x8613 EZ-USB FX2LP

0xAnnn 取决于芯片修订版本

(nnn = 芯片修订版本,其中第一

个硅片 = 001)

3.6 ReNumeration™

由于 FX2LP 的配置为软配置,因此一个芯片可以被识别成多个

不同 USB 设备。

当首次插入 USB 时,FX2LP 会自动进行枚举,并通过 USB 电缆

下载固件和 USB 描述符表。接着,FX2LP 会再次进行枚举,但这

次的 USB 设备由下载的信息所定义。这种名为 ReNumeration™

的专利性两步式过程会在插入设备后立即发生,而不提示初始下

载步骤已经发生。

USBCS (USB Control 和 Status)寄存器中有两个控制位对

ReNumeration 过程进行控制,它们是:DISCON 和 RENUM。

为了模拟 USB 断开连接,固件会将 DISCON 设为 1。为了重新

连接,固件会将 DISCON 清除为 0。

在重新连接前,固件会设置或清除 RENUM 位,以指明是由固件

还是由默认的 USB 设备处理通过端点零传输的设备请求:如果

RENUM = 0,则由默认的 USB 设备处理设备请求,如果 RENUM

= 1,则由固件处理请求。

3.7 总线供电应用

通过按照 USB 2.0 规范要求的小于 100 mA 进行枚举,FX2LP 完

全支持总线供电设计。

3.8 中断系统

3.8.1 INT2 中断请求和使能寄存器

FX2LP 针对 INT2 和 INT4 实现自动向量化功能。有 27 个 INT2

(USB) 向量和 14 个 INT4 (FIFO/GPIF) 向量。有关详细信息,请

参见 《EZ-USB 技术参考手册》 (TRM)。

3.8.2 USB 中断自动向量化

主 USB 中断由 27 个中断源共享。为节省确定独立 USB 中断源

所需的编码和处理时间,FX2LP 提供一个辅助级别的中断向量化

功能,叫做自动向量化。当触发 USB 中断时, FX2LP 会将程序

计数器推到其堆栈中,然后跳转到地址 0x0043,在那里它应该

会找到用于跳转到 USB 中断服务子程序的 “Jump” 指令。

注

2.

I2C 总线 SCL 和 SDA 引脚必须上拉,即使未接连 EEPROM 也是如此。否则,这种检测方法无法正常工作。

文件编号:001-50431 修订版 **

第 4 页,共 61 页

[+] Feedback

�

CY7C68013A, CY7C68014A

CY7C68015A, CY7C68016A

FX2LP jump 指令的编码如下所示:

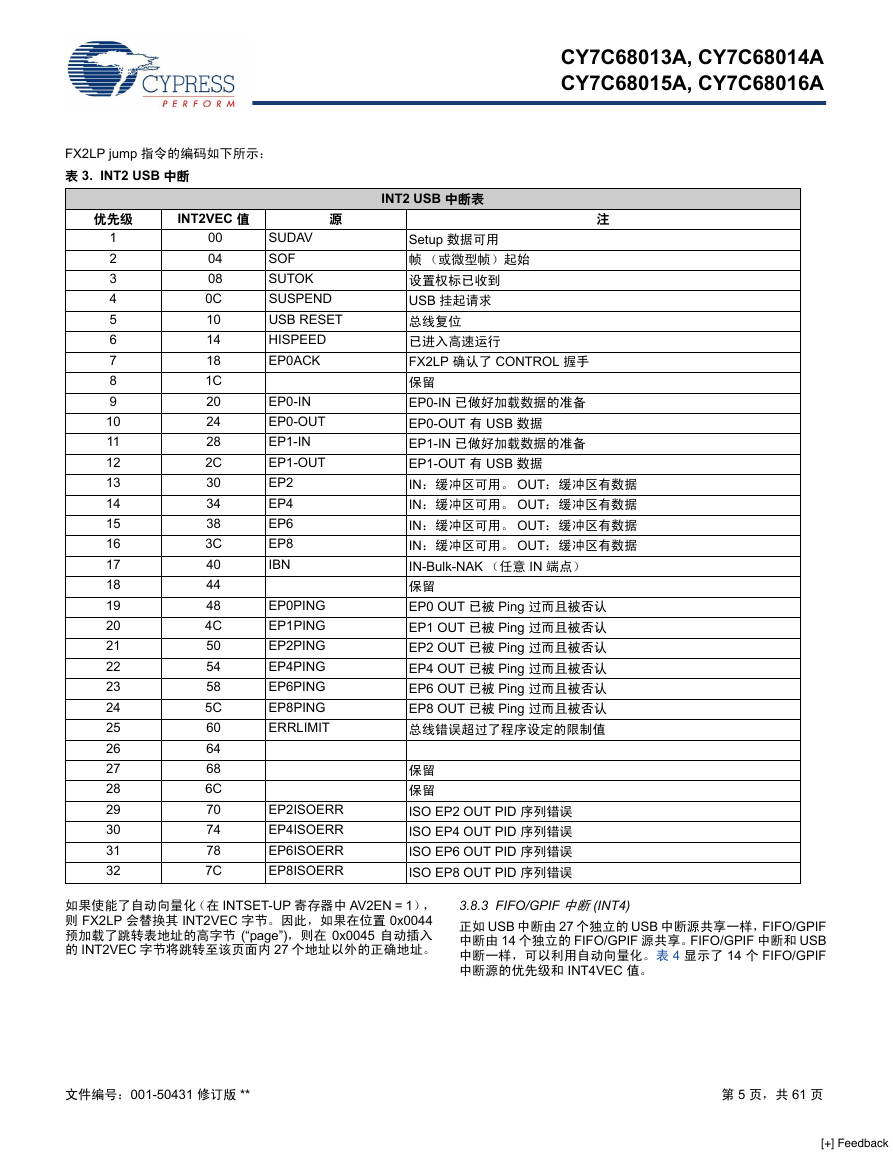

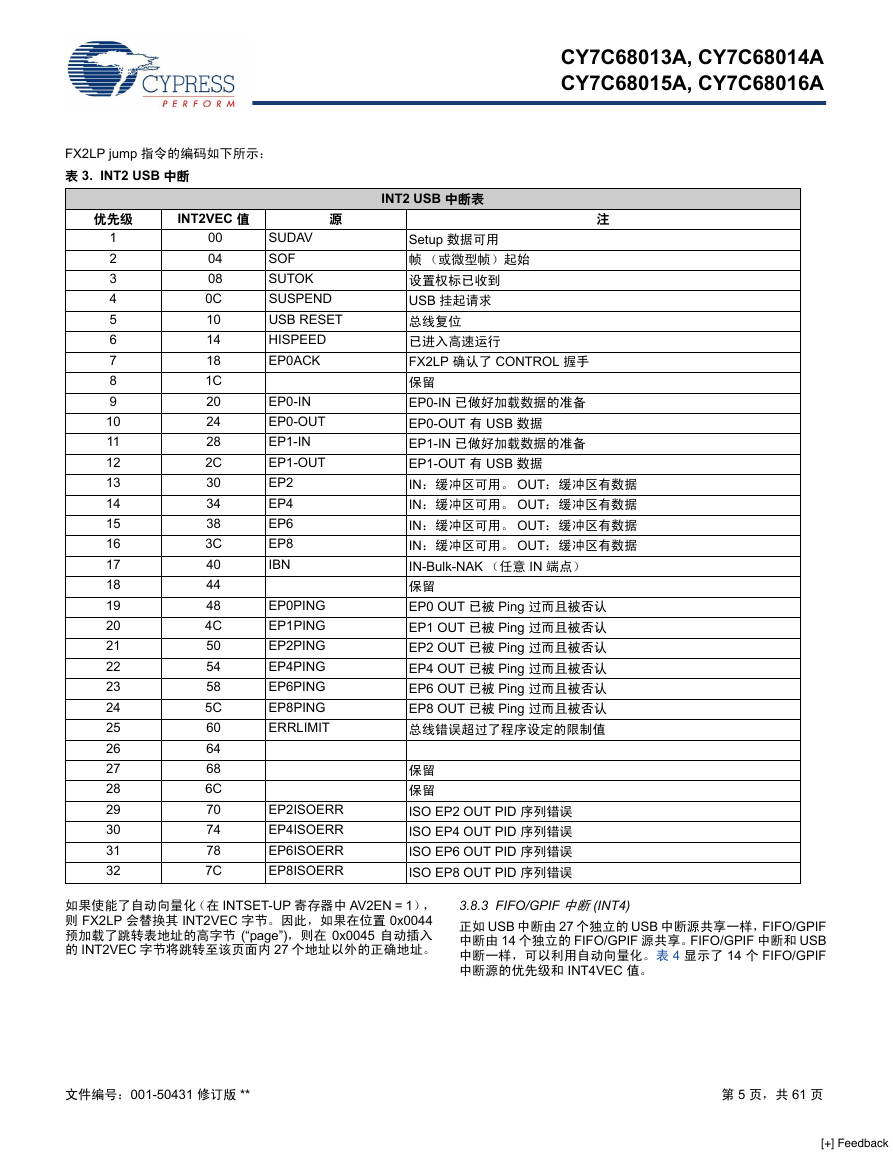

表 3. INT2 USB 中断

优先级

INT2VEC 值

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

00

04

08

0C

10

14

18

1C

20

24

28

2C

30

34

38

3C

40

44

48

4C

50

54

58

5C

60

64

68

6C

70

74

78

7C

源

SUDAV

SOF

SUTOK

SUSPEND

USB RESET

HISPEED

EP0ACK

EP0-IN

EP0-OUT

EP1-IN

EP1-OUT

EP2

EP4

EP6

EP8

IBN

EP0PING

EP1PING

EP2PING

EP4PING

EP6PING

EP8PING

ERRLIMIT

EP2ISOERR

EP4ISOERR

EP6ISOERR

EP8ISOERR

INT2 USB 中断表

注

Setup 数据可用

帧 (或微型帧)起始

设置权标已收到

USB 挂起请求

总线复位

已进入高速运行

FX2LP 确认了 CONTROL 握手

保留

EP0-IN 已做好加载数据的准备

EP0-OUT 有 USB 数据

EP1-IN 已做好加载数据的准备

EP1-OUT 有 USB 数据

IN: 缓冲区可用。 OUT: 缓冲区有数据

IN: 缓冲区可用。 OUT: 缓冲区有数据

IN: 缓冲区可用。 OUT: 缓冲区有数据

IN: 缓冲区可用。 OUT: 缓冲区有数据

IN-Bulk-NAK (任意 IN 端点)

保留

EP0 OUT 已被 Ping 过而且被否认

EP1 OUT 已被 Ping 过而且被否认

EP2 OUT 已被 Ping 过而且被否认

EP4 OUT 已被 Ping 过而且被否认

EP6 OUT 已被 Ping 过而且被否认

EP8 OUT 已被 Ping 过而且被否认

总线错误超过了程序设定的限制值

保留

保留

ISO EP2 OUT PID 序列错误

ISO EP4 OUT PID 序列错误

ISO EP6 OUT PID 序列错误

ISO EP8 OUT PID 序列错误

如果使能了自动向量化(在 INTSET-UP 寄存器中 AV2EN = 1),

则 FX2LP 会替换其 INT2VEC 字节。因此,如果在位置 0x0044

预加载了跳转表地址的高字节 (“page”),则在 0x0045 自动插入

的 INT2VEC 字节将跳转至该页面内 27 个地址以外的正确地址。

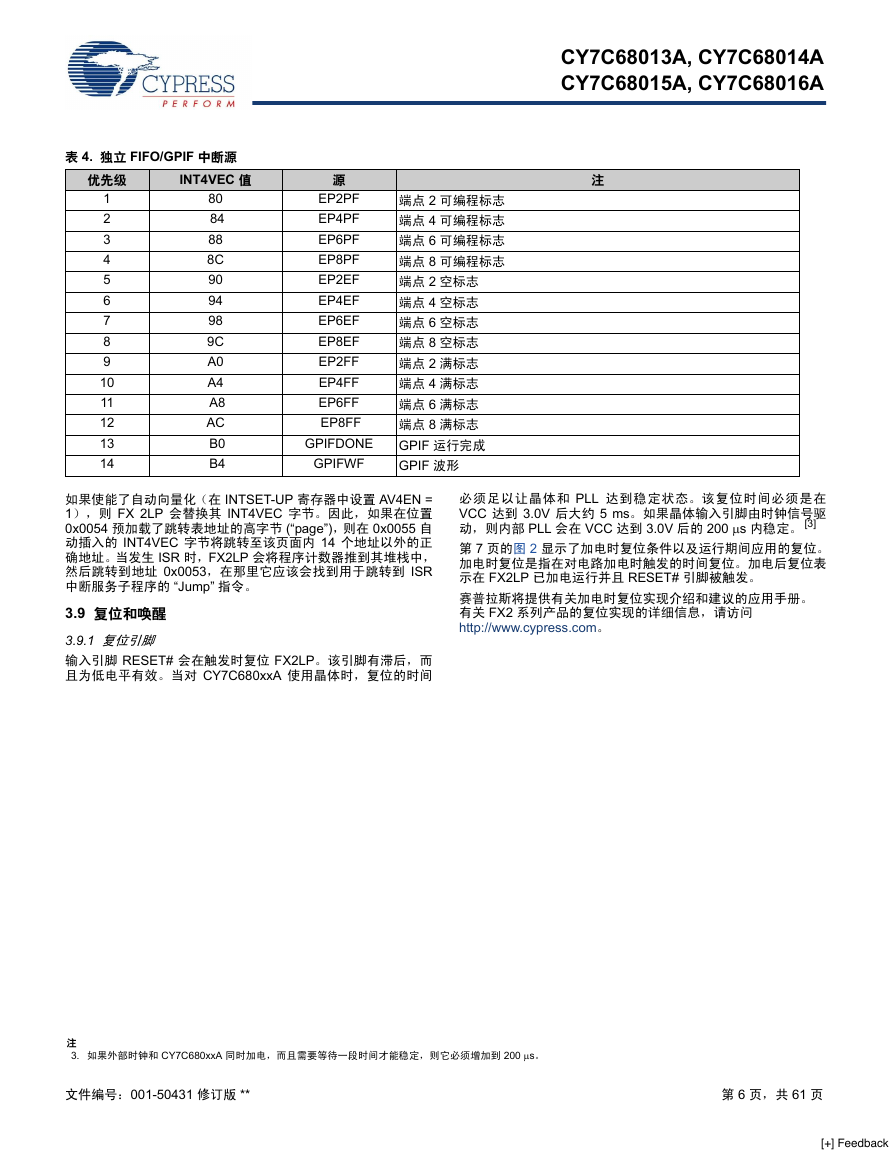

3.8.3 FIFO/GPIF 中断 (INT4)

正如 USB 中断由 27 个独立的 USB 中断源共享一样,FIFO/GPIF

中断由 14 个独立的 FIFO/GPIF 源共享。FIFO/GPIF 中断和 USB

中断一样,可以利用自动向量化。表 4 显示了 14 个 FIFO/GPIF

中断源的优先级和 INT4VEC 值。

文件编号:001-50431 修订版 **

第 5 页,共 61 页

[+] Feedback

�

CY7C68013A, CY7C68014A

CY7C68015A, CY7C68016A

注

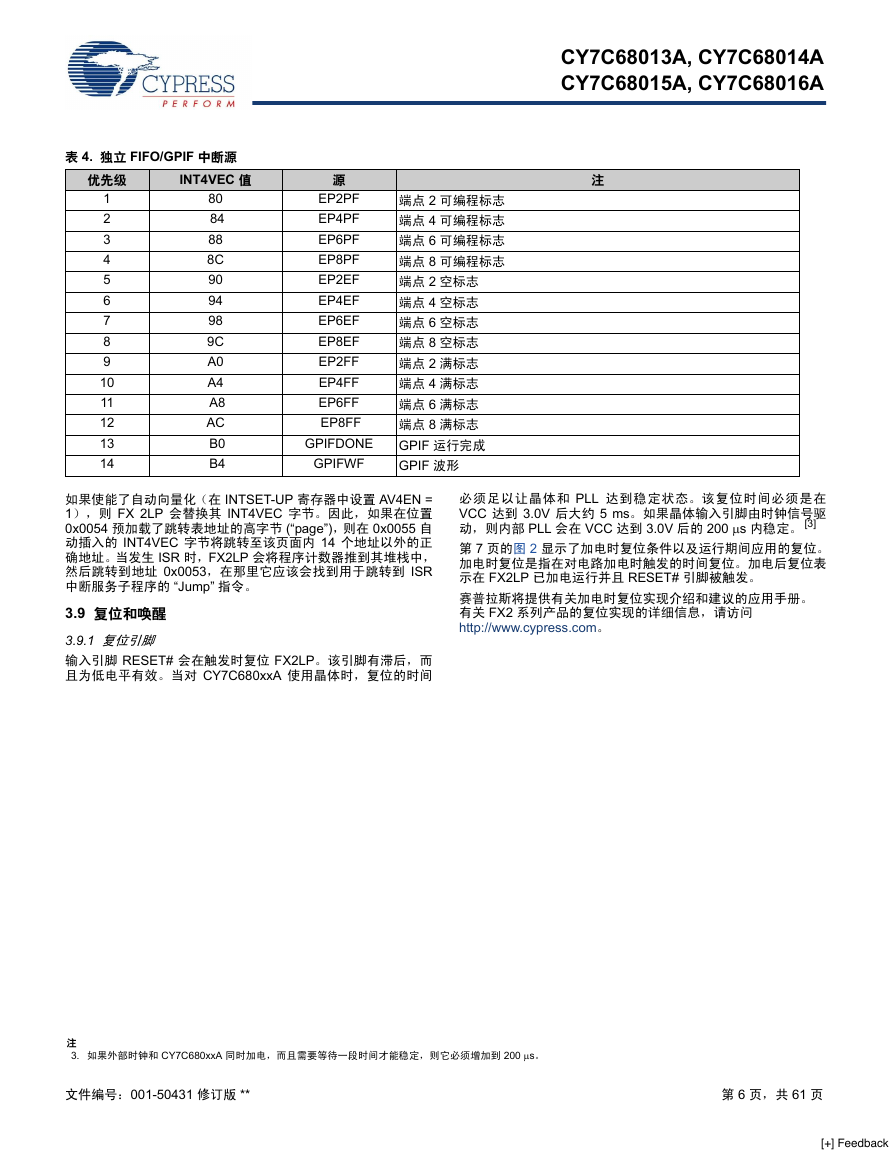

表 4. 独立 FIFO/GPIF 中断源

优先级

INT4VEC 值

1

2

3

4

5

6

7

8

9

10

11

12

13

14

80

84

88

8C

90

94

98

9C

A0

A4

A8

AC

B0

B4

源

EP2PF

EP4PF

EP6PF

EP8PF

EP2EF

EP4EF

EP6EF

EP8EF

EP2FF

EP4FF

EP6FF

EP8FF

GPIFDONE

GPIFWF

端点 2 可编程标志

端点 4 可编程标志

端点 6 可编程标志

端点 8 可编程标志

端点 2 空标志

端点 4 空标志

端点 6 空标志

端点 8 空标志

端点 2 满标志

端点 4 满标志

端点 6 满标志

端点 8 满标志

GPIF 运行完成

GPIF 波形

如果使能了自动向量化(在 INTSET-UP 寄存器中设置 AV4EN =

1),则 FX 2LP 会替换其 INT4VEC 字节。因此,如果在位置

0x0054 预加载了跳转表地址的高字节 (“page”),则在 0x0055 自

动插入的 INT4VEC 字节将跳转至该页面内 14 个地址以外的正

确地址。当发生 ISR 时,FX2LP 会将程序计数器推到其堆栈中,

然后跳转到地址 0x0053,在那里它应该会找到用于跳转到 ISR

中断服务子程序的 “Jump” 指令。

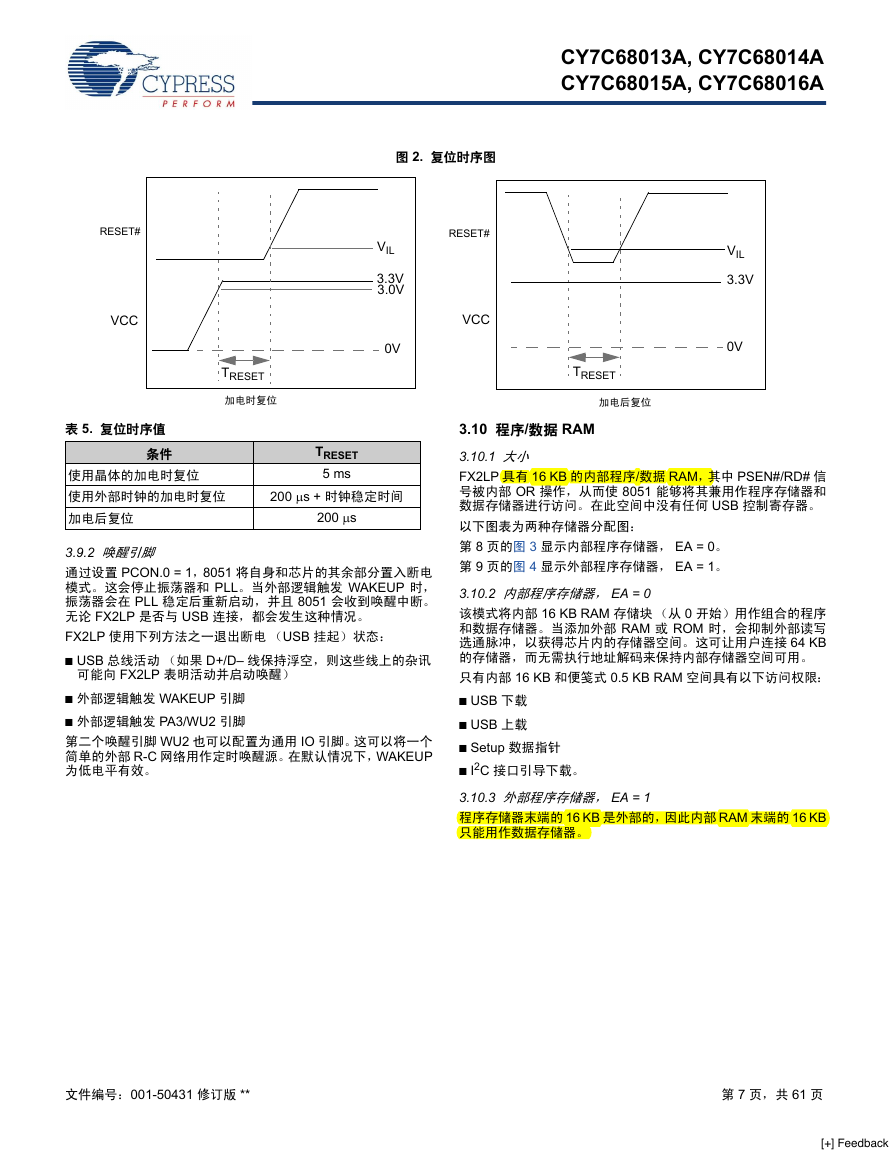

3.9 复位和唤醒

3.9.1 复位引脚

输入引脚 RESET# 会在触发时复位 FX2LP。该引脚有滞后,而

且为低电平有效。当对 CY7C680xxA 使用晶体时,复位的时间

必须足以让晶体和 PLL 达到稳定状态。该复位时间必须是在

VCC 达到 3.0V 后大约 5 ms。如果晶体输入引脚由时钟信号驱

动,则内部 PLL 会在 VCC 达到 3.0V 后的 200 μs 内稳定。 [3]

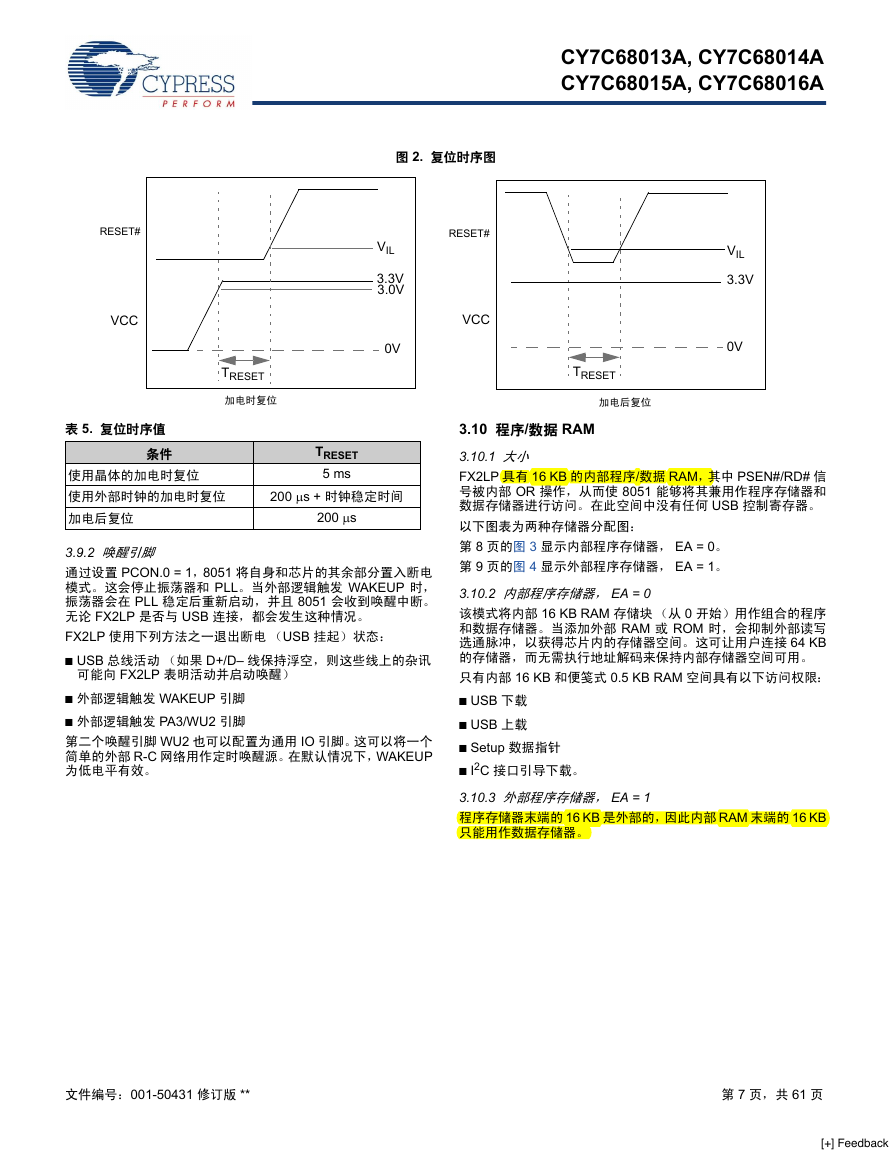

第 7 页的图 2 显示了加电时复位条件以及运行期间应用的复位。

加电时复位是指在对电路加电时触发的时间复位。加电后复位表

示在 FX2LP 已加电运行并且 RESET# 引脚被触发。

赛普拉斯将提供有关加电时复位实现介绍和建议的应用手册。

有关 FX2 系列产品的复位实现的详细信息,请访问

http://www.cypress.com。

注

3. 如果外部时钟和 CY7C680xxA 同时加电,而且需要等待一段时间才能稳定,则它必须增加到 200 μs。

文件编号:001-50431 修订版 **

第 6 页,共 61 页

[+] Feedback

�

CY7C68013A, CY7C68014A

CY7C68015A, CY7C68016A

图 2. 复位时序图

RESET#

VCC

RESET#

VCC

VIL

3.3V

3.0V

0V

VIL

3.3V

0V

TRESET

加电时复位

TRESET

加电后复位

表 5. 复位时序值

条件

使用晶体的加电时复位

TRESET

5 ms

使用外部时钟的加电时复位

200 μs + 时钟稳定时间

加电后复位

200 μs

3.9.2 唤醒引脚

通过设置 PCON.0 = 1,8051 将自身和芯片的其余部分置入断电

模式。这会停止振荡器和 PLL。当外部逻辑触发 WAKEUP 时,

振荡器会在 PLL 稳定后重新启动,并且 8051 会收到唤醒中断。

无论 FX2LP 是否与 USB 连接,都会发生这种情况。

FX2LP 使用下列方法之一退出断电 (USB 挂起)状态:

■ USB 总线活动 (如果 D+/D– 线保持浮空,则这些线上的杂讯

可能向 FX2LP 表明活动并启动唤醒)

■ 外部逻辑触发 WAKEUP 引脚

■ 外部逻辑触发 PA3/WU2 引脚

第二个唤醒引脚 WU2 也可以配置为通用 IO 引脚。这可以将一个

简单的外部 R-C 网络用作定时唤醒源。在默认情况下,WAKEUP

为低电平有效。

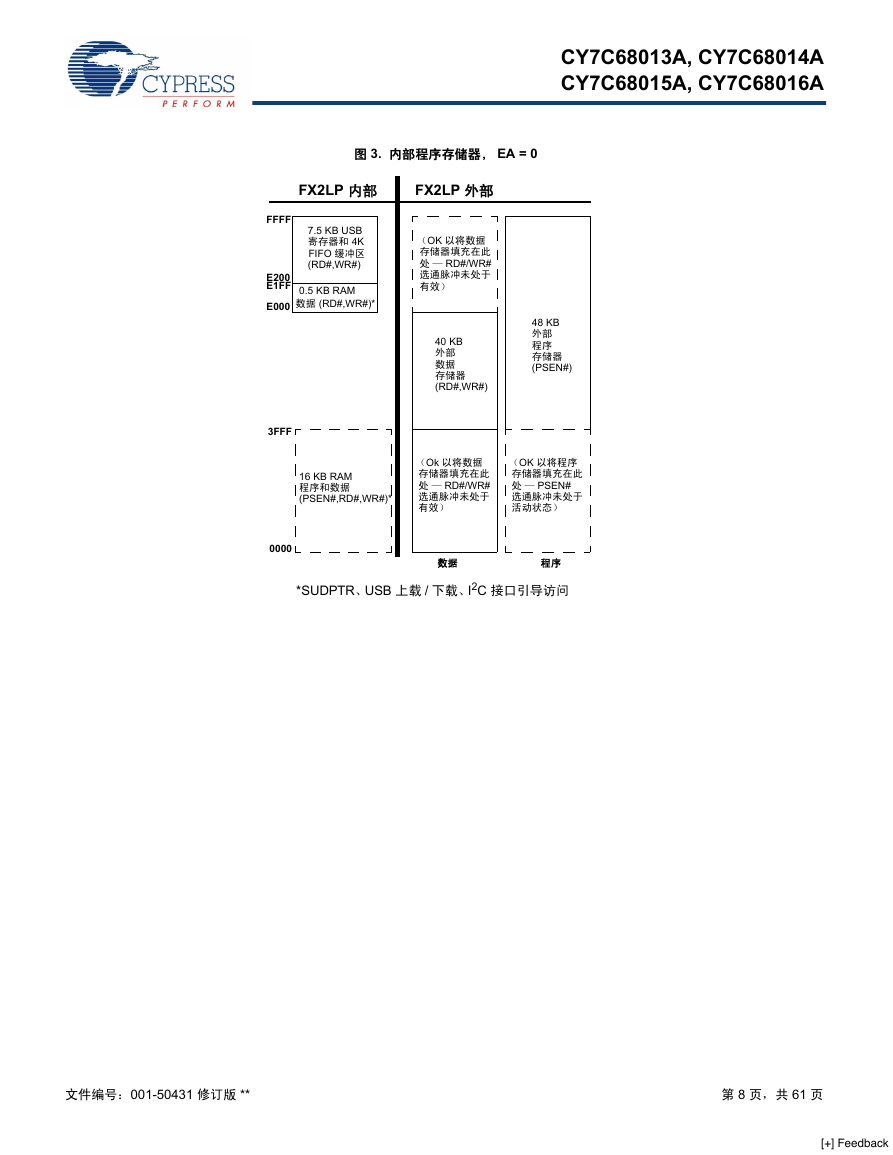

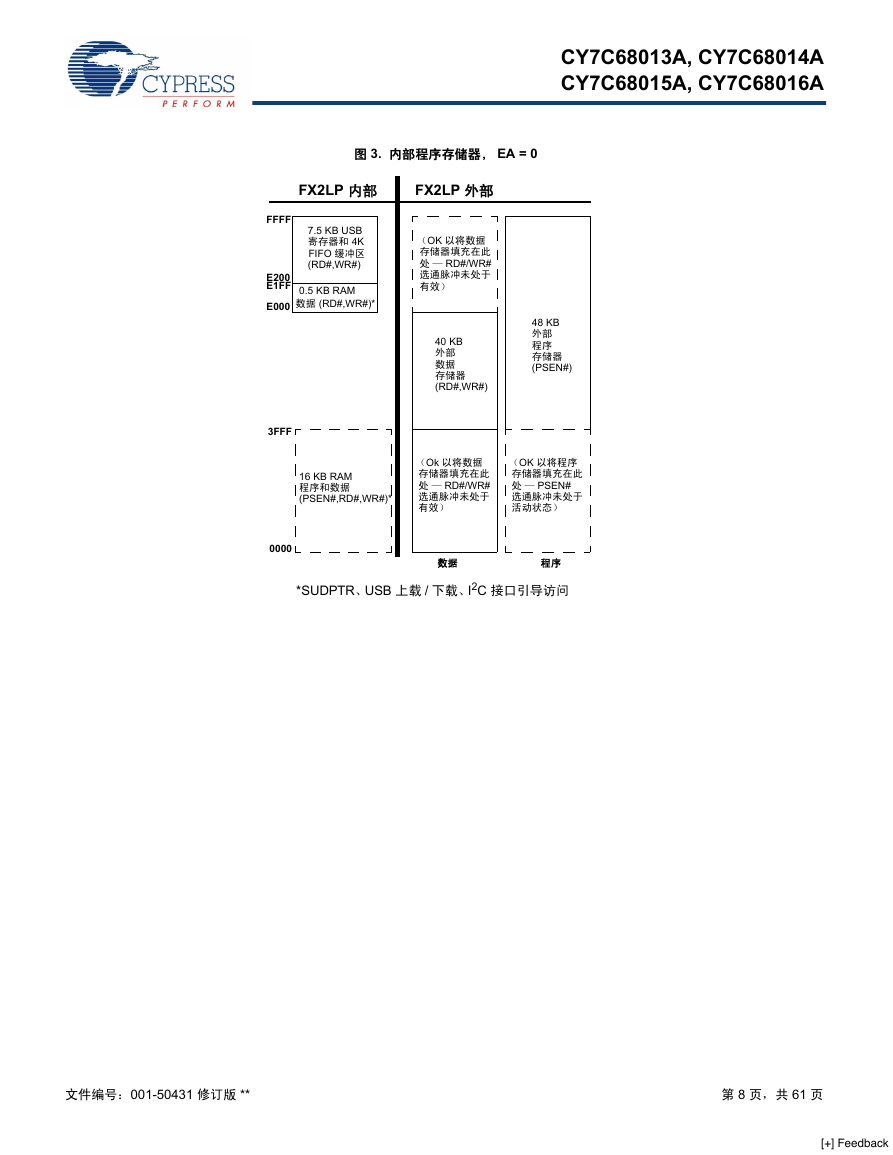

3.10 程序/数据 RAM

3.10.1 大小

FX2LP 具有 16 KB 的内部程序/数据 RAM,其中 PSEN#/RD# 信

号被内部 OR 操作,从而使 8051 能够将其兼用作程序存储器和

数据存储器进行访问。在此空间中没有任何 USB 控制寄存器。

以下图表为两种存储器分配图:

第 8 页的图 3 显示内部程序存储器, EA = 0。

第 9 页的图 4 显示外部程序存储器, EA = 1。

3.10.2 内部程序存储器,EA = 0

该模式将内部 16 KB RAM 存储块 (从 0 开始)用作组合的程序

和数据存储器。当添加外部 RAM 或 ROM 时,会抑制外部读写

选通脉冲,以获得芯片内的存储器空间。这可让用户连接 64 KB

的存储器,而无需执行地址解码来保持内部存储器空间可用。

只有内部 16 KB 和便笺式 0.5 KB RAM 空间具有以下访问权限:

■ USB 下载

■ USB 上载

■ Setup 数据指针

■ I2C 接口引导下载。

3.10.3 外部程序存储器,EA = 1

程序存储器末端的 16 KB 是外部的,因此内部 RAM 末端的 16 KB

只能用作数据存储器。

文件编号:001-50431 修订版 **

第 7 页,共 61 页

[+] Feedback

�

CY7C68013A, CY7C68014A

CY7C68015A, CY7C68016A

图 3. 内部程序存储器, EA = 0

FX2LP 内部

FX2LP 外部

FFFF

E200

E1FF

E000

7.5 KB USB

寄存器和 4K

FIFO 缓冲区

(RD#,WR#)

0.5 KB RAM

数据 (RD#,WR#)*

(OK 以将数据

存储器填充在此

处 — RD#/WR#

选通脉冲未处于

有效)

40 KB

外部

数据

存储器

(RD#,WR#)

48 KB

外部

程序

存储器

(PSEN#)

3FFF

0000

16 KB RAM

程序和数据

(PSEN#,RD#,WR#)*

(Ok 以将数据

存储器填充在此

处 — RD#/WR#

选通脉冲未处于

有效)

(OK 以将程序

存储器填充在此

处 — PSEN#

选通脉冲未处于

活动状态)

数据

程序

*SUDPTR、USB 上载 / 下载、I2C 接口引导访问

文件编号:001-50431 修订版 **

第 8 页,共 61 页

[+] Feedback

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc