1

2

3

4

5

6

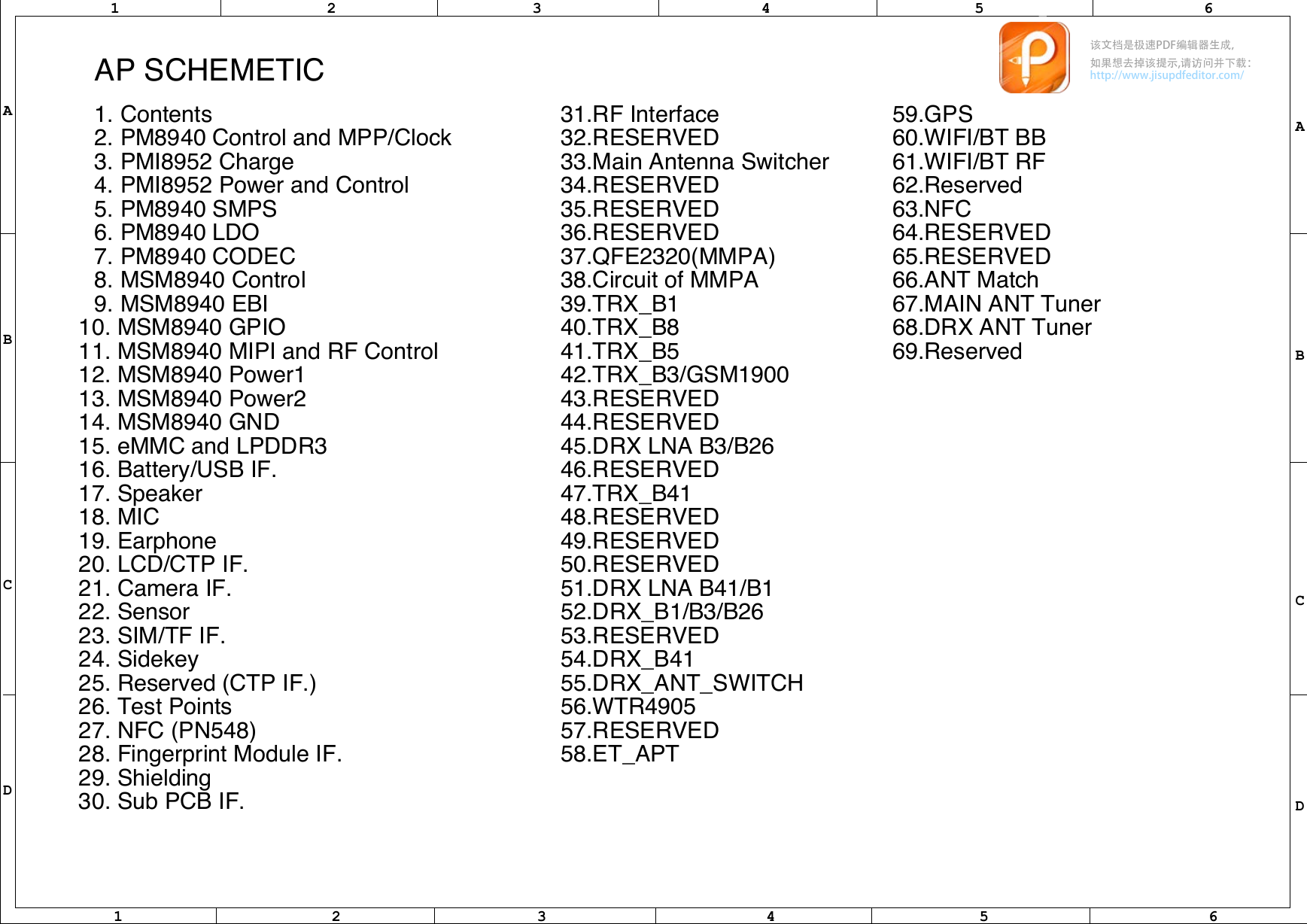

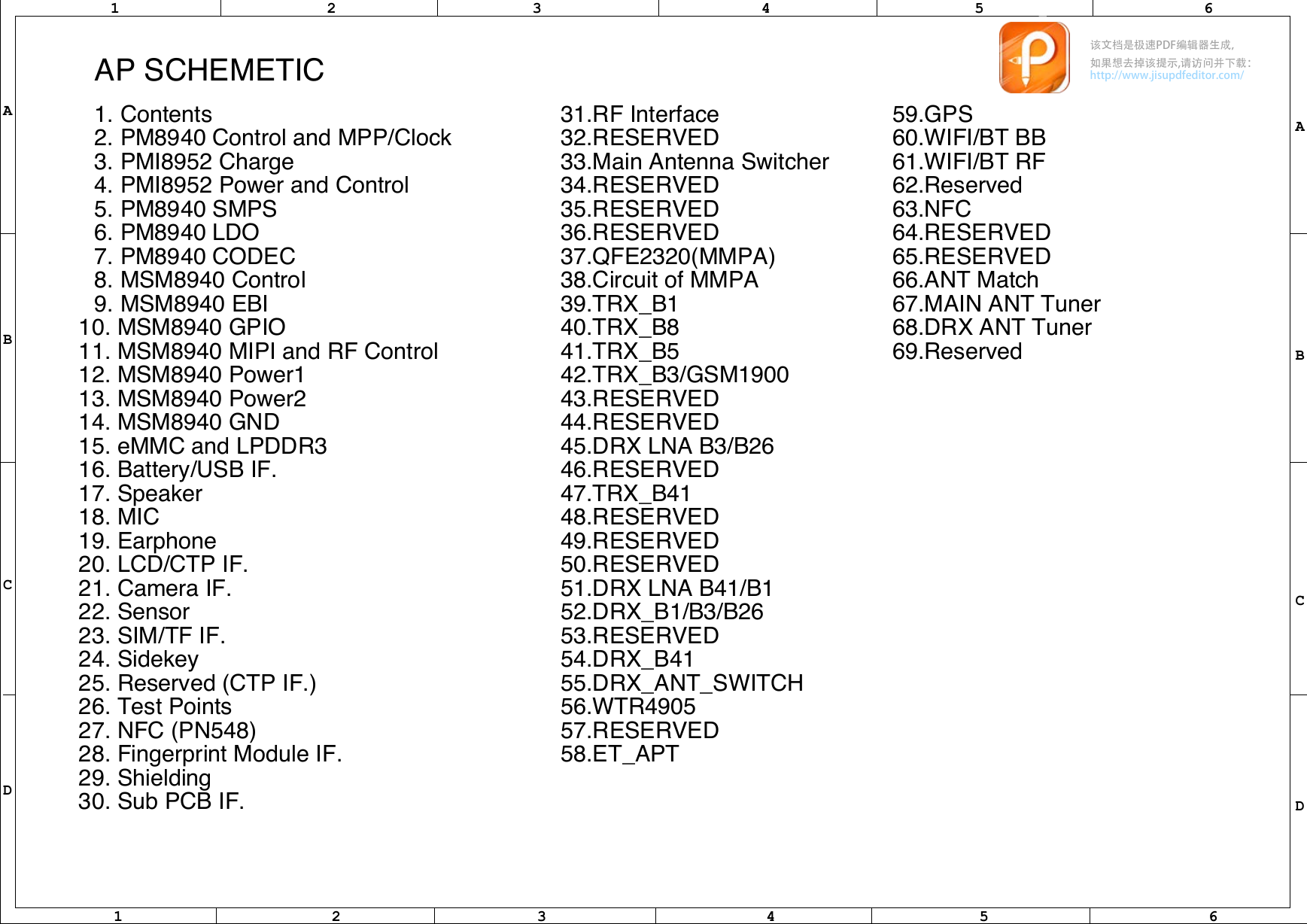

59.GPS

60.WIFI/BT BB

61.WIFI/BT RF

62.Reserved

63.NFC

64.RESERVED

65.RESERVED

66.ANT Match

67.MAIN ANT Tuner

68.DRX ANT Tuner

69.Reserved

AP SCHEMETIC

1. Contents

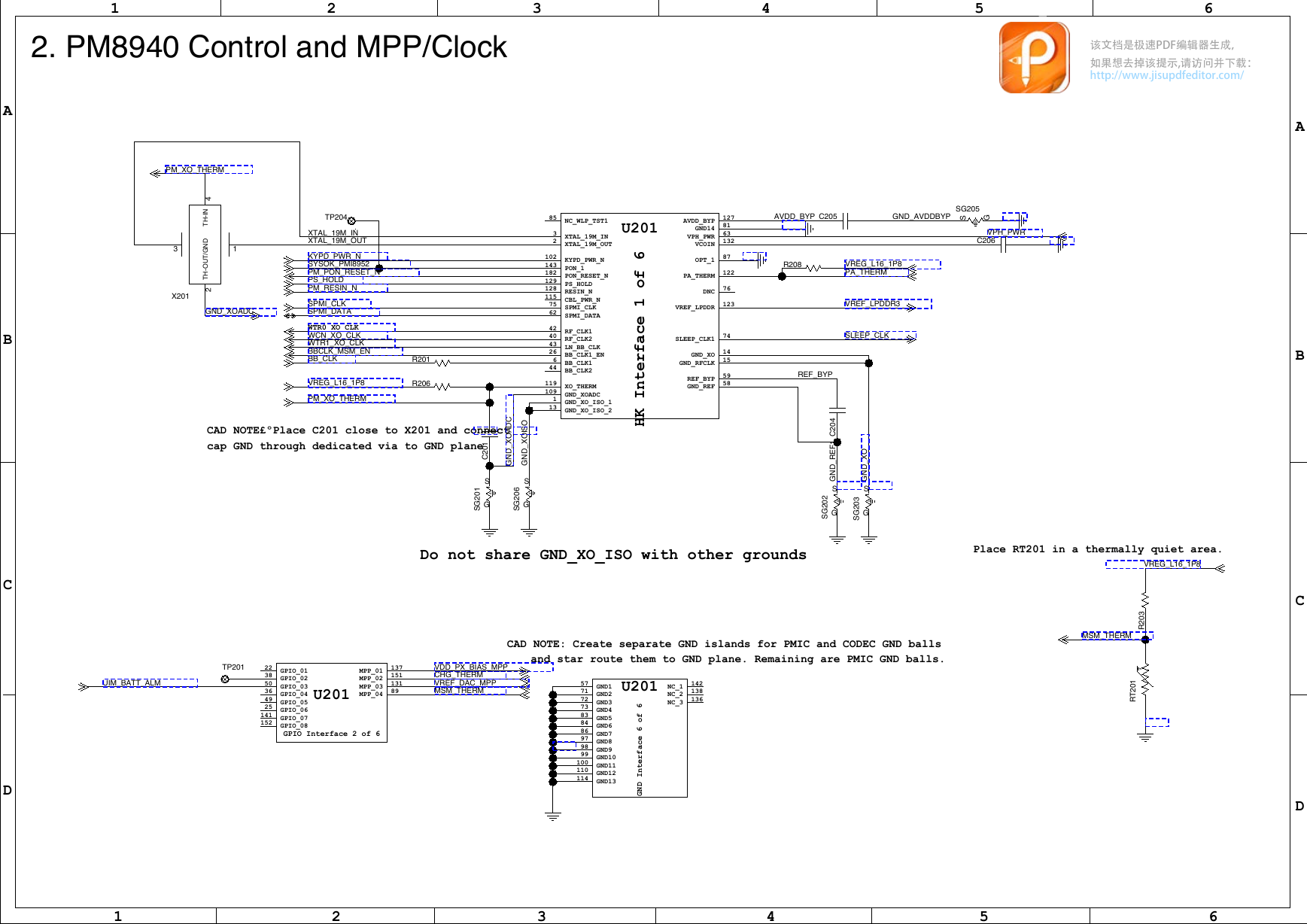

2. PM8940 Control and MPP/Clock

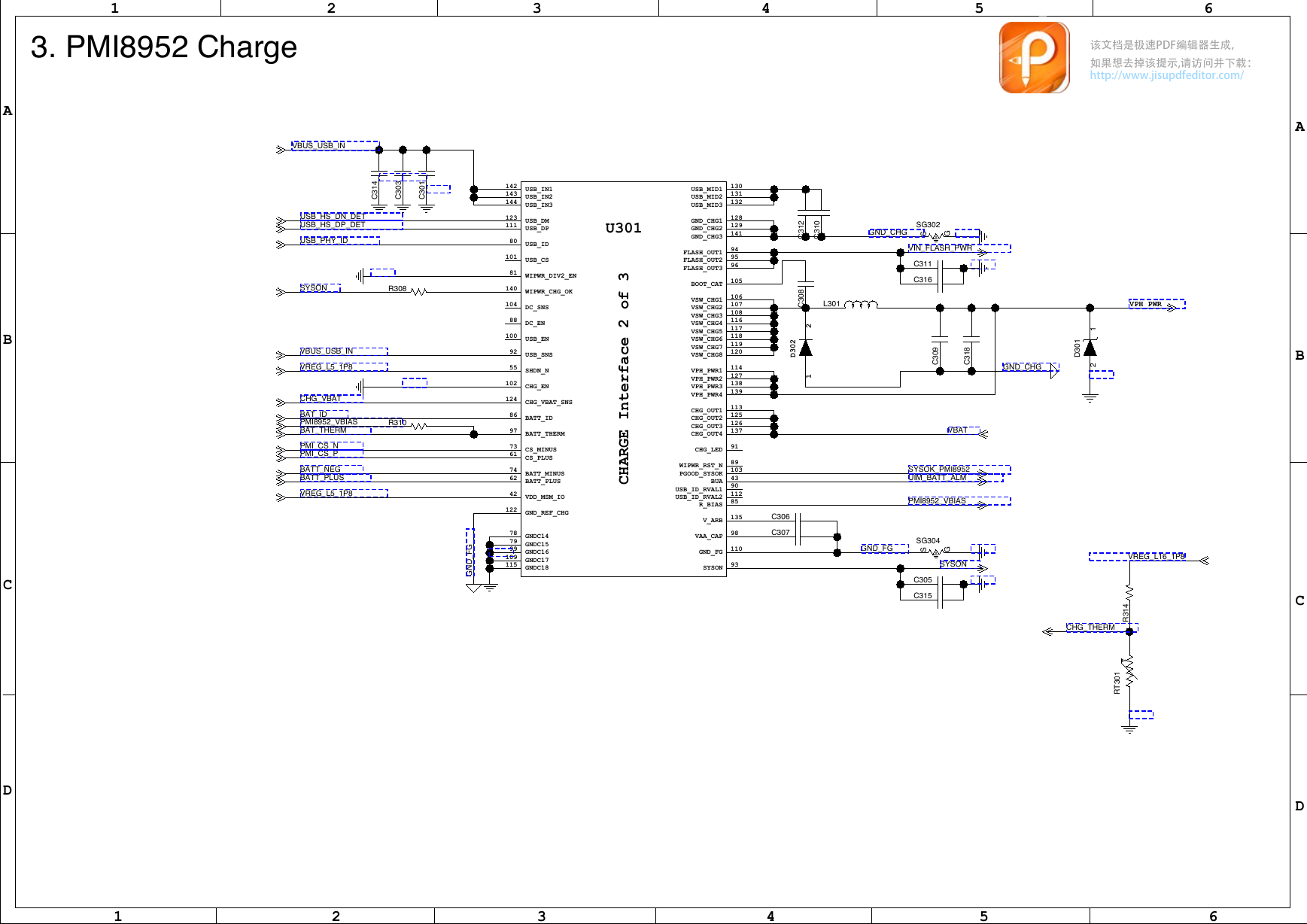

3. PMI8952 Charge

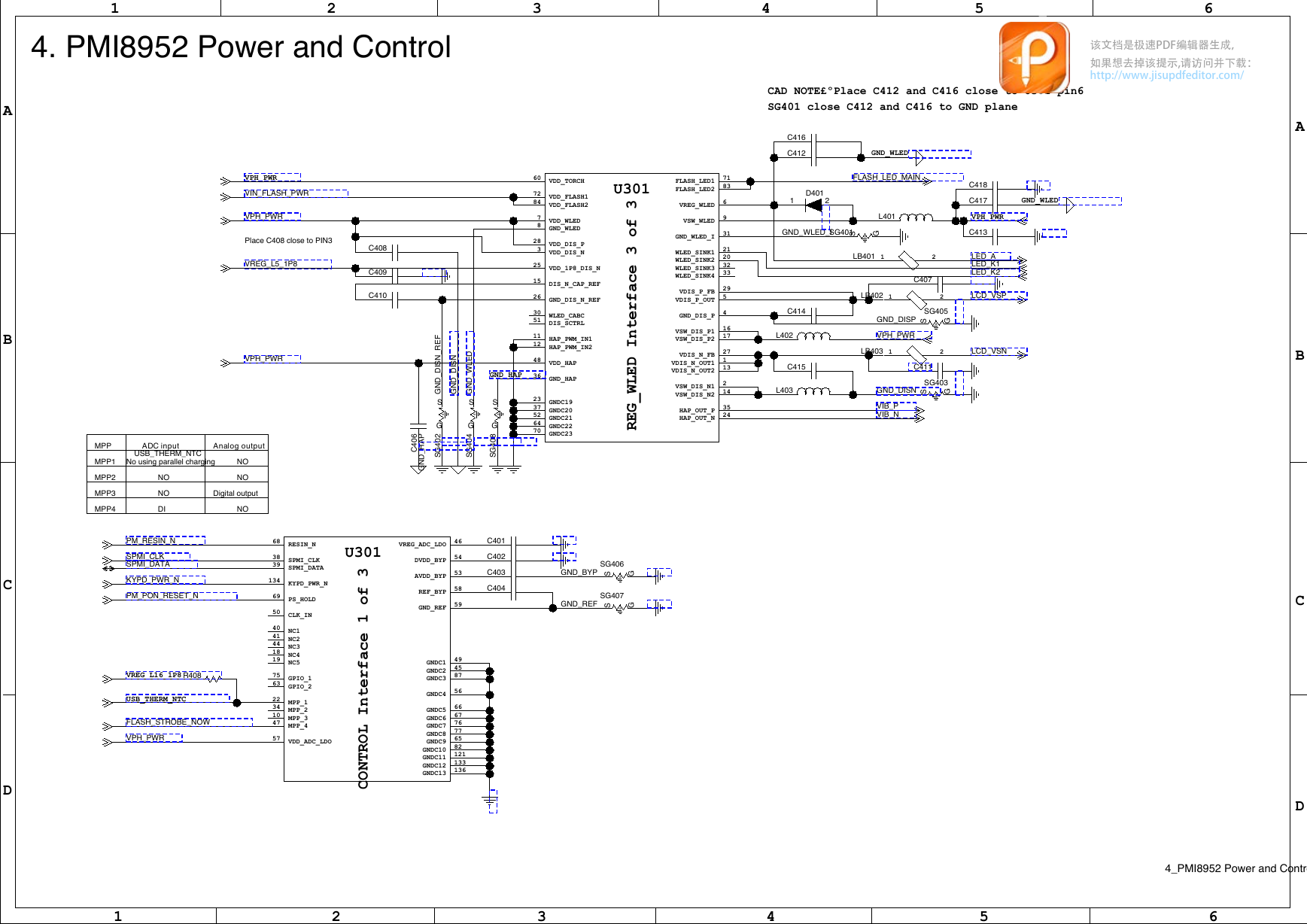

4. PMI8952 Power and Control

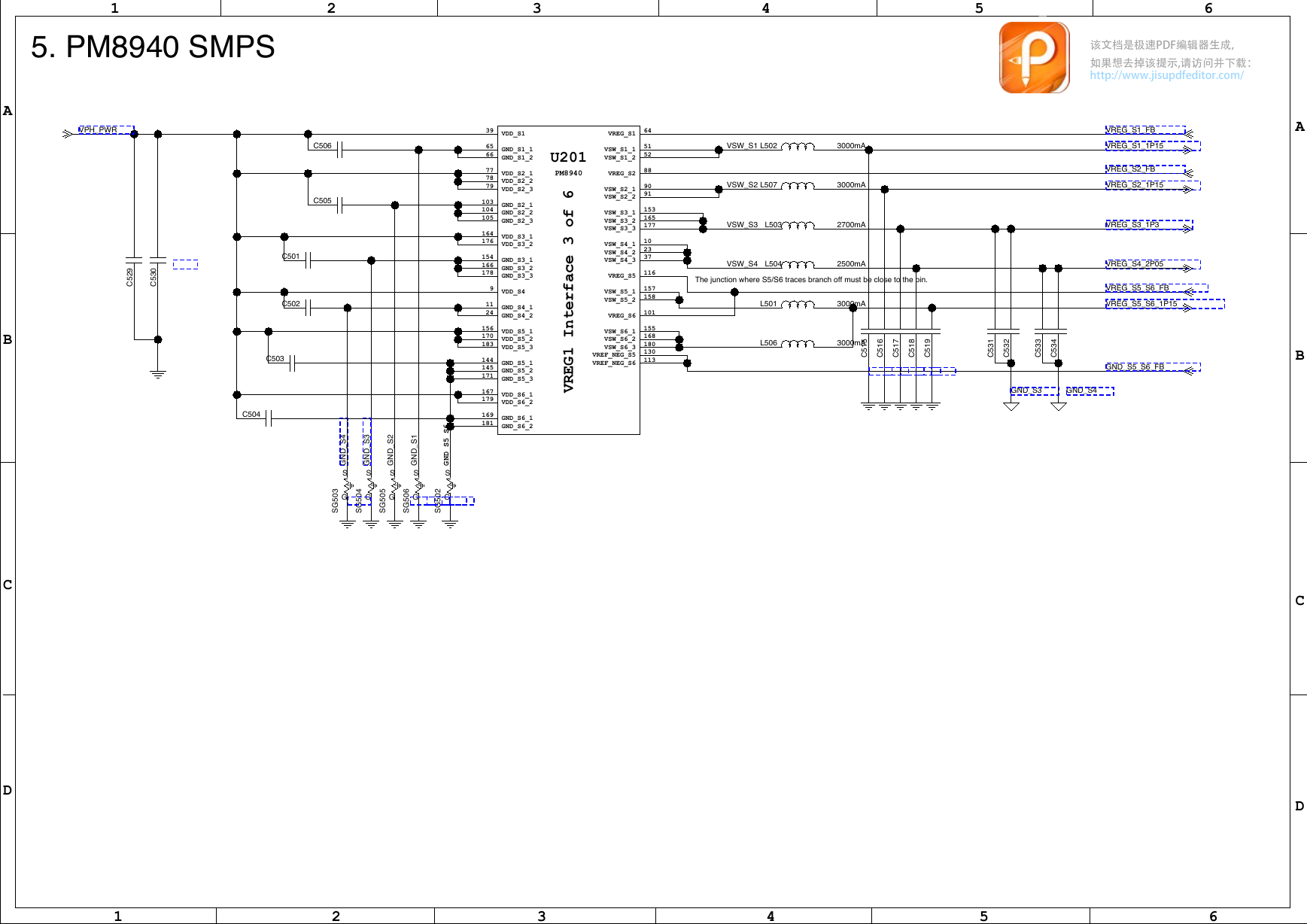

5. PM8940 SMPS

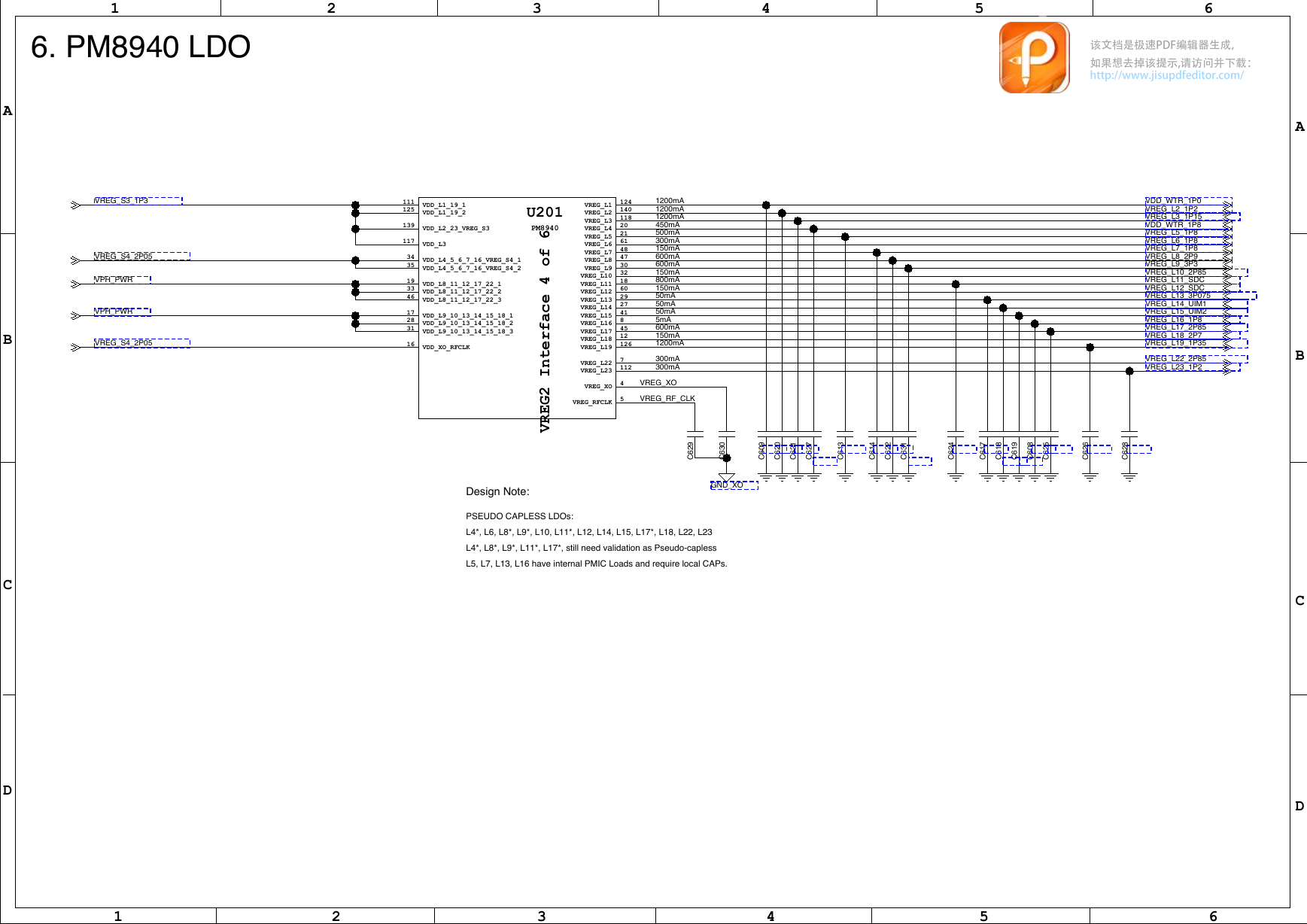

6. PM8940 LDO

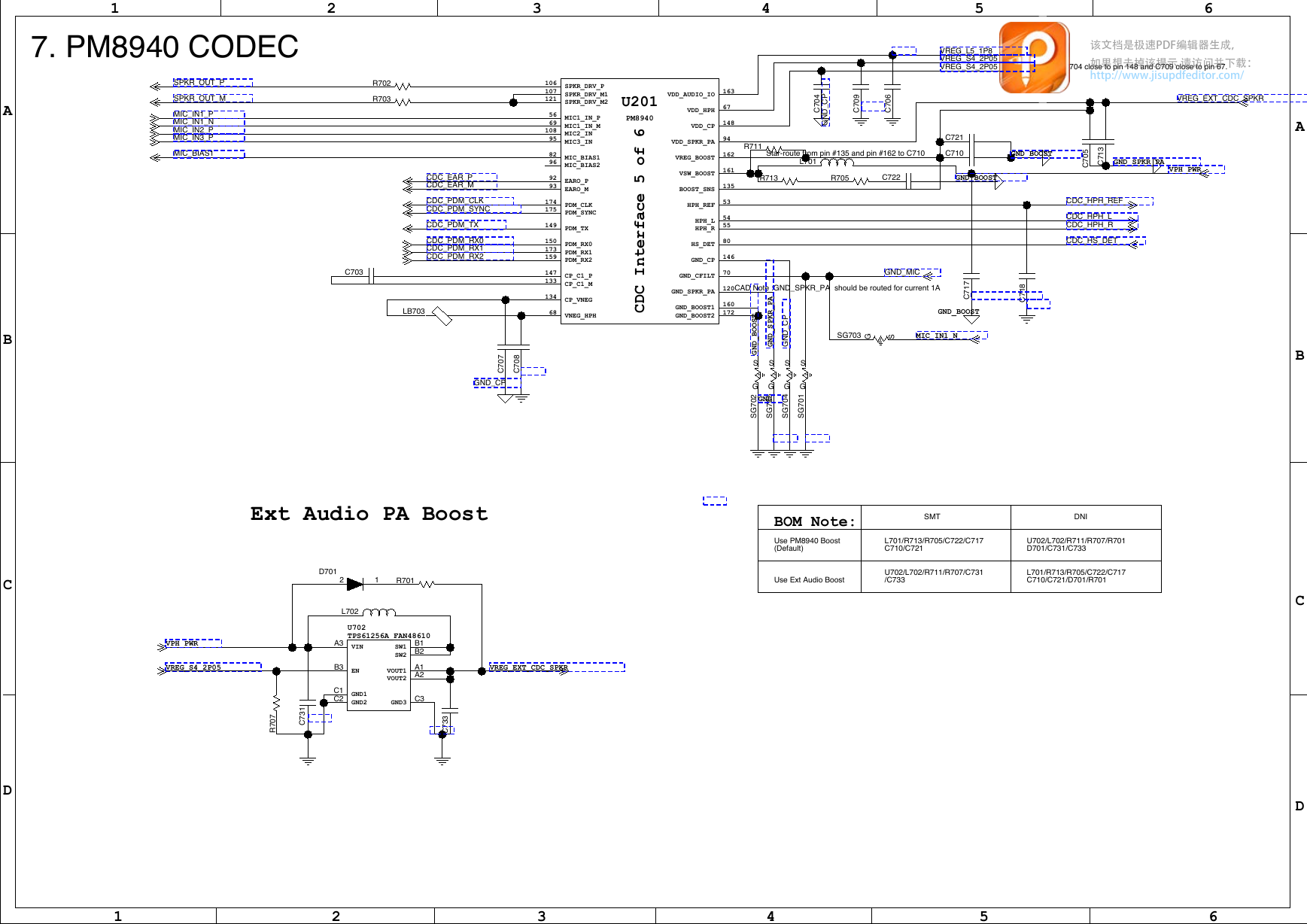

7. PM8940 CODEC

8. MSM8940 Control

9. MSM8940 EBI

10. MSM8940 GPIO

11. MSM8940 MIPI and RF Control

12. MSM8940 Power1

13. MSM8940 Power2

14. MSM8940 GND

15. eMMC and LPDDR3

16. Battery/USB IF.

17. Speaker

18. MIC

19. Earphone

20. LCD/CTP IF.

21. Camera IF.

22. Sensor

23. SIM/TF IF.

24. Sidekey

25. Reserved (CTP IF.)

26. Test Points

27. NFC (PN548)

28. Fingerprint Module IF.

29. Shielding

30. Sub PCB IF.

A

B

C

D

31.RF Interface

32.RESERVED

33.Main Antenna Switcher

34.RESERVED

35.RESERVED

36.RESERVED

37.QFE2320(MMPA)

38.Circuit of MMPA

39.TRX_B1

40.TRX_B8

41.TRX_B5

42.TRX_B3/GSM1900

43.RESERVED

44.RESERVED

45.DRX LNA B3/B26

46.RESERVED

47.TRX_B41

48.RESERVED

49.RESERVED

50.RESERVED

51.DRX LNA B41/B1

52.DRX_B1/B3/B26

53.RESERVED

54.DRX_B41

55.DRX_ANT_SWITCH

56.WTR4905

57.RESERVED

58.ET_APT

A

B

C

D

1

2

3

4

5

6

该文档是极速PDF编辑器生成,如果想去掉该提示,请访问并下载:http://www.jisupdfeditor.com/�

1

2

3

4

5

6

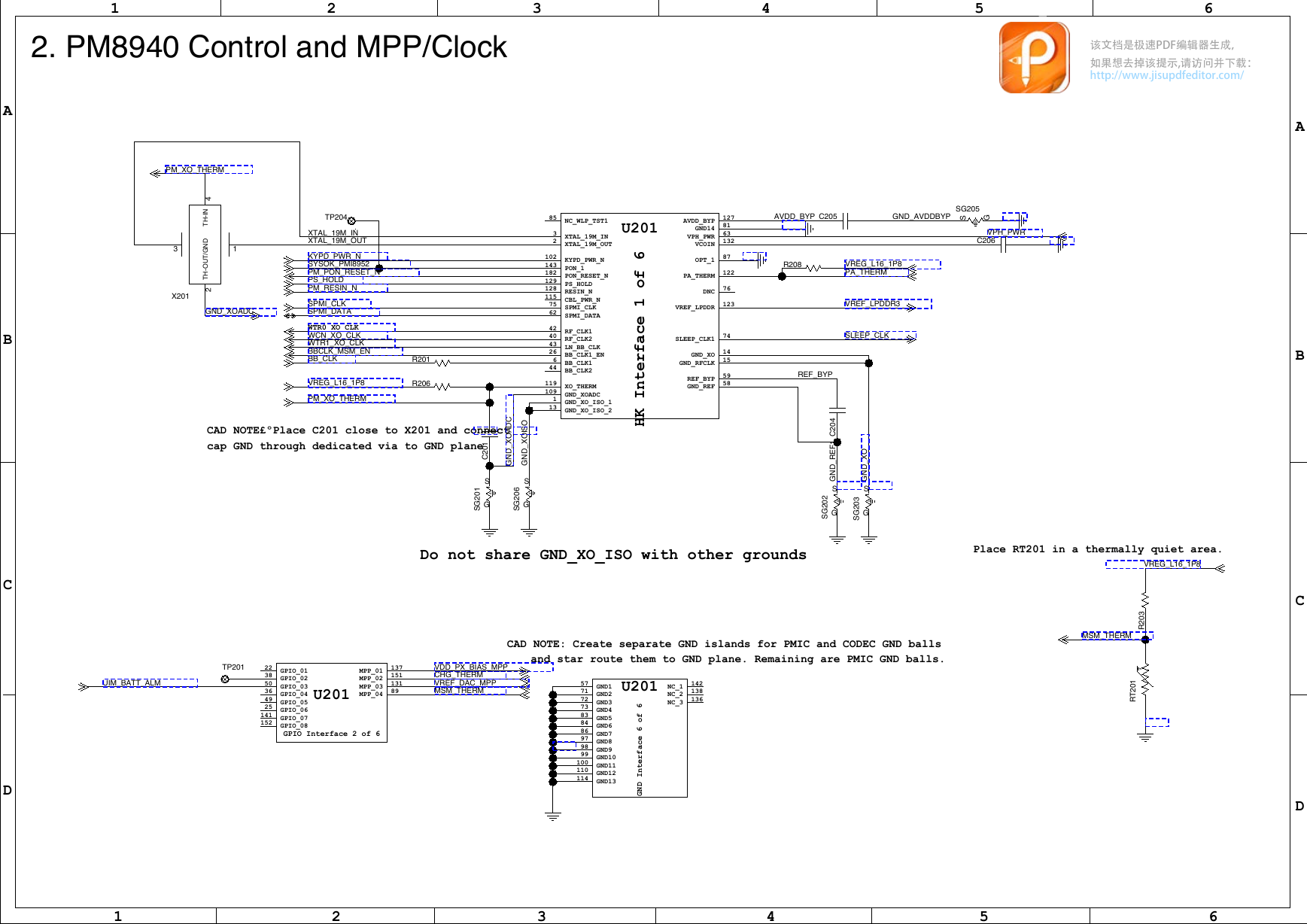

2. PM8940 Control and MPP/Clock

PM_XO_THERM

4

N

I

-

H

T

1

3

/

D

N

G

T

U

O

H

T

-

2

X201

GND_XOADC

TP204

XTAL_19M_IN

XTAL_19M_OUT

KYPD_PWR_N

SYSOK_PMI8952

PM_PON_RESET_N

PS_HOLD

PM_RESIN_N

SPMI_CLK

SPMI_DATA

WTR0_XO_CLK

WCN_XO_CLK

WTR1_XO_CLK

BBCLK_MSM_EN

BB_CLK

VREG_L16_1P8

PM_XO_THERM

R201

R206

C

D

CAD NOTE£ºPlace C201 close to X201 and connect

A

O

X

cap GND through dedicated via to GND plane

_

D

N

G

1

0

2

C

I

O

S

O

X

_

D

N

G

S

S

G

1

0

2

G

S

S

S

G

6

0

2

G

S

85

3

2

102

143

182

129

128

115

75

62

42

40

43

26

6

44

119

109

1

13

NC_WLP_TST1

XTAL_19M_IN

XTAL_19M_OUT

U201

KYPD_PWR_N

PON_1

PON_RESET_N

PS_HOLD

RESIN_N

CBL_PWR_N

SPMI_CLK

SPMI_DATA

RF_CLK1

RF_CLK2

LN_BB_CLK

BB_CLK1_EN

BB_CLK1

BB_CLK2

XO_THERM

GND_XOADC

GND_XO_ISO_1

GND_XO_ISO_2

6

f

o

1

e

c

a

f

r

e

t

n

I

K

H

AVDD_BYP

GND14

VPH_PWR

VCOIN

OPT_1

PA_THERM

DNC

VREF_LPDDR

SLEEP_CLK1

GND_XO

GND_RFCLK

REF_BYP

GND_REF

127

81

63

132

87

122

76

123

74

14

15

59

58

AVDD_BYP

C205

GND_AVDDBYP

SG205

S G

S

VPH_PWR

C206

R208

VREG_L16_1P8

PA_THERM

VREF_LPDDR3

SLEEP_CLK

REF_BYP

4

0

2

C

1

F

E

R

_

D

N

G

S

O

X

_

D

N

G

S

2

0

2

G

S

S

G

3

0

2

G

S

S

G

Do not share GND_XO_ISO with other grounds

Place RT201 in a thermally quiet area.

VREG_L16_1P8

CAD NOTE: Create separate GND islands for PMIC and CODEC GND balls

and star route them to GND plane. Remaining are PMIC GND balls.

3

0

2

R

MSM_THERM

T

1

0

2

T

R

UIM_BATT_ALM

TP201

MPP_01

MPP_02

MPP_03

MPP_04

22 GPIO_01

38

GPIO_02

50

GPIO_03

36

GPIO_04

49

GPIO_05

25

GPIO_06

141

GPIO_07

152

GPIO_08

GPIO Interface 2 of 6

U201

137

151

131

89

VDD_PX_BIAS_MPP

CHG_THERM

VREF_DAC_MPP

MSM_THERM

NC_1

NC_2

NC_3

142

138

136

57 GND1

71

GND2

72

GND3

73

GND4

83

GND5

84

GND6

86

GND7

97

GND8

98

GND9

99

GND10

100

GND11

110

GND12

114

GND13

U201

6

f

o

6

e

c

a

f

r

e

t

n

I

D

N

G

A

B

C

D

A

B

C

D

1

2

3

4

5

6

该文档是极速PDF编辑器生成,如果想去掉该提示,请访问并下载:http://www.jisupdfeditor.com/�

1

2

3

4

5

6

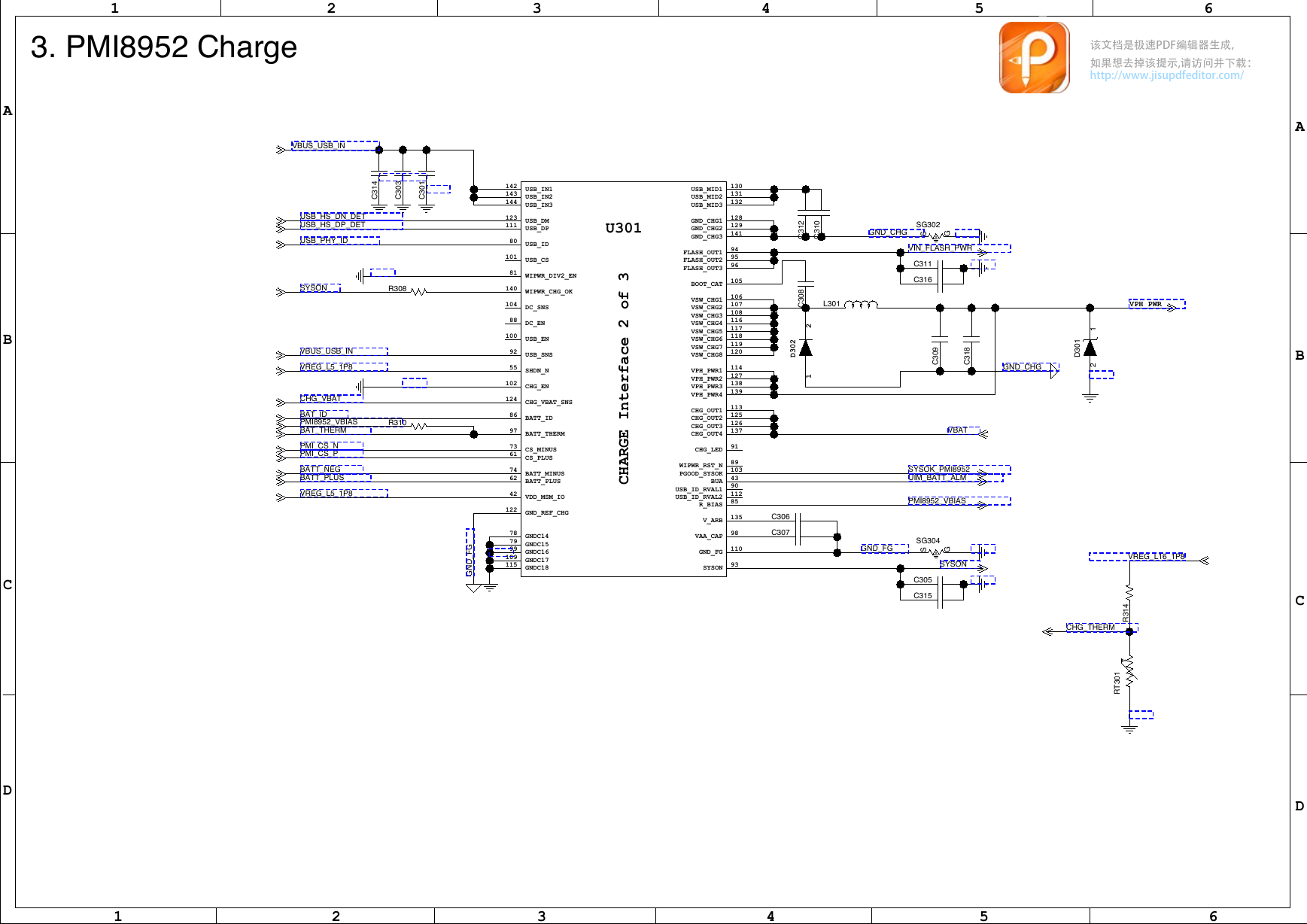

3. PMI8952 Charge

A

B

C

D

VBUS_USB_IN

USB_HS_DN_DET

USB_HS_DP_DET

USB_PHY_ID

SYSON

R308

VBUS_USB_IN

VREG_L5_1P8

CHG_VBAT

BAT_ID

PMI8952_VBIAS

BAT_THERM

PMI_CS_N

PMI_CS_P

BATT_NEG

BATT_PLUS

VREG_L5_1P8

R310

4

1

3

C

3

0

3

C

1

0

3

C

142 USB_IN1

143

USB_IN2

144

USB_IN3

U301

3

f

o

2

e

c

a

f

r

e

t

n

I

E

G

R

A

H

C

123

111

80

101

81

140

104

88

100

92

55

102

124

86

97

73

61

74

62

42

122

78

79

99

109

115

USB_DM

USB_DP

USB_ID

USB_CS

WIPWR_DIV2_EN

WIPWR_CHG_OK

DC_SNS

DC_EN

USB_EN

USB_SNS

SHDN_N

CHG_EN

CHG_VBAT_SNS

BATT_ID

BATT_THERM

CS_MINUS

CS_PLUS

BATT_MINUS

BATT_PLUS

VDD_MSM_IO

GND_REF_CHG

GNDC14

GNDC15

GNDC16

GNDC17

GNDC18

G

F

_

D

N

G

USB_MID1

USB_MID2

USB_MID3

GND_CHG1

GND_CHG2

GND_CHG3

FLASH_OUT1

FLASH_OUT2

FLASH_OUT3

BOOT_CAT

VSW_CHG1

VSW_CHG2

VSW_CHG3

VSW_CHG4

VSW_CHG5

VSW_CHG6

VSW_CHG7

VSW_CHG8

VPH_PWR1

VPH_PWR2

VPH_PWR3

VPH_PWR4

CHG_OUT1

CHG_OUT2

CHG_OUT3

CHG_OUT4

CHG_LED

WIPWR_RST_N

PGOOD_SYSOK

BUA

USB_ID_RVAL1

USB_ID_RVAL2

R_BIAS

V_ARB

VAA_CAP

GND_FG

SYSON

130

131

132

128

129

141

94

95

96

105

106

107

108

116

117

118

119

120

114

127

138

139

113

125

126

137

91

89

103

43

90

112

85

135

98

110

93

2

1

3

C

0

1

3

C

GND_CHG

SG302

S G

S

VIN_FLASH_PWR

C311

C316

8

0

3

C

L301

2

0

3

D

2

1

VPH_PWR

9

0

3

C

8

1

3

C

GND_CHG

1

0

3

D

1

2

C306

C307

GND_FG

VBAT

SYSOK_PMI8952

UIM_BATT_ALM

PMI8952_VBIAS

SG304

S G

S

SYSON

C305

C315

VREG_L16_1P8

4

1

3

R

CHG_THERM

T

1

0

3

T

R

A

B

C

D

1

2

3

4

5

6

该文档是极速PDF编辑器生成,如果想去掉该提示,请访问并下载:http://www.jisupdfeditor.com/�

1

2

3

4

5

6

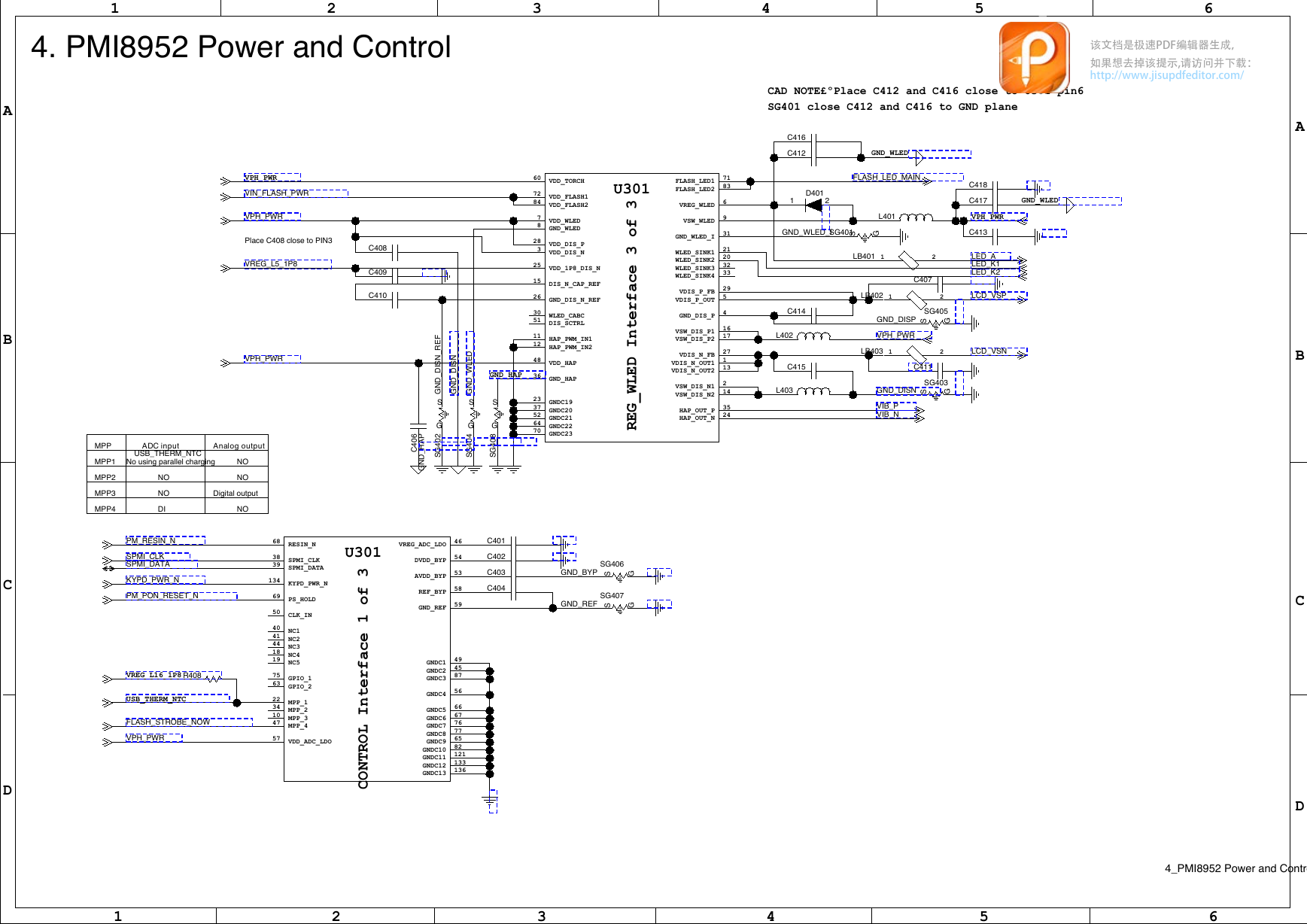

4. PMI8952 Power and Control

CAD NOTE£ºPlace C412 and C416 close to U301 pin6

SG401 close C412 and C416 to GND plane

VPH_PWR

VIN_FLASH_PWR

VPH_PWR

Place C408 close to PIN3

VREG_L5_1P8

C408

C409

C410

VPH_PWR

Analog output

60 VDD_TORCH

72

84

7

8

28

3

25

15

26

30

51

11

12

48

36

23

37

52

64

70

VDD_FLASH1

VDD_FLASH2

VDD_WLED

GND_WLED

VDD_DIS_P

VDD_DIS_N

VDD_1P8_DIS_N

DIS_N_CAP_REF

GND_DIS_N_REF

WLED_CABC

DIS_SCTRL

HAP_PWM_IN1

HAP_PWM_IN2

VDD_HAP

GND_HAP

GNDC19

GNDC20

GNDC21

GNDC22

GNDC23

U301

3

f

o

3

e

c

a

f

r

e

t

n

I

D

E

L

W

_

G

E

R

FLASH_LED1

FLASH_LED2

VREG_WLED

VSW_WLED

GND_WLED_I

WLED_SINK1

WLED_SINK2

WLED_SINK3

WLED_SINK4

VDIS_P_FB

VDIS_P_OUT

GND_DIS_P

VSW_DIS_P1

VSW_DIS_P2

VDIS_N_FB

VDIS_N_OUT1

VDIS_N_OUT2

VSW_DIS_N1

VSW_DIS_N2

HAP_OUT_P

HAP_OUT_N

71

83

6

9

31

21

20

32

33

29

5

4

16

17

27

1

13

2

14

35

24

I

F

E

R

_

N

S

D

_

D

N

G

S

I

N

S

D

_

D

N

G

D

E

L

W

_

D

N

G

S

GND_HAP

S

S

S

S

G

2

0

4

G

S

6

0

4

C

P

A

H

_

D

N

G

G

4

0

4

G

S

G

8

0

4

G

S

C416

C412

D401

2

1

GND_WLED

FLASH_LED_MAIN

L401

GND_WLED_I

SG401S G

S

LB401

1

2

C407

GND_WLED

C418

C417

VPH_PWR

C413

LED_A

LED_K1

LED_K2

C414

L402

C415

L403

LB402

1

2

LCD_VSP

SG405

S G

S

GND_DISP

VPH_PWR

LB403

1

2

LCD_VSN

C411

GND_DISN

SG403

S G

S

VIB_P

VIB_N

USB_THERM_NTC

No using parallel charging

NO

NO

MPP

MPP1

MPP2

MPP3

MPP4

ADC input

NO

NO

DI

PM_RESIN_N

SPMI_CLK

SPMI_DATA

KYPD_PWR_N

PM_PON_RESET_N

VREG_L16_1P8

R408

USB_THERM_NTC

FLASH_STROBE_NOW

VPH_PWR

C401

C402

C403

C404

GND_BYP

SG406

S G

S

GND_REF

SG407

S G

S

Digital output

NO

68 RESIN_N

38

39

134

SPMI_CLK

SPMI_DATA

KYPD_PWR_N

69

50

40

41

44

18

19

75

63

22

34

10

47

57

PS_HOLD

CLK_IN

NC1

NC2

NC3

NC4

NC5

GPIO_1

GPIO_2

MPP_1

MPP_2

MPP_3

MPP_4

VDD_ADC_LDO

VREG_ADC_LDO

DVDD_BYP

AVDD_BYP

REF_BYP

GND_REF

GNDC1

GNDC2

GNDC3

GNDC4

GNDC5

GNDC6

GNDC7

GNDC8

GNDC9

GNDC10

GNDC11

GNDC12

GNDC13

46

54

53

58

59

49

45

87

56

66

67

76

77

65

82

121

133

136

U301

3

f

o

1

e

c

a

f

r

e

t

n

I

L

O

R

T

N

O

C

A

B

C

D

A

B

C

D

1

2

3

4

5

6

4_PMI8952 Power and Control

该文档是极速PDF编辑器生成,如果想去掉该提示,请访问并下载:http://www.jisupdfeditor.com/�

1

2

3

4

5

6

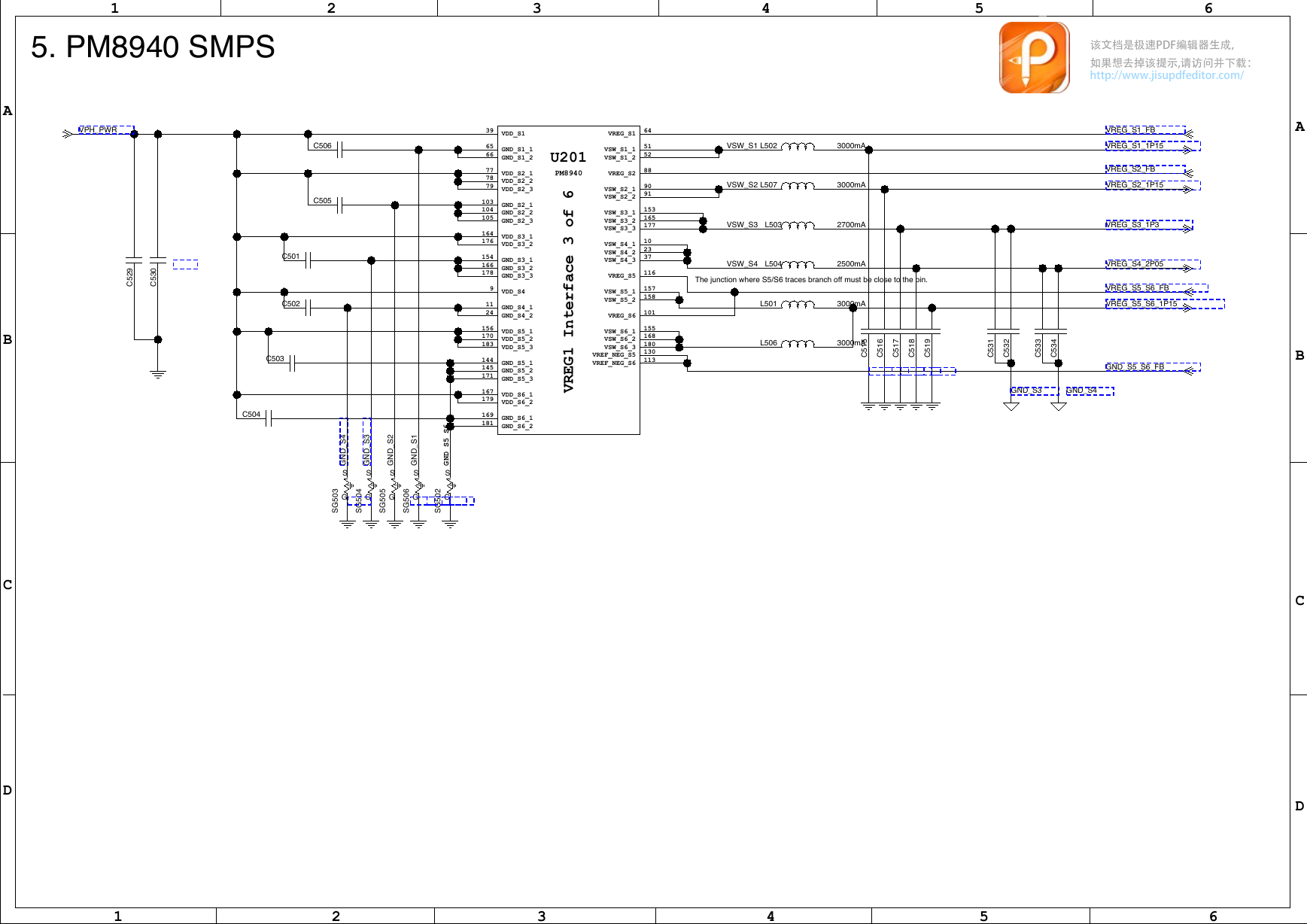

VREG_S1

VSW_S1_1

VSW_S1_2

VREG_S2

VSW_S2_1

VSW_S2_2

VSW_S3_1

VSW_S3_2

VSW_S3_3

VSW_S4_1

VSW_S4_2

VSW_S4_3

VREG_S5

VSW_S5_1

VSW_S5_2

VREG_S6

VSW_S6_1

VSW_S6_2

VSW_S6_3

VREF_NEG_S5

VREF_NEG_S6

64

51

52

88

90

91

153

165

177

10

23

37

116

157

158

101

155

168

180

130

113

U201

PM8940

6

f

o

3

e

c

a

f

r

e

t

n

I

1

G

E

R

V

39

VDD_S1

65 GND_S1_1

66

GND_S1_2

77

78

79

103

104

105

164

176

154

166

178

9

11

24

156

170

183

144

145

171

167

179

169

181

VDD_S2_1

VDD_S2_2

VDD_S2_3

GND_S2_1

GND_S2_2

GND_S2_3

VDD_S3_1

VDD_S3_2

GND_S3_1

GND_S3_2

GND_S3_3

VDD_S4

GND_S4_1

GND_S4_2

VDD_S5_1

VDD_S5_2

VDD_S5_3

GND_S5_1

GND_S5_2

GND_S5_3

VDD_S6_1

VDD_S6_2

GND_S6_1

GND_S6_2

VSW_S1

L502

3000mA

VSW_S2

L507

3000mA

VSW_S3

L503

2700mA

VSW_S4

L504

2500mA

The junction where S5/S6 traces branch off must be close to the pin.

L501

L506

3000mA

3000mA

5

1

5

C

6

1

5

C

7

1

5

C

8

1

5

C

9

1

5

C

1

3

5

C

2

3

5

C

3

3

5

C

4

3

5

C

VREG_S1_FB

VREG_S1_1P15

VREG_S2_FB

VREG_S2_1P15

VREG_S3_1P3

VREG_S4_2P05

VREG_S5_S6_FB

VREG_S5_S6_1P15

GND_S5_S6_FB

GND_S3

GND_S4

5. PM8940 SMPS

VPH_PWR

9

2

5

C

0

3

5

C

C506

C505

C501

C502

C503

C504

4

S

_

D

N

G

S

3

S

_

D

N

G

S

2

S

_

D

N

G

S

1

S

_

D

N

G

S

6

S

_

5

S

_

D

N

G

S

S

S

S

S

S

G

3

0

5

G

S

G

4

0

5

G

S

G

5

0

5

G

S

G

6

0

5

G

S

G

2

0

5

G

S

A

B

C

D

A

B

C

D

1

2

3

4

5

6

该文档是极速PDF编辑器生成,如果想去掉该提示,请访问并下载:http://www.jisupdfeditor.com/�

1

2

3

4

5

6

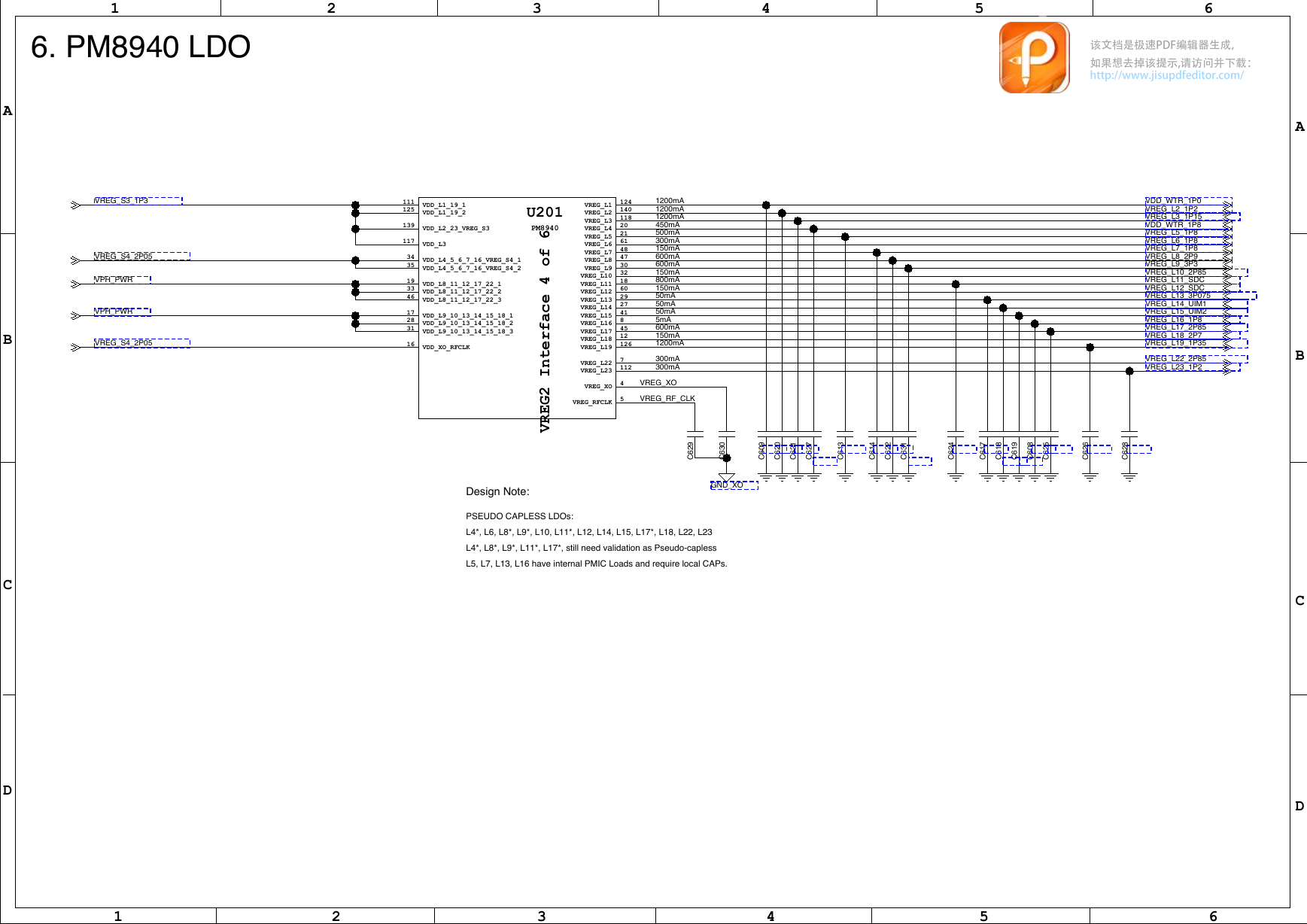

6. PM8940 LDO

A

B

C

D

VREG_S3_1P3

VREG_S4_2P05

VPH_PWR

VPH_PWR

VREG_S4_2P05

111 VDD_L1_19_1

125

VDD_L1_19_2

139

117

34

35

19

33

46

17

28

31

16

VDD_L2_23_VREG_S3

VDD_L3

VDD_L4_5_6_7_16_VREG_S4_1

VDD_L4_5_6_7_16_VREG_S4_2

VDD_L8_11_12_17_22_1

VDD_L8_11_12_17_22_2

VDD_L8_11_12_17_22_3

VDD_L9_10_13_14_15_18_1

VDD_L9_10_13_14_15_18_2

VDD_L9_10_13_14_15_18_3

VDD_XO_RFCLK

VREG_L1

VREG_L2

VREG_L3

VREG_L4

VREG_L5

VREG_L6

VREG_L7

VREG_L8

VREG_L9

VREG_L10

VREG_L11

VREG_L12

VREG_L13

VREG_L14

VREG_L15

VREG_L16

VREG_L17

VREG_L18

VREG_L19

VREG_L22

VREG_L23

VREG_XO

VREG_RFCLK

124

140

118

20

21

61

48

47

30

32

18

60

29

27

41

8

45

12

126

7

112

4

5

U201

PM8940

6

f

o

4

e

c

a

f

r

e

t

n

I

2

G

E

R

V

1200mA

1200mA

1200mA

450mA

500mA

300mA

150mA

600mA

600mA

150mA

800mA

150mA

50mA

50mA

50mA

5mA

600mA

150mA

1200mA

300mA

300mA

VREG_XO

VREG_RF_CLK

9

2

6

C

0

3

6

C

9

0

6

C

0

2

6

C

1

2

6

C

7

2

6

C

3

1

6

C

4

1

6

C

2

2

6

C

1

3

6

C

4

2

6

C

7

1

6

C

8

1

6

C

9

1

6

C

8

0

6

C

5

2

6

C

6

2

6

C

8

2

6

C

Design Note:

PSEUDO CAPLESS LDOs:

GND_XO

L4*, L6, L8*, L9*, L10, L11*, L12, L14, L15, L17*, L18, L22, L23

L4*, L8*, L9*, L11*, L17*, still need validation as Pseudo-capless

L5, L7, L13, L16 have internal PMIC Loads and require local CAPs.

VDD_WTR_1P0

VREG_L2_1P2

VREG_L3_1P15

VDD_WTR_1P8

VREG_L5_1P8

VREG_L6_1P8

VREG_L7_1P8

VREG_L8_2P9

VREG_L9_3P3

VREG_L10_2P85

VREG_L11_SDC

VREG_L12_SDC

VREG_L13_3P075

VREG_L14_UIM1

VREG_L15_UIM2

VREG_L16_1P8

VREG_L17_2P85

VREG_L18_2P7

VREG_L19_1P35

VREG_L22_2P85

VREG_L23_1P2

A

B

C

D

1

2

3

4

5

6

该文档是极速PDF编辑器生成,如果想去掉该提示,请访问并下载:http://www.jisupdfeditor.com/�

5

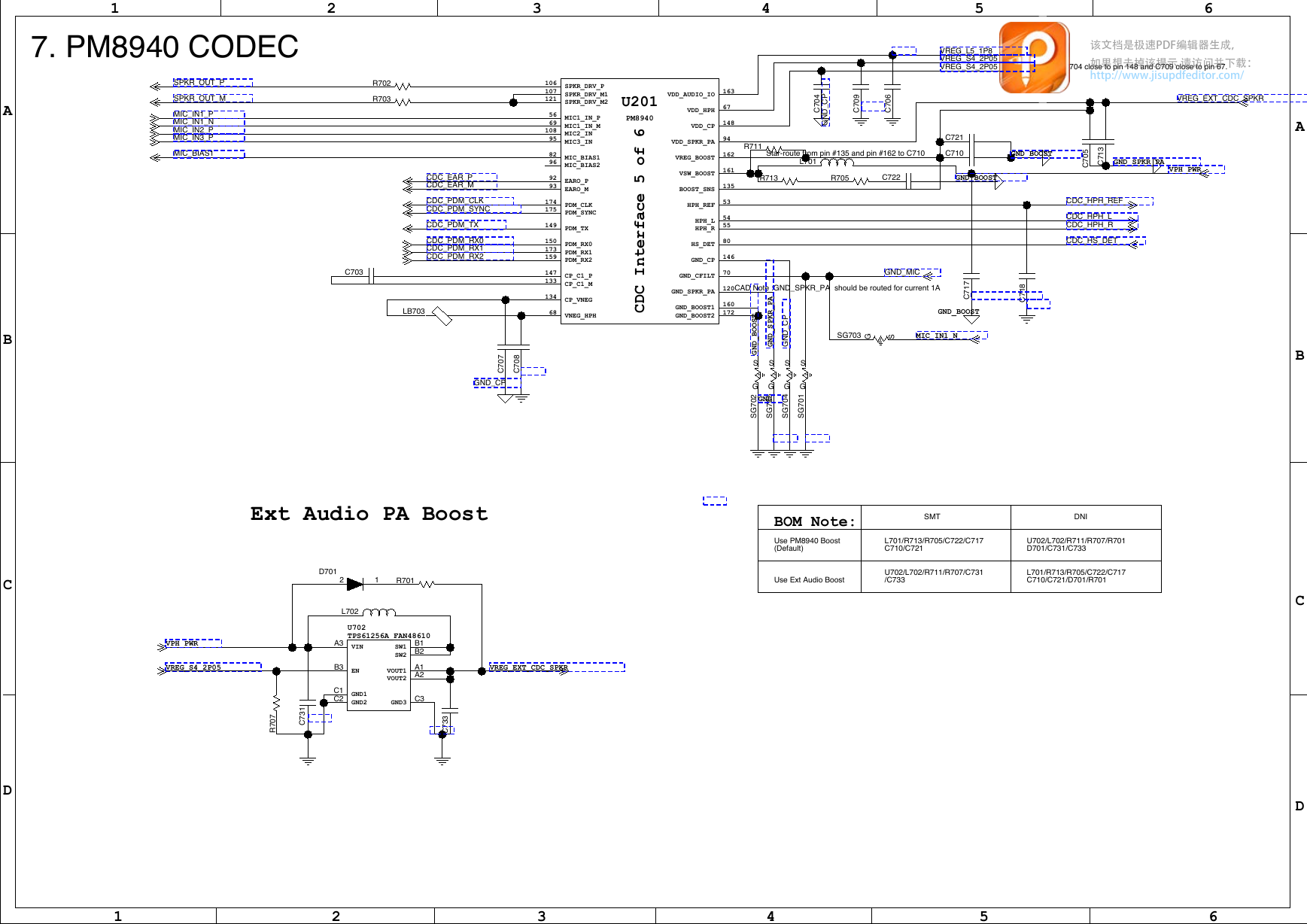

VREG_L5_1P8

VREG_S4_2P05

VREG_S4_2P05

6

Place C704 close to pin 148 and C709 close to pin 67.

VREG_EXT_CDC_SPKR

4

0

7

C

P

C

_

D

N

G

9

0

7

C

6

0

7

C

R711

Star-route from pin #135 and pin #162 to C710

L701

C721

C710

R713

R705

C722

GND_BOOST

GND_BOOST

5

0

7

C

3

1

7

C

GND_SPKR_PA

VPH_PWR

CDC_HPH_REF

CDC_HPH_L

CDC_HPH_R

CDC_HS_DET

7

1

7

C

8

1

7

C

120

CAD Note :GND_SPKR_PA should be routed for current 1A

GND_MIC

GND_BOOST1

GND_BOOST2

160

172

A

P

_

R

K

P

S

_

D

N

G

P

C

_

D

N

G

S

S

S

T

S

O

O

B

_

D

N

G

S

S

S

S

S

GND_BOOST

SG703

SG

S

MIC_IN1_N

G

2

0

7

G

S

G

5

GND

0

7

G

S

G

4

0

7

G

S

G

1

0

7

G

S

BOM Note:

Use PM8940 Boost

(Default)

SMT

DNI

L701/R713/R705/C722/C717

C710/C721

U702/L702/R711/R707/R701

D701/C731/C733

Use Ext Audio Boost

U702/L702/R711/R707/C731

/C733

L701/R713/R705/C722/C717

C710/C721/D701/R701

1

2

3

4

163

67

148

94

162

161

135

53

54

55

80

146

70

VDD_AUDIO_IO

VDD_HPH

VDD_CP

VDD_SPKR_PA

VREG_BOOST

VSW_BOOST

BOOST_SNS

HPH_REF

HPH_L

HPH_R

HS_DET

GND_CP

GND_CFILT

GND_SPKR_PA

106

107

121

56

69

108

95

82

96

92

93

174

175

149

150

173

159

147

133

134

68

SPKR_DRV_P

SPKR_DRV_M1

SPKR_DRV_M2

MIC1_IN_P

MIC1_IN_M

MIC2_IN

MIC3_IN

MIC_BIAS1

MIC_BIAS2

EARO_P

EARO_M

PDM_CLK

PDM_SYNC

PDM_TX

PDM_RX0

PDM_RX1

PDM_RX2

CP_C1_P

CP_C1_M

CP_VNEG

VNEG_HPH

U201

PM8940

6

f

o

5

e

c

a

f

r

e

t

n

I

C

D

C

7. PM8940 CODEC

SPKR_OUT_P

SPKR_OUT_M

MIC_IN1_P

MIC_IN1_N

MIC_IN2_P

MIC_IN3_P

MIC_BIAS1

R702

R703

CDC_EAR_P

CDC_EAR_M

CDC_PDM_CLK

CDC_PDM_SYNC

CDC_PDM_TX

CDC_PDM_RX0

CDC_PDM_RX1

CDC_PDM_RX2

C703

LB703

7

0

7

C

8

0

7

C

GND_CP

Ext Audio PA Boost

D701

2

1

R701

L702

A

B

C

D

VPH_PWR

VREG_S4_2P05

1

3

7

C

7

0

7

R

A3

B3

C1

C2

2

1

U702

TPS61256A_FAN48610

VIN

B1

B2

SW1

SW2

VREG_EXT_CDC_SPKR

EN

GND1

GND2

VOUT1

VOUT2

GND3

A1

A2

C3

3

3

7

C

3

4

5

6

A

B

C

D

该文档是极速PDF编辑器生成,如果想去掉该提示,请访问并下载:http://www.jisupdfeditor.com/�

1

2

3

4

5

6

8. MSM8940 Control

A

B

C

D

BB_CLK

BBCLK_MSM_EN

SLEEP_CLK

PM_PON_RESET_N

MSM_RESOUT_N

C807

PS_HOLD

JTAG_RESOUT_N

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

JTAG_TRST_N

VREF_LPDDR3

TP801

TP802

3

0

8

C

BD13 WLAN_XO

AA40

W40

AR40

CXO

CXO_EN

SLEEP_CLK

AH37

BA4

RESIN_N

RESOUT_N

T37

U38

Y39

Y3

AB3

AB1

Y1

AC2

AA2

G14

MODE_0

MODE_1

PS_HOLD

SRST_N

TCK

TDI

TDO

TMS

TRST_N

EBI_VREF

AF39

R2

R40

T39

GND1

DNC1

DNC2

DNC3

U801

SDC1_RCLK

SDC1_CLK

SDC1_CMD

2

1

f

o

1

e

c

a

f

r

e

t

n

I

1

C

S

I

M

SDC1_DATA_0

SDC1_DATA_1

SDC1_DATA_2

SDC1_DATA_3

SDC1_DATA_4

SDC1_DATA_5

SDC1_DATA_6

SDC1_DATA_7

SDC2_CLK

SDC2_CMD

SDC2_DATA_0

SDC2_DATA_1

SDC2_DATA_2

SDC2_DATA_3

USB_HS_DM

USB_HS_DP

USB_HS_ID

USB_HS_REXT

USB_HS_VBUS

SPMI_CLK

SPMI_DATA

L38

G38

H39

G40

H37

E38

J40

F37

F39

J38

K37

W4

U4

W2

V1

V3

U2

AE40

AD39

AB39

AC38

AC40

AH39

AG40

CAD NOTE: Place R802 close to MSM pin

R802

SDC1_RCLK

SDC1_CLK

SDC1_CMD

SDC1_DATA_0

SDC1_DATA_1

SDC1_DATA_2

SDC1_DATA_3

SDC1_DATA_4

SDC1_DATA_5

SDC1_DATA_6

SDC1_DATA_7

CAD NOTE: Place R808 resistor close to MSM

R808

R805

SDC2_SDCARD_CLK

SDC2_SDCARD_CMD

R803

R804

R806

R807

SDC2_SDCARD_D0

SDC2_SDCARD_D1

SDC2_SDCARD_D2

SDC2_SDCARD_D3

SOC_USB_DN

SOC_USB_DP

USB_HS_REXT

R801

CAD NOTE: Place R801 resistor close to MSM

SPMI_CLK

SPMI_DATA

4

0

8

C

5

0

8

C

CAD NOTE: SPMI should be well shielding and protected from MSM to PM/PMI side

please star routing SPMI_CLK/DATA from MSM to PM/PMI respectively

1

2

3

4

5

6

A

B

C

D

该文档是极速PDF编辑器生成,如果想去掉该提示,请访问并下载:http://www.jisupdfeditor.com/�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc