低功耗HART调制解调器

AD5700/AD5700-1

产品特性

HART兼容完全集成FSK调制解调器

1200 Hz和2200 Hz正弦偏移频率

接收模式下最大电源电流为115 �A

适合本质安全型应用集成了接收带通滤波器

所需外部元件极少

针对各种系统配置进行时钟优化

超低功耗晶振(最大值为60 �A)

外部CMOS时钟源

集成精密振荡器(仅限AD5700-1)

缓冲HART输出—额外驱动能力

8 kV HBM ESD额定值

2 V至5.5 V电源供电

1.71 V至5.5 V接口

工作温度范围:-40℃至+125℃

封装:4 mm x 4 mm LFCSP

兼容HART物理层

UART接口

应用

现场发射机

HART多路复用器

PLC和DCS模拟I/O模块

HART网络连接

概述

AD5700/AD5700-1均 为 单 芯 片 解 决 方 案 , 设 计 用 作

HART®FSK半双工调制解调器,符合HART物理层要求。

这些器件集成所有必要的滤波、信号检测、调制、解调和

信号生成功能,因此所需外部元件极少。AD5700-1上集成

0.5%精密振荡器,可极大节省电路板空间,因此非常适合

主机和从机配置下的线路供电应用。AD5700/AD5700-1的

最大电源功耗为115 �A,因此是低功耗环路供电型应用的最

佳选择。发射波形为相位连续1200 Hz和2200 Hz正弦波。

AD5700/AD5700-1内 置 精 密 载 波 检 测 电 路 , 采 用 标 准

UART接口。

表1. 相关产品

产品型号 描述

AD5755-1

四通道、16位、串行输入、

4 mA至20 mA和电压输出DAC,

提供动态电源控制和HART连接

16位、串行输入、环路供电、4 mA至20 mA DAC

单通道、12/16位、串行输入、

4 mA至20 mA电流源DAC

单通道、12/16位、串行输入、

内置电流源和电压输出DAC

AD5421

AD5410/

AD5420

AD5412/

AD5422

REG_CAP

CLKOUT

XTAL1

XTAL2

XTAL_EN

VCC

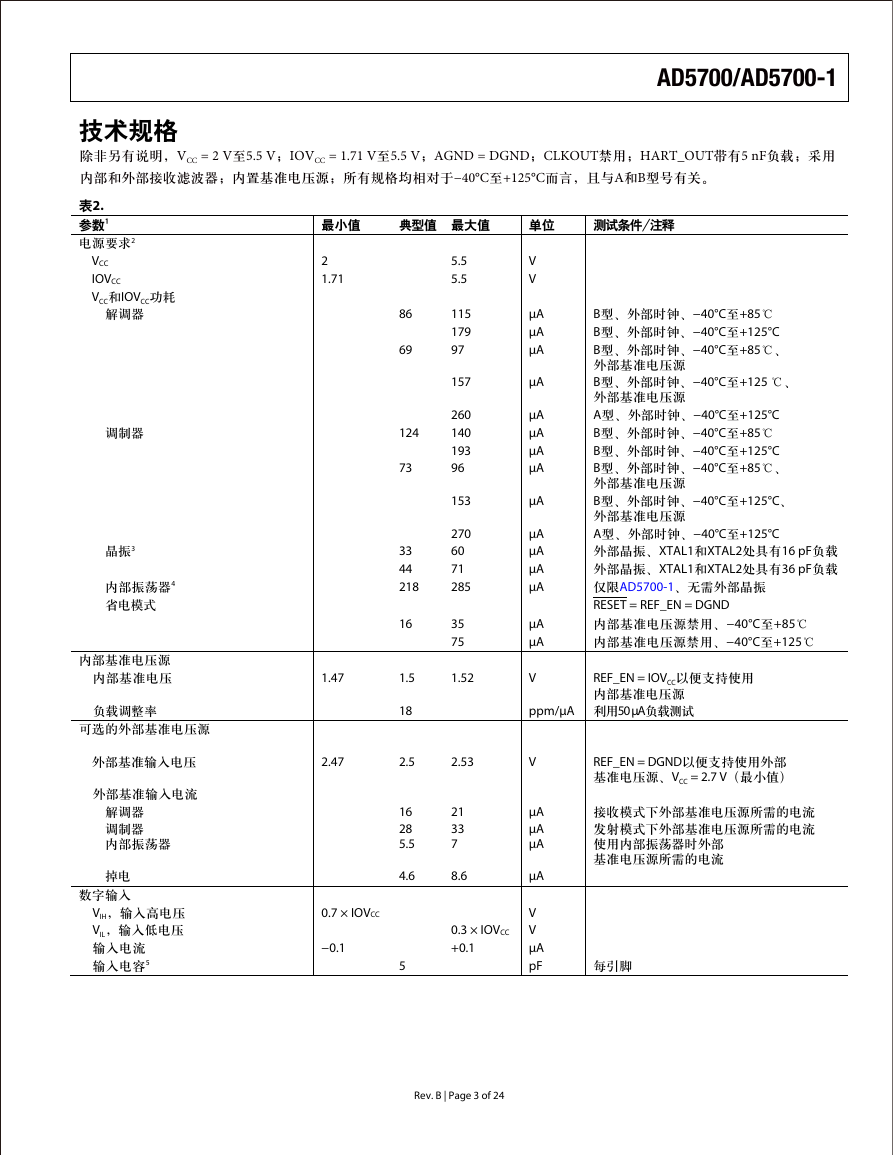

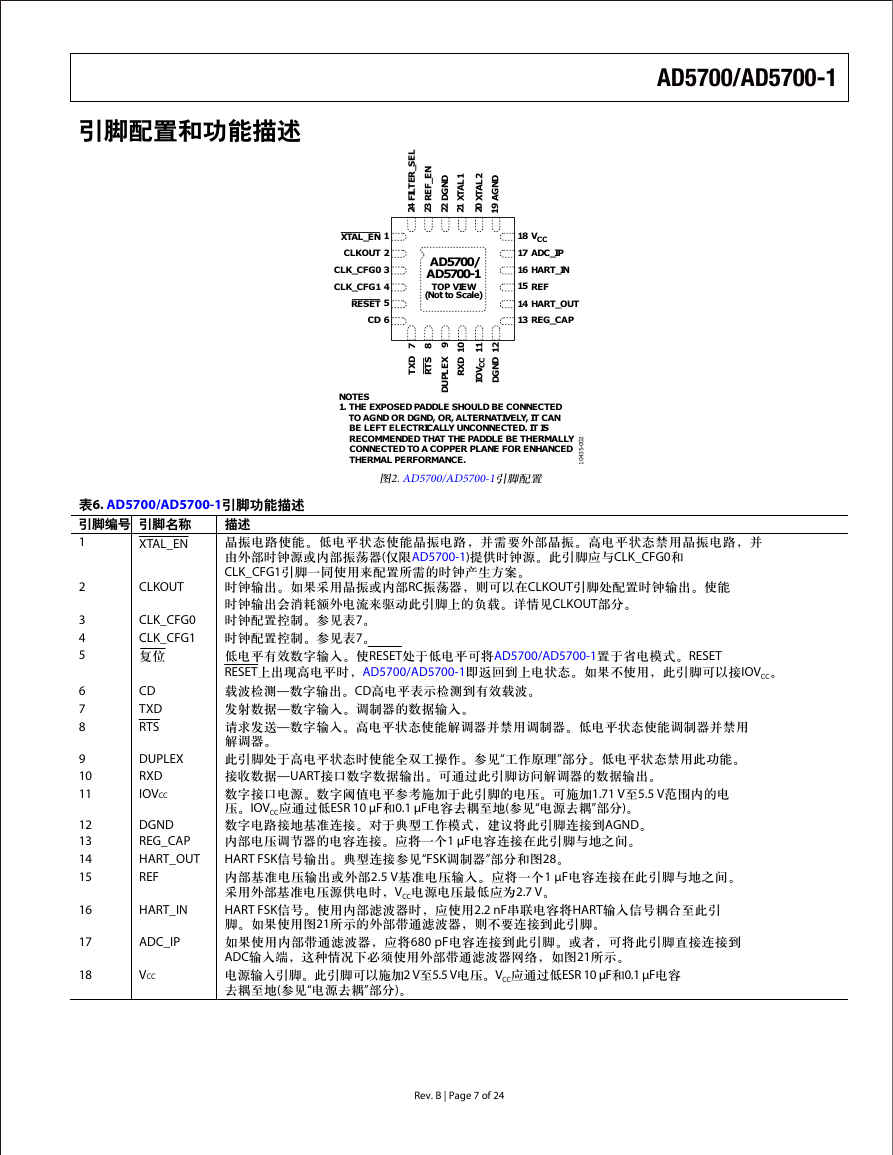

功能框图

IOVCC

DUPLEX

CD

RXD

TXD

RTS

CLK_CFG0

CLK_CFG1

OSC

AD5700/AD5700-1

FSK

MODULATOR

FSK

DEMODULATOR

DAC

ADC

BUFFER

BAND-PASS

FILTER AND

BIASING

HART_OUT

ADC_IP

HART_IN

I

C

G

O

L

L

O

R

T

N

O

C

RESET

DGND

VOLTAGE

REFERENCE

REF REF_EN

图1

AGND

FILTER_SEL

1

0

0

-

5

3

4

0

1

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

rights of third parties that may result from its use. Specications subject to change without notice. No

www.analog.com

Tel: 781.329.4700

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

©2012 Analog Devices, Inc. All rights reserved.

Fax: 781.461.3113

Trademarks and registered trademarks are the property of their respective owners.

ADI中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI不对翻译中存在的差异或由此产生的错误负责。如需确认任何词语的准确性,请参考ADI提供

的最新英文版数据手册。

�

AD5700/AD5700-1

目录

产品特性...........................................................................................1

应用....................................................................................................1

概述....................................................................................................1

功能框图...........................................................................................1

修订历史...........................................................................................2

技术规格...........................................................................................3

时序特性......................................................................................5

绝对最大额定值..............................................................................6

热阻 ..............................................................................................6

ESD警告.......................................................................................6

引脚配置和功能描述.....................................................................7

典型性能参数 ..................................................................................9

术语..................................................................................................12

工作原理.........................................................................................13

FSK调制器.................................................................................13

连接到HART_OUT.................................................................14

FSK解调器.................................................................................14

连接到HART_IN或ADC_IP..................................................14

时钟配置....................................................................................15

电源电流计算...........................................................................16

省电模式....................................................................................16

全双工操作 ...............................................................................16

应用信息.........................................................................................17

电源去耦....................................................................................17

瞬变电压保护...........................................................................17

典型连接图 ...............................................................................18

外形尺寸.........................................................................................21

订购指南....................................................................................21

修订历史

2012年7月—修订版A至修订版B

删除表2中的VCC和IOVCC功耗文本.............................................3

表2增加内部振荡器和外部时钟参数.........................................4

更改表3的t2描述和尾注2 ..............................................................5

更改表6的IOVCC描述.....................................................................7

增加“电源电流计算”部分 ...........................................................16

增加“瞬变电压保护”部分、图26和图27;重新排序 ...........17

更改“典型连接图”部分................................................................18

更改图29 .........................................................................................19

更改图30 .........................................................................................20

更新外形尺寸 ................................................................................21

2012年4月—修订版0至修订版A

更改表2中的发射阻抗参数(RTS低电平).............................4

更改图3、图4、图5和图7.............................................................9

更改图10和图11 ............................................................................10

通篇将AD5755更改为AD5755-1 ...............................................17

更改图27 .........................................................................................18

2012年2月—修订版0:初始版

Rev. B | Page 2 of 24

�

AD5700/AD5700-1

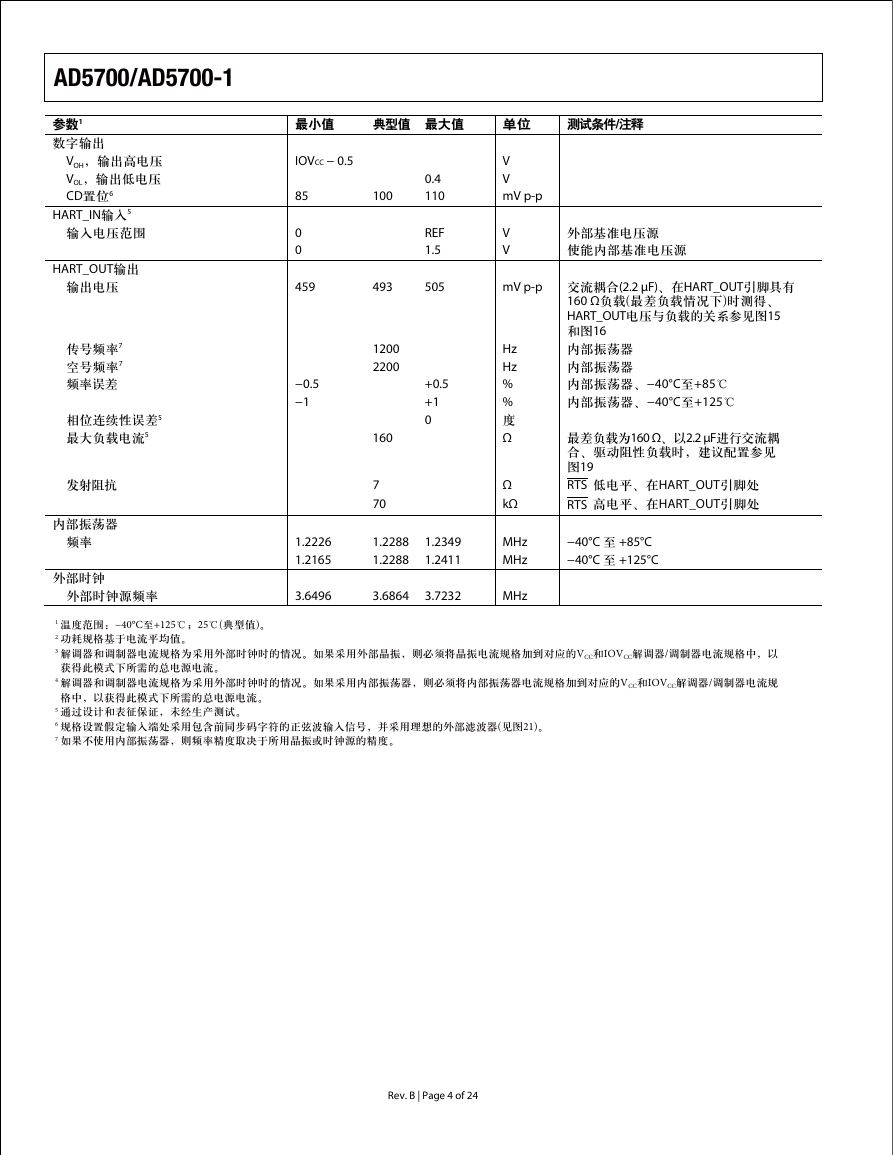

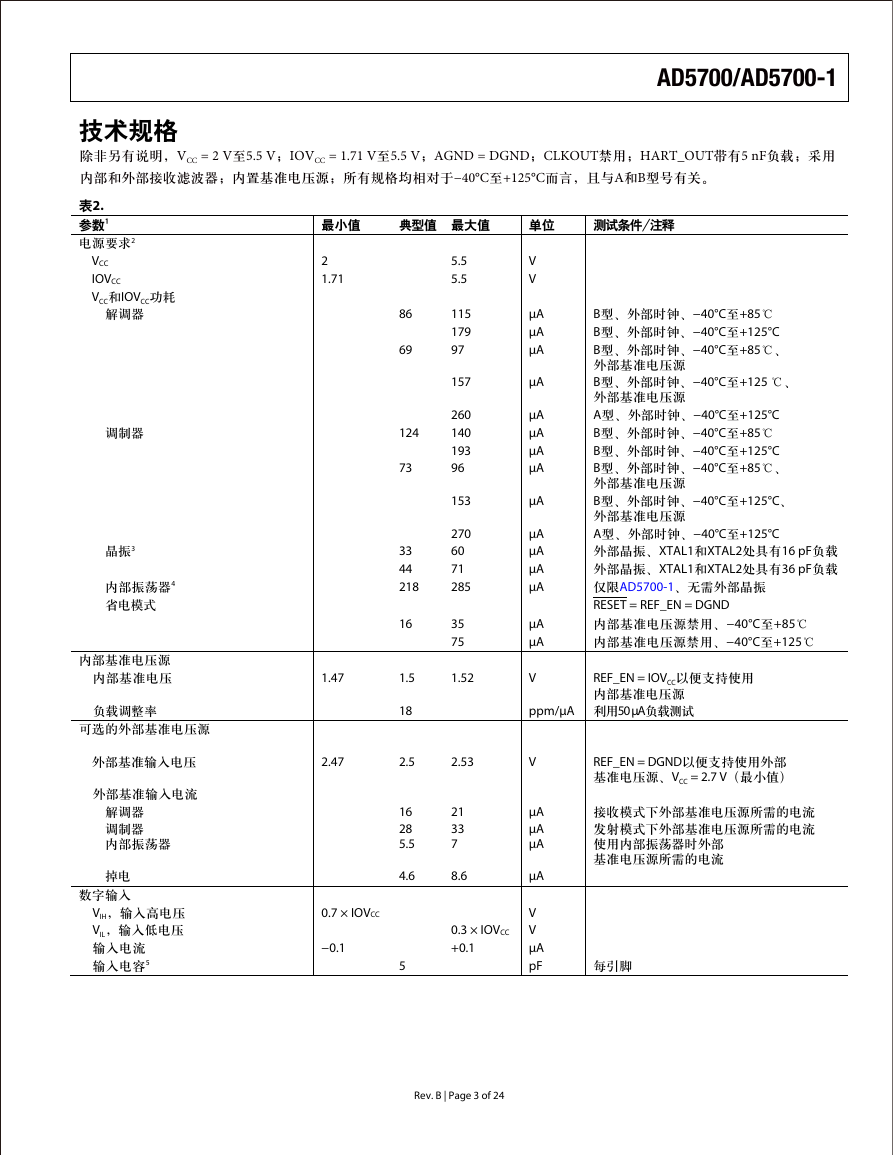

技术规格

除非另有说明,VCC = 2 V至5.5 V;IOVCC = 1.71 V至5.5 V;AGND = DGND;CLKOUT禁用;HART_OUT带有5 nF负载;采用

内部和外部接收滤波器;内置基准电压源;所有规格均相对于−40°C至+125°C而言,且与A和B型号有关。

表2.

参数1

电源要求2

VCC

IOVCC

VCC和IOVCC功耗

解调器

调制器

晶振3

内部振荡器4

省电模式

内部基准电压源

内部基准电压

负载调整率

可选的外部基准电压源

外部基准输入电压

外部基准输入电流

解调器

调制器

内部振荡器

掉电

数字输入

VIH,输入高电压

VIL,输入低电压

输入电流

输入电容5

单位

V

V

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

V

测试条件/注释

B型、外部时钟、−40°C至+85℃

B型、外部时钟、−40°C至+125°C

B型、外部时钟、−40°C至+85℃、

外部基准电压源

B型、外部时钟、−40°C至+125 ℃、

外部基准电压源

A型、外部时钟、−40°C至+125°C

B型、外部时钟、−40°C至+85℃

B型、外部时钟、−40°C至+125°C

B型、外部时钟、−40°C至+85℃、

外部基准电压源

B型、外部时钟、−40°C至+125°C、

外部基准电压源

A型、外部时钟、−40°C至+125°C

外部晶振、XTAL1和XTAL2处具有16 pF负载

外部晶振、XTAL1和XTAL2处具有36 pF负载

仅限AD5700-1、无需外部晶振

RESET = REF_EN = DGND

内部基准电压源禁用、−40°C至+85℃

内部基准电压源禁用、−40°C至+125℃

REF_EN = IOVCC以便支持使用

内部基准电压源

ppm/µA 利用50 �A负载测试

V

µA

µA

µA

µA

V

V

µA

pF

REF_EN = DGND以便支持使用外部

基准电压源、VCC = 2.7 V(最小值)

接收模式下外部基准电压源所需的电流

发射模式下外部基准电压源所需的电流

使用内部振荡器时外部

基准电压源所需的电流

每引脚

最小值

2

1.71

典型值 最大值

86

69

5.5

5.5

115

179

97

1.47

2.47

0.7 × IOVCC

−0.1

124

73

33

44

218

16

1.5

18

2.5

16

28

5.5

4.6

5

157

260

140

193

96

153

270

60

71

285

35

75

1.52

2.53

21

33

7

8.6

0.3 × IOVCC

+0.1

Rev. B | Page 3 of 24

�

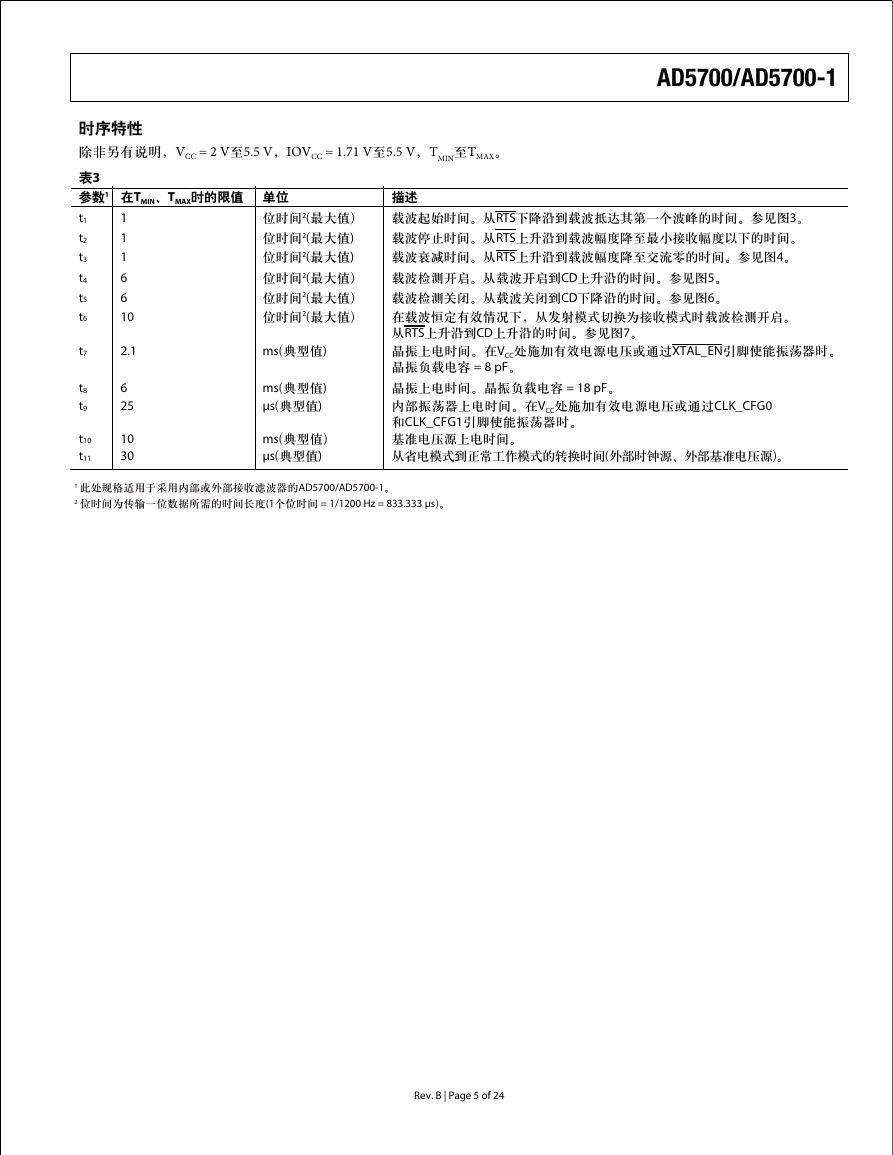

AD5700/AD5700-1

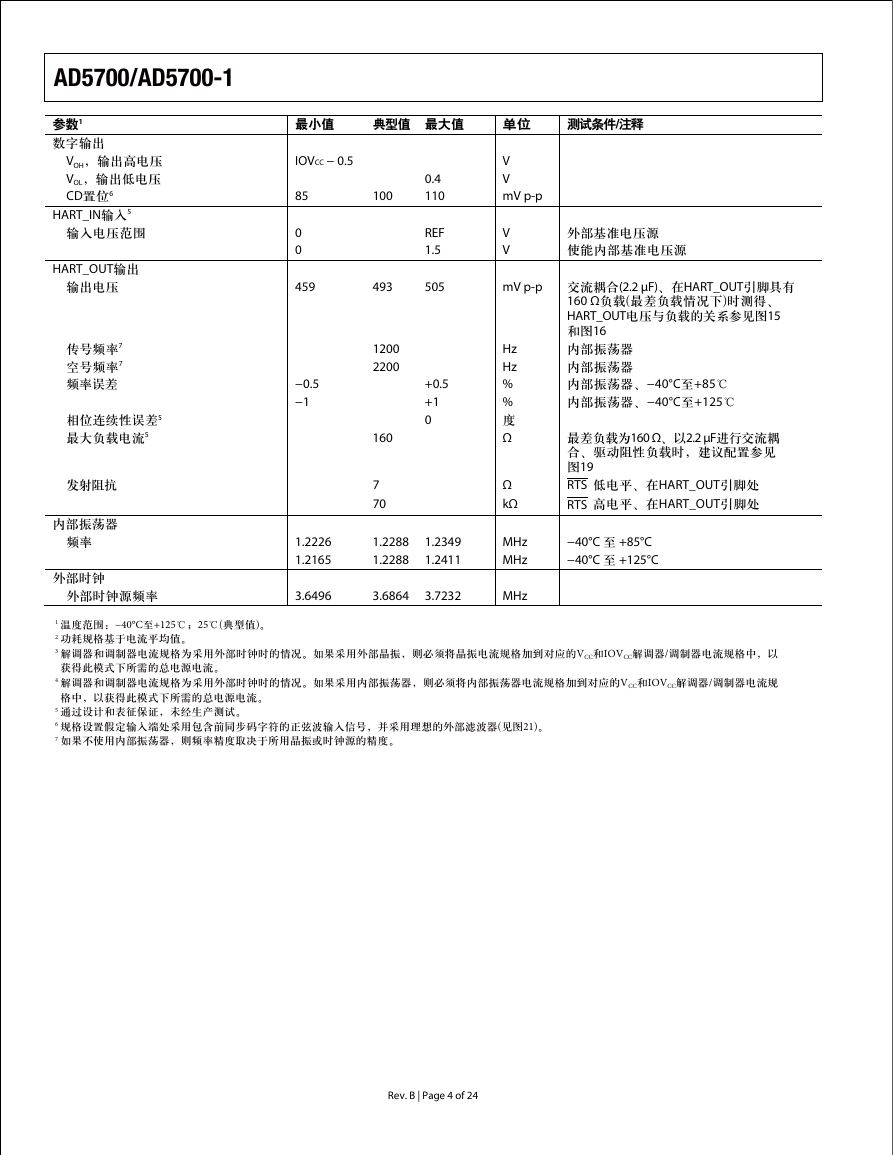

参数1

数字输出

VOH,输出高电压

VOL,输出低电压

CD置位6

HART_IN输入5

输入电压范围

HART_OUT输出

输出电压

传号频率7

空号频率7

频率误差

相位连续性误差5

最大负载电流5

发射阻抗

内部振荡器

频率

外部时钟

外部时钟源频率

最小值

IOVCC − 0.5

85

0

0

459

典型值

100

493

最大值

0.4

110

REF

1.5

505

−0.5

−1

1.2226

1.2165

3.6496

1200

2200

160

+0.5

+1

0

7

70

1.2288 1.2349

1.2288 1.2411

3.6864 3.7232

单位

V

V

mV p-p

V

V

mV p-p

Hz

Hz

%

%

度

Ω

Ω

kΩ

MHz

MHz

MHz

测试条件/注释

外部基准电压源

使能内部基准电压源

交流耦合(2.2 �F)、在HART_OUT引脚具有

160 �负载(最差负载情况下)时测得、

HART_OUT电压与负载的关系参见图15

和图16

内部振荡器

内部振荡器

内部振荡器、−40°C至+85℃

内部振荡器、−40°C至+125℃

最差负载为160 �、以2.2 �F进行交流耦

合、驱动阻性负载时,建议配置参见

图19

RTS 低电平、在HART_OUT引脚处

RTS 高电平、在HART_OUT引脚处

−40°C 至 +85°C

−40°C 至 +125°C

1 温度范围:−40°C至+125℃;25℃(典型值)。

2 功耗规格基于电流平均值。

3 解调器和调制器电流规格为采用外部时钟时的情况。如果采用外部晶振,则必须将晶振电流规格加到对应的VCC和IOVCC解调器/调制器电流规格中,以

获得此模式下所需的总电源电流。

4 解调器和调制器电流规格为采用外部时钟时的情况。如果采用内部振荡器,则必须将内部振荡器电流规格加到对应的VCC和IOVCC解调器/调制器电流规

格中,以获得此模式下所需的总电源电流。

5 通过设计和表征保证,未经生产测试。

6 规格设置假定输入端处采用包含前同步码字符的正弦波输入信号,并采用理想的外部滤波器(见图21)。

7 如果不使用内部振荡器,则频率精度取决于所用晶振或时钟源的精度。

Rev. B | Page 4 of 24

�

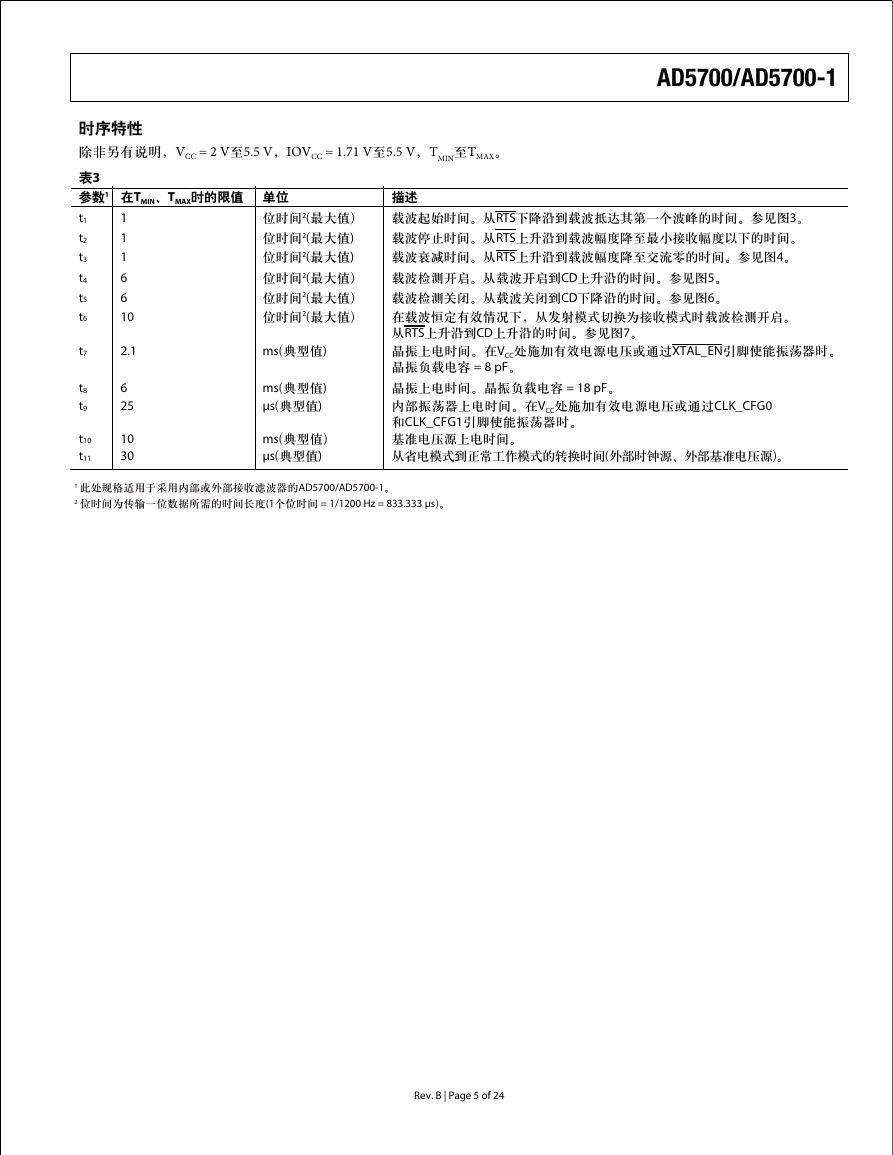

时序特性

除非另有说明,VCC = 2 V至5.5 V,IOVCC = 1.71 V至5.5 V,TMIN至TMAX。

表3

参数1

t1

t2

t3

t4

t5

t6

在TMIN、TMAX时的限值

1

1

1

6

6

10

单位

位时间2(最大值)

位时间2(最大值)

位时间2(最大值)

位时间2(最大值)

位时间2(最大值)

位时间2(最大值)

t7

t8

t9

2.1

6

25

ms(典型值)

ms(典型值)

�s(典型值)

10

30

t10

t11

1 此处规格适用于采用内部或外部接收滤波器的AD5700/AD5700-1。

2 位时间为传输一位数据所需的时间长度(1个位时间 = 1/1200 Hz = 833.333 �s)。

ms(典型值)

�s(典型值)

AD5700/AD5700-1

描述

载波起始时间。从RTS下降沿到载波抵达其第一个波峰的时间。参见图3。

载波停止时间。从RTS上升沿到载波幅度降至最小接收幅度以下的时间。

载波衰减时间。从RTS上升沿到载波幅度降至交流零的时间。参见图4。

载波检测开启。从载波开启到CD上升沿的时间。参见图5。

载波检测关闭。从载波关闭到CD下降沿的时间。参见图6。

在载波恒定有效情况下,从发射模式切换为接收模式时载波检测开启。

从RTS上升沿到CD上升沿的时间。参见图7。

晶振上电时间。在VCC处施加有效电源电压或通过XTAL_EN引脚使能振荡器时。

晶振负载电容 = 8 pF。

晶振上电时间。晶振负载电容 = 18 pF。

内部振荡器上电时间。在VCC处施加有效电源电压或通过CLK_CFG0

和CLK_CFG1引脚使能振荡器时。

基准电压源上电时间。

从省电模式到正常工作模式的转换时间(外部时钟源、外部基准电压源)。

Rev. B | Page 5 of 24

�

AD5700/AD5700-1

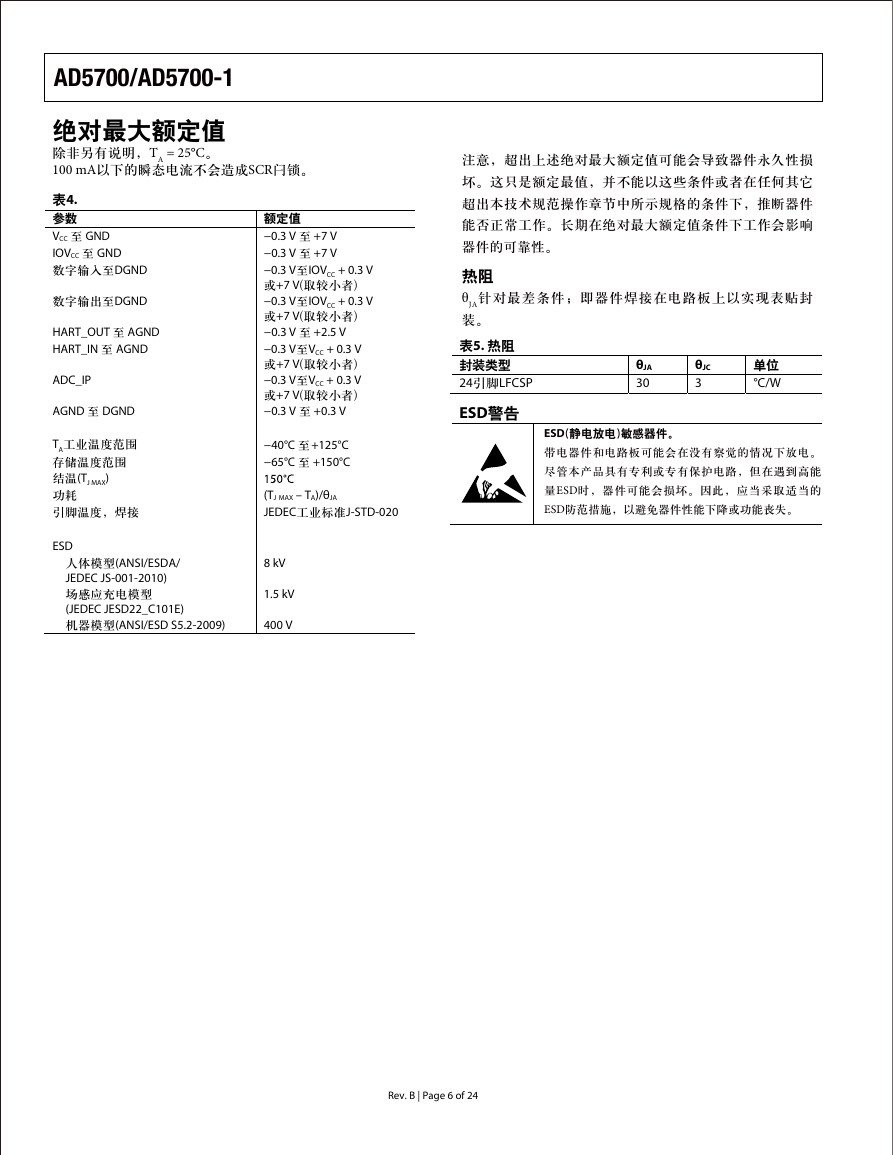

绝对最大额定值

除非另有说明,TA = 25°C。

100 mA以下的瞬态电流不会造成SCR闩锁。

表4.

参数

VCC 至 GND

IOVCC 至 GND

数字输入至DGND

数字输出至DGND

HART_OUT 至 AGND

HART_IN 至 AGND

ADC_IP

AGND 至 DGND

TA工业温度范围

存储温度范围

结温(TJ MAX)

功耗

引脚温度,焊接

DSE

人体模型(ANSI/ESDA/

JEDEC JS-001-2010)

场感应充电模型

(JEDEC JESD22_C101E)

机器模型(ANSI/ESD S5.2-2009)

额定值

−0.3 V 至 +7 V

−0.3 V 至 +7 V

−0.3 V至IOVCC + 0.3 V

或+7 V(取较小者)

−0.3 V至IOVCC + 0.3 V

或+7 V(取较小者)

−0.3 V 至 +2.5 V

−0.3 V至VCC + 0.3 V

或+7 V(取较小者)

−0.3 V至VCC + 0.3 V

或+7 V(取较小者)

−0.3 V 至 +0.3 V

C°04−

至 +125°C

−65°C 至 +150°C

(TJ MAX – TA)/θJA

JEDEC工业标准J-STD-020

8 kV

1.5 kV

400 V

注意,超出上述绝对最大额定值可能会导致器件永久性损

坏。这只是额定最值,并不能以这些条件或者在任何其它

超出本技术规范操作章节中所示规格的条件下,推断器件

能否正常工作。长期在绝对最大额定值条件下工作会影响

器件的可靠性。

热阻

θJA针对最差条件;即器件焊接在电路板上以实现表贴封

装。

表5. 热阻

封装类型

24引脚LFCSP

ESD警告

θJA

30

θJC

3

单位

°C/W

ESD(静电放电)敏感器件。

带电器件和电路板可能会在没有察觉的情况下放电。

尽管本产品具有专利或专有保护电路,但在遇到高能

量ESD时,器件可能会损坏。因此,应当采取适当的

ESD防范措施,以避免器件性能下降或功能丧失。

Rev. B | Page 6 of 24

�

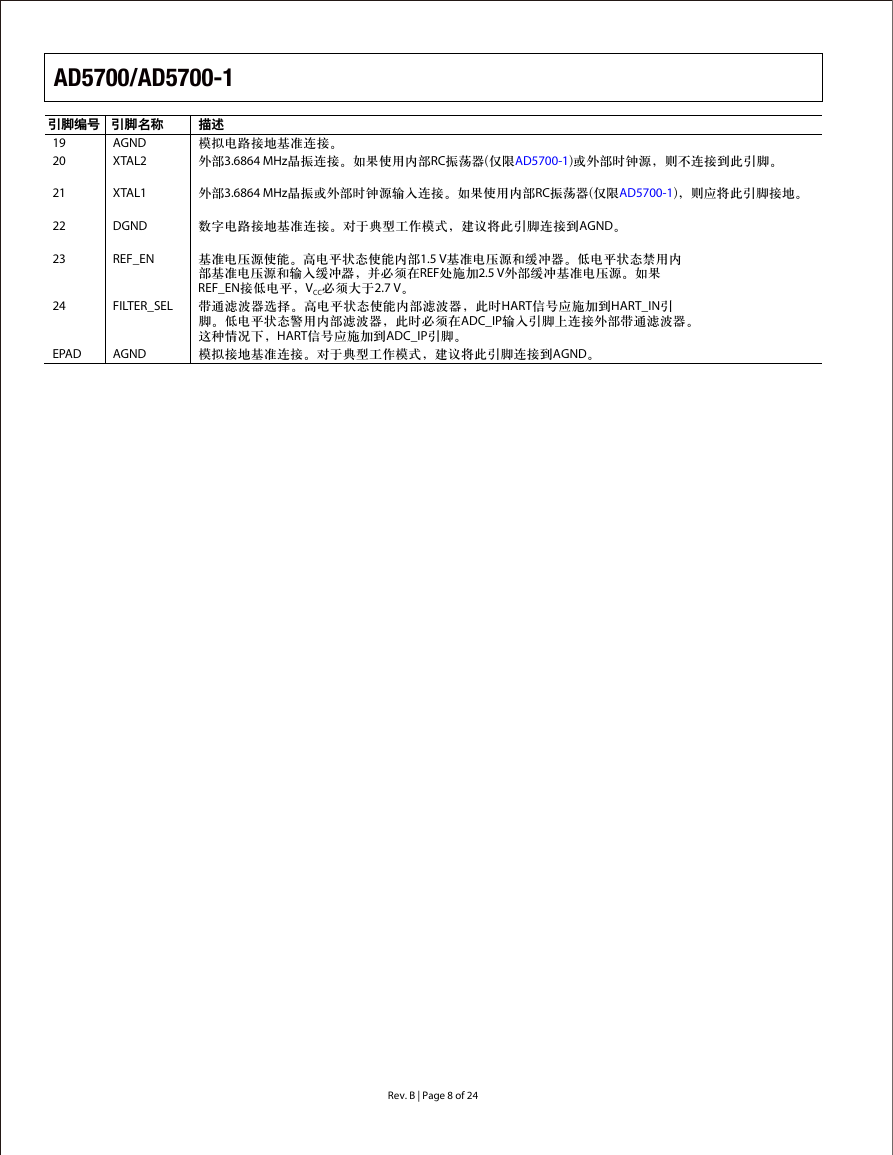

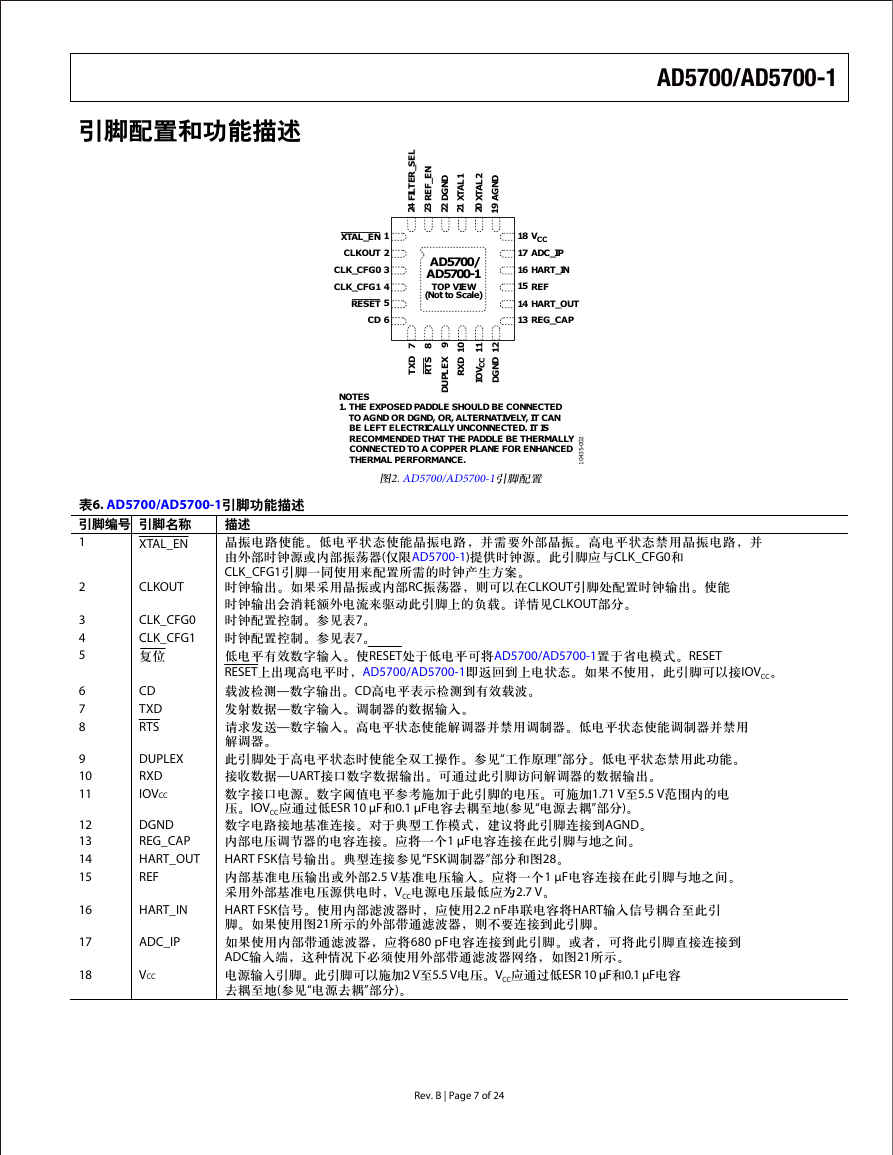

引脚配置和功能描述

AD5700/AD5700-1

L

E

S

_

R

E

T

L

F

4

2

I

N

E

_

F

E

R

3

2

D

N

G

D

2

2

1

L

A

T

X

1

2

2

L

A

T

X

0

2

D

N

G

A

9

1

AD5700/

AD5700-1

TOP VIEW

(Not to Scale)

XTAL_EN

CLKOUT

CLK_CFG0

CLK_CFG1

RESET

CD

1

2

3

4

5

6

18

17

16

15

14

13

VCC

ADC_IP

HART_IN

REF

HART_OUT

REG_CAP

7

8 9

D

X

T

S

T

R

0

1

D

X

R

1

1

2

1

C

C

V

O

I

D

N

G

D

X

E

L

P

U

D

NOTES

1. THE EXPOSED PADDLE SHOULD BE CONNECTED

TO AGND OR DGND, OR, ALTERNATIVELY, IT CAN

BE LEFT ELECTRICALLY UNCONNECTED. IT IS

RECOMMENDED THAT THE PADDLE BE THERMALLY

CONNECTED TO A COPPER PLANE FOR ENHANCED

THERMAL PERFORMANCE.

2

0

0

-

5

3

4

0

1

图2. AD5700/AD5700-1引脚配置

表6. AD5700/AD5700-1引脚功能描述

引脚编号 引脚名称

1

XTAL_EN

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

CLKOUT

CLK_CFG0

CLK_CFG1

复位

CD

TXD

RTS

DUPLEX

RXD

IOVCC

DGND

REG_CAP

HART_OUT

REF

HART_IN

ADC_IP

VCC

描述

晶振电路使能。低电平状态使能晶振电路,并需要外部晶振。高电平状态禁用晶振电路,并

由外部时钟源或内部振荡器(仅限AD5700-1)提供时钟源。此引脚应与CLK_CFG0和

CLK_CFG1引脚一同使用来配置所需的时钟产生方案。

时钟输出。如果采用晶振或内部RC振荡器,则可以在CLKOUT引脚处配置时钟输出。使能

时钟输出会消耗额外电流来驱动此引脚上的负载。详情见CLKOUT部分。

时钟配置控制。参见表7。

时钟配置控制。参见表7。

低电平有效数字输入。使RESET处于低电平可将AD5700/AD5700-1置于省电模式。RESET

RESET上出现高电平时,AD5700/AD5700-1即返回到上电状态。如果不使用,此引脚可以接IOVCC。

载波检测—数字输出。CD高电平表示检测到有效载波。

发射数据—数字输入。调制器的数据输入。

请求发送—数字输入。高电平状态使能解调器并禁用调制器。低电平状态使能调制器并禁用

解调器。

此引脚处于高电平状态时使能全双工操作。参见“工作原理”部分。低电平状态禁用此功能。

接收数据—UART接口数字数据输出。可通过此引脚访问解调器的数据输出。

数字接口电源。数字阈值电平参考施加于此引脚的电压。可施加1.71 V至5.5 V范围内的电

压。IOVCC应通过低ESR 10 �F和0.1 �F电容去耦至地(参见“电源去耦”部分)。

数字电路接地基准连接。对于典型工作模式,建议将此引脚连接到AGND。

内部电压调节器的电容连接。应将一个1 �F电容连接在此引脚与地之间。

HART FSK信号输出。典型连接参见“FSK调制器”部分和图28。

内部基准电压输出或外部2.5 V基准电压输入。应将一个1 �F电容连接在此引脚与地之间。

采用外部基准电压源供电时,VCC电源电压最低应为2.7 V。

HART FSK信号。使用内部滤波器时,应使用2.2 nF串联电容将HART输入信号耦合至此引

脚。如果使用图21所示的外部带通滤波器,则不要连接到此引脚。

如果使用内部带通滤波器,应将680 pF电容连接到此引脚。或者,可将此引脚直接连接到

ADC输入端,这种情况下必须使用外部带通滤波器网络,如图21所示。

电源输入引脚。此引脚可以施加2 V至5.5 V电压。VCC应通过低ESR 10 �F和0.1 �F电容

去耦至地(参见“电源去耦”部分)。

Rev. B | Page 7 of 24

�

AD5700/AD5700-1

引脚名称 描述

EPAD

AGND

引脚编号

19

20

21

22

23

24

AGND

XTAL2

XTAL1

DGND

REF_EN

FILTER_SEL

模拟电路接地基准连接。

外部3.6864 MHz晶振连接。如果使用内部RC振荡器(仅限AD5700-1)或外部时钟源,则不连接到此引脚。

外部3.6864 MHz晶振或外部时钟源输入连接。如果使用内部RC振荡器(仅限AD5700-1),则应将此引脚接地。

数字电路接地基准连接。对于典型工作模式,建议将此引脚连接到AGND。

,

基准电压源使能。高电平状态使能内部1.5 V基准电压源和缓冲器。低电平状态禁用内

部基准电压源和输入缓冲器,并必须在REF处施加2.5 V外部缓冲基准电压源。如果

REF_EN接低电平,VCC必须大于2.7 V。

带通滤波器选择。高电平状态使能内部滤波器,此时HART信号应施加到HART_IN引

脚。低电平状态警用内部滤波器,此时必须在ADC_IP输入引脚上连接外部带通滤波器。

这种情况下,HART信号应施加到ADC_IP引脚。

模拟接地基准连接。对于典型工作模式,建议将此引脚连接到AGND。

Rev. B | Page 8 of 24

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc