PCB 阻抗匹配总结

网名:chinawei97qq: 1219658831

做硬件工程师好几年,有最初的不做阻抗,到后面认为做阻抗是 PCB 厂家

的事情,导致设计的 pcb 交给 pcb 厂家后重新修改修改布线,影响项目进度,下面把

总结写在后面,以面再犯同样的错误。

做 4 层板,正片工艺,这样就对做半孔工艺带来加工不方便,半孔工艺会

带来价格的增加,单价增加 0.05 元/cm2

1.6mm 厚度的 4 层 PCB 板加工,建议做阻抗设计的时候按照 1.5mm 厚度进

行设计,剩下 0.1mm 厚度留给工厂作为其他工艺要求用(后制诚厚度,绿油、丝印

等)。

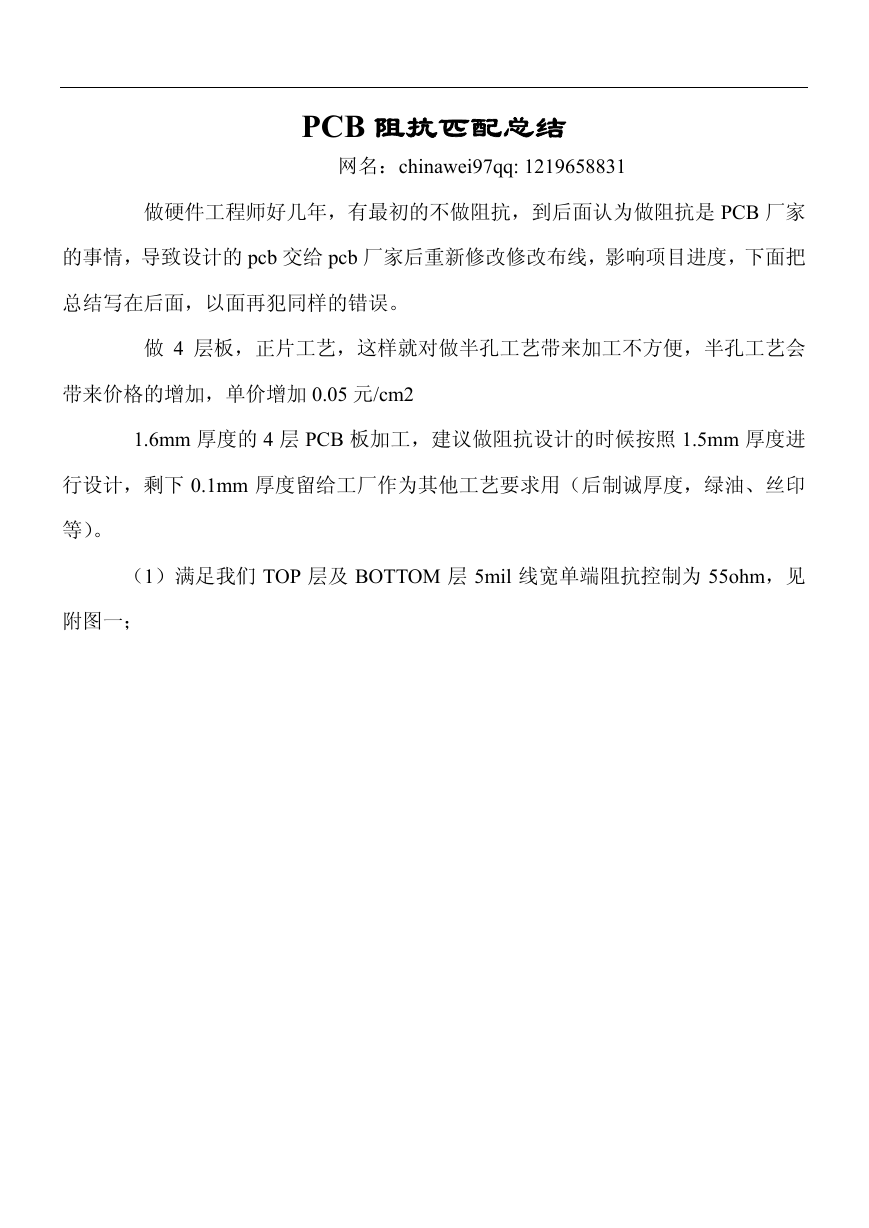

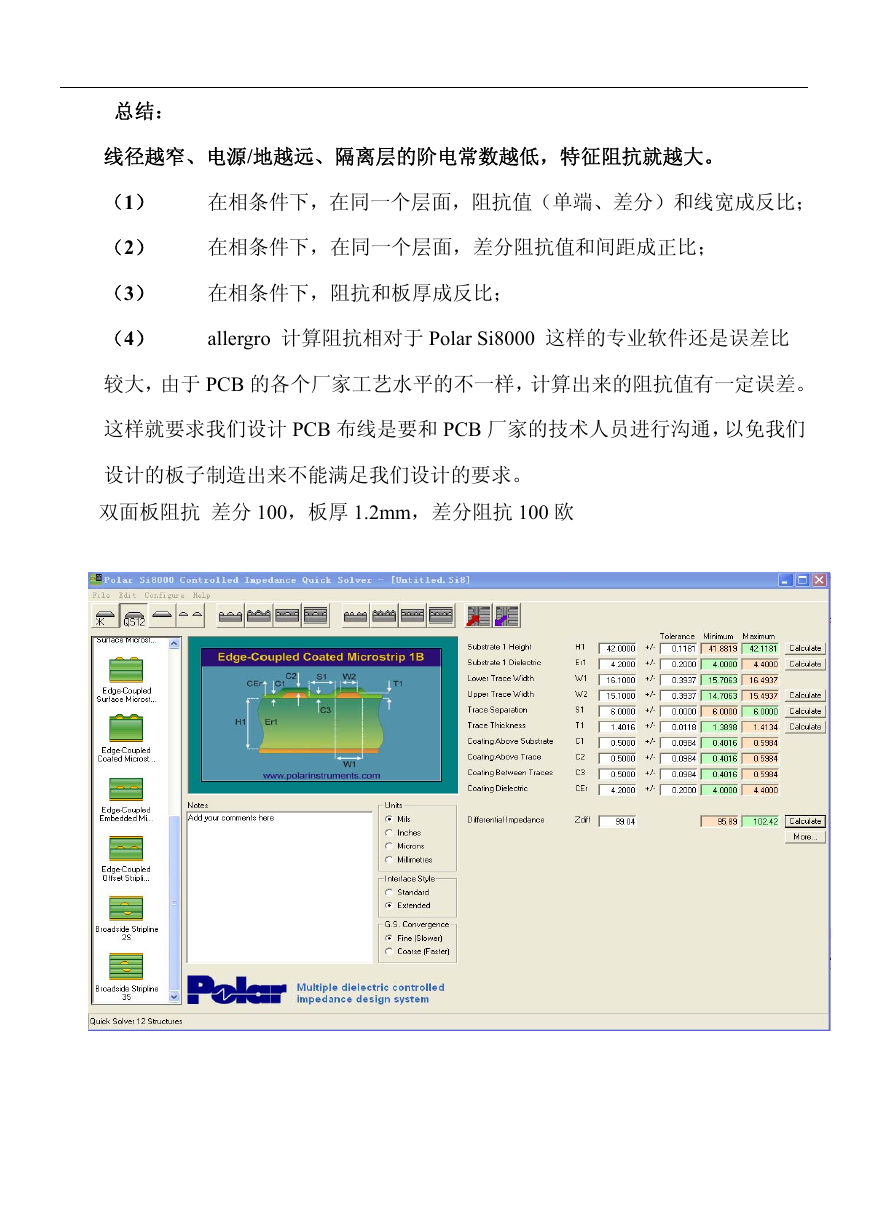

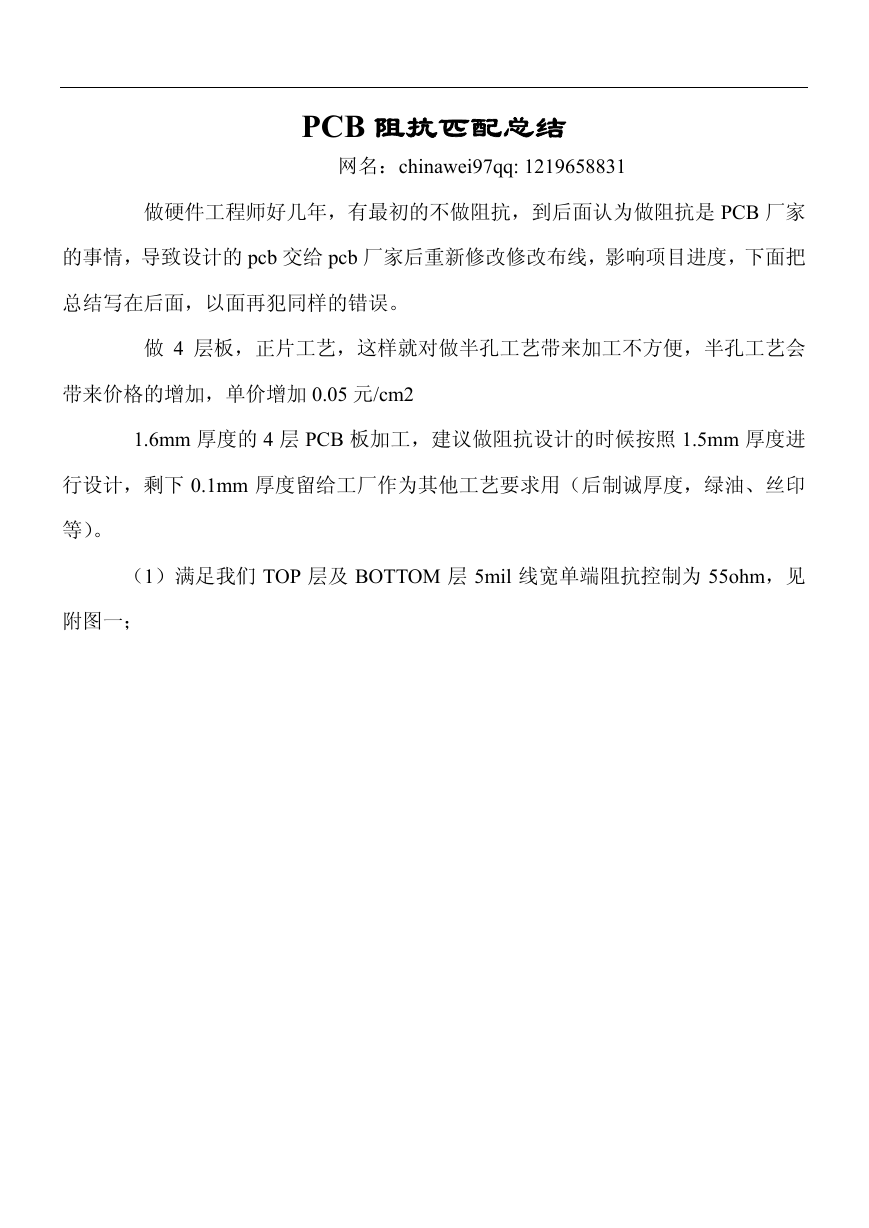

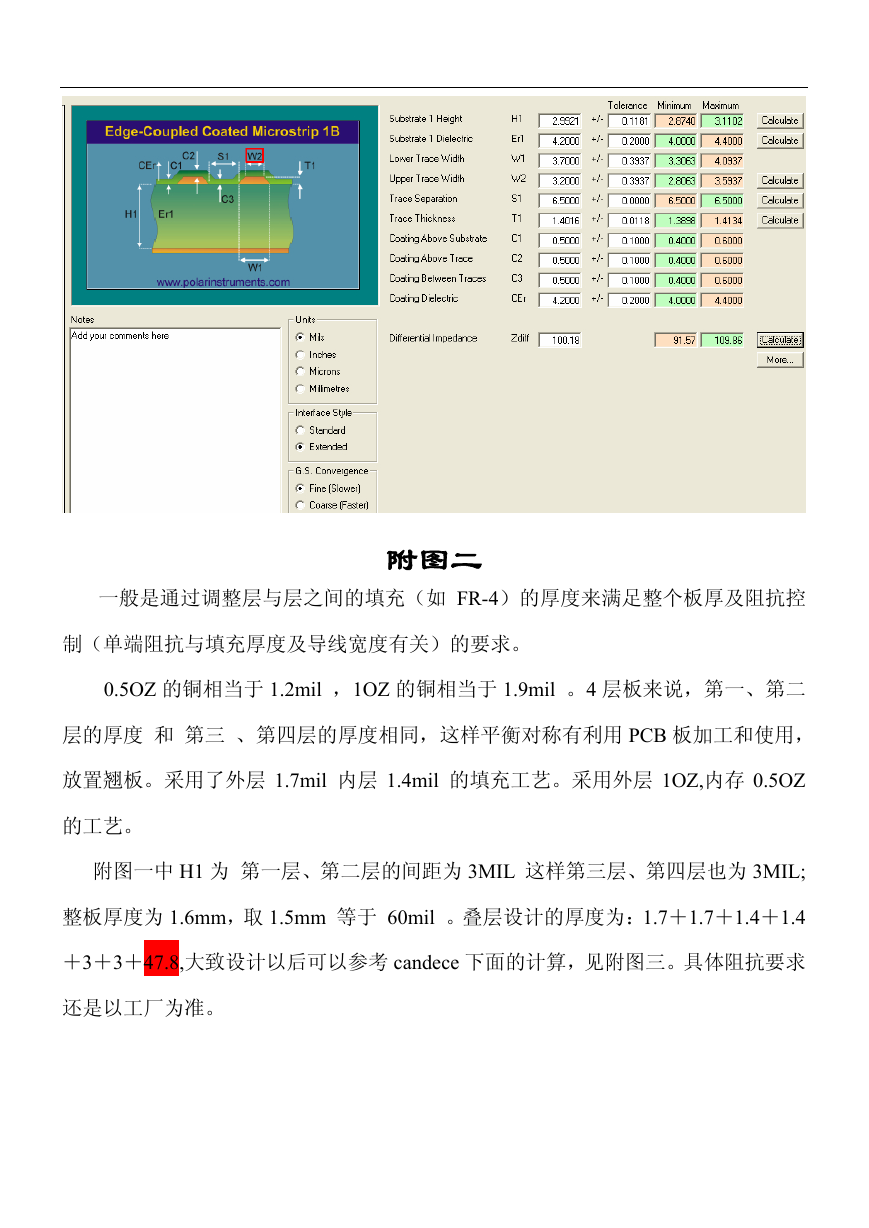

(1)满足我们 TOP 层及 BOTTOM 层 5mil 线宽单端阻抗控制为 55ohm,见

附图一;

�

附图一

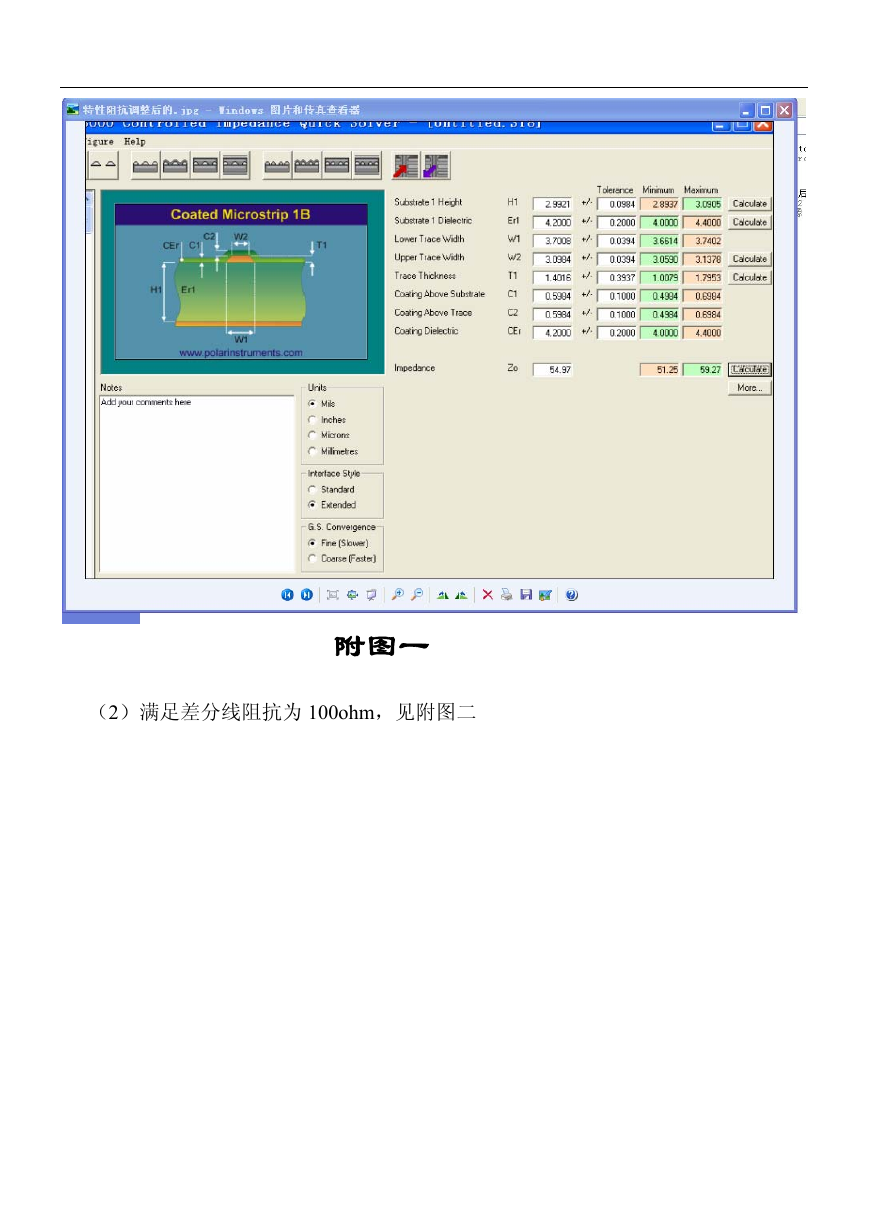

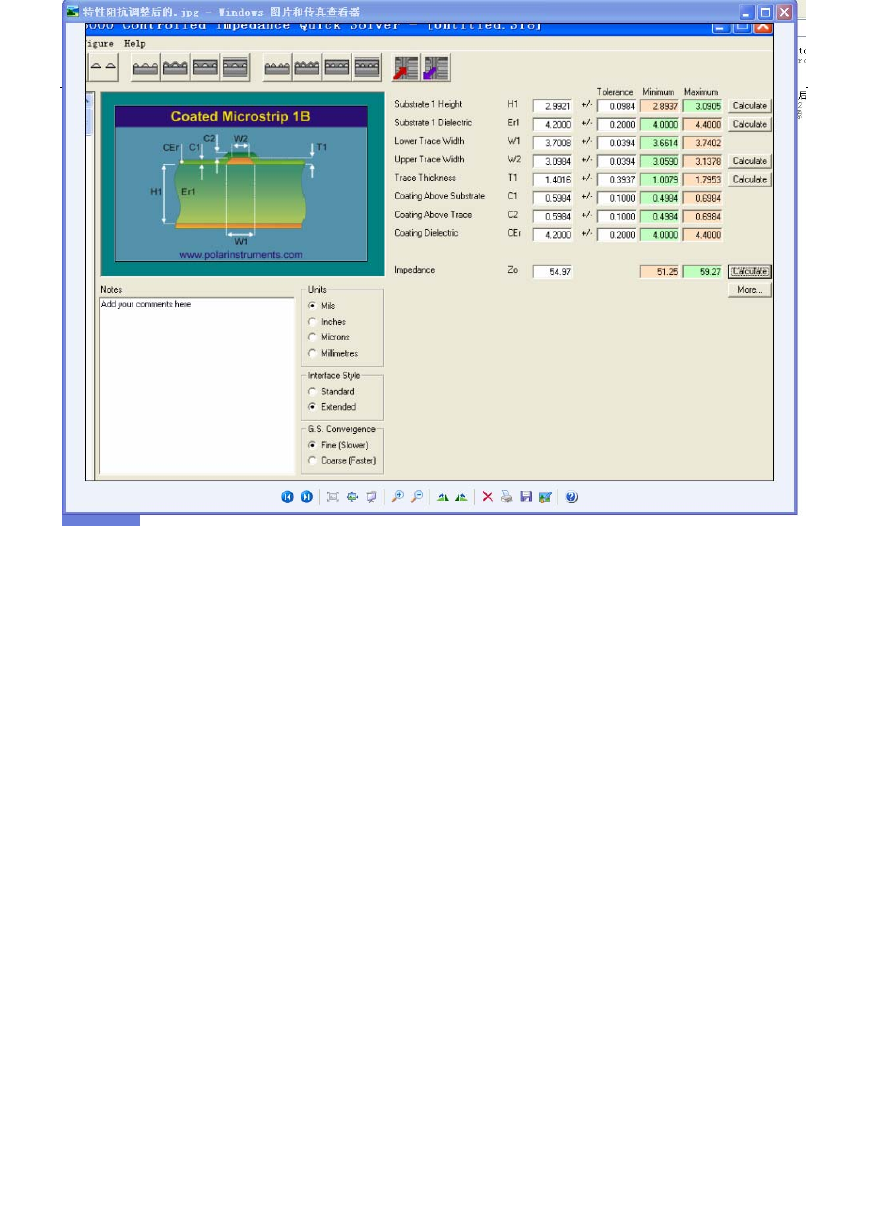

(2)满足差分线阻抗为 100ohm,见附图二

�

附图二

一般是通过调整层与层之间的填充(如 FR-4)的厚度来满足整个板厚及阻抗控

制(单端阻抗与填充厚度及导线宽度有关)的要求。

0.5OZ 的铜相当于 1.2mil ,1OZ 的铜相当于 1.9mil 。4 层板来说,第一、第二

层的厚度 和 第三 、第四层的厚度相同,这样平衡对称有利用 PCB 板加工和使用,

放置翘板。采用了外层 1.7mil 内层 1.4mil 的填充工艺。采用外层 1OZ,内存 0.5OZ

的工艺。

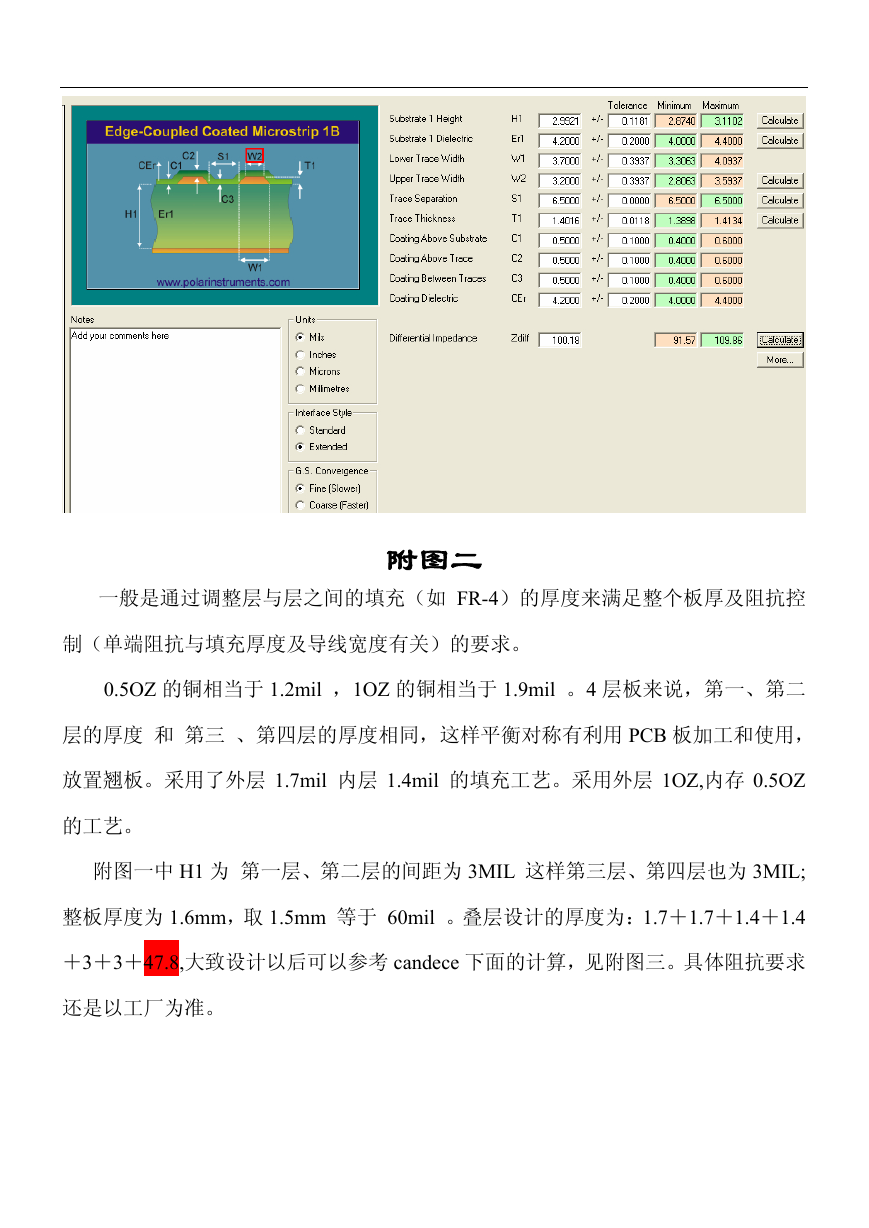

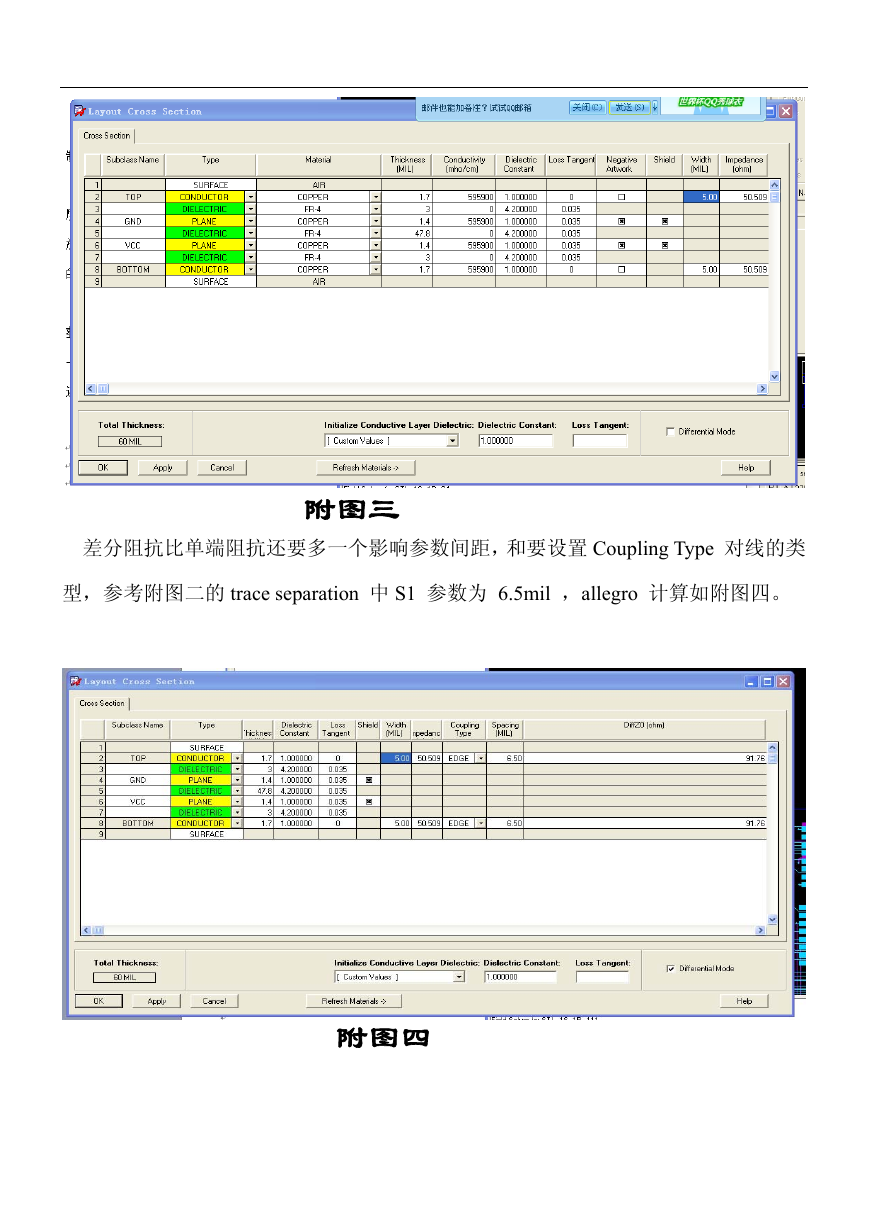

附图一中 H1 为 第一层、第二层的间距为 3MIL 这样第三层、第四层也为 3MIL;

整板厚度为 1.6mm,取 1.5mm 等于 60mil 。叠层设计的厚度为:1.7+1.7+1.4+1.4

+3+3+47.8,大致设计以后可以参考 candece 下面的计算,见附图三。具体阻抗要求

还是以工厂为准。

�

附图三

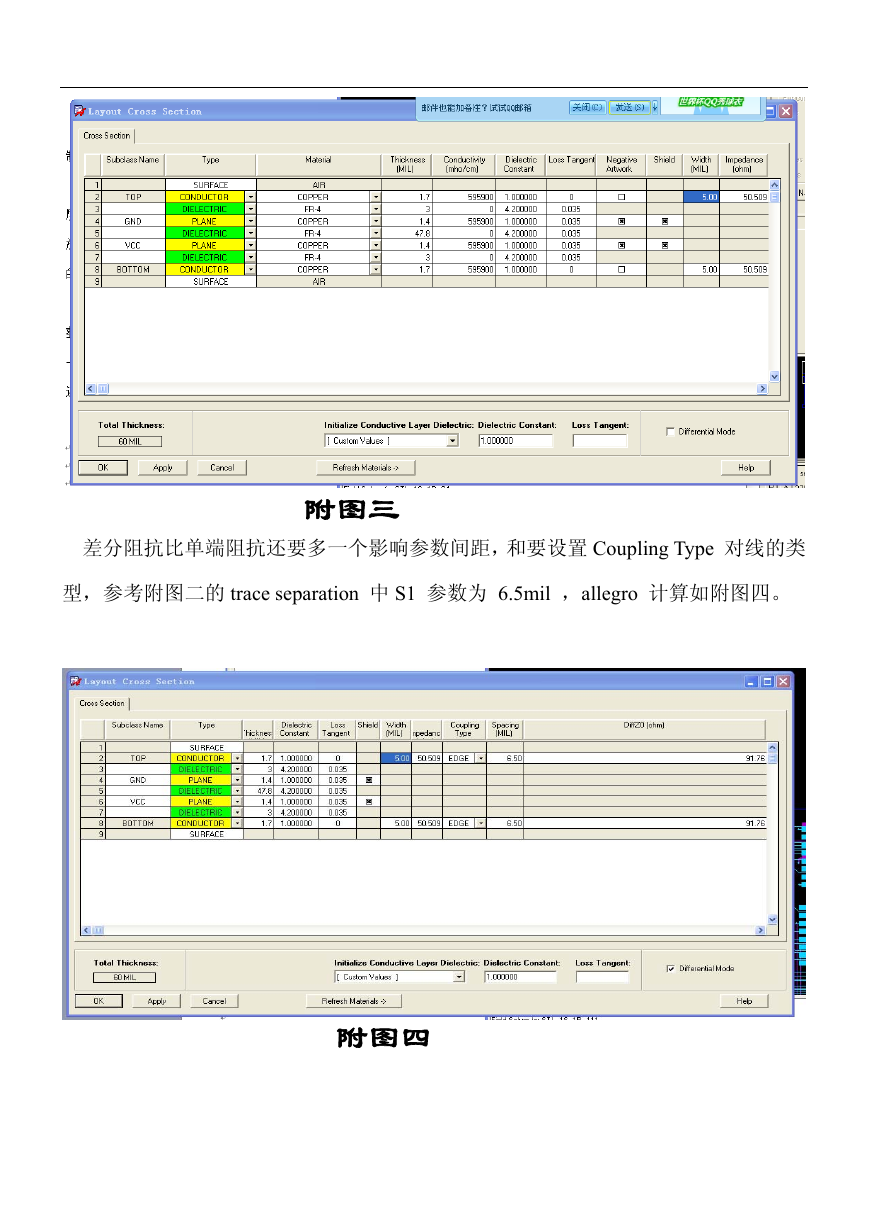

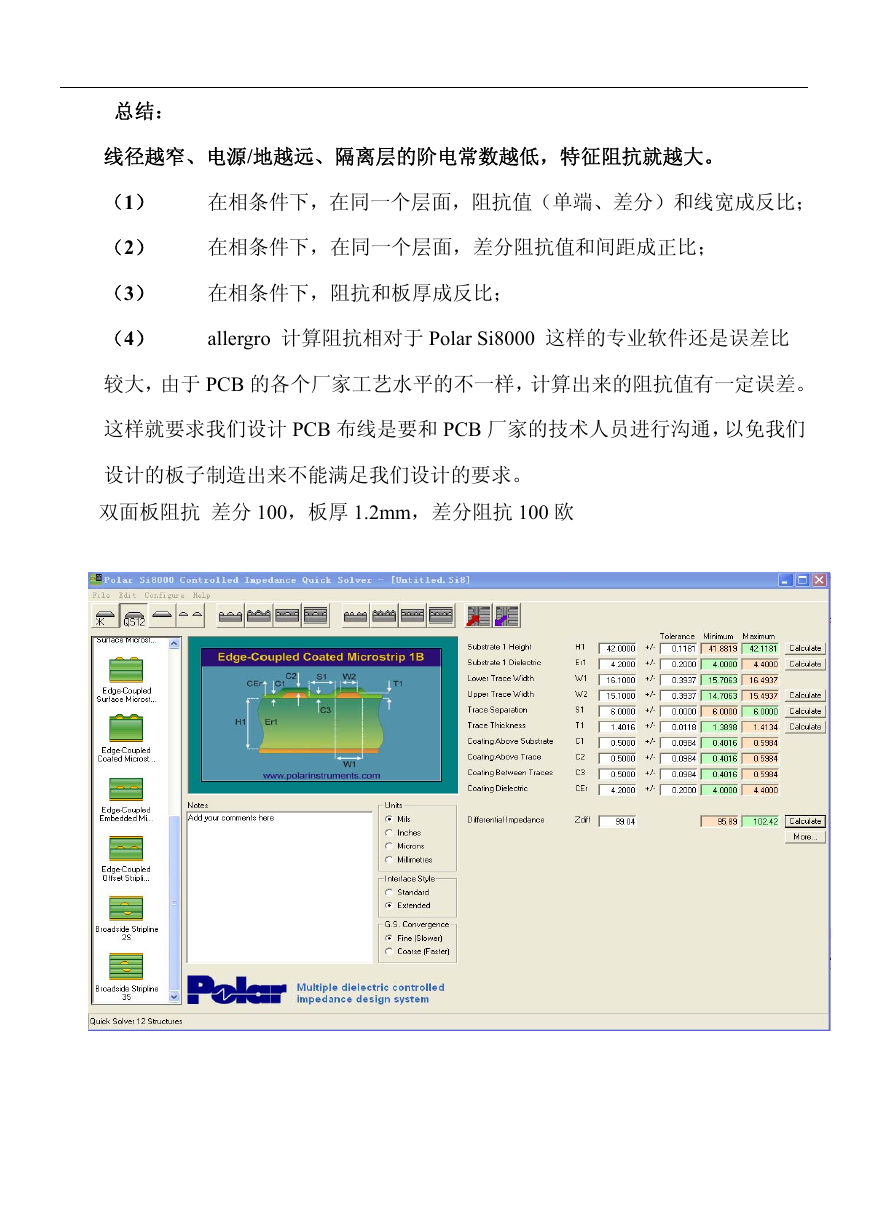

差分阻抗比单端阻抗还要多一个影响参数间距,和要设置 Coupling Type 对线的类

型,参考附图二的 trace separation 中 S1 参数为 6.5mil ,allegro 计算如附图四。

附图四

�

总结:

线径越窄、电源/地越远、隔离层的阶电常数越低,特征阻抗就越大。

(1)

(2)

(3)

(4)

在相条件下,在同一个层面,阻抗值(单端、差分)和线宽成反比;

在相条件下,在同一个层面,差分阻抗值和间距成正比;

在相条件下,阻抗和板厚成反比;

allergro 计算阻抗相对于 Polar Si8000 这样的专业软件还是误差比

较大,由于 PCB 的各个厂家工艺水平的不一样,计算出来的阻抗值有一定误差。

这样就要求我们设计 PCB 布线是要和 PCB 厂家的技术人员进行沟通,以免我们

设计的板子制造出来不能满足我们设计的要求。

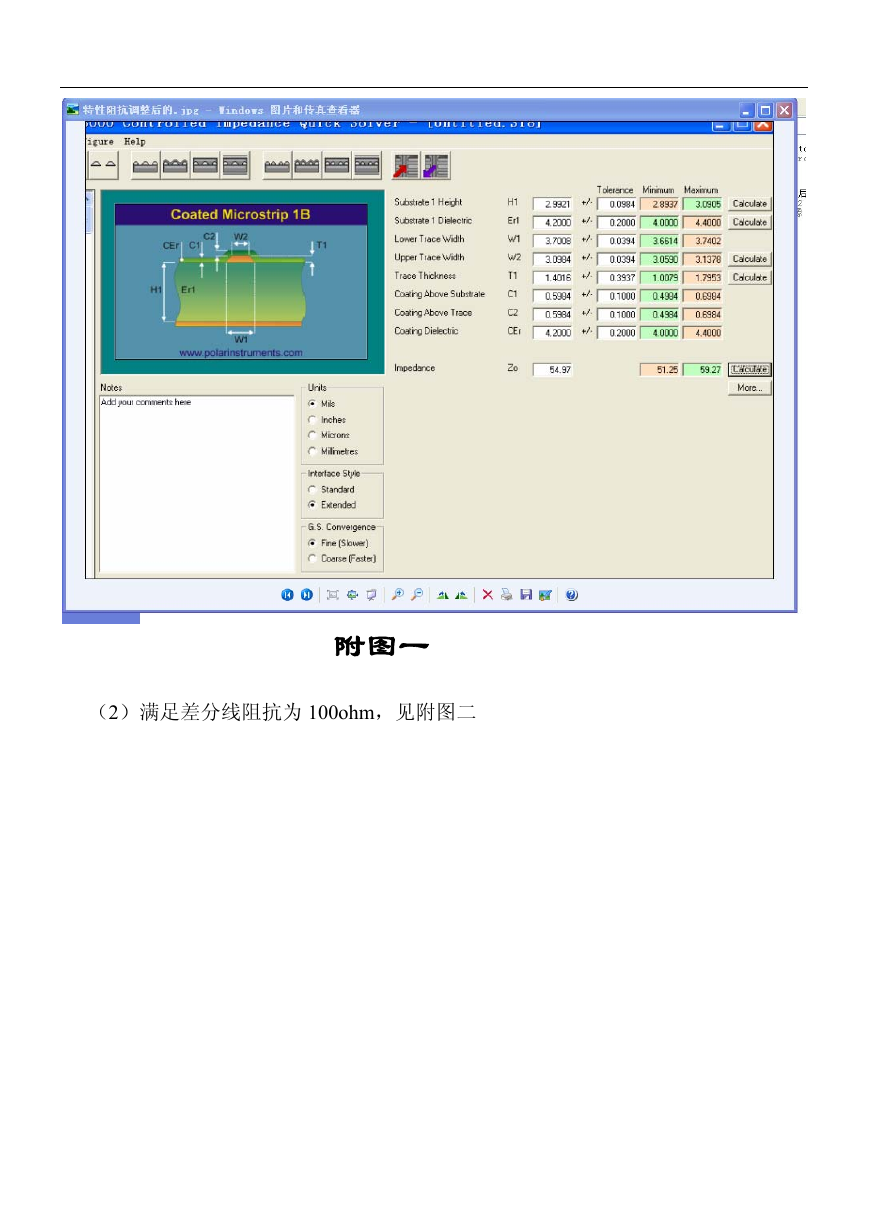

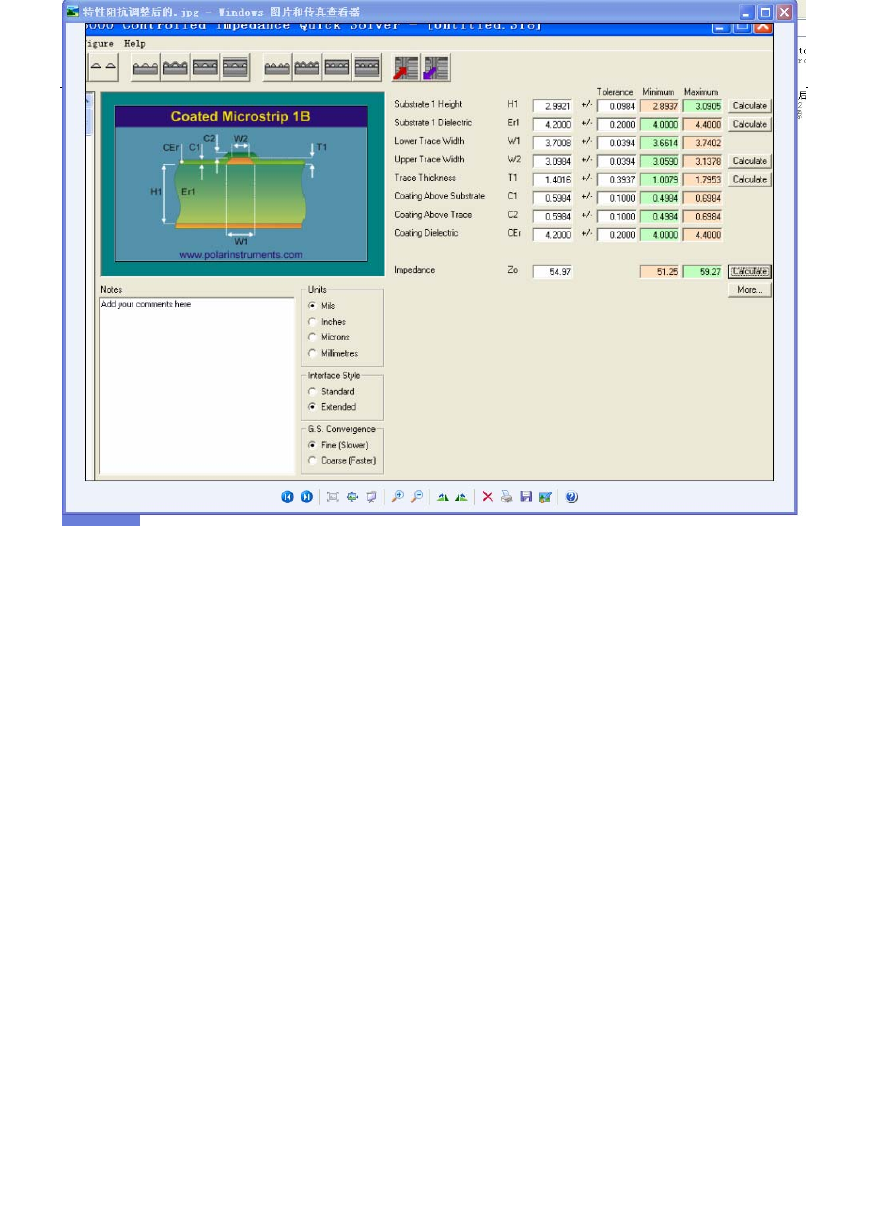

双面板阻抗 差分 100,板厚 1.2mm,差分阻抗 100 欧

�

(5)

(6)

(7)

trace 宽度和电路板的叠层决定 Trace 特性;

Trace 和参考平面间的距离对阻抗和窜扰的影响:阻抗,随距离增加

而增加;窜扰,随距离增加而增加

Trace 的阻抗依据下面的因素:

绝缘材料的介电常数:在布线层之间是否有平面层,在平面层的存

在对于布线层间的窜扰起了重要作用;

绝缘材料的厚度;

Trace 的宽度和厚度;

Thanks

(8)

�

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc