MT7530B/MT7530W

Approval Datasheet

7-port Gigabit Ethernet Switch

FOR RD04@ b-link.net.cn USE ONLY

MEDIATEK CONFIDENTIAL

© 2013 MediaTek Inc.

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

Specifications are subject to change without notice.

Version:

Release date:

0.92

2013-05-14

loginid=RD04@b-link.net.cn,time=2014-10-21 09:44:38,ip=58.251.146.207,doctitle=MT7530B_MT7530W_approval_datasheet_V0.92.pdf,company=B-LINK_WCN

�

MT7530B/MT7530W

Approval Datasheet

1.1.1

2

3

4

Table of Contents

Table of Contents ................................................................................................................................... 2

Lists of Tables and Figures ................................................................................................................... 3

General Description ..................................................................................................................... 4

1

1.1 Overview ............................................................................................................................... 4

Features ............................................................................................................... 4

Block Diagram .............................................................................................................................. 6

Pin Assignment ............................................................................................................................ 7

Pin Description ............................................................................................................................. 9

4.1 System Pins .......................................................................................................................... 9

4.2 Digital Signal Pins ............................................................................................................... 10

4.3 Analog Signal Pins ............................................................................................................. 12

4.4 Power Pins .......................................................................................................................... 13

Electrical Specifications ............................................................................................................ 14

5.1 Absolute Maximum Ratings ................................................................................................ 14

5.2 Recommended Operating Conditions ................................................................................ 14

5.3 Thermal Characteristics ...................................................................................................... 14

JEDEC 2-Layer System PCB*1 ........................................................................... 14

JEDEC 4-Layer System PCB ............................................................................. 15

5.4 DC Characteristics .............................................................................................................. 15

P5 IO (3.3V) ....................................................................................................... 15

P5 IO (2.5V), P6 IO (2.5V) ................................................................................. 15

P6 IO (1.8V) ....................................................................................................... 15

P6 IO (1.5V) ....................................................................................................... 15

5.5 AC Characteristics .............................................................................................................. 16

P5 RGMII Timing ................................................................................................ 16

P5 GMII Timing .................................................................................................. 16

P6 TRGMII Timing .............................................................................................. 17

Package Dimension ................................................................................................................... 18

Top Marking ................................................................................................................................ 20

FOR RD04@ b-link.net.cn USE ONLY

MEDIATEK CONFIDENTIAL

5.3.1

5.3.2

5.4.1

5.4.2

5.4.3

5.4.4

5.5.1

5.5.2

5.5.3

5

6

7

MediaTek Confidential

© 2013 MediaTek Inc.

Page 2

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

loginid=RD04@b-link.net.cn,time=2014-10-21 09:44:38,ip=58.251.146.207,doctitle=MT7530B_MT7530W_approval_datasheet_V0.92.pdf,company=B-LINK_WCN

�

Lists of Tables and Figures

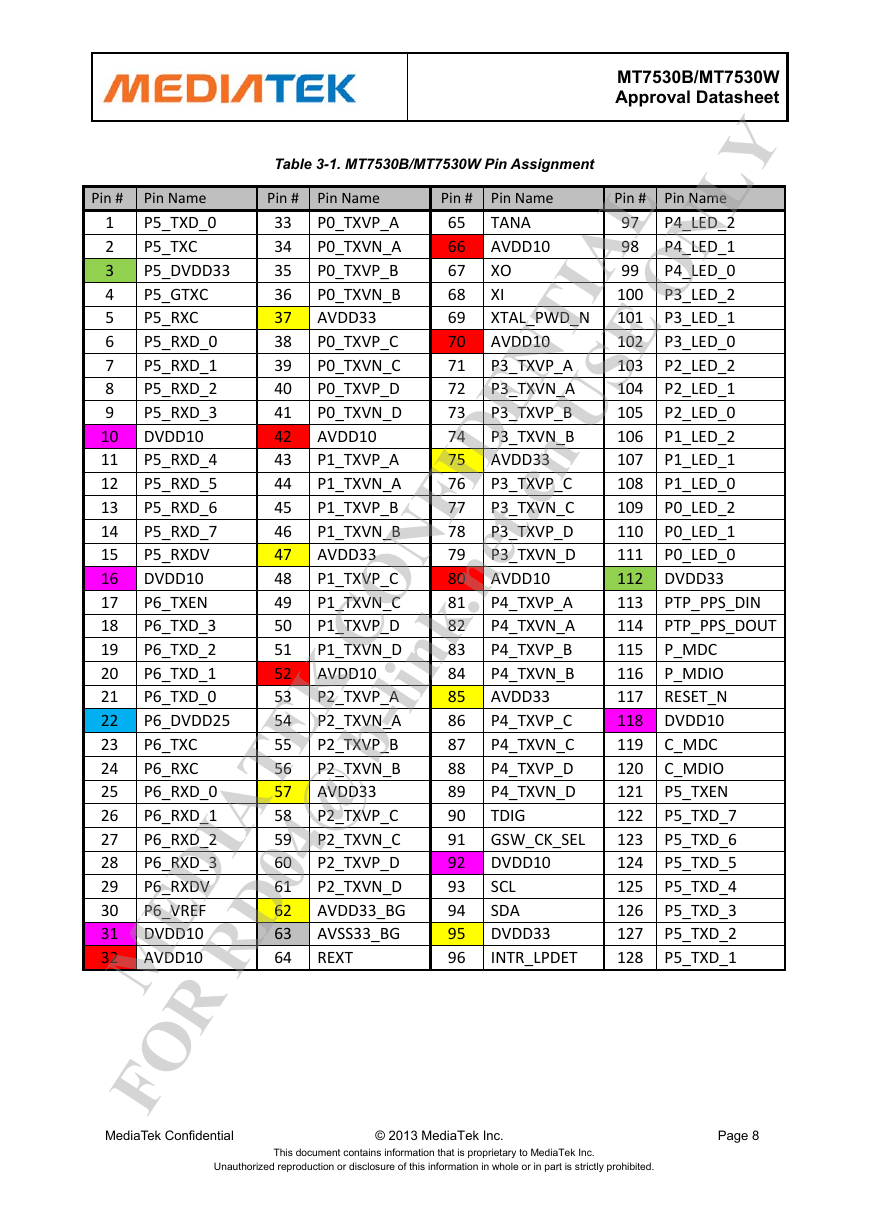

Table 3-1. MT7530B/MT7530W Pin Assignment .................................................................................... 8

Table 4-1. System Clock and Reset Pins ................................................................................................ 9

Table 4-2. System hardware trap pins .................................................................................................... 9

Table 4-3. P5 RGMII/GMII pins ............................................................................................................. 10

Table 4-4. P6 RGMII/TRGMII Pins ........................................................................................................ 11

Table 4-5. P0 to P5 PHY LED pins........................................................................................................ 11

Table 4-6. Digital control pins ................................................................................................................ 12

Table 4-7. Analog signal pins ................................................................................................................ 12

Table 4-8. Analog and digital power pins .............................................................................................. 13

Table 6-1. 128-pin LQFP package dimension ....................................................................................... 19

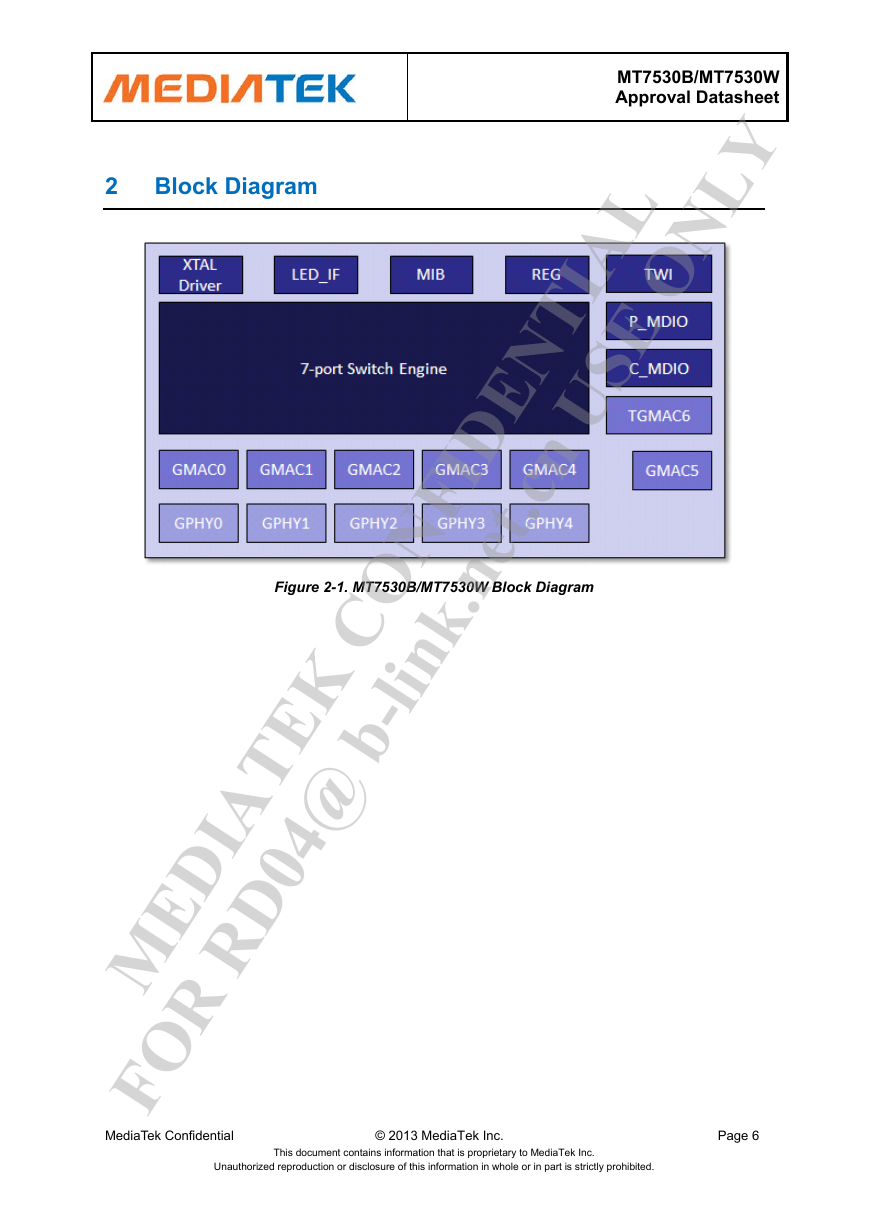

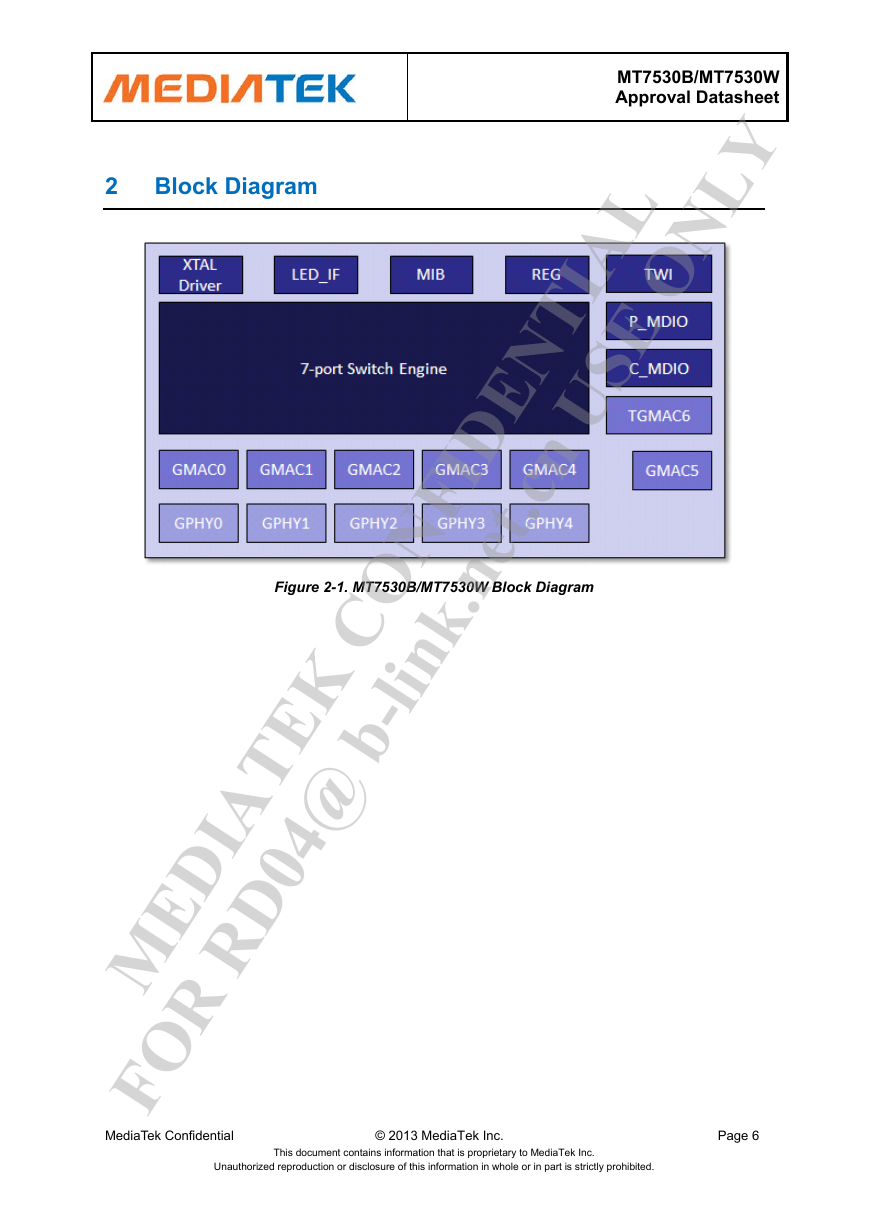

Figure 2-1. MT7530B/MT7530W Block Diagram .................................................................................... 6

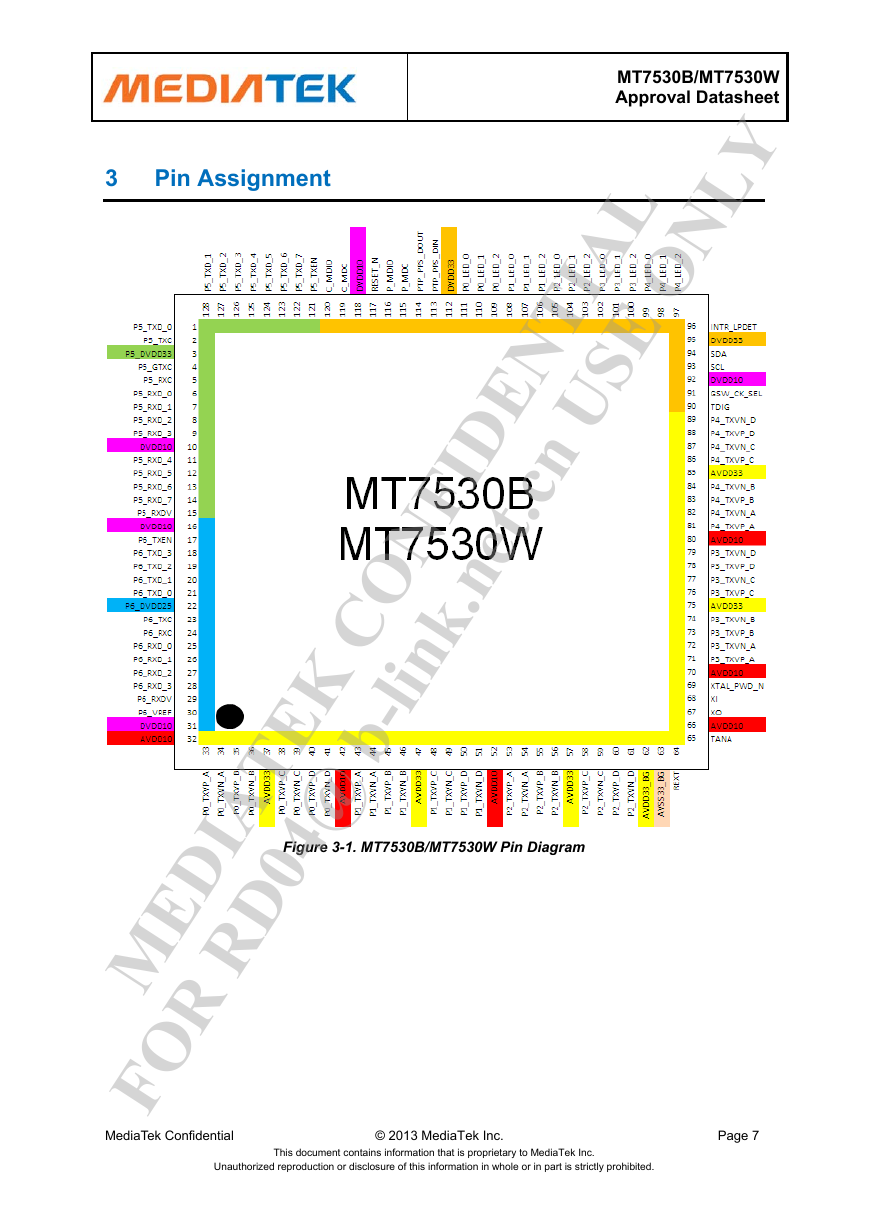

Figure 3-1. MT7530B/MT7530W Pin Diagram ........................................................................................ 7

Figure 6-1. 128-pin LQFP package drawing ......................................................................................... 18

Figure 7-1. MT7530B Top marking........................................................................................................ 20

Figure 7-2. MT7530W Top marking....................................................................................................... 20

FOR RD04@ b-link.net.cn USE ONLY

MEDIATEK CONFIDENTIAL

MT7530B/MT7530W

Approval Datasheet

MediaTek Confidential

© 2013 MediaTek Inc.

Page 3

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

loginid=RD04@b-link.net.cn,time=2014-10-21 09:44:38,ip=58.251.146.207,doctitle=MT7530B_MT7530W_approval_datasheet_V0.92.pdf,company=B-LINK_WCN

�

Features

RGMII/TRGMII MAC

1 General Description

Overview

1.1

MT7530B/MT7530W is a highly integrated Ethernet switch with high performance and non-blocking

transmission. It includes a 7-port Gigabit Ethernet MAC and a 5-port Gigabit Ethernet PHY for several

applications, such as xDSL, xPON, WiFi AP, and cable modem. MT7530B/MT7530W enables an

advanced power-saving feature to meet the market requirement. It complies with IEEE803.3az for

Energy Efficient Ethernet and cable-length/link-down power saving mode. MT7530B/MT7530W is also

designed for cost-sensitive applications in retail and Telecom market. MediaTek's industry-leading

techniques provide customers with the most cost-competitive and lowest power consumption Ethernet

product in the industry.

1.1.1

5-port 10/100/1000Mbps MDI transceivers, 1-port RGMII/GMII/TMII/MII MAC, and 1-port

FOR RD04@ b-link.net.cn USE ONLY

MEDIATEK CONFIDENTIAL

One RGMII port supports PHY mode for router application

Supports 2Gbps TRGMII mode

Accessible MAC address table with 2048 entries and auto aging and learning capabilities

Programmable aging timer for MAC address table

Supports programmable 1518/1536/1552 and 9K Jumbo frame length

Supports 20/25/40MHz clock source

Supports SVL and IVL with 8 filtering database

Supports RSTP and MSTP

Supports 802.1X

Supports 4K VLAN entries

Supports VLAN ID tag and un-tag options for each port

Supports double tagging VLAN

Supports hardware port isolation

Supports 8 priority queues per port

Supports SP, WFQ, and SP+WFQ latency scheduler

Supports Max-Min bandwidth scheduler

Supports ingress and egress rate control

Supports 64 sets of ACL rules

Supports IGMPv1/v2/v3 and MLDv1/v2 snooping

Supports IPv4 and IPv6 multicast frames hardware forwarding

Supports 40 MIB counters per port

Supports IEEE 1588v2

Supports Loop detection indicator

Supports Broadcast/Multicast/Unknown frames storm suppression

10Base-T, 10Base-Te, 100Base-TX, and 1000Base-T compliant Transceivers

Compliant with IEEE 802.3 Auto-Negotiation

MediaTek Confidential

MT7530B/MT7530W

Approval Datasheet

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

loginid=RD04@b-link.net.cn,time=2014-10-21 09:44:38,ip=58.251.146.207,doctitle=MT7530B_MT7530W_approval_datasheet_V0.92.pdf,company=B-LINK_WCN

© 2013 MediaTek Inc.

Page 4

�

MT7530B/MT7530W

Approval Datasheet

Integrated MDI resistors

Supports 3 LEDs per GEPHY port

Supports short-cable power saving

Supports IEEE 802.3az Energy Efficient Ethernet

128-pin E-PAD, QFP, 14mm x 14mm

FOR RD04@ b-link.net.cn USE ONLY

MEDIATEK CONFIDENTIAL

MediaTek Confidential

© 2013 MediaTek Inc.

Page 5

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

loginid=RD04@b-link.net.cn,time=2014-10-21 09:44:38,ip=58.251.146.207,doctitle=MT7530B_MT7530W_approval_datasheet_V0.92.pdf,company=B-LINK_WCN

�

MT7530B/MT7530W

Approval Datasheet

2 Block Diagram

FOR RD04@ b-link.net.cn USE ONLY

MEDIATEK CONFIDENTIAL

Figure 2-1. MT7530B/MT7530W Block Diagram

MediaTek Confidential

© 2013 MediaTek Inc.

Page 6

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

loginid=RD04@b-link.net.cn,time=2014-10-21 09:44:38,ip=58.251.146.207,doctitle=MT7530B_MT7530W_approval_datasheet_V0.92.pdf,company=B-LINK_WCN

�

MT7530B/MT7530W

Approval Datasheet

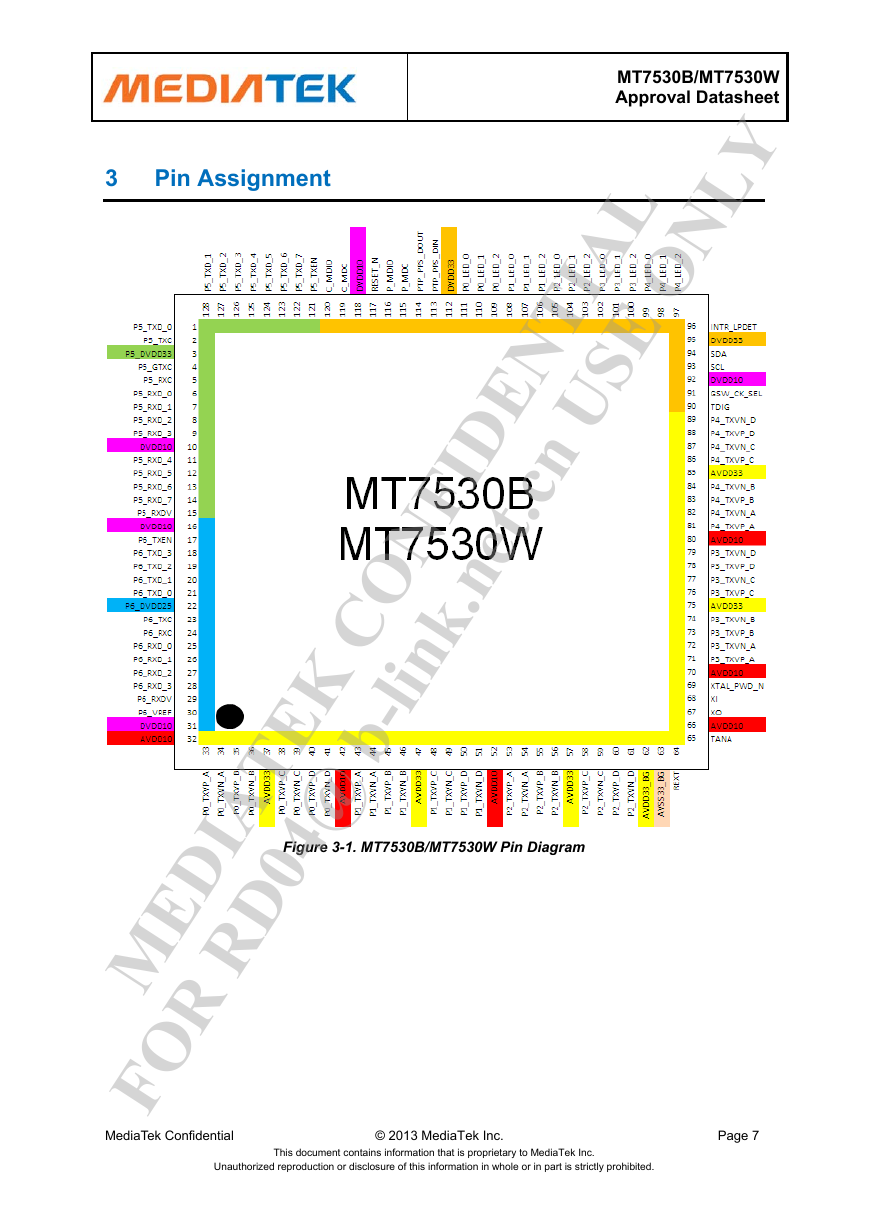

3 Pin Assignment

FOR RD04@ b-link.net.cn USE ONLY

MEDIATEK CONFIDENTIAL

Figure 3-1. MT7530B/MT7530W Pin Diagram

MediaTek Confidential

© 2013 MediaTek Inc.

Page 7

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

loginid=RD04@b-link.net.cn,time=2014-10-21 09:44:38,ip=58.251.146.207,doctitle=MT7530B_MT7530W_approval_datasheet_V0.92.pdf,company=B-LINK_WCN

�

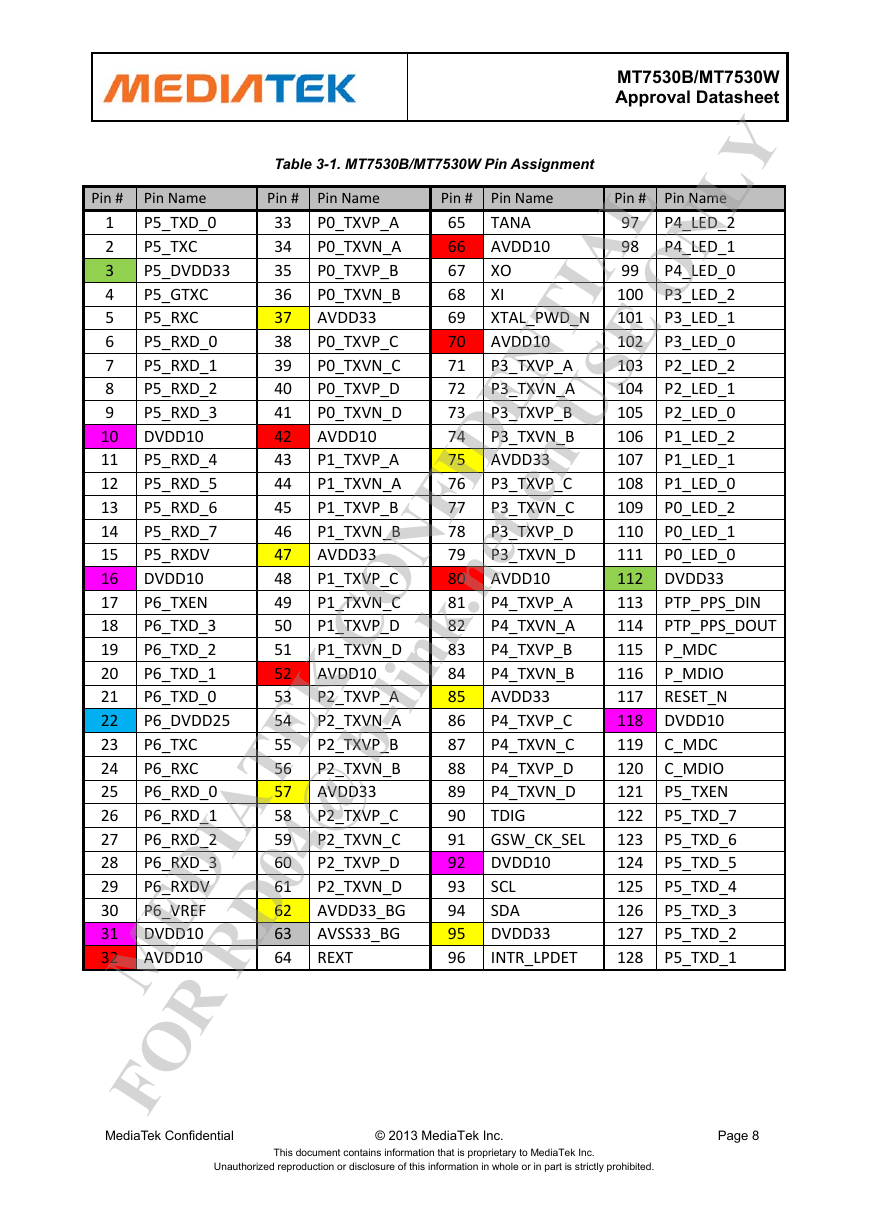

Table 3-1. MT7530B/MT7530W Pin Assignment

Pin Name

P5_TXD_0

P5_TXC

P5_DVDD33

P5_GTXC

P5_RXC

P5_RXD_0

P5_RXD_1

P5_RXD_2

P5_RXD_3

Pin # Pin Name

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

P0_TXVP_A

P0_TXVN_A

P0_TXVP_B

P0_TXVN_B

AVDD33

P0_TXVP_C

P0_TXVN_C

P0_TXVP_D

P0_TXVN_D

AVDD10

P1_TXVP_A

P1_TXVN_A

P1_TXVP_B

P1_TXVN_B

AVDD33

P1_TXVP_C

P1_TXVN_C

P1_TXVP_D

P1_TXVN_D

AVDD10

P2_TXVP_A

P2_TXVN_A

P2_TXVP_B

P2_TXVN_B

AVDD33

P2_TXVP_C

P2_TXVN_C

P2_TXVP_D

P2_TXVN_D

AVDD33_BG

AVSS33_BG

REXT

Pin #

1

2

3

4

5

6

7

8

9

10 DVDD10

11

P5_RXD_4

12

P5_RXD_5

13

P5_RXD_6

14

P5_RXD_7

15

P5_RXDV

16 DVDD10

P6_TXEN

17

18

P6_TXD_3

P6_TXD_2

19

P6_TXD_1

20

21

P6_TXD_0

P6_DVDD25

22

P6_TXC

23

24

P6_RXC

P6_RXD_0

25

P6_RXD_1

26

27

P6_RXD_2

P6_RXD_3

28

P6_RXDV

29

30

P6_VREF

31 DVDD10

32

AVDD10

FOR RD04@ b-link.net.cn USE ONLY

MEDIATEK CONFIDENTIAL

Pin # Pin Name

P4_LED_2

97

98

P4_LED_1

99

P4_LED_0

100 P3_LED_2

101 P3_LED_1

102 P3_LED_0

103 P2_LED_2

104 P2_LED_1

105 P2_LED_0

106 P1_LED_2

107 P1_LED_1

108 P1_LED_0

109 P0_LED_2

110 P0_LED_1

111 P0_LED_0

112 DVDD33

113 PTP_PPS_DIN

114 PTP_PPS_DOUT

115 P_MDC

116 P_MDIO

117 RESET_N

118 DVDD10

119 C_MDC

120 C_MDIO

121 P5_TXEN

122 P5_TXD_7

123 P5_TXD_6

124 P5_TXD_5

125 P5_TXD_4

126 P5_TXD_3

127 P5_TXD_2

128 P5_TXD_1

TANA

AVDD10

XO

XI

XTAL_PWD_N

AVDD10

P3_TXVP_A

P3_TXVN_A

P3_TXVP_B

P3_TXVN_B

AVDD33

P3_TXVP_C

P3_TXVN_C

P3_TXVP_D

P3_TXVN_D

AVDD10

P4_TXVP_A

P4_TXVN_A

P4_TXVP_B

P4_TXVN_B

AVDD33

P4_TXVP_C

P4_TXVN_C

P4_TXVP_D

P4_TXVN_D

TDIG

Pin # Pin Name

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91 GSW_CK_SEL

92 DVDD10

93

94

95 DVDD33

96

SCL

SDA

INTR_LPDET

MT7530B/MT7530W

Approval Datasheet

MediaTek Confidential

© 2013 MediaTek Inc.

Page 8

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

loginid=RD04@b-link.net.cn,time=2014-10-21 09:44:38,ip=58.251.146.207,doctitle=MT7530B_MT7530W_approval_datasheet_V0.92.pdf,company=B-LINK_WCN

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc