基于 FPGA 的俄罗斯方块

一、 开发思路

我们项目的主题是开发一款基于 Xilinx 的 ZYBO 开发板的俄罗斯方块游

戏。我们认为,游戏的开发应该分输入控制——游戏逻辑——输出显示三个

模块来开发。

1.1 输入控制

当一款游戏在电脑上运行时,输入一般是鼠标或键盘信号。然而,现在

我们需要把游戏在开发板上实现,因此其输入信号的来源就变成了与板子匹

配的外设。Zybo 开发板上提供了 4 个按键和 4 个开关,这都是可以当作控

制信号的。此外,电脑端的 UART 串口也可以作为控制信号;可扩展的键盘

或是手势识别,也都可以作为控制信号输入给游戏。

1.2 游戏逻辑

游戏逻辑是保证游戏能符合规则正常运行的前提。俄罗斯方块作为一款

人尽皆知的大众化游戏,其规则不难理解:每次有一个由小方块组成的不同

形状的板块陆续从屏幕上方落下来,玩家通过调整板块的位置和方向,使它

们在屏幕底部拼出完整的一条或几条。这些完整的横条会随即消失,给新落

下来的板块腾出空间。与此同时,玩家得到相应的分数奖励。不能被消除的

方块不断堆积起来,一旦堆到屏幕顶端,玩家便告负,游戏结束。我们的俄

罗斯方块的游戏逻辑就是根据以上规则来制定的。

1.3 显示输出

游戏最终是要显示出来给大家玩的,所以最后的显示模块是必不可少的。

现在主要的输出方式主要有 HDMI 和 VGA 两种。考虑到实现起来的复杂度,

我们选择使用 VGA 输出的方式。

在开发方式上,我们有两种方式可以选择:

一种是 RTL 方式,即编写 verilog 代码,直接操控硬件,用电路的方

式来实现游戏的功能;

另一种是嵌入式 PS、PL 协同的方式,即在 Vivado 中搭好硬件,进入

SDK 下编写游戏逻辑,来实现最终游戏的功能。

�

二、 RTL 实现

本项目是基于 Verilog 硬件描述语言的 FPGA 开发。通过 Vivado 综合实

现,VGA 显示器输出,最终完成项目的整体开发。

2.1 实现工具

硬件平台:ZYNQ-7000 开发板、VGA 显示器

软件平台:Vivado 2016.4、Modelsim 10.2c、Visual Studio Code

编程语言:Verilog

2.2 实现过程

项目开发的总体流程为架构设计、模块实现、Vivado 综合、上板验证。

下面将对各个部分进行详细介绍。

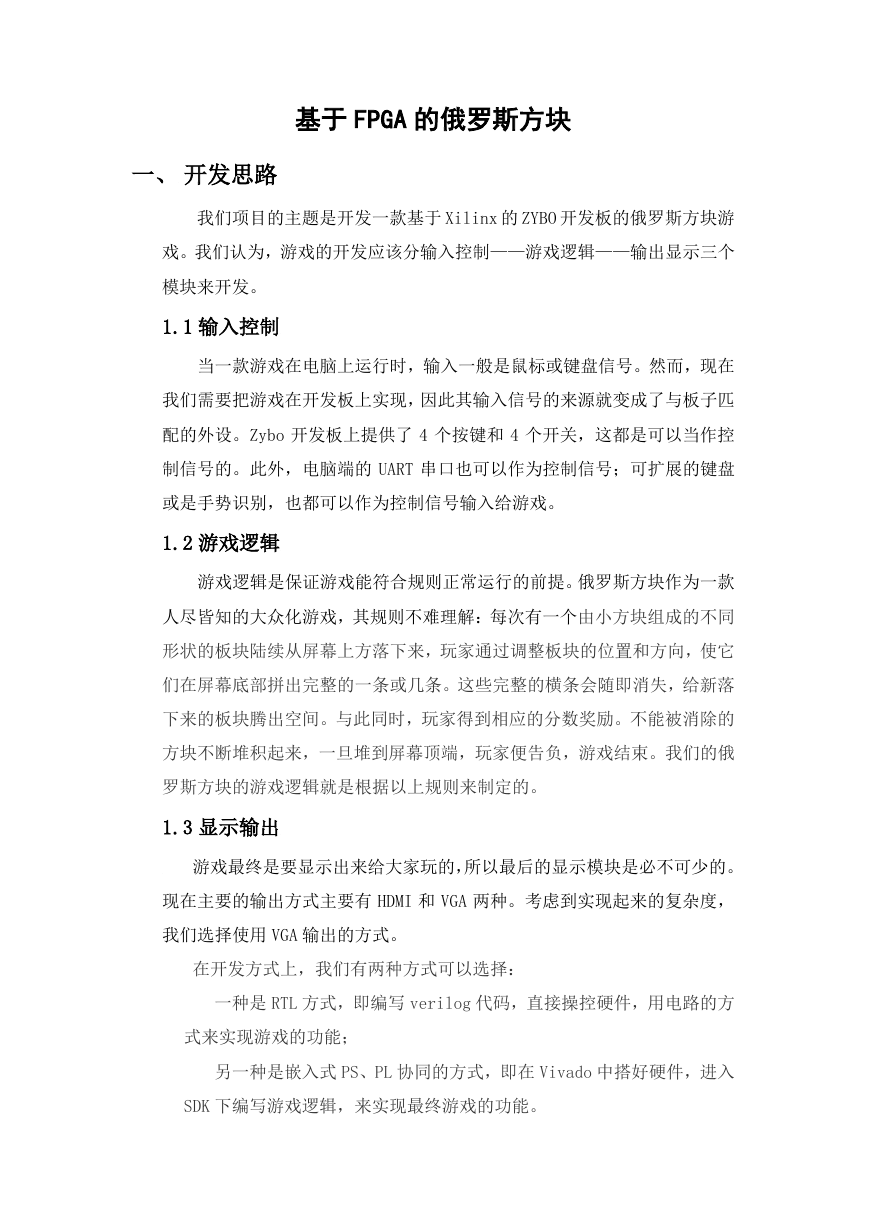

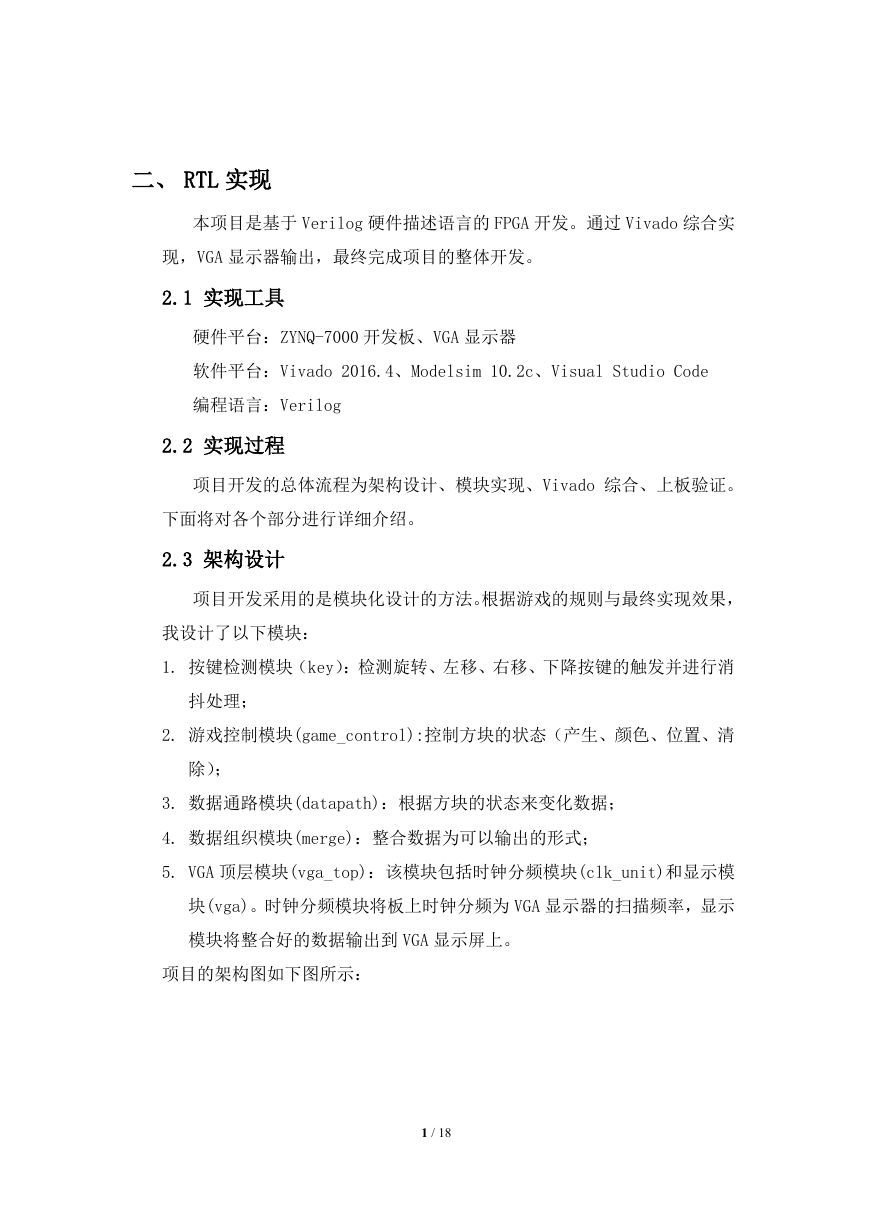

2.3 架构设计

项目开发采用的是模块化设计的方法。根据游戏的规则与最终实现效果,

我设计了以下模块:

1. 按键检测模块(key):检测旋转、左移、右移、下降按键的触发并进行消

抖处理;

2. 游戏控制模块(game_control):控制方块的状态(产生、颜色、位置、清

除);

3. 数据通路模块(datapath):根据方块的状态来变化数据;

4. 数据组织模块(merge):整合数据为可以输出的形式;

5. VGA 顶层模块(vga_top):该模块包括时钟分频模块(clk_unit)和显示模

块(vga)。时钟分频模块将板上时钟分频为 VGA 显示器的扫描频率,显示

模块将整合好的数据输出到 VGA 显示屏上。

项目的架构图如下图所示:

1 / 18

�

2.3 模块实现

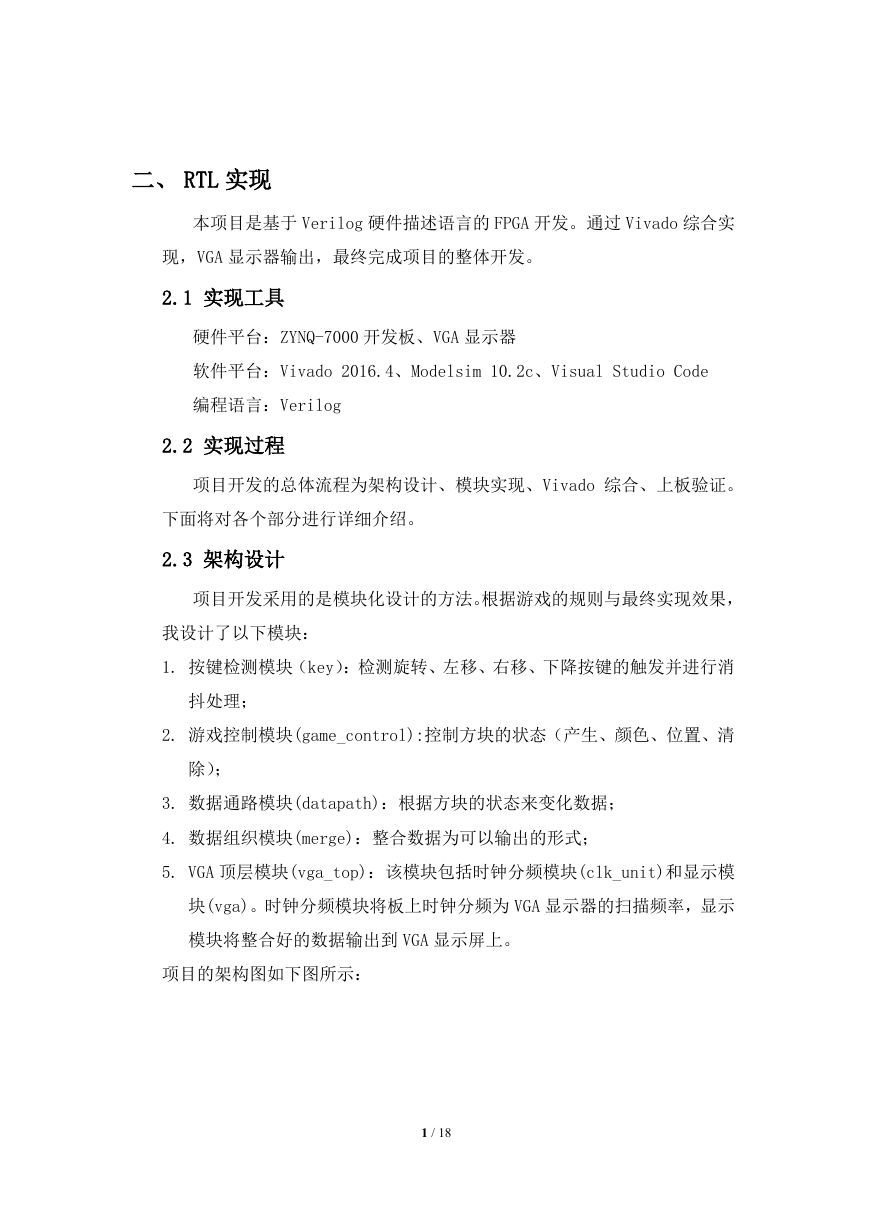

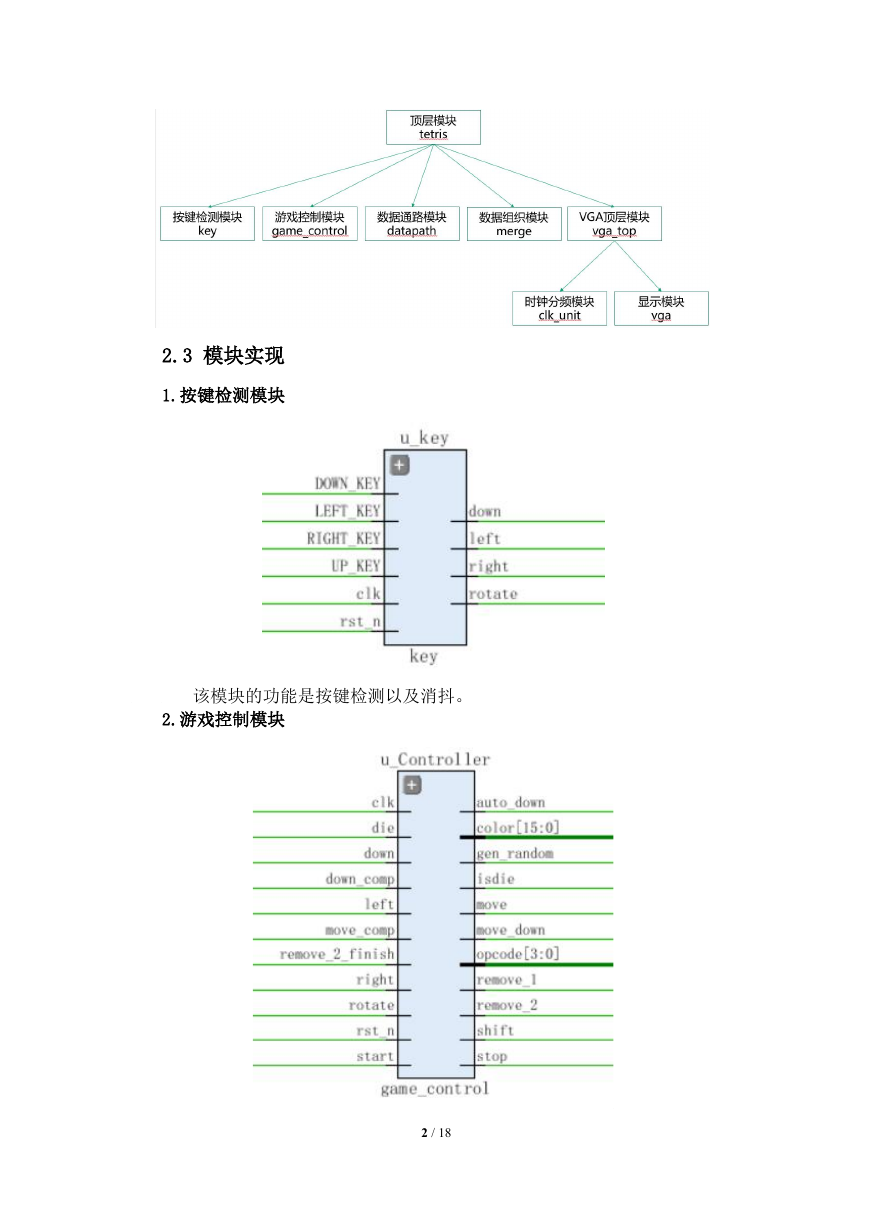

1.按键检测模块

该模块的功能是按键检测以及消抖。

2.游戏控制模块

2 / 18

�

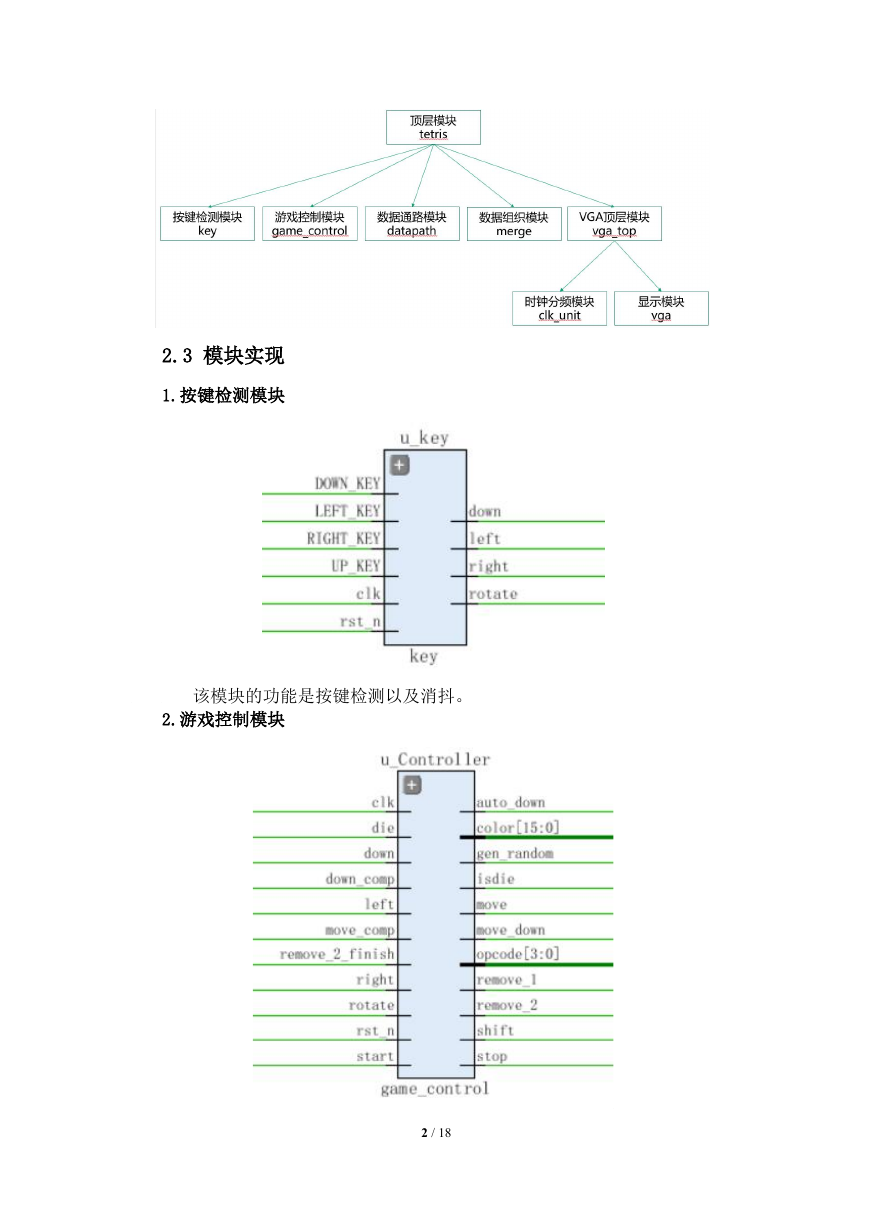

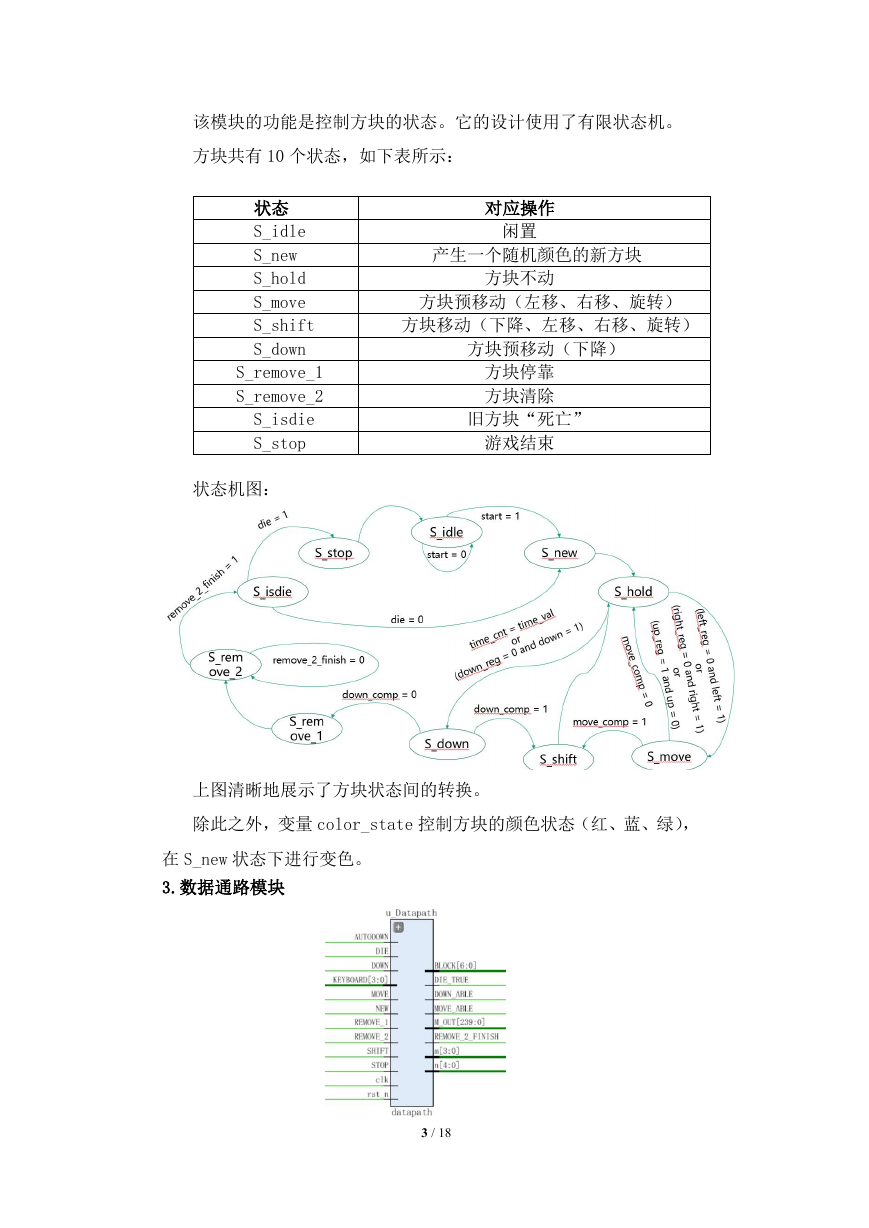

该模块的功能是控制方块的状态。它的设计使用了有限状态机。

方块共有 10 个状态,如下表所示:

状态

S_idle

S_new

S_hold

S_move

S_shift

S_down

S_remove_1

S_remove_2

S_isdie

S_stop

对应操作

闲置

产生一个随机颜色的新方块

方块不动

方块预移动(左移、右移、旋转)

方块移动(下降、左移、右移、旋转)

方块预移动(下降)

方块停靠

方块清除

旧方块“死亡”

游戏结束

状态机图:

上图清晰地展示了方块状态间的转换。

除此之外,变量 color_state 控制方块的颜色状态(红、蓝、绿),

在 S_new 状态下进行变色。

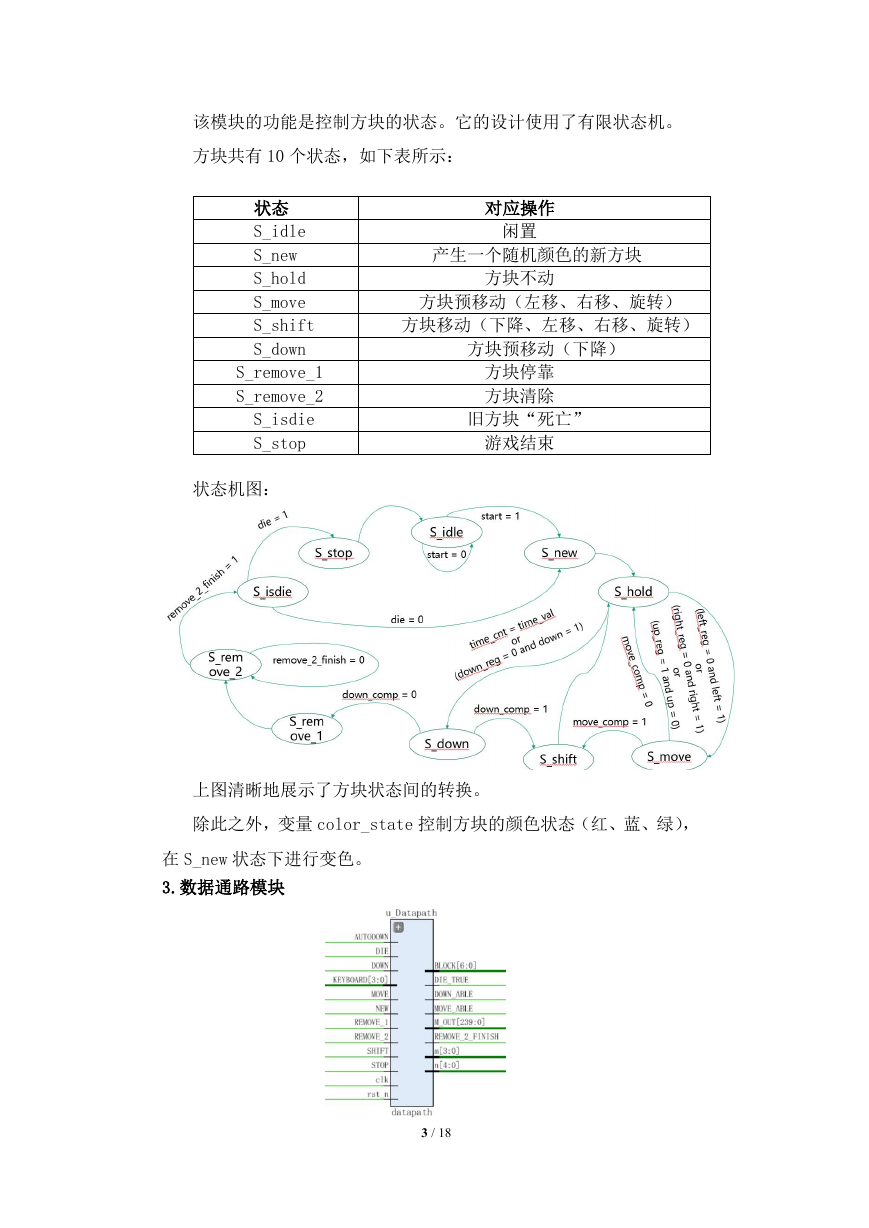

3.数据通路模块

3 / 18

�

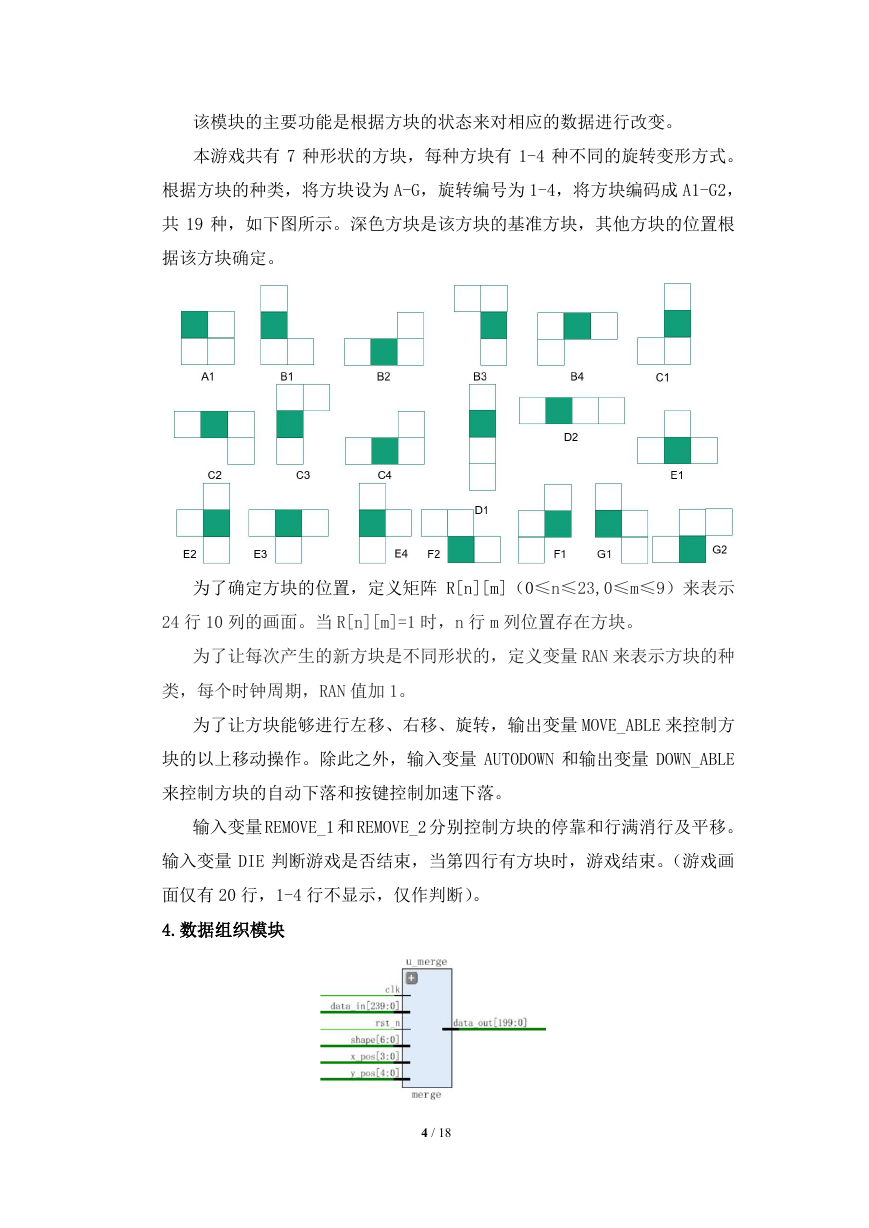

该模块的主要功能是根据方块的状态来对相应的数据进行改变。

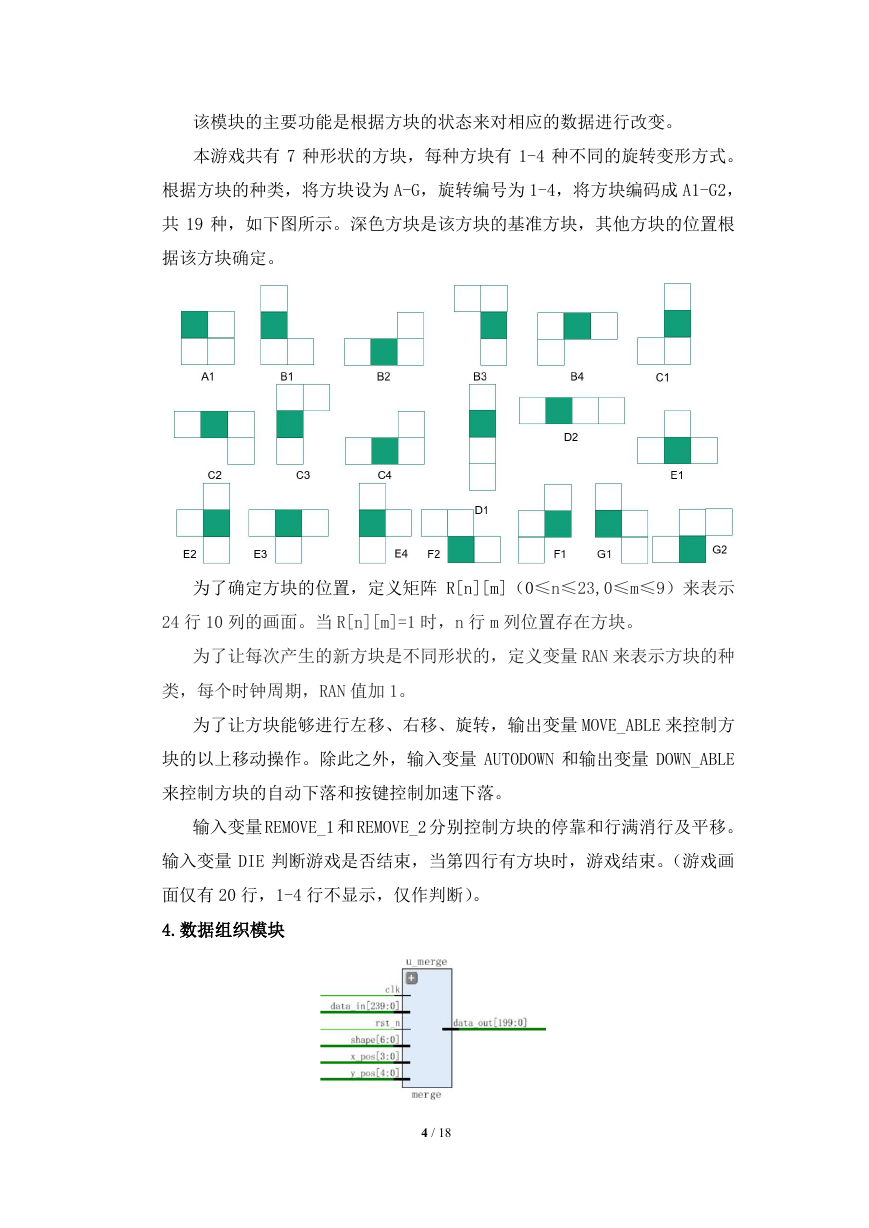

本游戏共有 7 种形状的方块,每种方块有 1-4 种不同的旋转变形方式。

根据方块的种类,将方块设为 A-G,旋转编号为 1-4,将方块编码成 A1-G2,

共 19 种,如下图所示。深色方块是该方块的基准方块,其他方块的位置根

据该方块确定。

为了确定方块的位置,定义矩阵 R[n][m](0≤n≤23,0≤m≤9)来表示

24 行 10 列的画面。当 R[n][m]=1 时,n 行 m 列位置存在方块。

为了让每次产生的新方块是不同形状的,定义变量 RAN 来表示方块的种

类,每个时钟周期,RAN 值加 1。

为了让方块能够进行左移、右移、旋转,输出变量 MOVE_ABLE 来控制方

块的以上移动操作。除此之外,输入变量 AUTODOWN 和输出变量 DOWN_ABLE

来控制方块的自动下落和按键控制加速下落。

输入变量 REMOVE_1 和 REMOVE_2 分别控制方块的停靠和行满消行及平移。

输入变量 DIE 判断游戏是否结束,当第四行有方块时,游戏结束。(游戏画

面仅有 20 行,1-4 行不显示,仅作判断)。

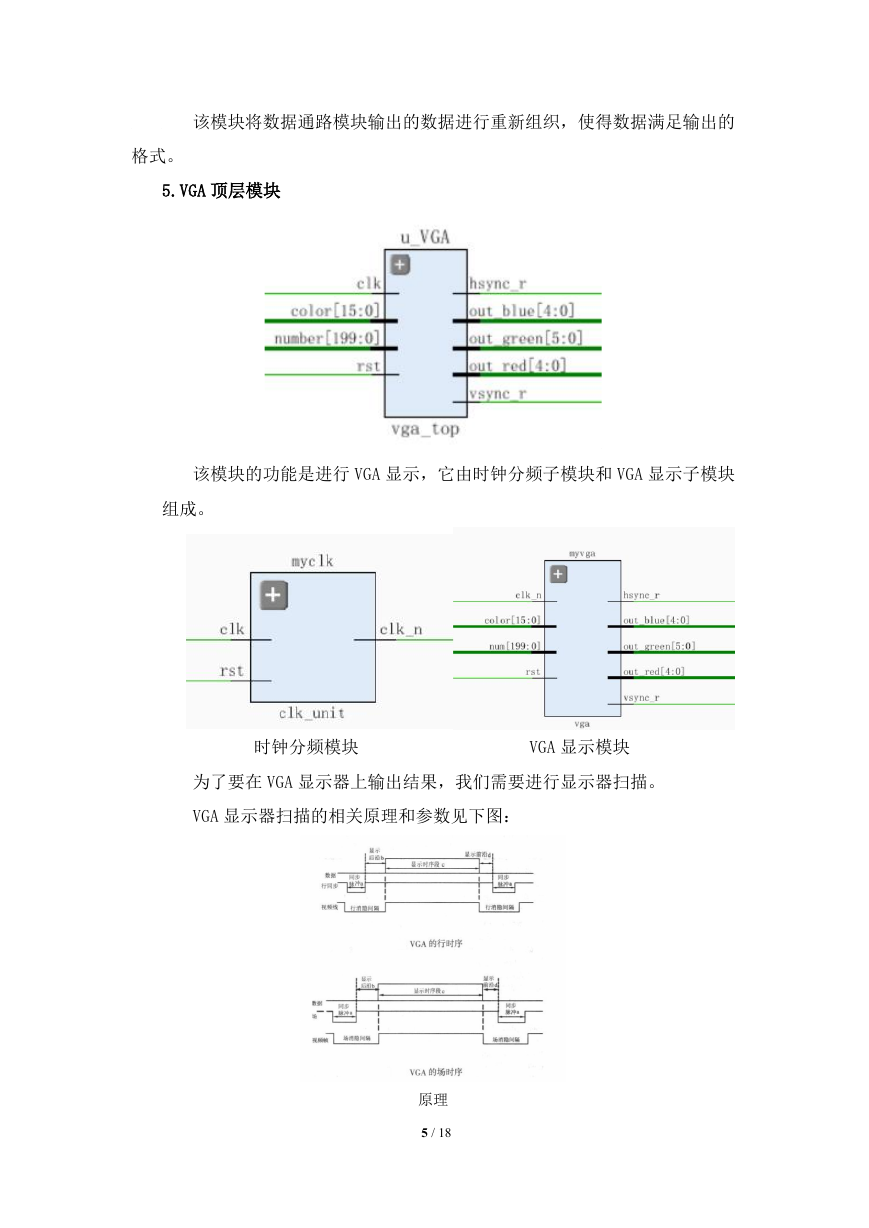

4.数据组织模块

4 / 18

�

该模块将数据通路模块输出的数据进行重新组织,使得数据满足输出的

格式。

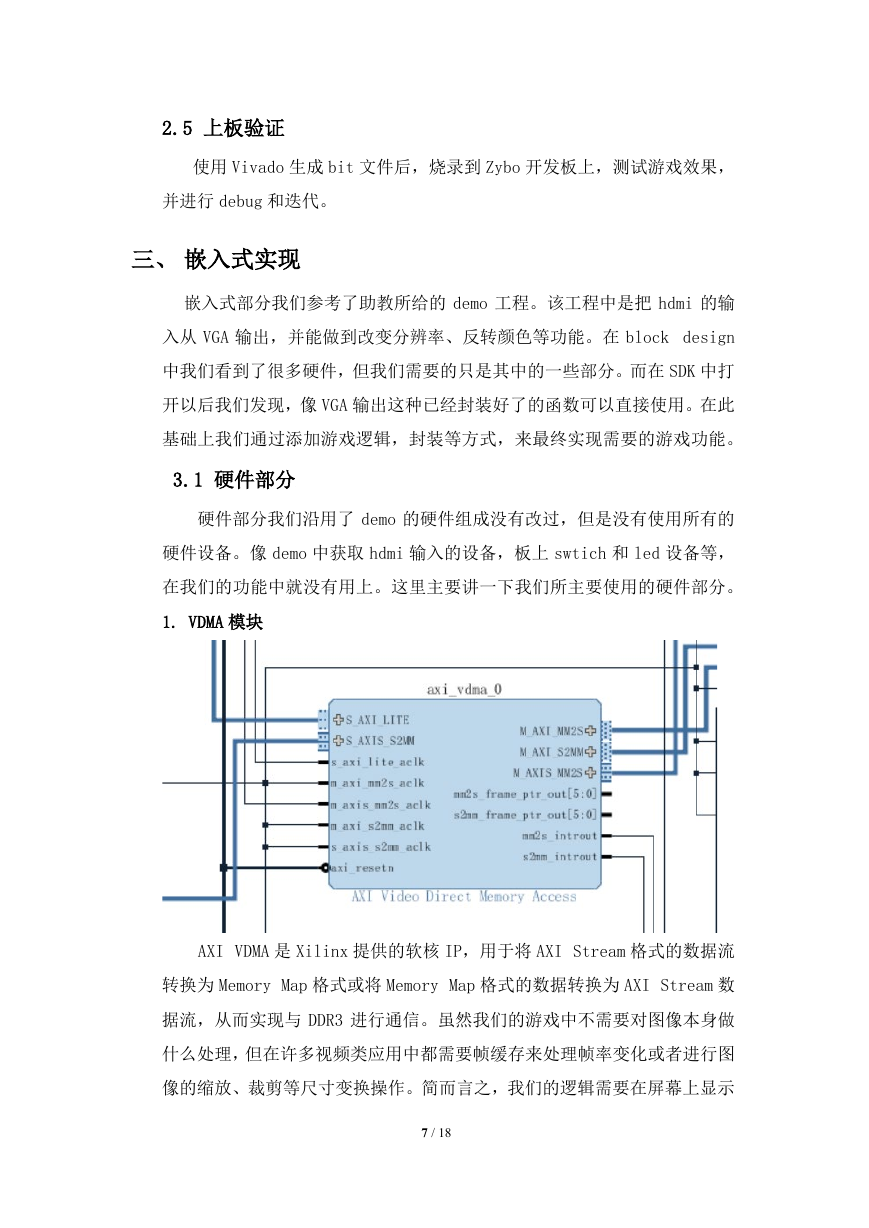

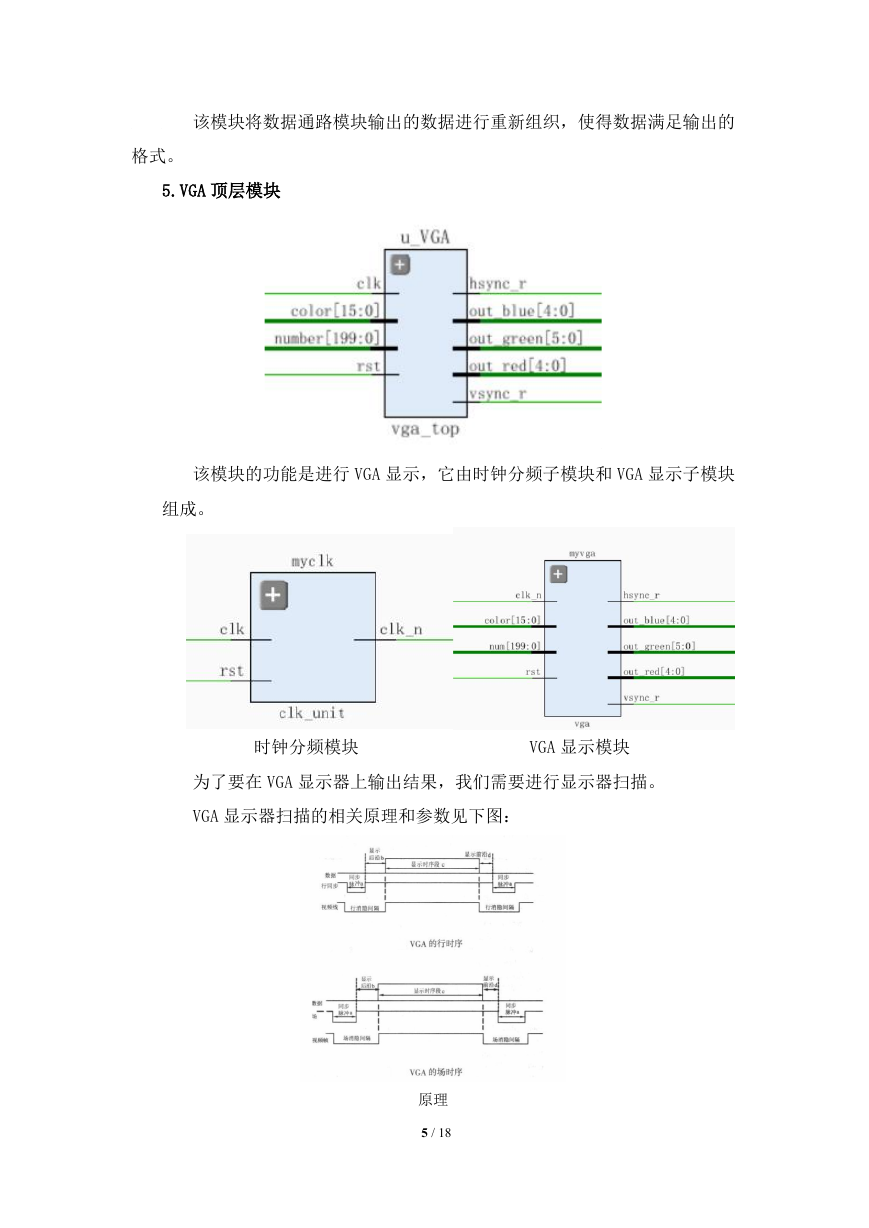

5.VGA 顶层模块

该模块的功能是进行 VGA 显示,它由时钟分频子模块和 VGA 显示子模块

组成。

时钟分频模块

VGA 显示模块

为了要在 VGA 显示器上输出结果,我们需要进行显示器扫描。

VGA 显示器扫描的相关原理和参数见下图:

原理

5 / 18

�

参数

由上图我们可以知道,显示器扫描的频率约为 25MHZ,因此我们需要用

时钟分频模块对我们的板上时钟(频率为 125MHZ)进行分频,与显示器扫描

频率保持一致。

在 VGA 显示模块中,模拟显示器逐行扫描的过程,将游戏画面显示在屏

幕正中央。

游戏界面中,有方块处显示相应颜色的方块,无方块处显示白色背景;

游戏界面外显示黑色背景。

2.4 Vivado 综合

模块设计完成后,使用 Vivado 建立工程,并进行综合。

综合完成后,先进行相应的管脚绑定,管脚绑定如下图所示:

查看资源报告、能耗报告以及时序报告,在第四节中与 SDK 实现进行对

比。

6 / 18

�

2.5 上板验证

使用 Vivado 生成 bit 文件后,烧录到 Zybo 开发板上,测试游戏效果,

并进行 debug 和迭代。

三、 嵌入式实现

嵌入式部分我们参考了助教所给的 demo 工程。该工程中是把 hdmi 的输

入从 VGA 输出,并能做到改变分辨率、反转颜色等功能。在 block design

中我们看到了很多硬件,但我们需要的只是其中的一些部分。而在 SDK 中打

开以后我们发现,像 VGA 输出这种已经封装好了的函数可以直接使用。在此

基础上我们通过添加游戏逻辑,封装等方式,来最终实现需要的游戏功能。

3.1 硬件部分

硬件部分我们沿用了 demo 的硬件组成没有改过,但是没有使用所有的

硬件设备。像 demo 中获取 hdmi 输入的设备,板上 swtich 和 led 设备等,

在我们的功能中就没有用上。这里主要讲一下我们所主要使用的硬件部分。

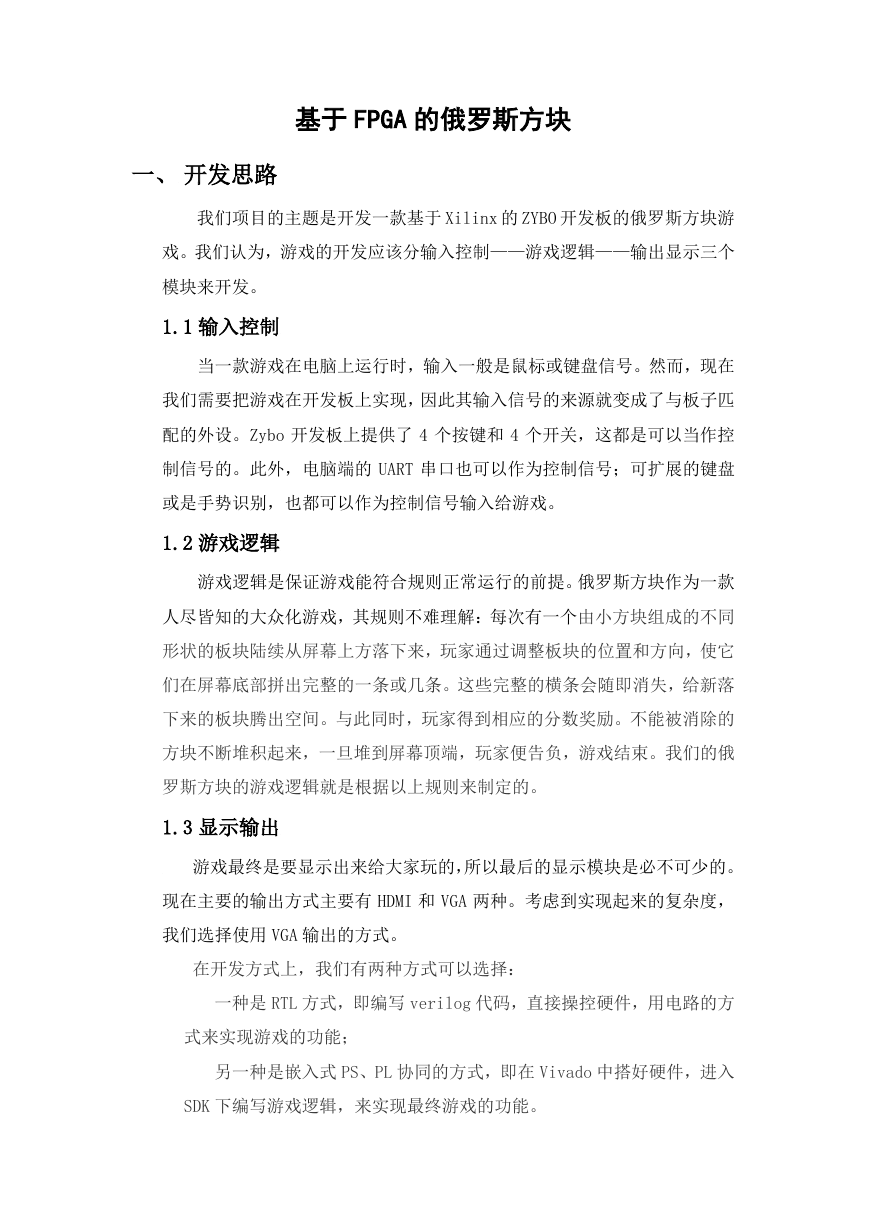

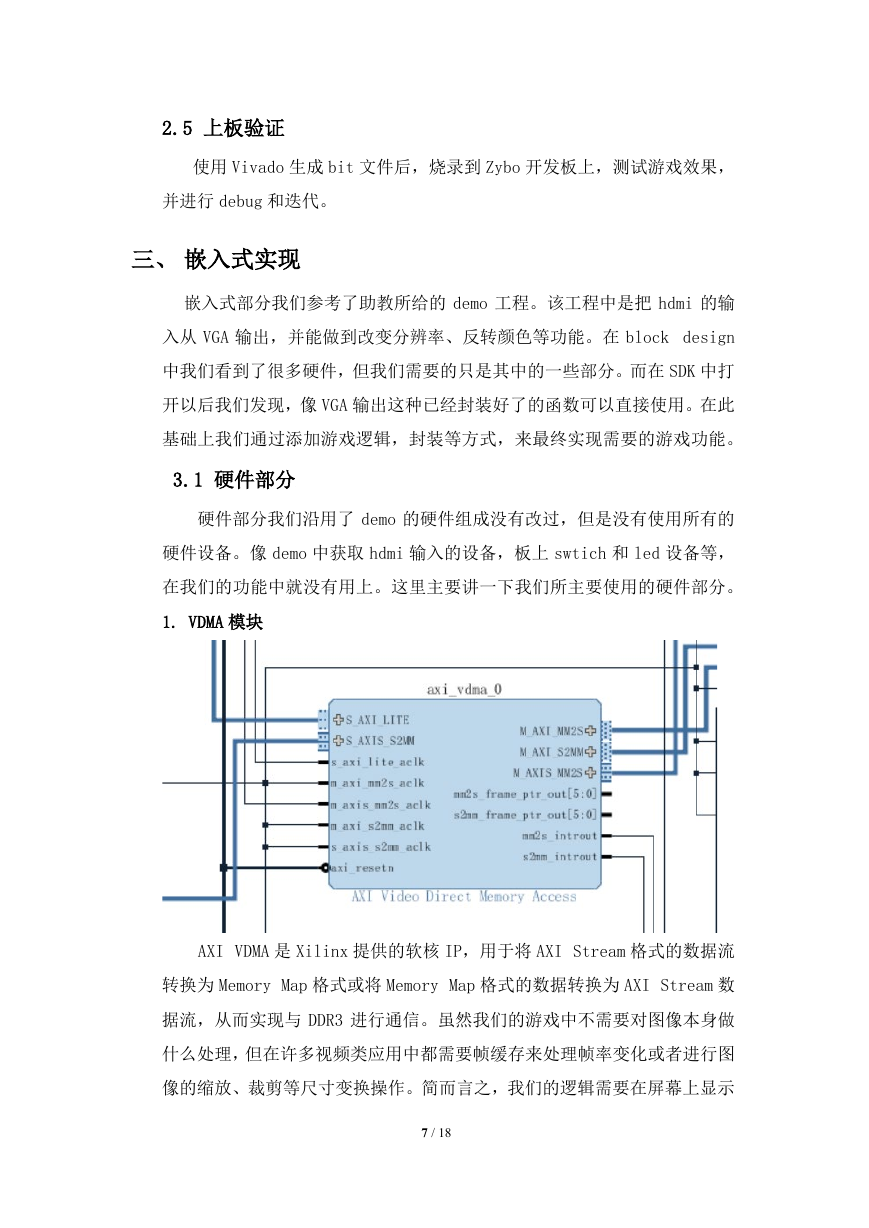

1. VDMA 模块

AXI VDMA 是 Xilinx 提供的软核 IP,用于将 AXI Stream 格式的数据流

转换为 Memory Map 格式或将 Memory Map 格式的数据转换为 AXI Stream 数

据流,从而实现与 DDR3 进行通信。虽然我们的游戏中不需要对图像本身做

什么处理,但在许多视频类应用中都需要帧缓存来处理帧率变化或者进行图

像的缩放、裁剪等尺寸变换操作。简而言之,我们的逻辑需要在屏幕上显示

7 / 18

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc