AXI Quad SPI v3.2

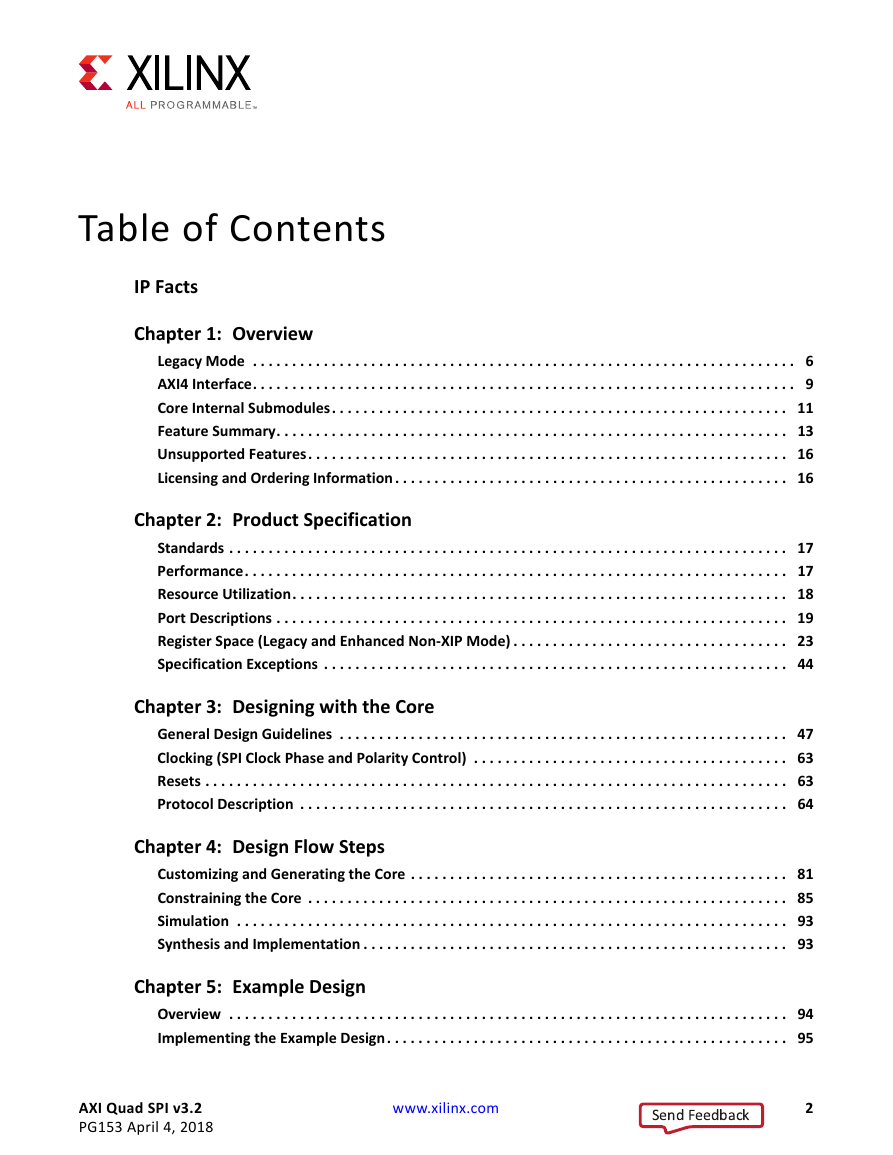

Table of Contents

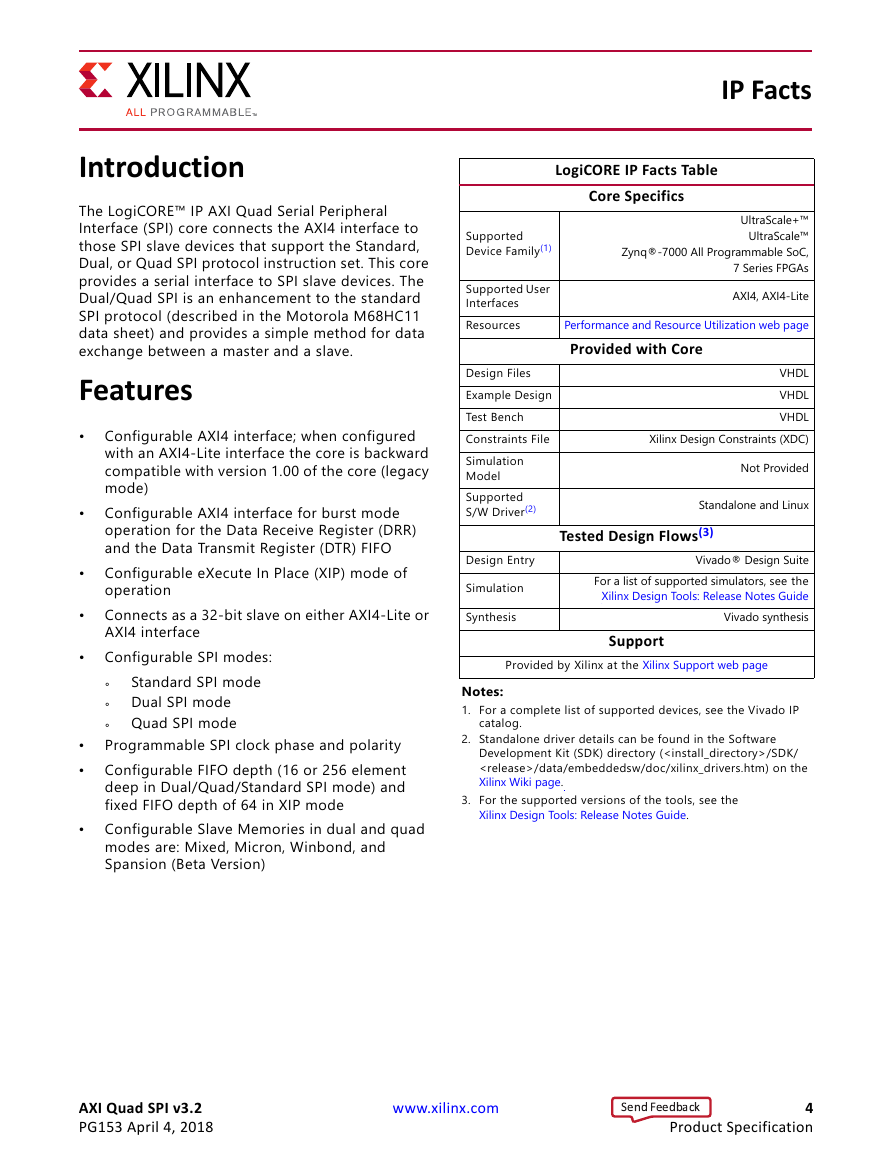

IP Facts

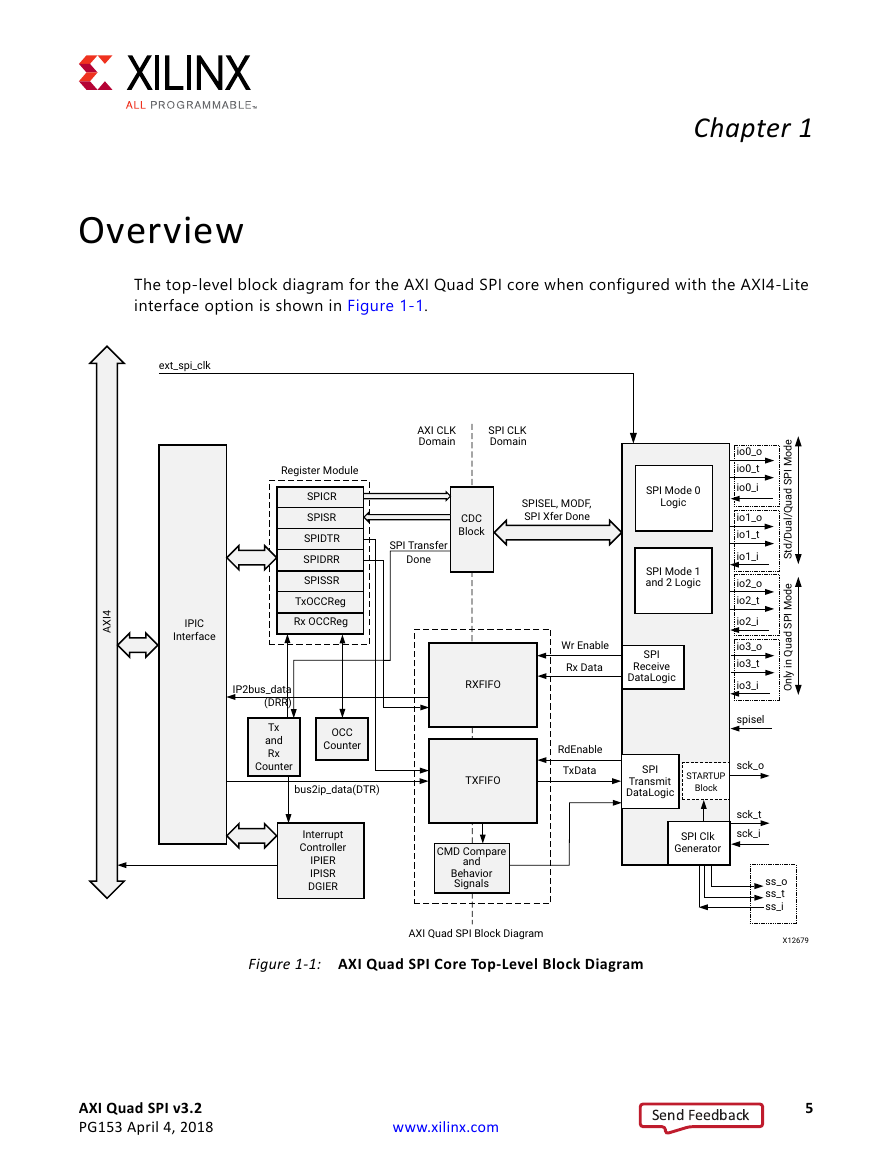

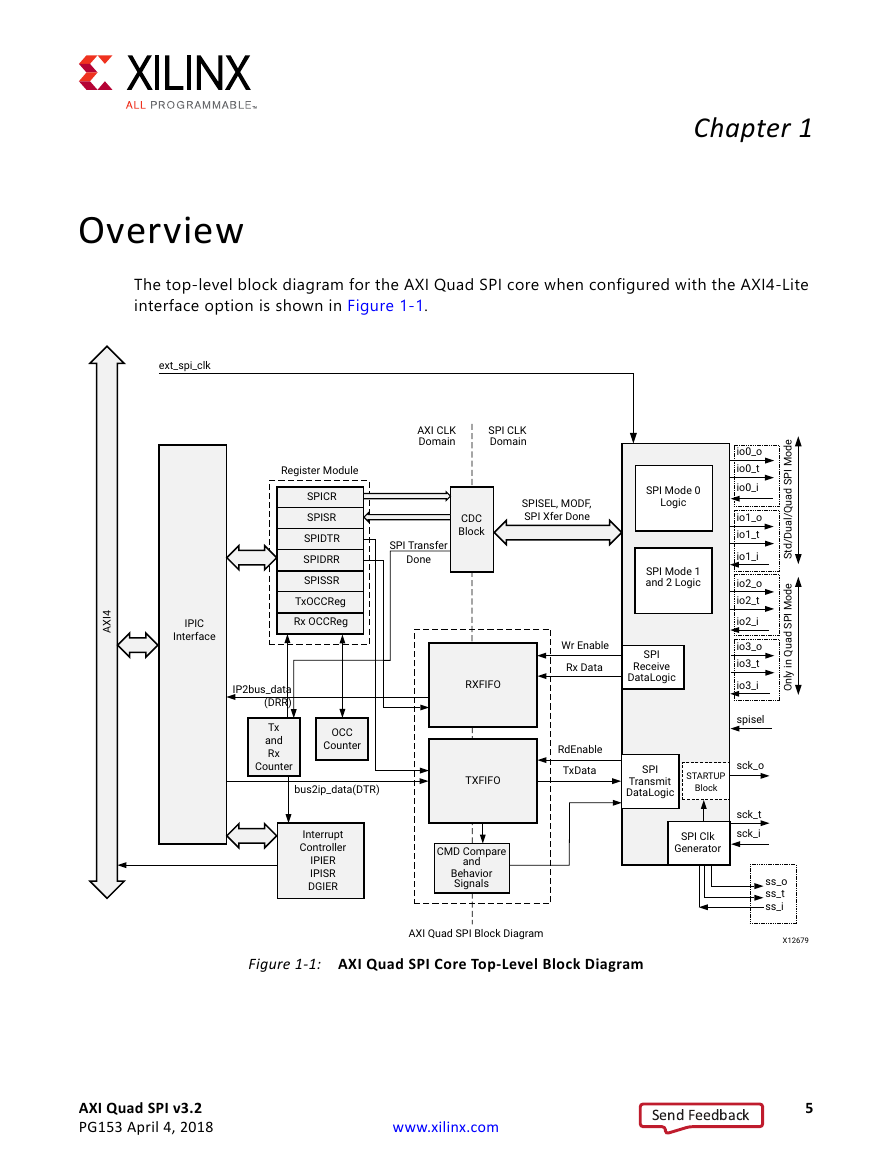

Ch. 1: Overview

Legacy Mode

Standard SPI Mode

Dual/Quad SPI Mode

Common Information for Both SPI Modes

AXI4 Interface

Enhanced Mode

XIP Mode

Dual Quad SPI Mode

Core Internal Submodules

Enable Performance Mode Not Selected

AXI4-Lite Interface Module

SPI Register Module

Interrupt Controller Register Set Module

SPI Module

Optional FIFOs

STARTUPEn Module

Enable STARTUPE2 Primitive Parameter

Enable STARTUPE3 Primitive Parameter

Quad SPI Control Logic Module

Feature Summary

Unsupported Features

Licensing and Ordering Information

Ch. 2: Product Specification

Standards

Performance

Resource Utilization

Port Descriptions

Register Space (Legacy and Enhanced Non-XIP Mode)

Register Details

Software Reset Register

SPI Control Register

SPI Status Register

SPI Data Transmit Register

Dual/Quad Mode

SPI Data Receive Register

SPI Slave Select Register

SPI Transmit FIFO Occupancy Register

SPI Receive FIFO Occupancy Register

Interrupt Register Set Description

Device Global Interrupt Enable Register

IP Interrupt Status Register (IPISR)

IP Interrupt Enable Register (IPIER)

XIP Mode

XIP Mode Commands

XIP Configuration Register

XIP Status Register

Specification Exceptions

Exceptions from the Motorola M68HC11-Rev. 4.0 Reference Manual

Other Exceptions

Ch. 3: Designing with the Core

General Design Guidelines

Functionality Based on AXI Interfaces

AXI4-Lite Interface

AXI4 Interface (Enhanced Mode)

AXI4 Read-Only Interface (XIP Mode)

Standard SPI Device Features with Only AXI4-Lite Interface

AXI4-Lite Interface Functionality in Standard SPI Multi-Master Configuration

AXI4-Lite Interface Standard SPI Mode — Optional FIFOs in Legacy Mode

AXI4-Lite Interface Dual/Quad SPI Mode — Optional FIFO Depth

AXI4-Lite Interface SPI Master Loopback Operation

AXI4-Lite Interface Hardware Error Detection

Setting the Frequency Ratio Parameter

AXI4-Lite Interface SPI Slave Mode — Standard SPI Configuration in Legacy Mode Only

Using the Enable STARTUPEn Primitive Parameter

Enable STARTUPEn Primitive is Selected

Core Behavior and Ports

Using the Dual Quad Mode

Enable STARTUPEn Primitive is Not Selected

Core Behavior and Ports

Core Behavior in Legacy and Enhanced Non-XIP Mode

Core Behavior in XIP Mode

Winbond Memory

Micron Memory

Spansion Memory

Commonly Supported Commands for Dual SPI and Mixed Memory Mode

Commonly Supported Commands for Quad SPI and Mixed Memory Mode

XIP Mode Commands

Winbond Memory (Ex: W25Q64VSFIG)

Micron Memory (Ex: N25Q256)

Spansion Memory (Ex: S70FL01GS)

Clocking (SPI Clock Phase and Polarity Control)

Resets

Protocol Description

AXI Quad SPI Core Behavior in Legacy and Enhanced Mode

Mode = Dual

Slave Device = Mixed

Slave Device = Winbond

Slave Device = Micron

Slave Device = Spansion

Mode = Quad

Slave Device = Mixed

Slave Device = Winbond

Slave Device = Micron

Slave Device = Spansion

Core Behavior in XIP Mode

Standard SPI Mode Transactions

SPI Master Device with/without FIFOs and Slave Select Vector Asserted Manually Using SPICR Bit 7

SPI Master and Slave Devices without FIFOs Performing One 8-bit/16-bit/ 32-bit Transfer (Optional Mode)

SPI Master and Slave Devices where Registers/FIFOs are Filled Before the SPI Transfer Begins and Multiple Discrete 8-bit Transfers are Performed (Optional Mode)

SPI Master and Slave Devices with FIFOs Where Some Initial Data is Written to FIFOs, the SPI Transfer is Started, Data is Written to the FIFOs as Fast or Faster than the SPI Transfer and Multiple Discrete 8-bit Transfers are Performed (Optional Mode).

Dual/Quad SPI Mode Transactions

Dual/Quad Mode SPI Configuration

Transfer Formats

CPHA Equals Zero Transfer Format

CPHA Equals One Transfer Format

SPI Protocol Slave Select Assertion Modes

SPI Protocol with Automatic Slave Select Assertion

SPI Protocol with Manual Slave Select Assertion

Beginning and Ending SPI Transfers

Transfer Begin Period

Transfer End Period

Ch. 4: Design Flow Steps

Customizing and Generating the Core

AXI Interface Options

SPI Options

Remaining Options

User Parameters

Output Generation

Constraining the Core

Required Constraints

Write Operation to SPI

Read Operation

Constraining the IP

Constraints in Dual Quad Mode

Device, Package, and Speed Grade Selections

Clock Frequencies

Clock Management

Clock Placement

Banking

Transceiver Placement

I/O Standard and Placement

Simulation

Synthesis and Implementation

Ch. 5: Example Design

Overview

Implementing the Example Design

Testing the Example Design on a KC705 Board

Legacy Mode and Performance Mode Example Design Behavior

XIP Mode Example Design Behavior

Simulating the Example Design

Setting up the Simulation

Example Programming Sequence

Write Enable Command Sequence

Erase Command Sequence

Write Data Command Sequence

Read Data Command Sequence

Ch. 6: Test Bench

Overview

Checking Results

Appx. A: Verification, Compliance, and Interoperability

Appx. B: Migrating and Upgrading

Migrating to the Vivado Design Suite

Upgrading in the Vivado Design Suite

Appx. C: Debugging

Finding Help on Xilinx.com

Documentation

Answer Records

Technical Support

Vivado Design Suite Debug Feature

Hardware Debug

Interface Debug

AXI4-Lite Interfaces

AXI4 Interfaces

Enhanced Mode Debug

XIP Mode Debug

Appx. D: Additional Resources and Legal Notices

Xilinx Resources

References

Revision History

Please Read: Important Legal Notices

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc