嵌入式技术 Embedded Technology

一种改进 Turbo 码译码器的 FPGA 设计与实现

( 哈 尔 滨 工 程 大 学 信 息 与 通 信 工 程 学 院 , 黑 龙 江 哈 尔 滨 150001)

赵 旦 峰 , 罗 清 华 , 焉 晓 贞

摘 要 : 提 出 了 一 种 基 于 MAX- Log- MAP 算 法 的 更 有 效 减 小 译 码 延 时 的 方 法 , 通 过 并 行 计 算 前 向

状 态 度 量 和 后 向 状 态 度 量 , 将 半 次 迭 代 译 码 延 时 缩 短 一 半 , 而 译 码 性 能 没 有 损 失 , 同 时 也 减 小 了 硬 件

实 现 中 的 时 序 控 制 复 杂 度 。 仿 真 表 明 , 该 方 法 有 效 降 低 了 译 码 的 延 时 , 并 且 性 能 没 有 损 失 , 具 有 较 高

的 实 用 价 值 。

关 键 词 : Turbo 码 ; MAX- Log- MAP; FPGA

Design and implementation of an improved Turbo decoder based on FPGA

(School of Information and Communication Engineering, Harbin Engineering University, Harbin 150001 , China)

ZHAO Dan Feng, LUO Qing Hua , YAN Xiao Zhen

Abs tract : Base on MAX- Log- MAP algorithm, by parallel computing the forward state metric and backward metric, this paper

loss in coding

presented a more powerful decoding scheme which could reduce the total

the plan

performance. At

effectively decreases the latency of a half- iteration without loss in coding performance. Thus, this plan has a lot of practical value.

the difficulty of time sequence control were reduced. Finally,

latency of a half- iteration to half without

the simulation showed that

the same time,

Key words : Turbo code ; MAX- Log- MAP ; FPGA

Turbo 码 又 称 并 行 级 联 卷 积 码 (PCCC), 1993 年 由 Berro

等 人 在 ICC 国 际 会 议 上 提 出 。 由 于 其 充 分 利 用 了 Shan-

non 信 道 编 码 定 理 的 随 机 化 编 码 条 件 , 因 此 获 得 几 乎 接

近 Shannon 理 论 极 限 的 译 码 性 能 [1]。

Turbo 码 在 低 信 噪 比 应 用 环 境 下 的 优 异 性 能 , 使 得

其 在 很 多 通 信 系 统 中 拥 有 非 常 好 的 应 用 前 景 。 第 三 、四

代 移 动 通 信 系 统 的 多 种 方 案 , 都 将 Turbo 码 作 为 信 道 编

码 的 方 案 之 一 。 但 是 , Turbo 码 存 在 着 译 码 时 延 长 、硬 件

实 现 复 杂 度 高 的 问 题 , 这 使 得 其 实 现 和 应 用 都 受 到 了 一

定 的 局 限 。 人 们 也 推 出 了 一 些 减 小 译 码 延 时 的 译 码 方

法 , 例 如 分 块 并 行 、滑 窗 等 方 法 。但 是 这 些 译 码 方 法 对 应

的 译 码 性 能 有 损 失 , 而 且 在 硬 件 实 现 上 控 制 时 序 也 比 较

复 杂 。 本 文 给 出 了 一 种 更 加 有 效 减 小 译 码 延 时 方 法 , 其

译 码 性 能 没 有 性 能 损 失 , 硬 件 实 现 时 的 时 序 控 制 相 对 简

单 , 存 储 空 间 也 有 一 定 的 减 少 。

1 改 进 译 码 方 法

成 员 译 码 器 (DEC1 , DEC2)首 先 根 据 输 入 的 外 信 息 和

接 收 到 的 信 息 序 列 进 行 正 向 (按 帧 长 从 前 向 后 的 顺 序 )分

支 度 量 值 计 算 和 前 向 递 归 计 算 , 同 时 进 行 反 向 ( 按 帧 长

的 逆 序 ) 分 支 度 量 值 计 算 和 后 向 递 归 计 算 。 当 正 向 递 归

计 算 和 反 向 递 归 计 算 到 帧 长 一 半 ( N/2 ) 时 , 进 行 正 向 对

32

欢迎网上投稿 www.chinaaet.com

数 似 然 比 计 算 和 反 向 对 数 似 然 比 计 算 , 同 时 计 算 出 对 应

的 外 信 息 经 过 交 织 后 作 为 另 一 个 成 员 译 码 器 的 输 入 先

验 信 息 。

这 样 每 半 次 迭 代 过 程 可 分 如 下 二 个 步 骤 进 行 :

(1) 第 一 步 : DEC 正 向 分 支 转 移 度 量 !k 计 算 和 DEC

前 向 递 归 "k 计 算 [2][3], 同 时 进 行 反 向 分 支 转 移 度 量 !j 计

算 和 DEC 后 向 递 归 #j 计 算 :

!k(s′, s)=Ak(Lc·yk , l·uk+Lc·yk , v·xk , v+uk·L(uk))

(1)

其 中 : s′为 前 一 状 态 , s 为 后 一 状 态 , k 为 对 应 的 状 态 数 ,

uk 为 编 码 的 信 息 位 , xk , v 为 校 验 位 , yk , l 为 接 收 到 的 信 息

位 , yk , v 为 接 收 到 校 验 位 , Ak 为 一 个 常 数 , Lc 为 信 道 可 信

度 。 同 时 进 行 前 向 递 归 :

"k(s)=max(s ′, s ) ([! u

= 0 (s′, s)+"k- 1(s′)])

(2)

k(s)的初始化条件为( 假定编码器的初始态为零状态) :

(3)

0(0)=1 ,

= 1 (s′, s)+"k- 1(s′)], [! u

0(s≠0)=0

"

i

i

k

i

k

"

"

DEC 反 向 递 归 :

$j(s)=max(s ′, s ) ([! u

k

= 1 (s′, s)+$k+1(s)], [! u

= 0 (s′, s)+$k+1(s)])

(4)

对 于 $ 的 初 始 化 , 如 果 编 码 在 每 帧 编 码 之 后 通 过 加

k

《电子技术应用》2008 年第 3 期

�

嵌入式技术 Embedded Technology

入 归 零 比 特 使 编 码 状 态 回 到 零 状 态 。 则 可 初 始 为 :

i

L(0)=1 ,

i

L(s≠0)=0

!

!

否 则 , 应 设 定 为 :

L(s)=1/2v,

!

这 里 v 为 编 码 成 员 码 中 寄 存 器 的 个 数 。

"s

i

(5)

(6)

(2) 第 二 步 : 正 向 对 数 似 然 值 L(u! k) 计 算 和 反 向 对 数

似 然 比 L(u! k) 计 算 , 同 时 计 算 对 应 的 外 信 息 Le(u! k), 然 后

进 行 交 织 :

L(u! k)=max(s ′, s )

uk = 1

(["k(s′, s)+#k- 1(s)]+!k(s′)], ["k(s′, s)+

#k(s)]+!k(s′)])(7)- max(s ′, s )

!k(s′)], ["k(s′, s)+#k(s)]+!k(s′)])

uk = 0

(["k(s′, s)+#k- 1(s)]+

(7)

(8)

(9)

Le(u! k)=L(u! k)- yk , l- L(uk)

L(uk)=$(Le(u! k))

其 中 $()为 交 织 函 数 。

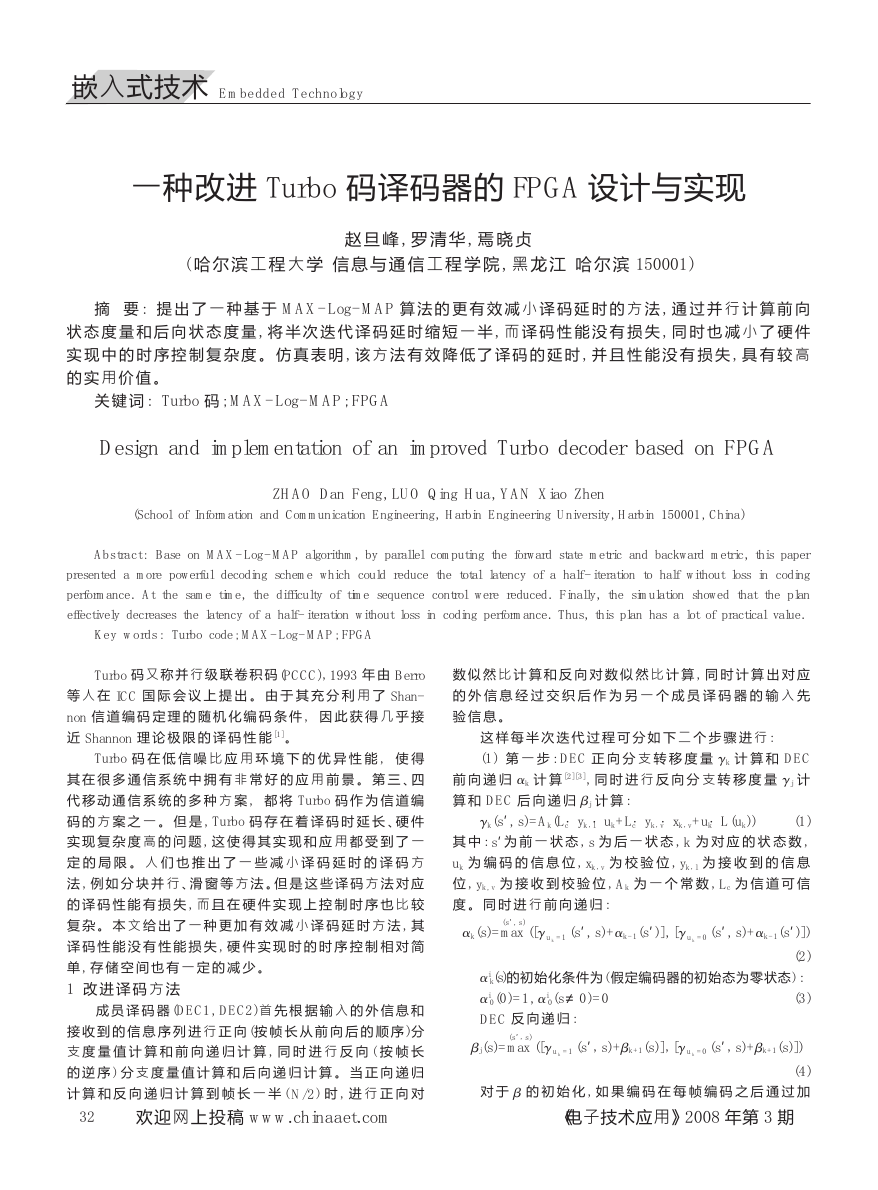

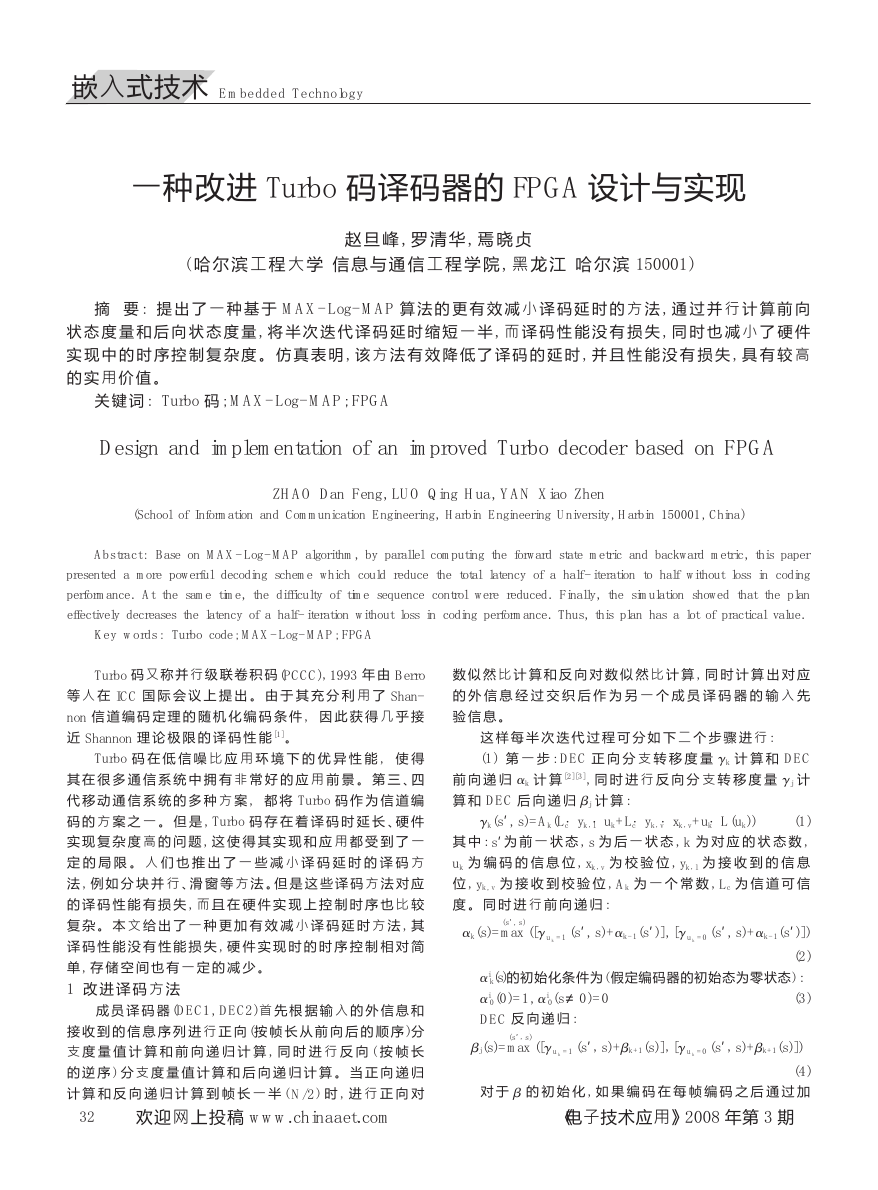

经 典 译 码 和 改 进 译 码 方 法 的 半 次 迭 代 ( 一 个 子 译 码

的 译 码 过 程 ) 对 应 的 时 序 图 如 图 1 所 示 。 由 图 1 可 知 对

应 半 次 迭 代 译 码 延 时 为 T, 图 中 下 半 部 分 是 改 进 的 译 码

时 序 , 改 进 的 译 码 延 时 为 T/2 。 这 种 新 的 译 码 方 法 能 将

译 码 延 时 缩 短 一 半 。由 于 在 整 个 计 算 过 程 中 没 有 采 用 任

何 近 似 计 算 , 所 以 译 码 性 能 没 有 任 何 损 失 。 在 计 算 过 程

中 , 不 需 要 对 "k(s′, s)进 行 存 储 , 从 而 减 少 了 在 硬 件 实 现

时 所 需 的 存 储 容 量 。

0

"k

#k

0

"k

#k

N

"j

!j

0

N

2

LLR

LLR

N

2

N N

0

!k

LLR

N

0

T

2

T

t

R

E

B

图 1 经 典 译 码 和 改 进 译 码 时 序 图

2 与 其 他 译 码 方 法 的 比 较

为 了 减 小 译 码 延 时 , 人 们 推 出 了 分 块 并 行 译 码 算

法 、滑 窗 译 码 等 方 法 。它 们 都 采 用 了 相 应 的 近 似 计 算 , 从

而 在 译 码 性 能 上 或 多 或 少 有 些 损 失 , 它 们 都 是 通 过 牺 牲

译 码 性 能 来 换 取 减 小 译 码 延 时 的 , 同 时 它 们 硬 件 实 现 时

的 时 序 控 制 也 比 较 复 杂 。

分 块 并 行 是 将 接 收 的 整 个 码 字 分 成 若 干 子 块 [ 4 ] [ 5 ],

各 子 块 进 行 并 行 处 理 , 其 中 各 子 块 的 前 后 向 递 推 公 式 的

初 始 值 由 相 邻 子 块 的 前 一 次 迭 代 译 码 的 边 界 计 算 值 传

递 , 这 样 就 引 入 了 近 似 计 算 , 译 码 性 能 就 有 一 定 损 失 。设

经 典 半 次 迭 代 译 码 延 时 为 T, 分 块 的 块 数 为 M, 则 分 块

并 行 译 码 方 法 的 译 码 延 时 为 T/M。 但 是 , 由 于 它 的 控 制

时 序 很 复 杂 , 因 而 硬 件 实 现 复 杂 度 较 高 。

对 于 滑 窗 译 码 方 法 而 言 [6 ] [7 ], 它 通 过 预 先 递 推 一 段

后 向 递 归 量 作 为 真 正 计 算 后 向 递 归 的 初 值 , 也 采 取 了 近

似 计 算 , 因 而 译 码 性 能 也 有 一 定 的 损 失 。 设 经 典 半 次 迭

代 译 码 延 时 为 T, 则 滑 窗 译 码 方 法 的 半 次 迭 代 译 码 延 时

为 : ( T/2+T/ ( 2×N/W) ) , 因 而 其 时 序 控 制 很 复 杂 , 但 是

这 种 方 法 能 很 大 程 度 上 节 省 存 储 容 量 。

本 文 采 用 的 译 码 方 法 的 译 码 延 时 为 T/2 , 译 码 延 时

能 节 省 一 半 , 更 主 要 的 是 其 译 码 性 能 没 有 任 何 损 失 , 而

对 应 的 时 序 控 制 也 相 对 简 单 , 更 有 实 际 应 用 价 值 。

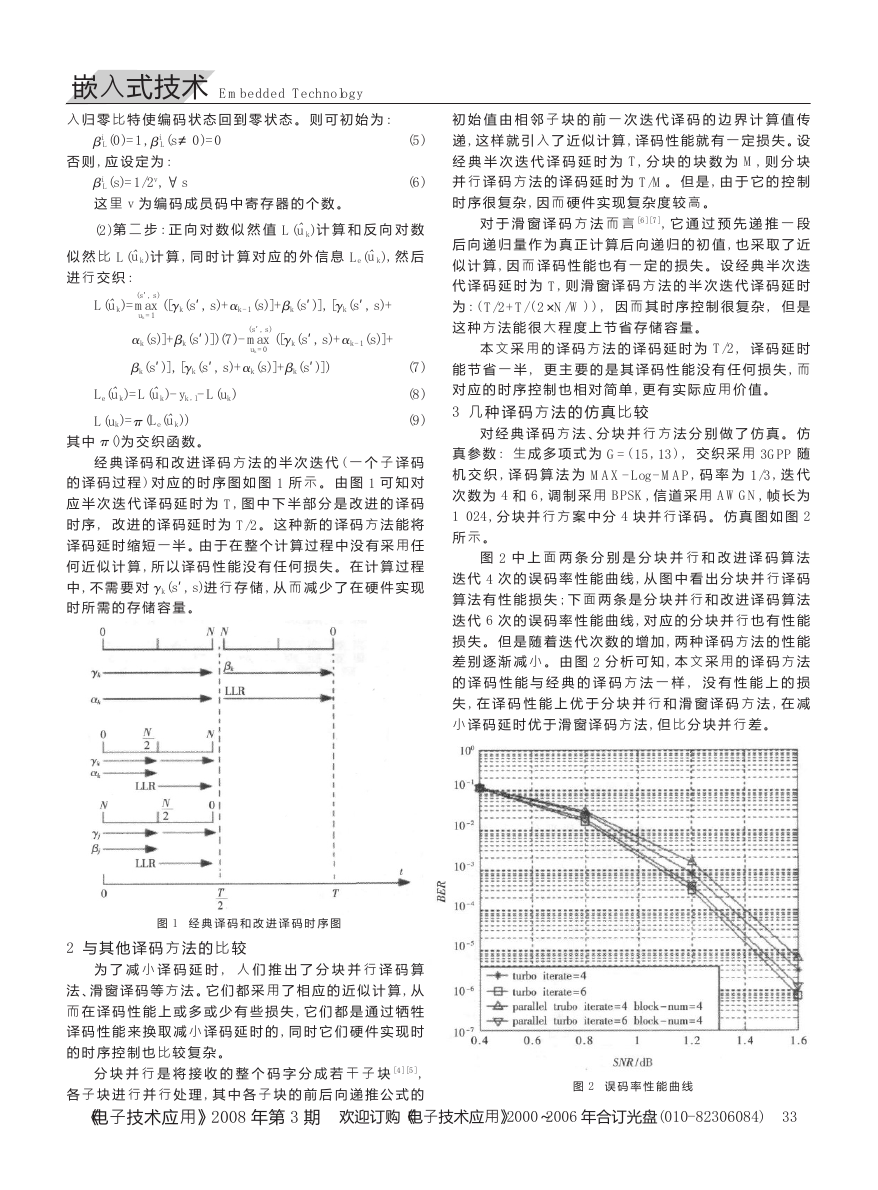

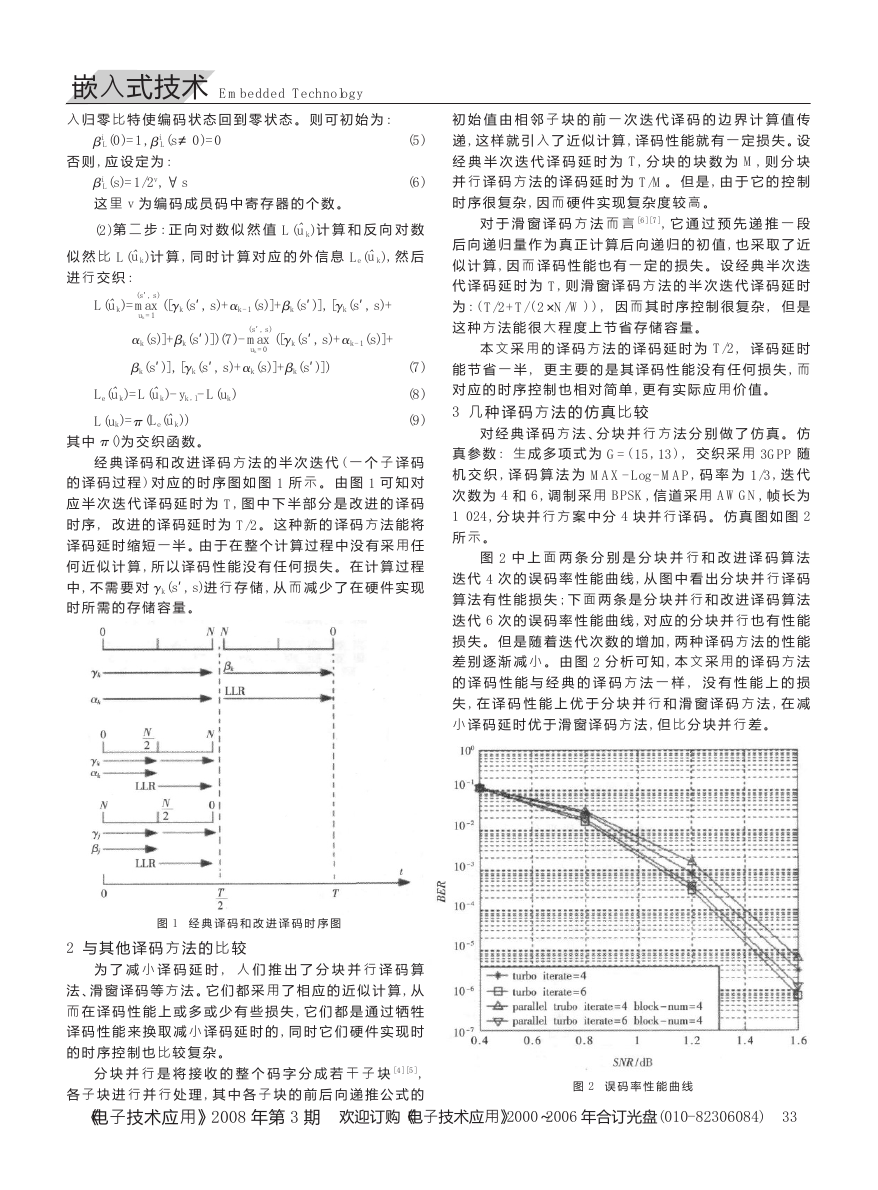

3 几 种 译 码 方 法 的 仿 真 比 较

对 经 典 译 码 方 法 、分 块 并 行 方 法 分 别 做 了 仿 真 。 仿

真 参 数 : 生 成 多 项 式 为 G= ( 15 , 13 ) , 交 织 采 用 3GPP 随

机 交 织 , 译 码 算 法 为 MAX- Log- MAP , 码 率 为 1/3 , 迭 代

次 数 为 4 和 6 , 调 制 采 用 BPSK, 信 道 采 用 AWGN, 帧 长 为

1 024 , 分 块 并 行 方 案 中 分 4 块 并 行 译 码 。 仿 真 图 如 图 2

所 示 。

图 2 中 上 面 两 条 分 别 是 分 块 并 行 和 改 进 译 码 算 法

迭 代 4 次 的 误 码 率 性 能 曲 线 , 从 图 中 看 出 分 块 并 行 译 码

算 法 有 性 能 损 失 ; 下 面 两 条 是 分 块 并 行 和 改 进 译 码 算 法

迭 代 6 次 的 误 码 率 性 能 曲 线 , 对 应 的 分 块 并 行 也 有 性 能

损 失 。 但 是 随 着 迭 代 次 数 的 增 加 , 两 种 译 码 方 法 的 性 能

差 别 逐 渐 减 小 。 由 图 2 分 析 可 知 , 本 文 采 用 的 译 码 方 法

的 译 码 性 能 与 经 典 的 译 码 方 法 一 样 , 没 有 性 能 上 的 损

失 , 在 译 码 性 能 上 优 于 分 块 并 行 和 滑 窗 译 码 方 法 , 在 减

小 译 码 延 时 优 于 滑 窗 译 码 方 法 , 但 比 分 块 并 行 差 。

100

10 - 1

10 - 2

10 - 3

10 - 4

10 - 5

10 - 6

10 - 7

0.4

turbo iterate=4

turbo iterate=6

parallel trubo iterate=4 block- num=4

parallel turbo iterate=6 block- num=4

0.6

0.8

1

1.2

1.4

1.6

SNR/ dB

图 2 误 码 率 性 能 曲 线

《电子技术应用》2008 年第 3 期 欢迎订购《电子技术应用》2000~2006 年合订光盘(010- 82306084)

33

�

嵌入式技术 Embedded Technology

4 硬 件 实 现 方 案

y

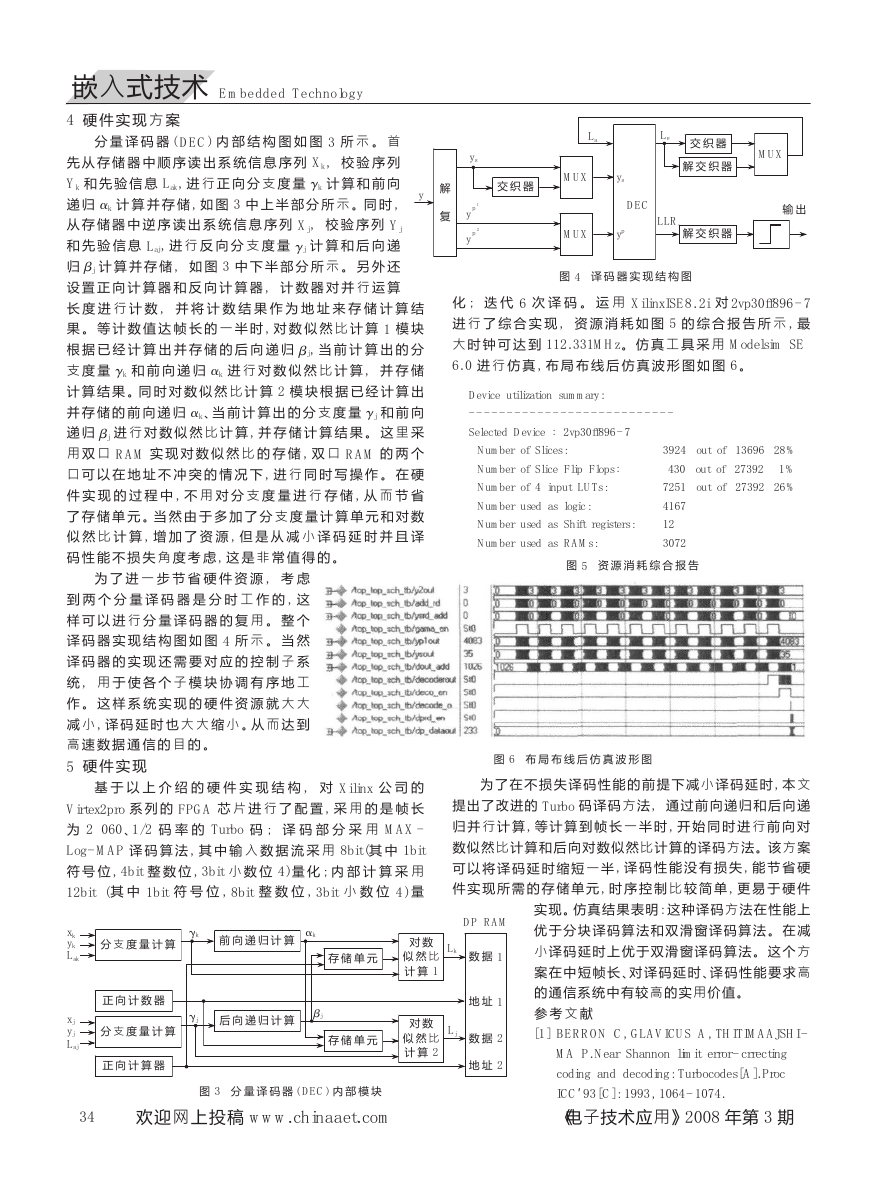

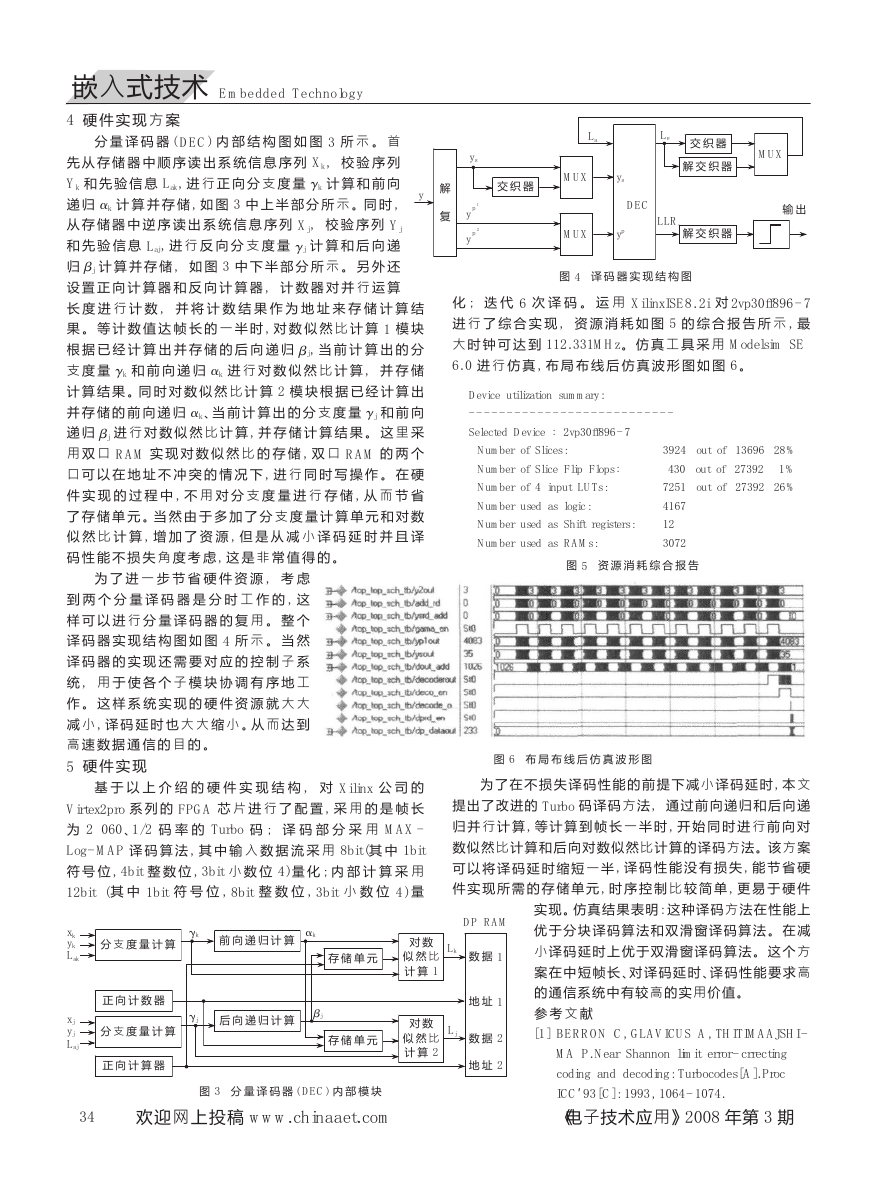

分 量 译 码 器 ( DEC) 内 部 结 构 图 如 图 3 所 示 。 首

先 从 存 储 器 中 顺 序 读 出 系 统 信 息 序 列 Xk, 校 验 序 列

Yk 和 先 验 信 息 Lak, 进 行 正 向 分 支 度 量 "k 计 算 和 前 向

递 归 #k 计 算 并 存 储 , 如 图 3 中 上 半 部 分 所 示 。同 时 ,

从 存 储 器 中 逆 序 读 出 系 统 信 息 序 列 Xj, 校 验 序 列 Yj

和 先 验 信 息 Laj, 进 行 反 向 分 支 度 量 "j 计 算 和 后 向 递

归 !j 计 算 并 存 储 , 如 图 3 中 下 半 部 分 所 示 。 另 外 还

设 置 正 向 计 算 器 和 反 向 计 算 器 , 计 数 器 对 并 行 运 算

长 度 进 行 计 数 , 并 将 计 数 结 果 作 为 地 址 来 存 储 计 算 结

果 。 等 计 数 值 达 帧 长 的 一 半 时 , 对 数 似 然 比 计 算 1 模 块

根 据 已 经 计 算 出 并 存 储 的 后 向 递 归 !j, 当 前 计 算 出 的 分

支 度 量 "k 和 前 向 递 归 #k 进 行 对 数 似 然 比 计 算 , 并 存 储

计 算 结 果 。同 时 对 数 似 然 比 计 算 2 模 块 根 据 已 经 计 算 出

并 存 储 的 前 向 递 归 #k、当 前 计 算 出 的 分 支 度 量 "j 和 前 向

递 归 !j 进 行 对 数 似 然 比 计 算 , 并 存 储 计 算 结 果 。 这 里 采

用 双 口 RAM 实 现 对 数 似 然 比 的 存 储 , 双 口 RAM 的 两 个

口 可 以 在 地 址 不 冲 突 的 情 况 下 , 进 行 同 时 写 操 作 。 在 硬

件 实 现 的 过 程 中 , 不 用 对 分 支 度 量 进 行 存 储 , 从 而 节 省

了 存 储 单 元 。当 然 由 于 多 加 了 分 支 度 量 计 算 单 元 和 对 数

似 然 比 计 算 , 增 加 了 资 源 , 但 是 从 减 小 译 码 延 时 并 且 译

码 性 能 不 损 失 角 度 考 虑 , 这 是 非 常 值 得 的 。

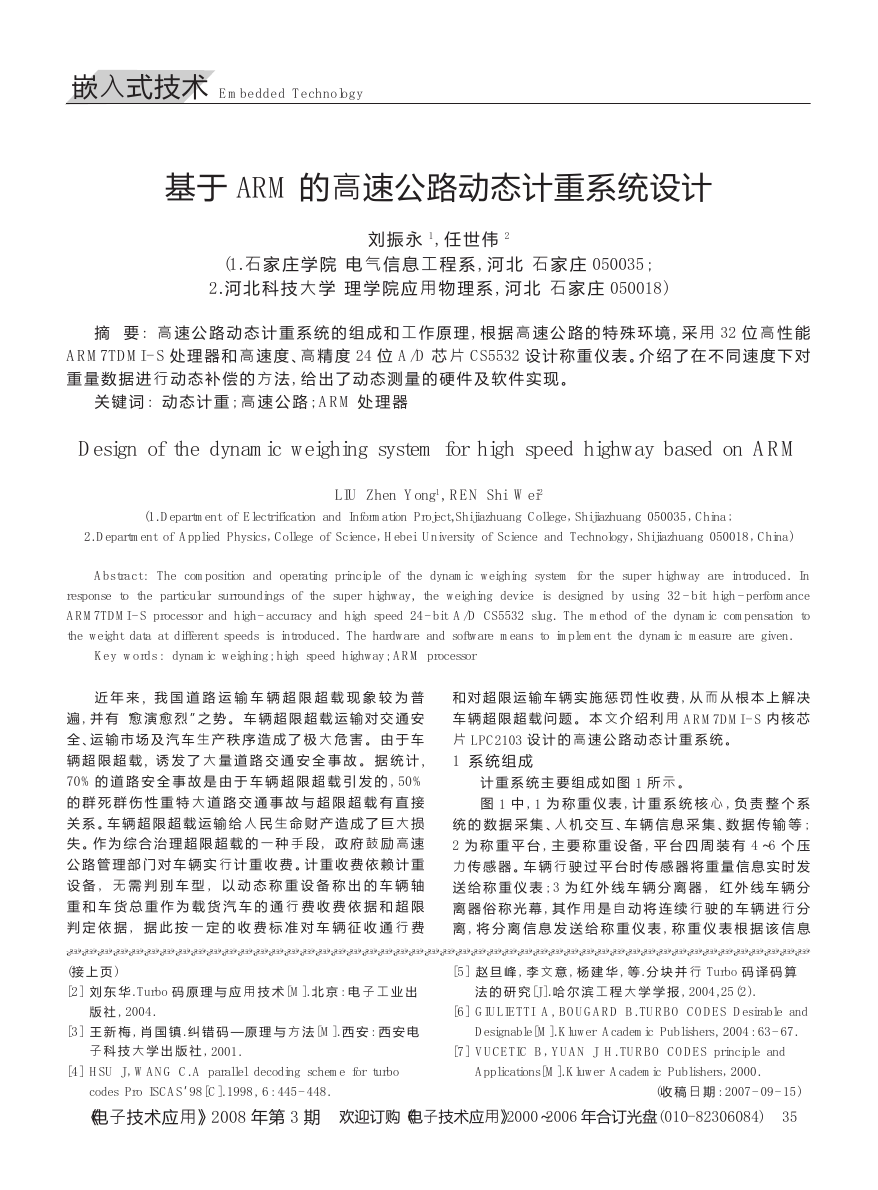

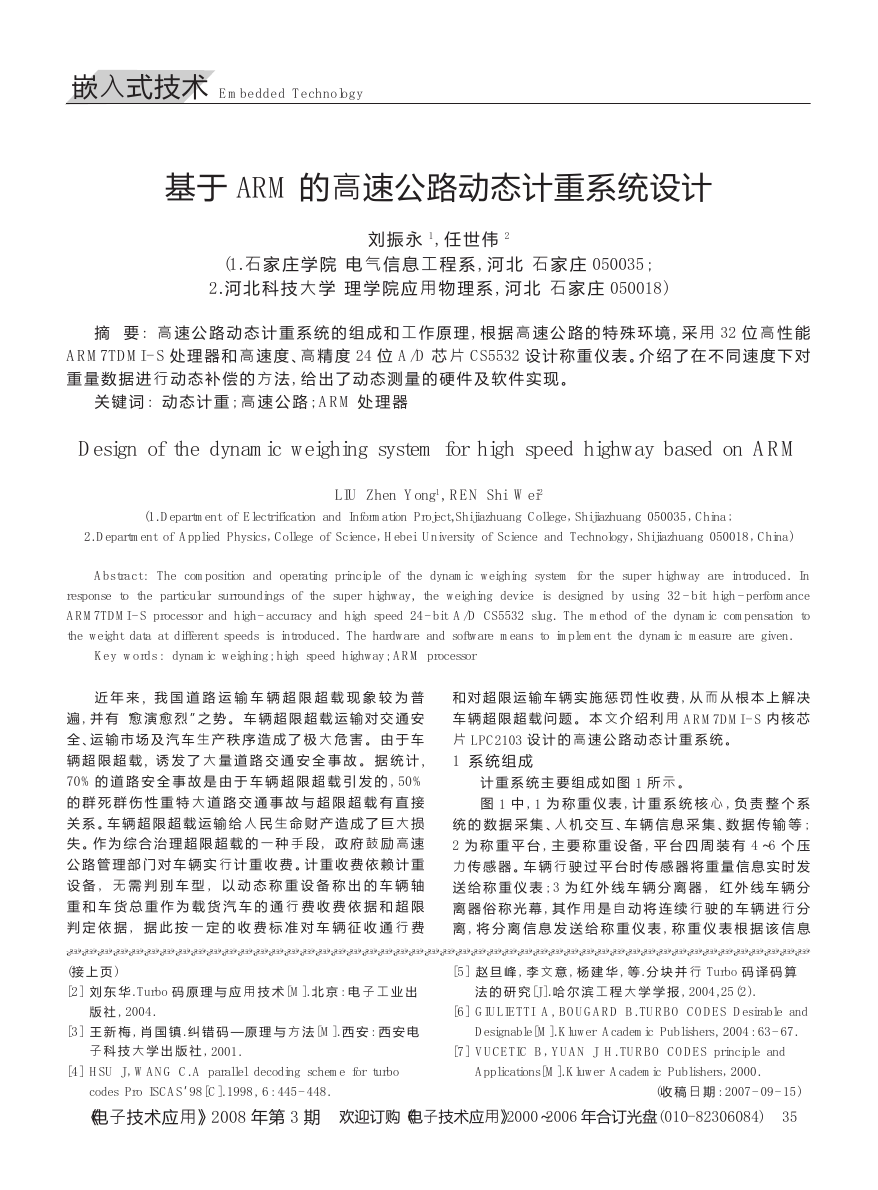

为 了 进 一 步 节 省 硬 件 资 源 , 考 虑

到 两 个 分 量 译 码 器 是 分 时 工 作 的 , 这

样 可 以 进 行 分 量 译 码 器 的 复 用 。 整 个

译 码 器 实 现 结 构 图 如 图 4 所 示 。 当 然

译 码 器 的 实 现 还 需 要 对 应 的 控 制 子 系

统 , 用 于 使 各 个 子 模 块 协 调 有 序 地 工

作 。 这 样 系 统 实 现 的 硬 件 资 源 就 大 大

减 小 , 译 码 延 时 也 大 大 缩 小 。从 而 达 到

高 速 数 据 通 信 的 目 的 。

5 硬 件 实 现

基 于 以 上 介 绍 的 硬 件 实 现 结 构 , 对 Xilinx 公 司 的

Virtex2pro 系 列 的 FPGA 芯 片 进 行 了 配 置 , 采 用 的 是 帧 长

为 2 060 、1/2 码 率 的 Turbo 码 ; 译 码 部 分 采 用 MAX -

Log- MAP 译 码 算 法 , 其 中 输 入 数 据 流 采 用 8bit(其 中 1bit

符 号 位 , 4bit 整 数 位 , 3bit 小 数 位 4)量 化 ; 内 部 计 算 采 用

12bit ( 其 中 1bit 符 号 位 , 8bit 整 数 位 , 3bit 小 数 位 4 ) 量

La

Le

交 织 器

MUX

ys

交 织 器

解 交 织 器

MUX

DEC

LLR

解 交 织 器

MUX

yp

输 出

ys

yp 1

yp 2

解

复

图 4 译 码 器 实 现 结 构 图

化 ; 迭 代 6 次 译 码 。 运 用 XilinxISE8 . 2i 对 2vp30ff896 - 7

进 行 了 综 合 实 现 , 资 源 消 耗 如 图 5 的 综 合 报 告 所 示 , 最

大 时 钟 可 达 到 112.331MHz。 仿 真 工 具 采 用 Modelsim SE

6.0 进 行 仿 真 , 布 局 布 线 后 仿 真 波 形 图 如 图 6 。

Device utilization summary:

- - - - - - - - - - - - - - - - - - - - - - - - - - -

Selected Device : 2vp30ff896- 7

Number of Slices :

Number of Slice Flip Flops :

Number of 4 input LUTs :

Number used as logic :

Number used as Shift registers :

Number used as RAMs :

3924 out of 13696 28%

430 out of 27392

1%

7251 out of 27392 26%

4167

12

3072

图 5 资 源 消 耗 综 合 报 告

图 6 布 局 布 线 后 仿 真 波 形 图

为 了 在 不 损 失 译 码 性 能 的 前 提 下 减 小 译 码 延 时 , 本 文

提 出 了 改 进 的 Turbo 码 译 码 方 法 , 通 过 前 向 递 归 和 后 向 递

归 并 行 计 算 , 等 计 算 到 帧 长 一 半 时 , 开 始 同 时 进 行 前 向 对

数 似 然 比 计 算 和 后 向 对 数 似 然 比 计 算 的 译 码 方 法 。该 方 案

可 以 将 译 码 延 时 缩 短 一 半 , 译 码 性 能 没 有 损 失 , 能 节 省 硬

件 实 现 所 需 的 存 储 单 元 , 时 序 控 制 比 较 简 单 , 更 易 于 硬 件

实 现 。仿 真 结 果 表 明: 这 种 译 码 方 法 在 性 能 上

DP RAM

xkyk

Lak

xjyj

Laj

分 支 度 量 计 算

!k

前 向 递 归 计 算 "k

正 向 计 数 器

分 支 度 量 计 算

正 向 计 算 器

!j

后 向 递 归 计 算

!j

存 储 单 元

存 储 单 元

Lk

对 数

似 然 比

计 算 1

Lj

对 数

似 然 比

计 算 2

数 据 1

地 址 1

数 据 2

地 址 2

图 3 分 量 译 码 器 ( DEC) 内 部 模 块

欢迎网上投稿 www.chinaaet.com

34

优 于 分 块 译 码 算 法 和 双 滑 窗 译 码 算 法 。 在 减

小 译 码 延 时 上 优 于 双 滑 窗 译 码 算 法 。 这 个 方

案 在 中 短 帧 长 、对 译 码 延 时 、译 码 性 能 要 求 高

的 通 信 系 统 中 有 较 高 的 实 用 价 值 。

参 考 文 献

[1] BERRON C, GLAVICUS A, THITIMAAJSHI-

MA P.Near Shannon limit error- crrecting

coding and decoding: Turbocodes[A].Proc

ICC′93[C]: 1993 , 1064- 1074.

《电子技术应用》2008 年第 3 期

�

嵌入式技术 Embedded Technology

基于 ARM 的高速公路动态计重系统设计

刘 振 永 1, 任 世 伟 2

(1.石 家 庄 学 院 电 气 信 息 工 程 系 , 河 北 石 家 庄 050035;

2.河 北 科 技 大 学 理 学 院 应 用 物 理 系 , 河 北 石 家 庄 050018)

摘 要 : 高 速 公 路 动 态 计 重 系 统 的 组 成 和 工 作 原 理 , 根 据 高 速 公 路 的 特 殊 环 境 , 采 用 32 位 高 性 能

ARM7TDMI- S 处 理 器 和 高 速 度 、高 精 度 24 位 A/D 芯 片 CS5532 设 计 称 重 仪 表 。介 绍 了 在 不 同 速 度 下 对

重 量 数 据 进 行 动 态 补 偿 的 方 法 , 给 出 了 动 态 测 量 的 硬 件 及 软 件 实 现 。

关 键 词 : 动 态 计 重 ; 高 速 公 路 ; ARM 处 理 器

Design of the dynamic weighing system for high speed highway based on ARM

(1.Department of Electrification and Information Project,Shijiazhuang College , Shijiazhuang 050035 , China ;

2.Department of Applied Physics , College of Science , Hebei University of Science and Technology, Shijiazhuang 050018 , China)

LIU Zhen Yong1, REN Shi Wei2

Abs tract : The composition and operating principle of the dynamic weighing system for the super highway are introduced. In

the weighing device is designed by using 32 - bit high - performance

response to the particular surroundings of the super highway,

ARM7TDMI- S processor and high- accuracy and high speed 24- bit A/D CS5532 slug. The method of the dynamic compensation to

the weight data at different speeds is introduced. The hardware and software means to implement the dynamic measure are given.

Key words : dynamic weighing; high speed highway; ARM processor

近 年 来 , 我 国 道 路 运 输 车 辆 超 限 超 载 现 象 较 为 普

遍 , 并 有 “愈 演 愈 烈 ”之 势 。 车 辆 超 限 超 载 运 输 对 交 通 安

全 、运 输 市 场 及 汽 车 生 产 秩 序 造 成 了 极 大 危 害 。 由 于 车

辆 超 限 超 载 , 诱 发 了 大 量 道 路 交 通 安 全 事 故 。 据 统 计 ,

70% 的 道 路 安 全 事 故 是 由 于 车 辆 超 限 超 载 引 发 的 , 50%

的 群 死 群 伤 性 重 特 大 道 路 交 通 事 故 与 超 限 超 载 有 直 接

关 系 。车 辆 超 限 超 载 运 输 给 人 民 生 命 财 产 造 成 了 巨 大 损

失 。作 为 综 合 治 理 超 限 超 载 的 一 种 手 段 , 政 府 鼓 励 高 速

公 路 管 理 部 门 对 车 辆 实 行 计 重 收 费 。计 重 收 费 依 赖 计 重

设 备 , 无 需 判 别 车 型 , 以 动 态 称 重 设 备 称 出 的 车 辆 轴

重 和 车 货 总 重 作 为 载 货 汽 车 的 通 行 费 收 费 依 据 和 超 限

判 定 依 据 , 据 此 按 一 定 的 收 费 标 准 对 车 辆 征 收 通 行 费

和 对 超 限 运 输 车 辆 实 施 惩 罚 性 收 费 , 从 而 从 根 本 上 解 决

车 辆 超 限 超 载 问 题 。 本 文 介 绍 利 用 ARM7DMI- S 内 核 芯

片 LPC2103 设 计 的 高 速 公 路 动 态 计 重 系 统 。

1 系 统 组 成

计 重 系 统 主 要 组 成 如 图 1 所 示 。

图 1 中 , 1 为 称 重 仪 表 , 计 重 系 统 核 心 , 负 责 整 个 系

统 的 数 据 采 集 、人 机 交 互 、车 辆 信 息 采 集 、数 据 传 输 等 ;

2 为 称 重 平 台 , 主 要 称 重 设 备 , 平 台 四 周 装 有 4 ~6 个 压

力 传 感 器 。车 辆 行 驶 过 平 台 时 传 感 器 将 重 量 信 息 实 时 发

送 给 称 重 仪 表 ; 3 为 红 外 线 车 辆 分 离 器 , 红 外 线 车 辆 分

离 器 俗 称 光 幕 , 其 作 用 是 自 动 将 连 续 行 驶 的 车 辆 进 行 分

离 , 将 分 离 信 息 发 送 给 称 重 仪 表 , 称 重 仪 表 根 据 该 信 息

!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

(接 上 页 )

[2] 刘 东 华 .Turbo 码 原 理 与 应 用 技 术 [M]. 北 京 : 电 子 工 业 出

[5] 赵 旦 峰 , 李 文 意 , 杨 建 华 , 等 . 分 块 并 行 Turbo 码 译 码 算

法 的 研 究 [J]. 哈 尔 滨 工 程 大 学 学 报 , 2004,25(2).

版 社 , 2004.

[6] GIULIETTI A, BOUGARD B.TURBO CODES Desirable and

[3] 王 新 梅 , 肖 国 镇 . 纠 错 码 — 原 理 与 方 法 [M]. 西 安 : 西 安 电

Designable[M].Kluwer Academic Publishers , 2004 : 63- 67.

子 科 技 大 学 出 版 社 , 2001.

[7] VUCETIC B, YUAN J H.TURBO CODES principle and

[4] HSU J , WANG C.A parallel decoding scheme for turbo

Applications[M].Kluwer Academic Publishers , 2000.

codes Pro ISCAS′98[C].1998 , 6 : 445- 448.

《电子技术应用》2008 年第 3 期 欢迎订购《电子技术应用》2000~2006 年合订光盘(010- 82306084)

(收 稿 日 期 : 2007- 09- 15)

35

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc