小梅哥 FPGA 团队 武汉芯路恒科技

专注于培养您的 FPGA 独立开发能力 开发板 培训 项目研发三位一体

说 明

1、本内容节选自《FPGA 自学笔记——设计与验证》一书 6.4 节,内容仅供学习

使用,不得用于任何其他商业目的。如果您喜欢,建议购买正版纸质书。

2、本节内容由小梅哥于 2019 年 4 月 30 日修订,增加了系统测试部分的细节内

容。

3、如果有更新,我们将会发布在我们的官方论坛 www.corecourse.cn,如需关注

本节内容的更新,可至我们的官方网站以本文档标题为关键词进行检索,以查找

相关内容。

4、本教程对应的 FPGA 工程源码名为“29_DDS2”,位于“【书本源码】FPGA 自

学笔记——设计与验证.rar”压缩包的“chapter6”中。

本节导读

本节将结合第三章中串口收发小节实现的串口收发模块、第四章中 ROM 使用

小节讲解的 ROM 使用知识以及第 5 章中的 DAC 驱动小节实现的 DAC 驱动模块实

现一个双通道幅度、频率、相位均可调的 DDS 信号发生器。

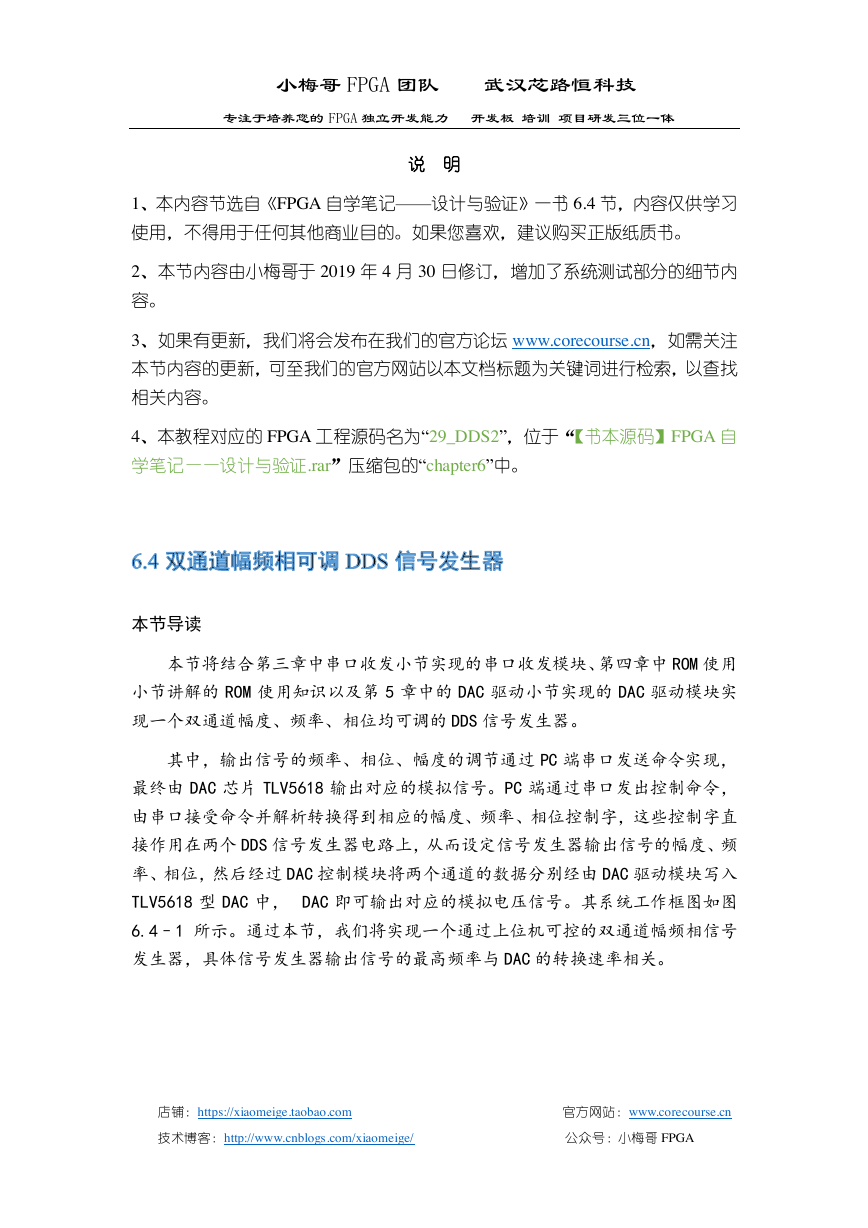

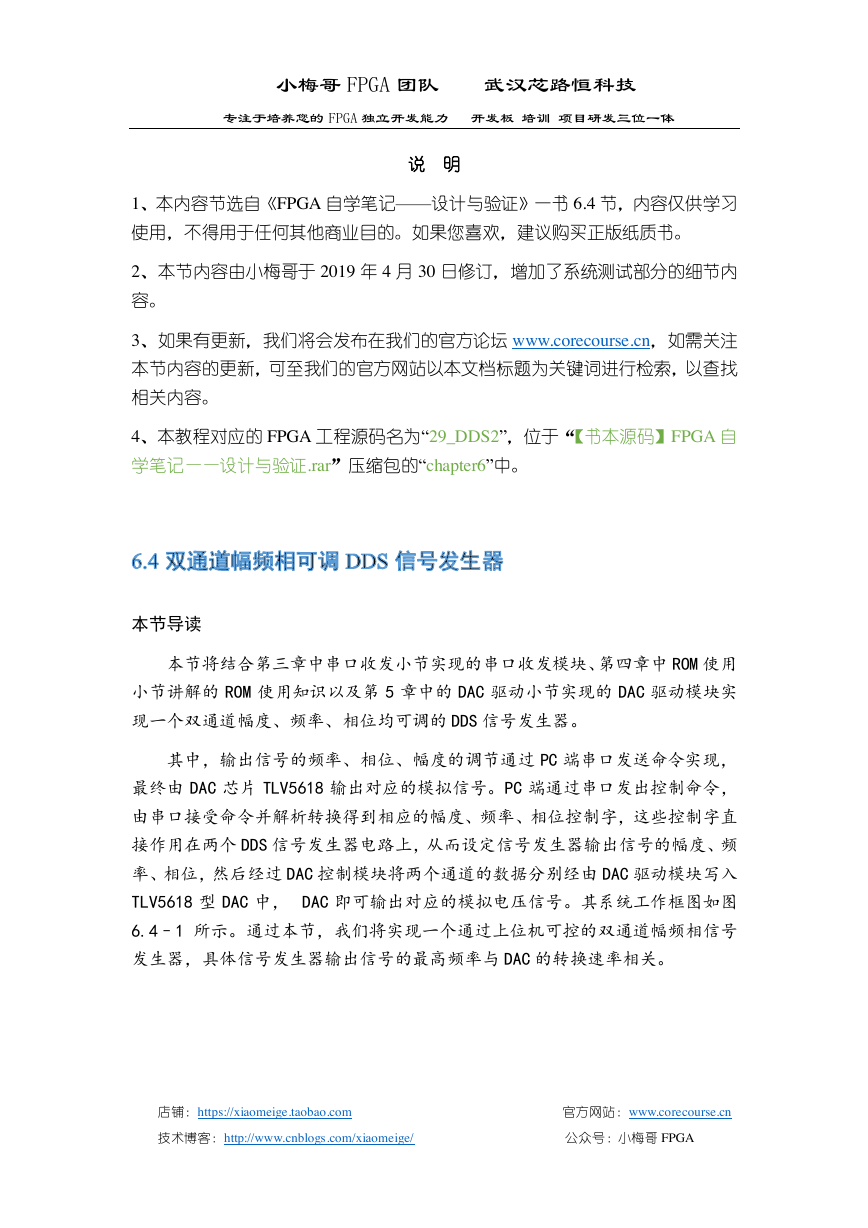

其中,输出信号的频率、相位、幅度的调节通过 PC 端串口发送命令实现,

最终由 DAC 芯片 TLV5618 输出对应的模拟信号。PC 端通过串口发出控制命令,

由串口接受命令并解析转换得到相应的幅度、频率、相位控制字,这些控制字直

接作用在两个 DDS 信号发生器电路上,从而设定信号发生器输出信号的幅度、频

率、相位,然后经过 DAC 控制模块将两个通道的数据分别经由 DAC 驱动模块写入

TLV5618 型 DAC 中, DAC 即可输出对应的模拟电压信号。其系统工作框图如图

6.4–1 所示。通过本节,我们将实现一个通过上位机可控的双通道幅频相信号

发生器,具体信号发生器输出信号的最高频率与 DAC 的转换速率相关。

店铺:https://xiaomeige.taobao.com 官方网站:www.corecourse.cn

技术博客:http://www.cnblogs.com/xiaomeige/ 公众号:小梅哥 FPGA

�

小梅哥 FPGA 团队 武汉芯路恒科技

专注于培养您的 FPGA 独立开发能力 开发板 培训 项目研发三位一体

图 6.4–1 基于 AC620 开发板的双通道 DDS 系统架构图

由工作原理图可以暂时将本系统划分为串口接收模块、命令解析模块、DDS

信号生成模块、DAC 控制模块和 DAC 驱动模块。

DDS 原理与实现

6.4.1.1 DDS 基本原理

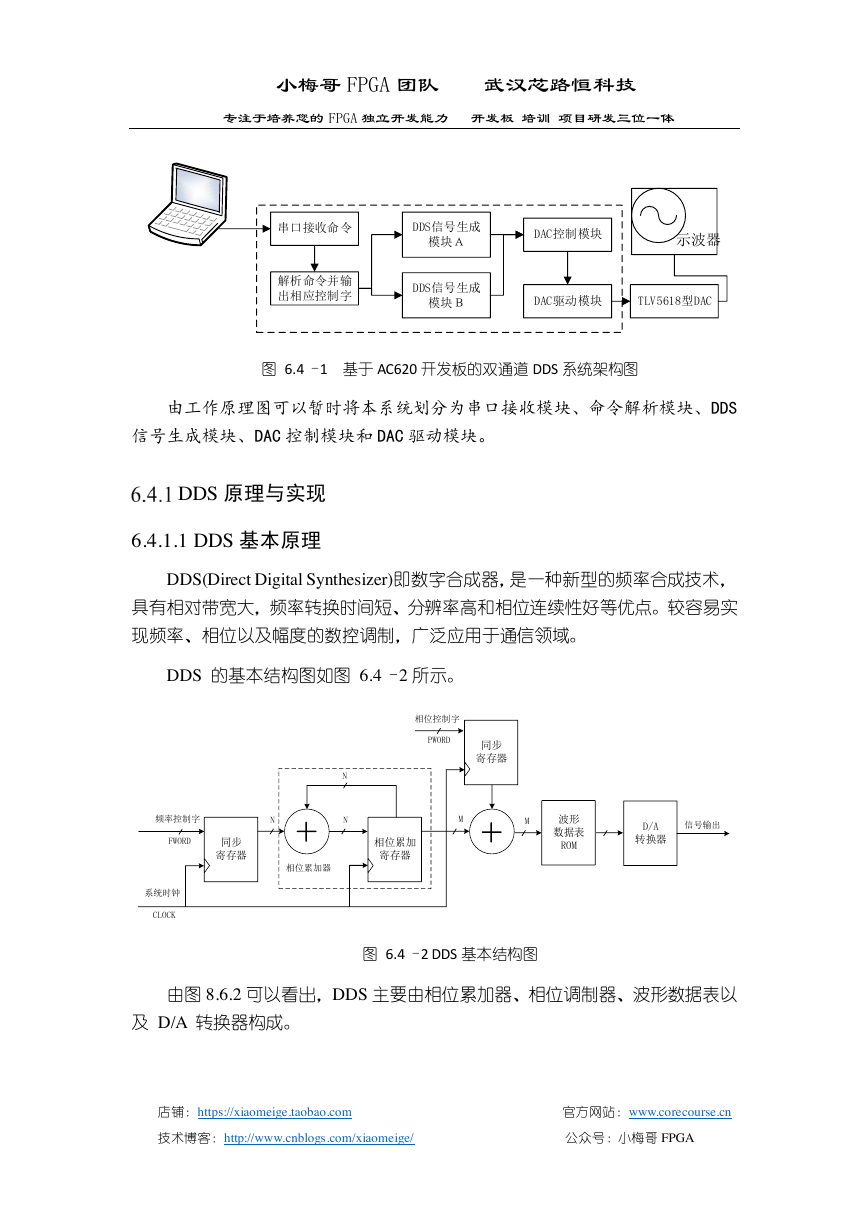

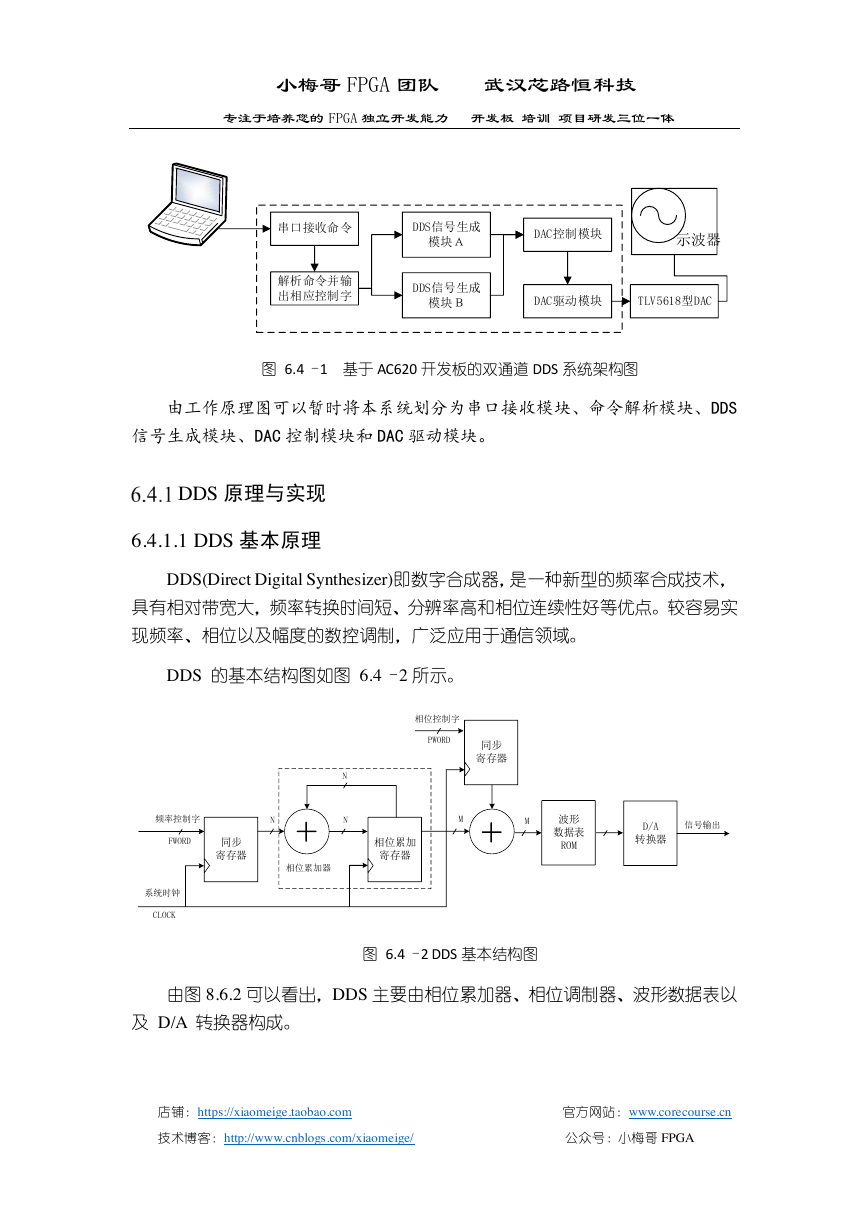

DDS(Direct Digital Synthesizer)即数字合成器,是一种新型的频率合成技术,

具有相对带宽大,频率转换时间短、分辨率高和相位连续性好等优点。较容易实

现频率、相位以及幅度的数控调制,广泛应用于通信领域。

DDS 的基本结构图如图 6.4–2 所示。

图 6.4–2 DDS 基本结构图

由图 8.6.2 可以看出,DDS 主要由相位累加器、相位调制器、波形数据表以

及 D/A 转换器构成。

店铺:https://xiaomeige.taobao.com 官方网站:www.corecourse.cn

技术博客:http://www.cnblogs.com/xiaomeige/ 公众号:小梅哥 FPGA

串口接收命令解析命令并输出相应控制字DDS信号生成模块BDDS信号生成模块ADAC控制模块DAC驱动模块TLV5618型DAC示波器同步寄存器相位累加寄存器同步寄存器波形数据表ROMD/A转换器频率控制字FWORD相位累加器相位控制字PWORDNNNMM信号输出系统时钟CLOCK�

小梅哥 FPGA 团队 武汉芯路恒科技

专注于培养您的 FPGA 独立开发能力 开发板 培训 项目研发三位一体

其中相位累加器由 N 位加法器与 N 位寄存器构成。每个时钟周期的时钟上

升沿,加法器就将频率控制字与累加寄存器输出的相位数据相加,相加的结果又

反馈至累加寄存器的数据输入端,以使加法器在下一个时钟脉冲的作用下继续与

频率控制字相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性

相位累加。即在每一个时钟脉冲输入时,相位累加器便把频率控制字累加一次。

相位累加器输出的数据就是合成信号的相位。相位累加器的溢出频率,就是

DDS 输出的信号频率图 2.30 相位累加器输出的数据,作为波形存储器的相位采

样地址,这样就可以把存储在波形存储器里的波形采样值经查表找出,完成相位

到幅度的转换。波形存储器的输出数据送到 D/A 转换器,由 D/A 转换器将数

字信号转换成模拟信号输出。

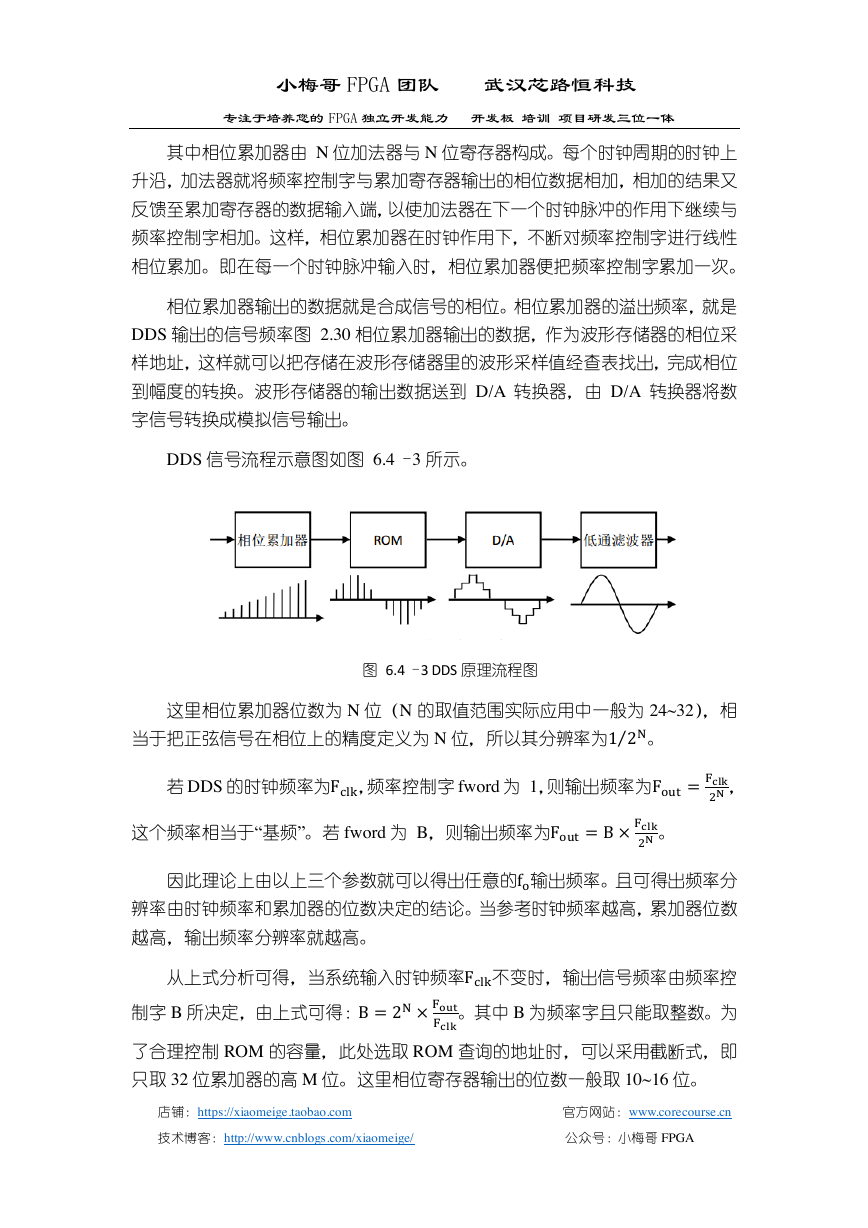

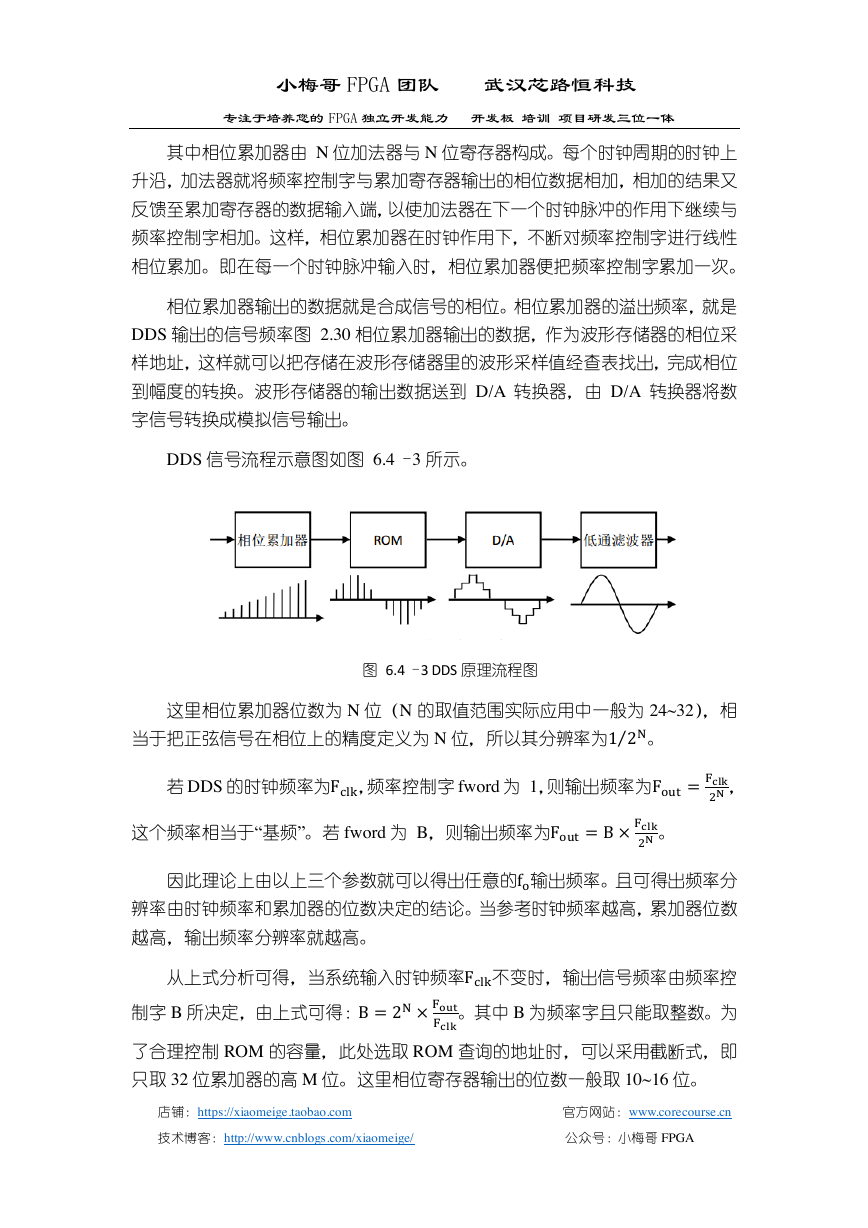

DDS 信号流程示意图如图 6.4–3 所示。

图 6.4–3 DDS 原理流程图

这里相位累加器位数为 N 位(N 的取值范围实际应用中一般为 24~32),相

当于把正弦信号在相位上的精度定义为 N 位,所以其分辨率为1 2N⁄ 。

若 DDS 的时钟频率为Fclk,频率控制字 fword 为 1,则输出频率为Fout =

Fclk

2N ,

这个频率相当于“基频”。若 fword 为 B,则输出频率为Fout = B ×

Fclk

2N 。

因此理论上由以上三个参数就可以得出任意的fo输出频率。且可得出频率分

辨率由时钟频率和累加器的位数决定的结论。当参考时钟频率越高,累加器位数

越高,输出频率分辨率就越高。

从上式分析可得,当系统输入时钟频率Fclk不变时,输出信号频率由频率控

制字 B 所决定,由上式可得:B = 2N ×

Fout

Fclk

。其中 B 为频率字且只能取整数。为

了合理控制 ROM 的容量,此处选取 ROM 查询的地址时,可以采用截断式,即

只取 32 位累加器的高 M 位。这里相位寄存器输出的位数一般取 10~16 位。

店铺:https://xiaomeige.taobao.com 官方网站:www.corecourse.cn

技术博客:http://www.cnblogs.com/xiaomeige/ 公众号:小梅哥 FPGA

�

小梅哥 FPGA 团队 武汉芯路恒科技

专注于培养您的 FPGA 独立开发能力 开发板 培训 项目研发三位一体

以上通过理论计算加数据变换的形式对 DDS 原理进行了较为严谨的解释,

但是 DDS 究竟是怎么实现频率和相位的控制的呢,以下通过一个简化的实例来

描述 DDS 实现频率和相位控制的过程。

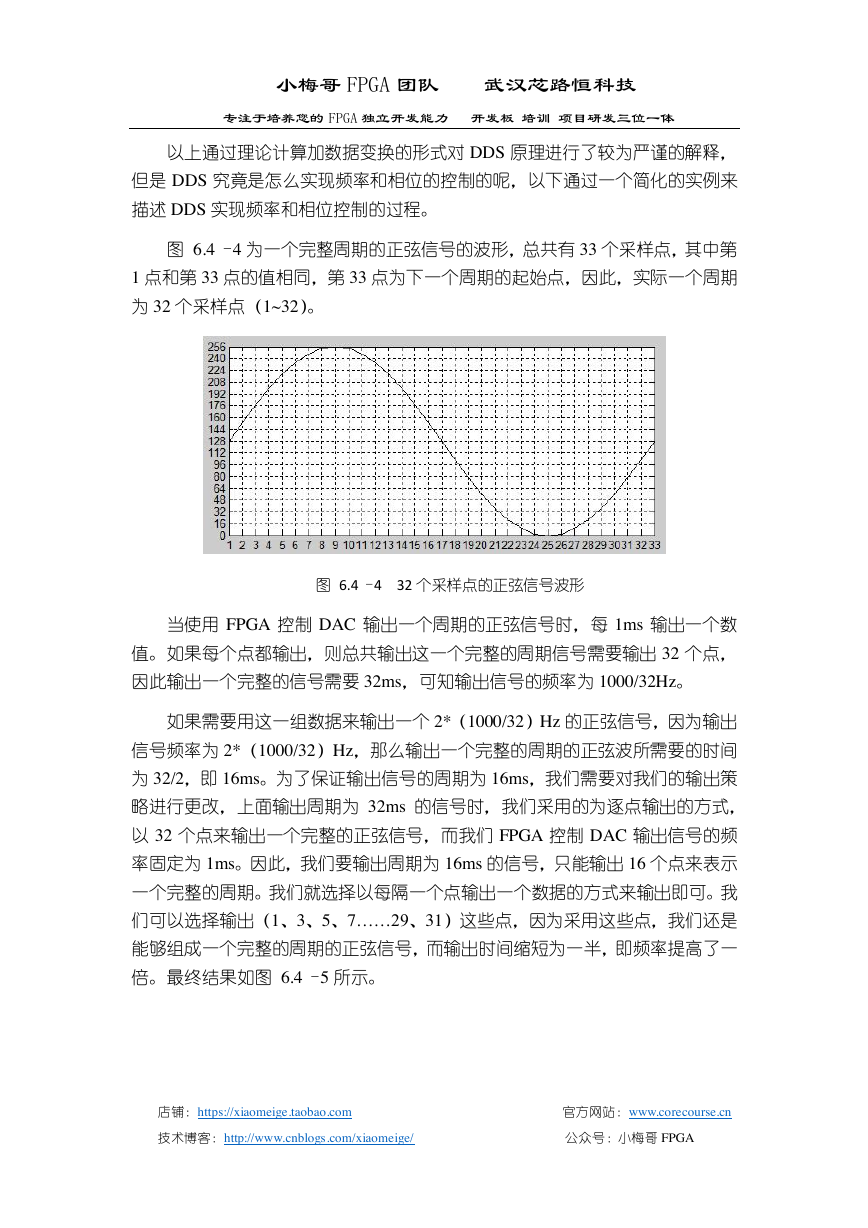

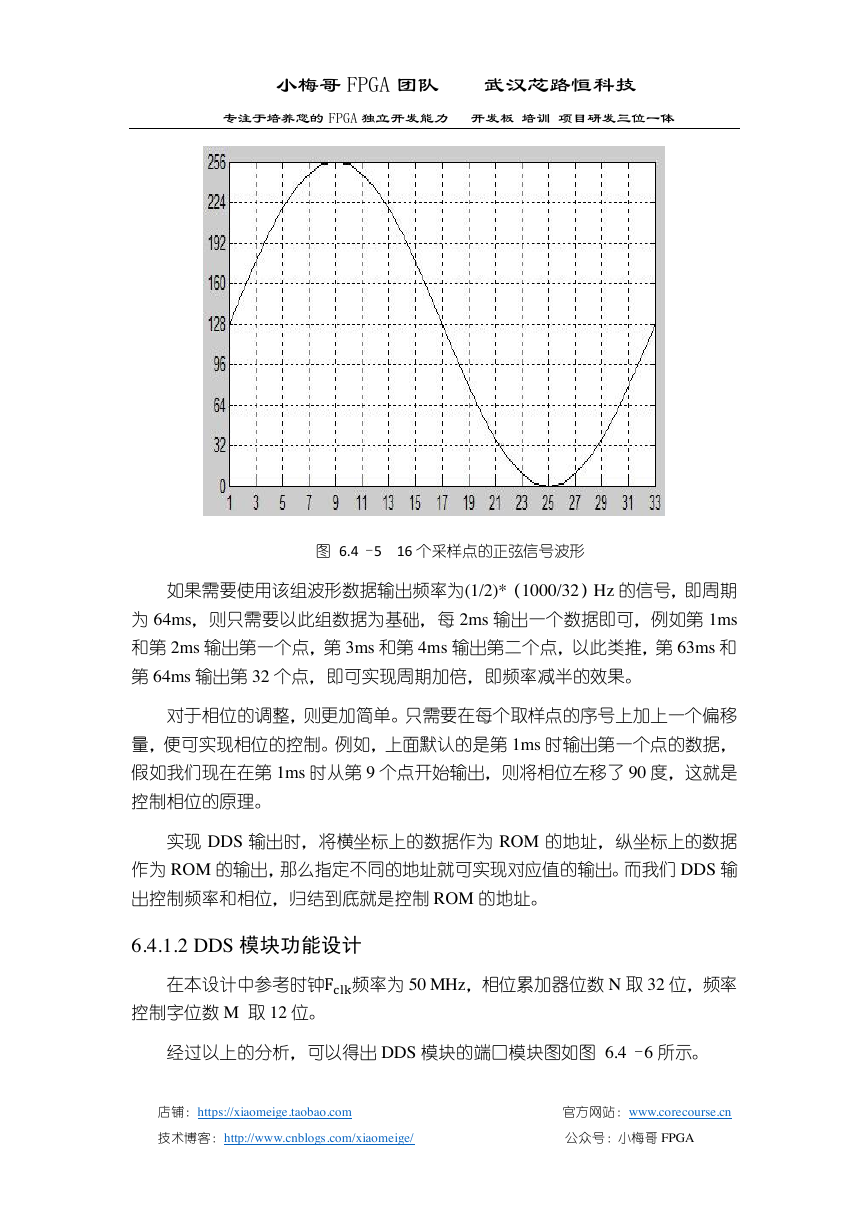

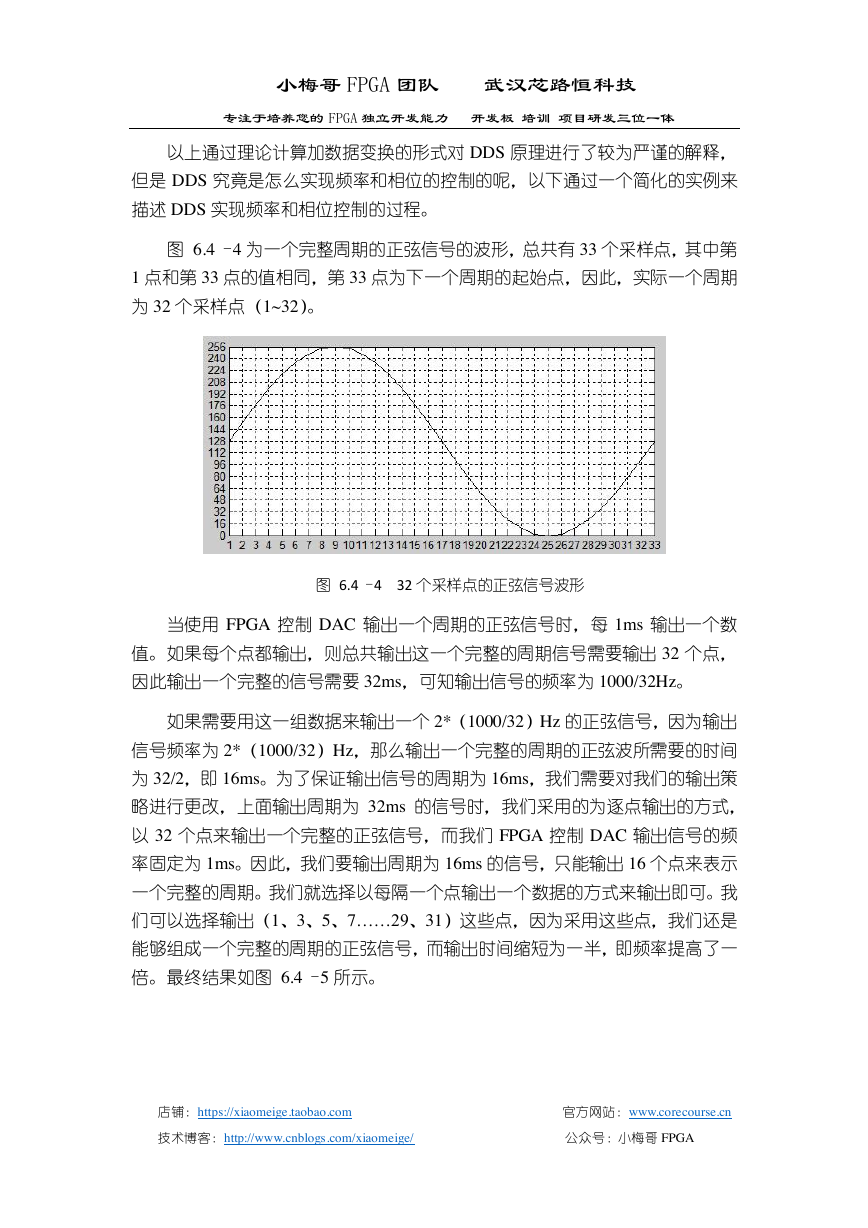

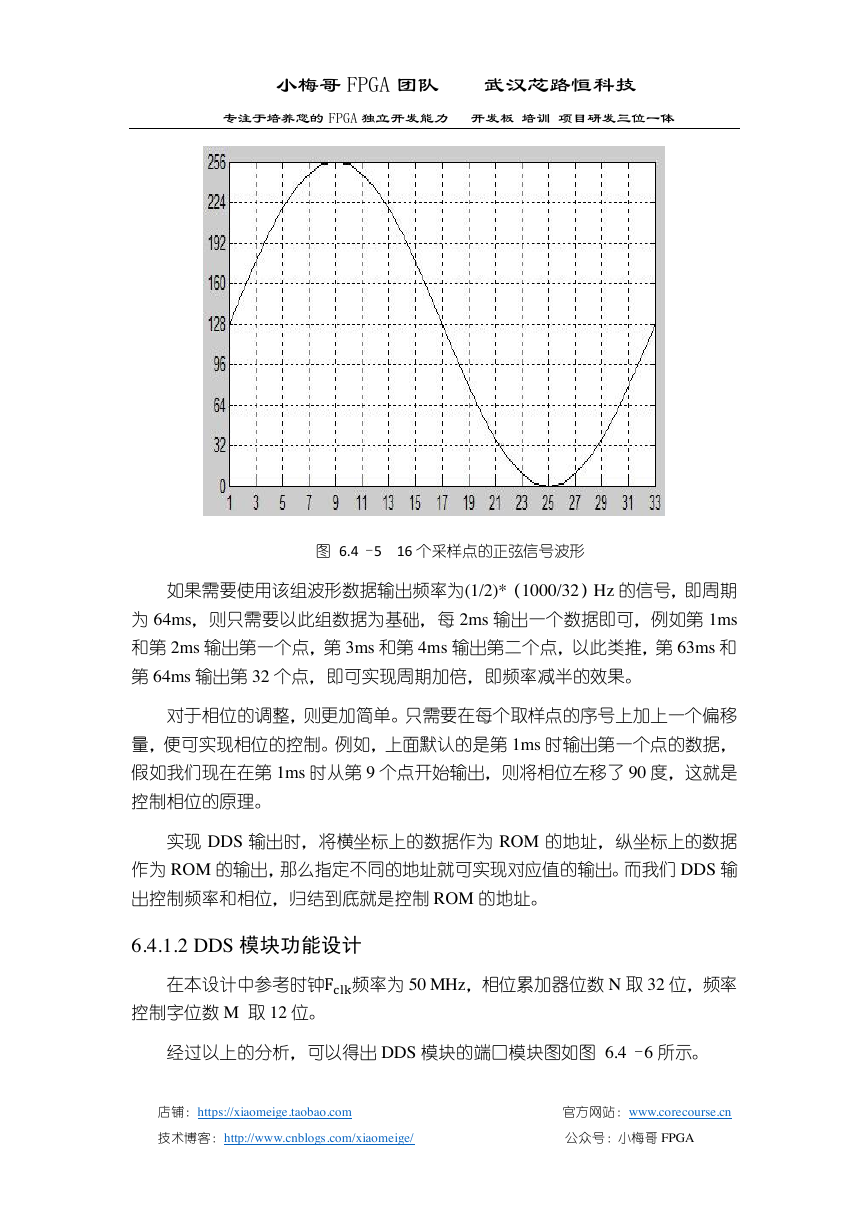

图 6.4–4 为一个完整周期的正弦信号的波形,总共有 33 个采样点,其中第

1 点和第 33 点的值相同,第 33 点为下一个周期的起始点,因此,实际一个周期

为 32 个采样点(1~32)。

图 6.4–4 32 个采样点的正弦信号波形

当使用 FPGA 控制 DAC 输出一个周期的正弦信号时,每 1ms 输出一个数

值。如果每个点都输出,则总共输出这一个完整的周期信号需要输出 32 个点,

因此输出一个完整的信号需要 32ms,可知输出信号的频率为 1000/32Hz。

如果需要用这一组数据来输出一个 2*(1000/32)Hz 的正弦信号,因为输出

信号频率为 2*(1000/32)Hz,那么输出一个完整的周期的正弦波所需要的时间

为 32/2,即 16ms。为了保证输出信号的周期为 16ms,我们需要对我们的输出策

略进行更改,上面输出周期为 32ms 的信号时,我们采用的为逐点输出的方式,

以 32 个点来输出一个完整的正弦信号,而我们 FPGA 控制 DAC 输出信号的频

率固定为 1ms。因此,我们要输出周期为 16ms 的信号,只能输出 16 个点来表示

一个完整的周期。我们就选择以每隔一个点输出一个数据的方式来输出即可。我

们可以选择输出(1、3、5、7……29、31)这些点,因为采用这些点,我们还是

能够组成一个完整的周期的正弦信号,而输出时间缩短为一半,即频率提高了一

倍。最终结果如图 6.4–5 所示。

店铺:https://xiaomeige.taobao.com 官方网站:www.corecourse.cn

技术博客:http://www.cnblogs.com/xiaomeige/ 公众号:小梅哥 FPGA

�

小梅哥 FPGA 团队 武汉芯路恒科技

专注于培养您的 FPGA 独立开发能力 开发板 培训 项目研发三位一体

图 6.4–5 16 个采样点的正弦信号波形

如果需要使用该组波形数据输出频率为(1/2)*(1000/32)Hz 的信号,即周期

为 64ms,则只需要以此组数据为基础,每 2ms 输出一个数据即可,例如第 1ms

和第 2ms 输出第一个点,第 3ms 和第 4ms 输出第二个点,以此类推,第 63ms 和

第 64ms 输出第 32 个点,即可实现周期加倍,即频率减半的效果。

对于相位的调整,则更加简单。只需要在每个取样点的序号上加上一个偏移

量,便可实现相位的控制。例如,上面默认的是第 1ms 时输出第一个点的数据,

假如我们现在在第 1ms 时从第 9 个点开始输出,则将相位左移了 90 度,这就是

控制相位的原理。

实现 DDS 输出时,将横坐标上的数据作为 ROM 的地址,纵坐标上的数据

作为 ROM 的输出,那么指定不同的地址就可实现对应值的输出。而我们 DDS 输

出控制频率和相位,归结到底就是控制 ROM 的地址。

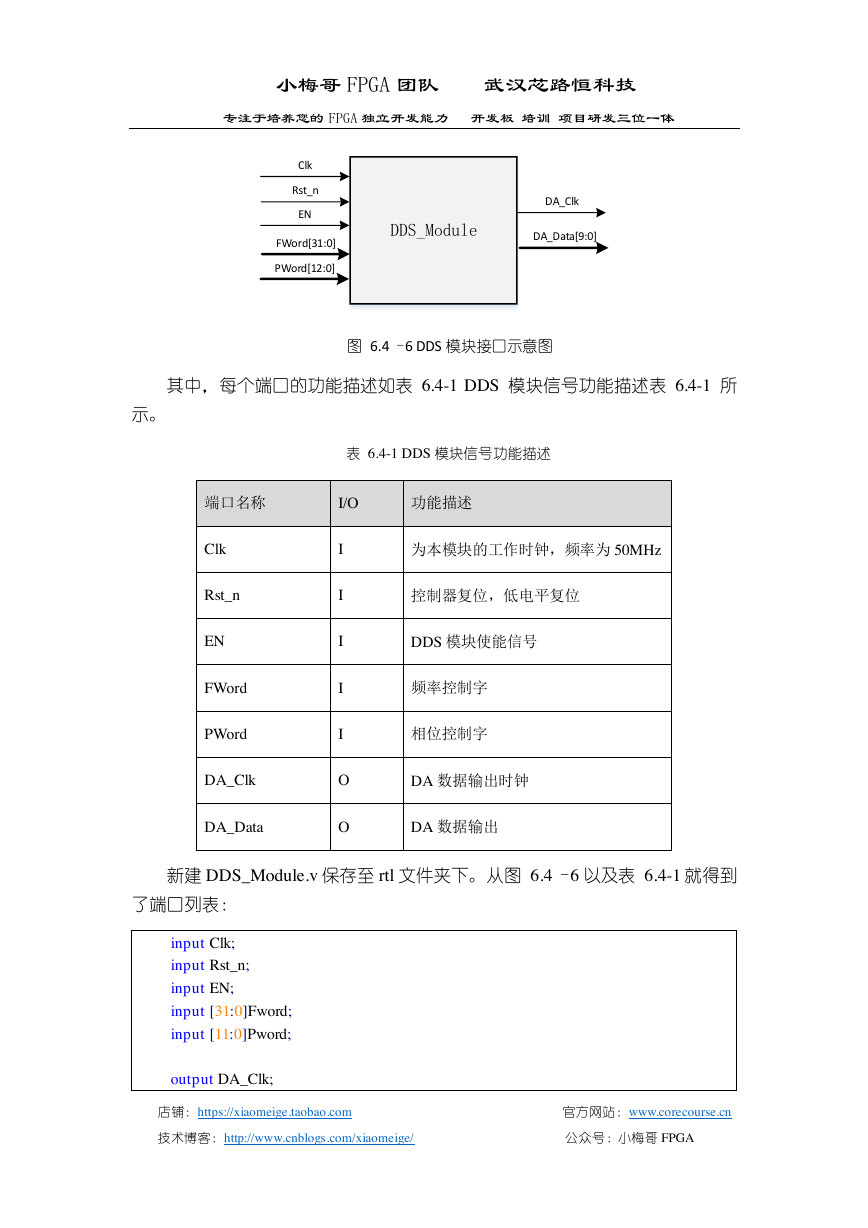

6.4.1.2 DDS 模块功能设计

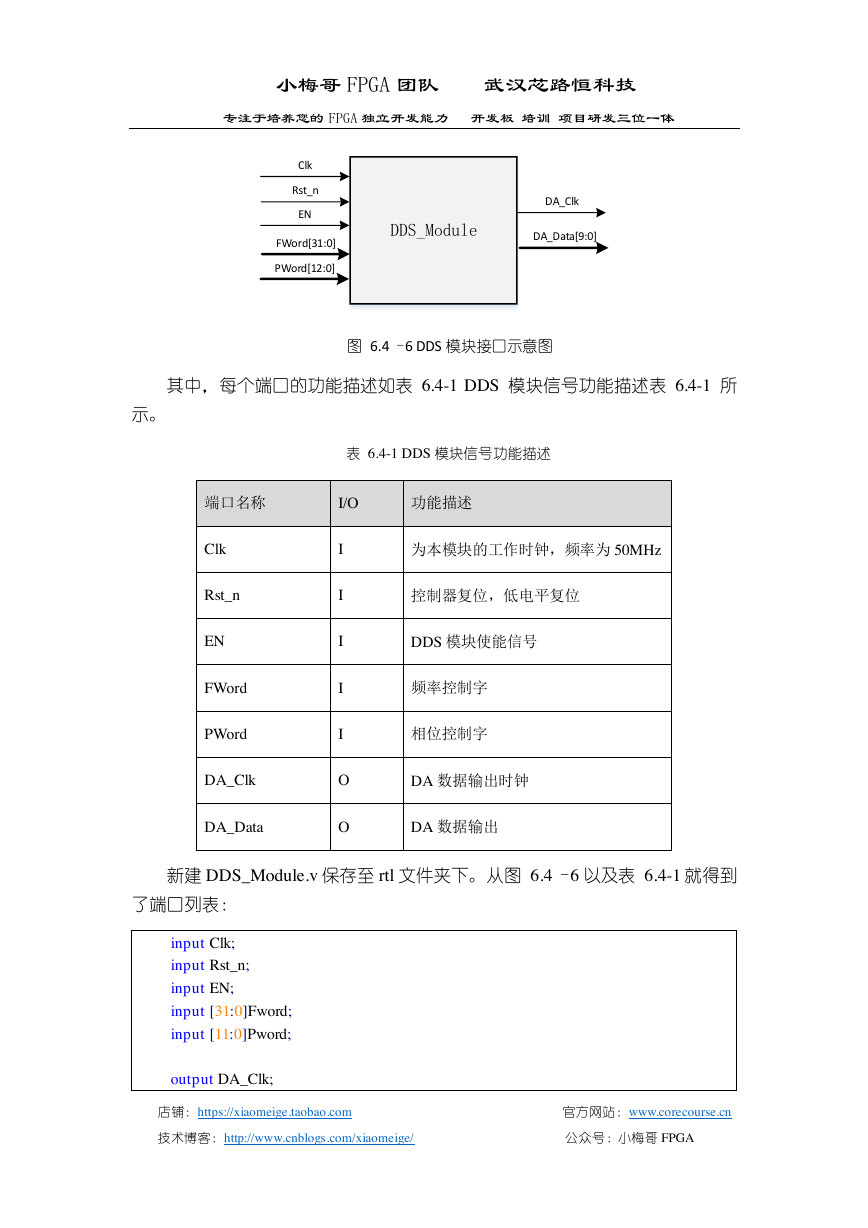

在本设计中参考时钟Fclk频率为 50 MHz,相位累加器位数 N 取 32 位,频率

控制字位数 M 取 12 位。

经过以上的分析,可以得出 DDS 模块的端口模块图如图 6.4–6 所示。

店铺:https://xiaomeige.taobao.com 官方网站:www.corecourse.cn

技术博客:http://www.cnblogs.com/xiaomeige/ 公众号:小梅哥 FPGA

�

小梅哥 FPGA 团队 武汉芯路恒科技

专注于培养您的 FPGA 独立开发能力 开发板 培训 项目研发三位一体

图 6.4–6 DDS 模块接口示意图

其中,每个端口的功能描述如表 6.4-1 DDS 模块信号功能描述表 6.4-1 所

示。

表 6.4-1 DDS 模块信号功能描述

端口名称

I/O

功能描述

Clk

Rst_n

EN

FWord

PWord

DA_Clk

DA_Data

I

I

I

I

I

O

O

为本模块的工作时钟,频率为 50MHz

控制器复位,低电平复位

DDS 模块使能信号

频率控制字

相位控制字

DA 数据输出时钟

DA 数据输出

新建 DDS_Module.v 保存至 rtl 文件夹下。从图 6.4–6 以及表 6.4-1 就得到

了端口列表:

input Clk;

input Rst_n;

input EN;

input [31:0]Fword;

input [11:0]Pword;

output DA_Clk;

店铺:https://xiaomeige.taobao.com 官方网站:www.corecourse.cn

技术博客:http://www.cnblogs.com/xiaomeige/ 公众号:小梅哥 FPGA

DDS_ModuleClkRst_nFWord[31:0]ENDA_ClkPWord[12:0]DA_Data[9:0]�

小梅哥 FPGA 团队 武汉芯路恒科技

专注于培养您的 FPGA 独立开发能力 开发板 培训 项目研发三位一体

output [9:0]DA_Data;

以下只需按照图 6.4–2 进行编写。相位累加器此处即为一个 32bit 的加法

器。

reg [31:0]Fre_acc;

always @(posedge Clk or negedge Rst_n)

if(!Rst_n)

Fre_acc <= 32'd0;

else if(!EN)

Fre_acc <= 32'd0;

else

Fre_acc <= Fre_acc + Fword;

查找表地址生成,此处即为 12bit 的加法器。这里直接截取 32 位累加器结果

中的高 12 位作为 ROM 的查询地址,这样产生的误差会对频谱纯度有影响,但

是对波形的精度的影响是可以忽略的。

reg [11:0]Rom_Addr;

always @(posedge Clk or negedge Rst_n)

if(!Rst_n)

Rom_Addr <= 12'd0;

else if(!EN)

Rom_Addr <= 12'd0;

else

Rom_Addr <= Fre_acc[31:20] + Pword;

DA 数据输出时钟模块使能,通过选择器来进行控制。

assign DA_Clk = (EN)?Clk:1'b1;

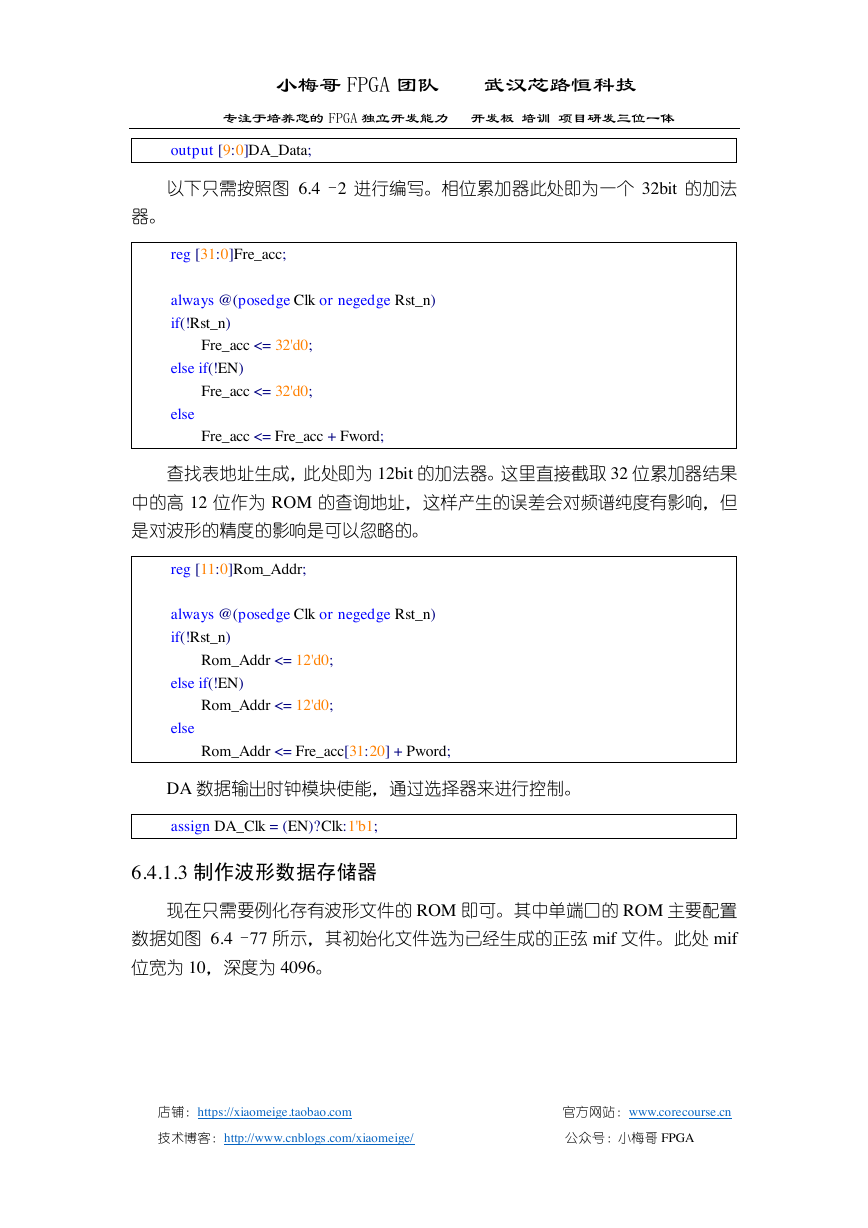

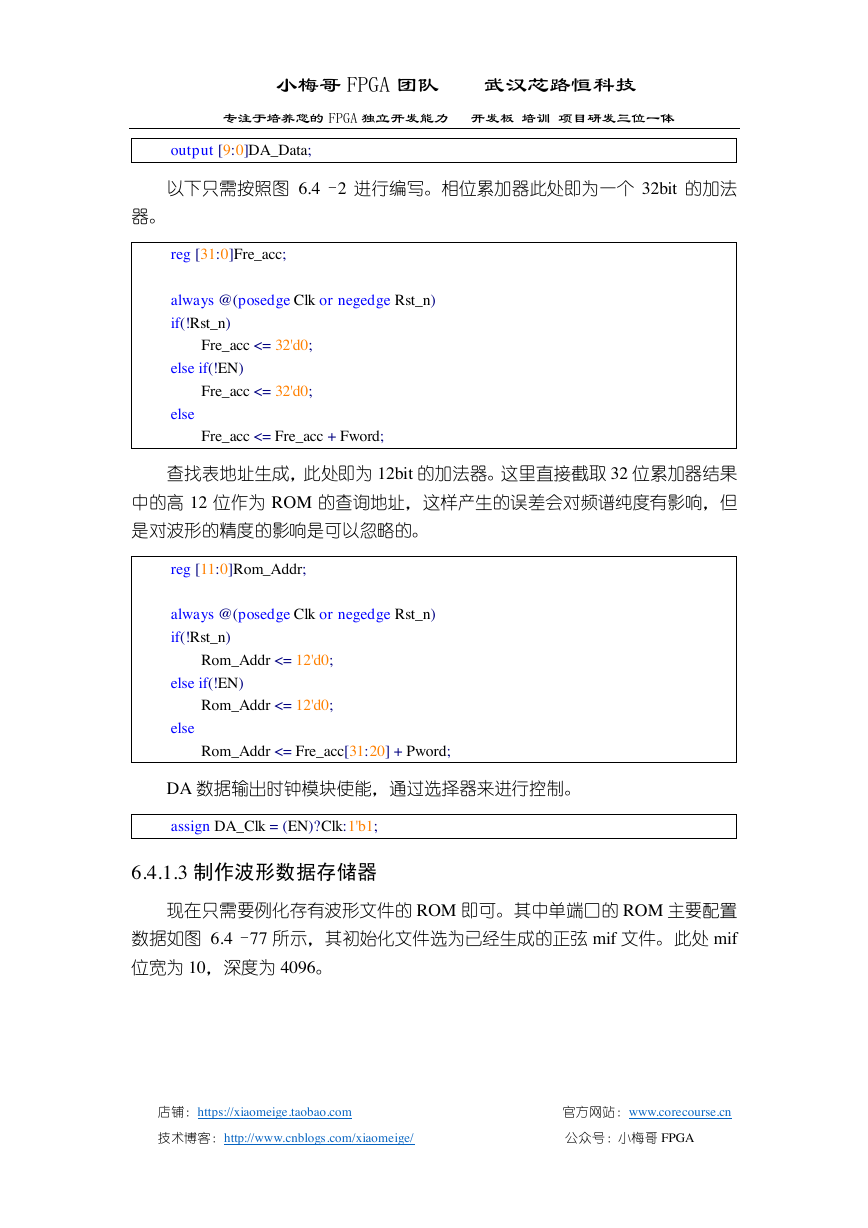

6.4.1.3 制作波形数据存储器

现在只需要例化存有波形文件的 ROM 即可。其中单端口的 ROM 主要配置

数据如图 6.4–77 所示,其初始化文件选为已经生成的正弦 mif 文件。此处 mif

位宽为 10,深度为 4096。

店铺:https://xiaomeige.taobao.com 官方网站:www.corecourse.cn

技术博客:http://www.cnblogs.com/xiaomeige/ 公众号:小梅哥 FPGA

�

小梅哥 FPGA 团队 武汉芯路恒科技

专注于培养您的 FPGA 独立开发能力 开发板 培训 项目研发三位一体

图 6.4–7 ROM 主要配置参数

这样例化到 DDS_Module 中即为如下内容。

ddsrom ddsrom(

.address(Rom_Addr),

.clock(Clk),

.q(DA_Data)

);

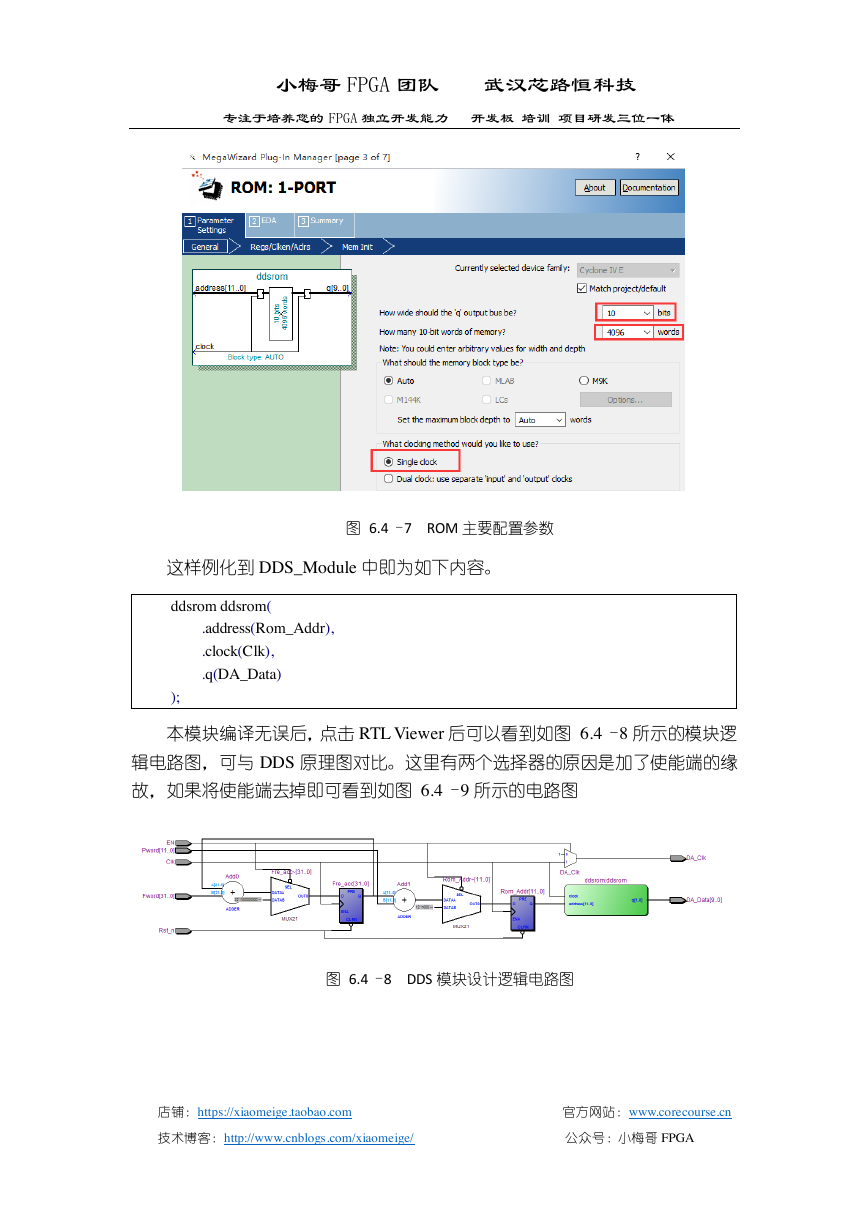

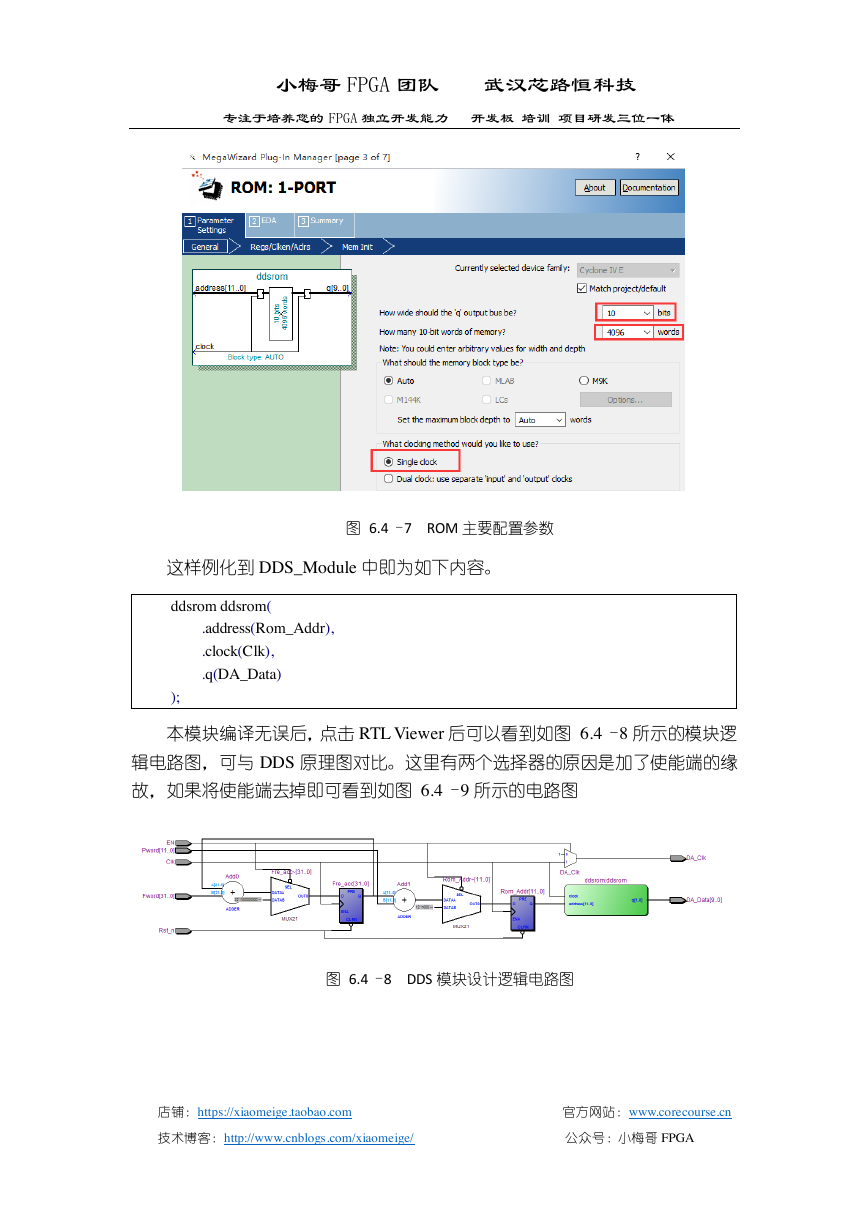

本模块编译无误后,点击 RTL Viewer 后可以看到如图 6.4–8 所示的模块逻

辑电路图,可与 DDS 原理图对比。这里有两个选择器的原因是加了使能端的缘

故,如果将使能端去掉即可看到如图 6.4–9 所示的电路图

图 6.4–8 DDS 模块设计逻辑电路图

店铺:https://xiaomeige.taobao.com 官方网站:www.corecourse.cn

技术博客:http://www.cnblogs.com/xiaomeige/ 公众号:小梅哥 FPGA

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc