大规模集成电路设计基础实验报告

班级:

学号:

姓名:

�

实验一、反相器链缓冲器级数和尺寸优化

1. 实验目的

运用所学理论知识,完成一个 CMOS 工艺数字集成电路的设计,并用 HSPICE 软件验证

电路设计的正确性。加深对 MOS 晶体管理论、CMOS 数字电路的理解,掌握 MOS 晶体管尺

寸调整对时序电路性能参数影响的规律,设计正确的数字缓冲器电路。

2. 实验要求

采用所学过的 CMOS 数字集成电路结构,设计缓冲器电路(偶数个反相器链组成)满

足下列指标(晶体管最小长度 L 为 0.24um,最小宽度为 0.24um): VDD=2.5V;

1).设计缓冲器电路中的反相器的级数和反相器尺寸放大的倍数,当输出负载为 100pF,

使传输延时最小;采用附录所给的晶体管模型。

2).Hspice 进行仿真验证,给出缓冲器电路尺寸为最小时,电路的延时时间;经过优化之

后,缓冲器的延时时间各是多少。

3. 实验材料

HSPICE 仿真软件,原理图输入工具 scad3,可选,用于生成 SPICE 网表。也可以自己编

写 HSPICE 网表程序。

4. 报告要求

独立完成电路结构设计和电路参数的调试,给出最终完成的电路图或者电路的 SPICE

网表。给出 HPSICE 仿真结果,分析瞬态仿真结果,表明所设计的电路达到实验要求。

5. 实验参数计算

本设计使用的 CMOS 工艺为 0.25um 工艺,要完成实验要求,设计出一个 N(偶数)级反

相器链,使总延时最小,需要已知的参数有 CL,Cg,1 和 tp0。其中,CL 和 Cg,1 直接影响最后

设计出的反相器链的级数及各级的尺寸,而 tp0 影响具体延时时间,本题中 tp0 可暂不考虑

其影响。这里题目给出 CL=100pF,因此需估出 Cg,1 的值。

1

�

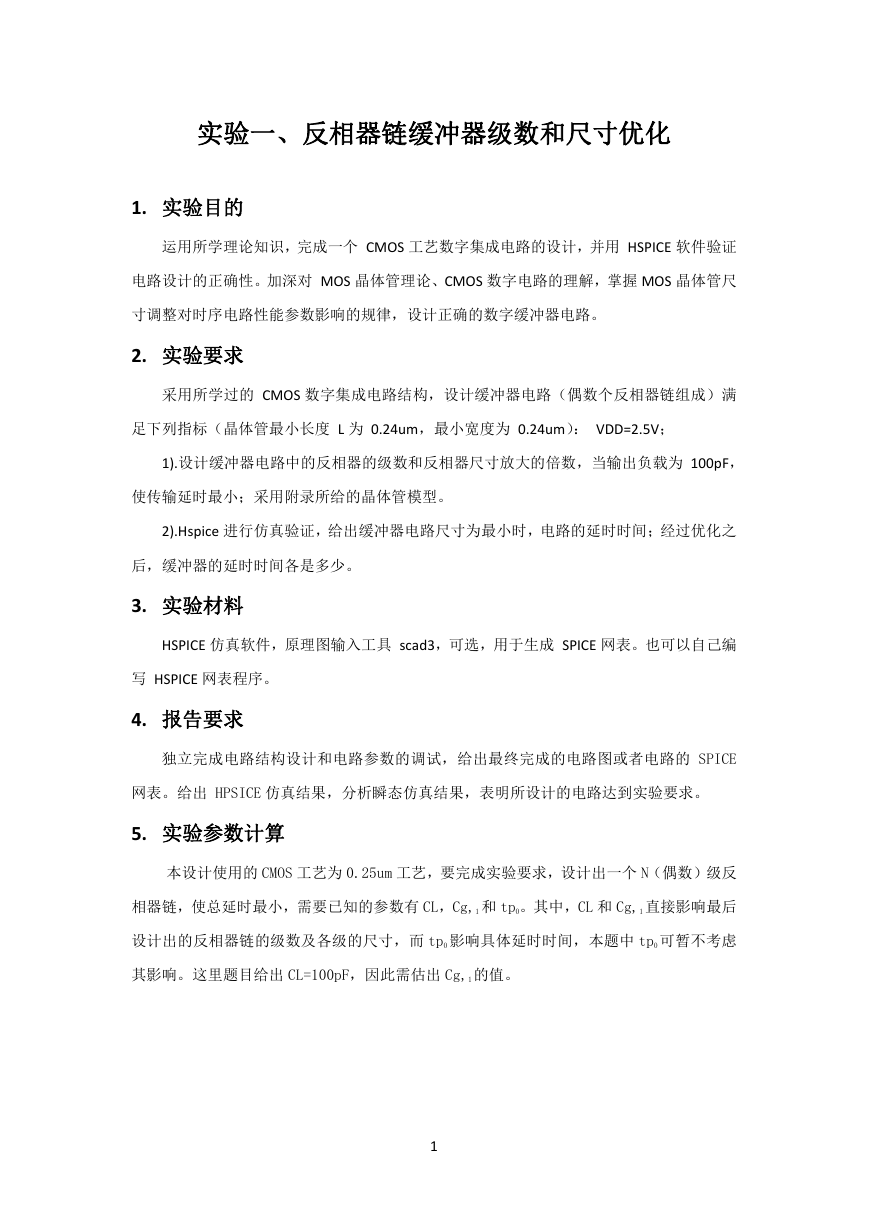

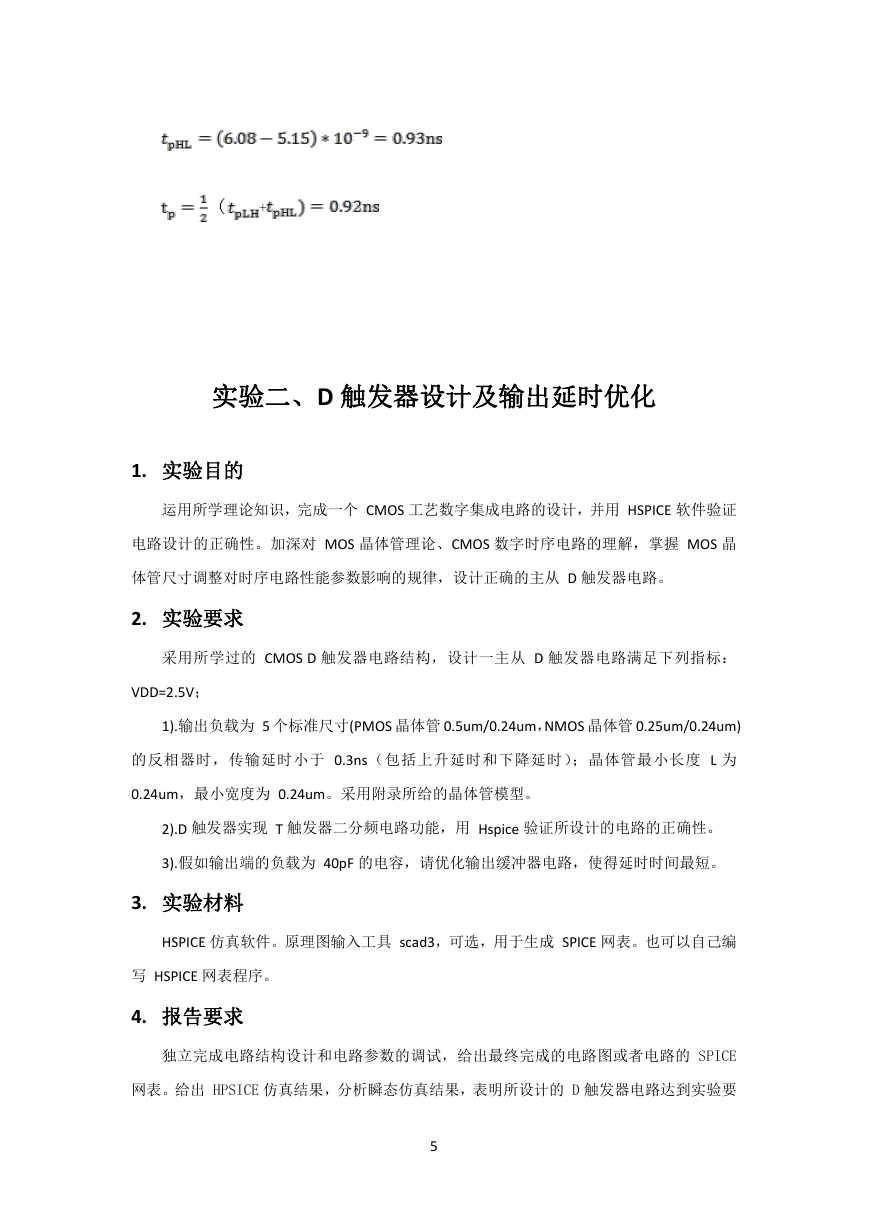

图 1 缓冲器的级联

反相器链的 Cg,1 可认为是第一级反相器(最小尺寸)本身的寄生电容 Cint1,由教材

第 216 页公式(4-24),Cint=Cdb1+Cdb2+Cgd12。同时有该页底部表 4.1,即下表:

0.25um CMOS 最小尺寸对称反相器负载电容

电容

Cgd1

H-L(fF) 0.23

L-H(fF)

0.23

Cgd2

0.61

0.61

Cdb1

0.66

0.90

Cdb2

1.5

1.15

Cgs3

0.76

0.97

Cgs4

2.28

2.28

Cw

0.12

0.12

CL

6.1

6.0

因此,可算出 Cg,1 实际电容在 3fF 左右。

下面进行反相器链的设计:

Cg,1=3fF,CL=100pF,暂时先设 f=4,

,使延时最小所需的级数为:

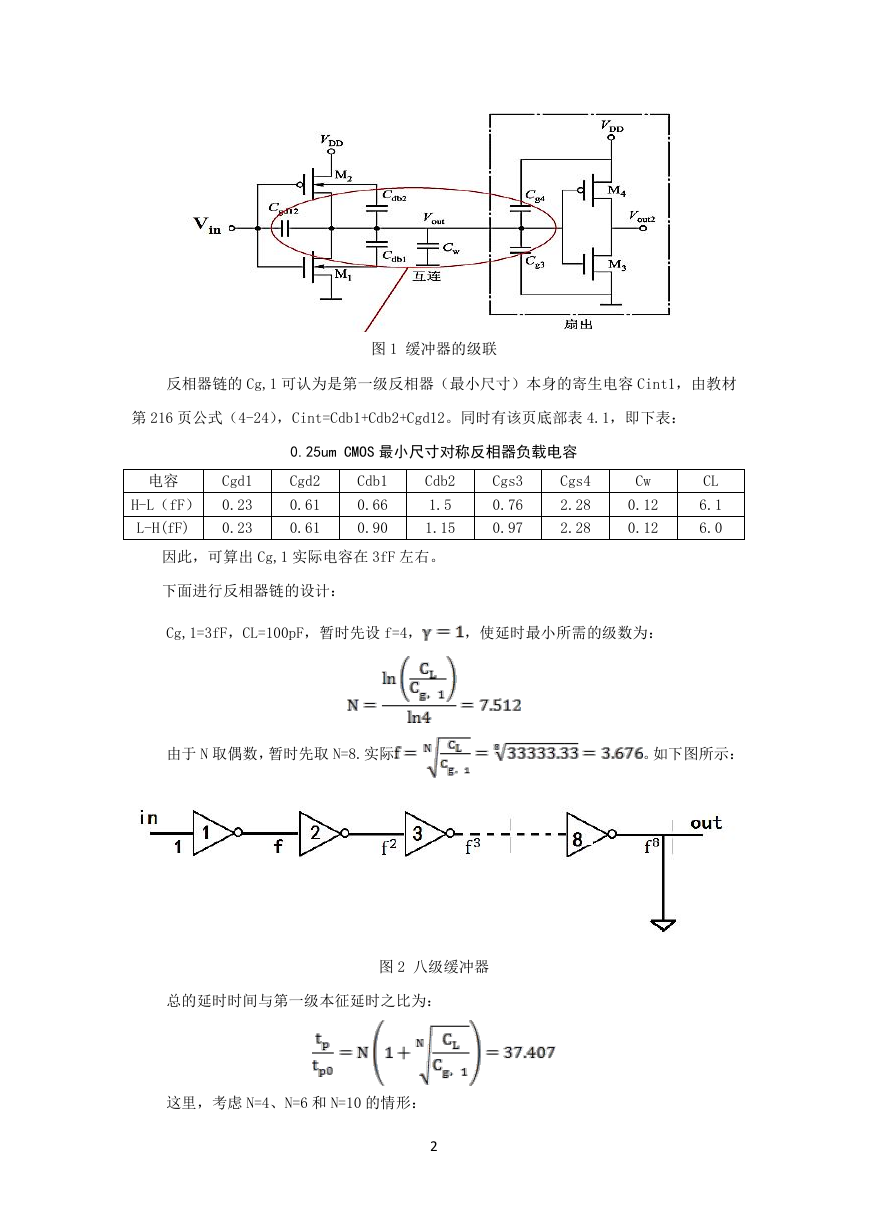

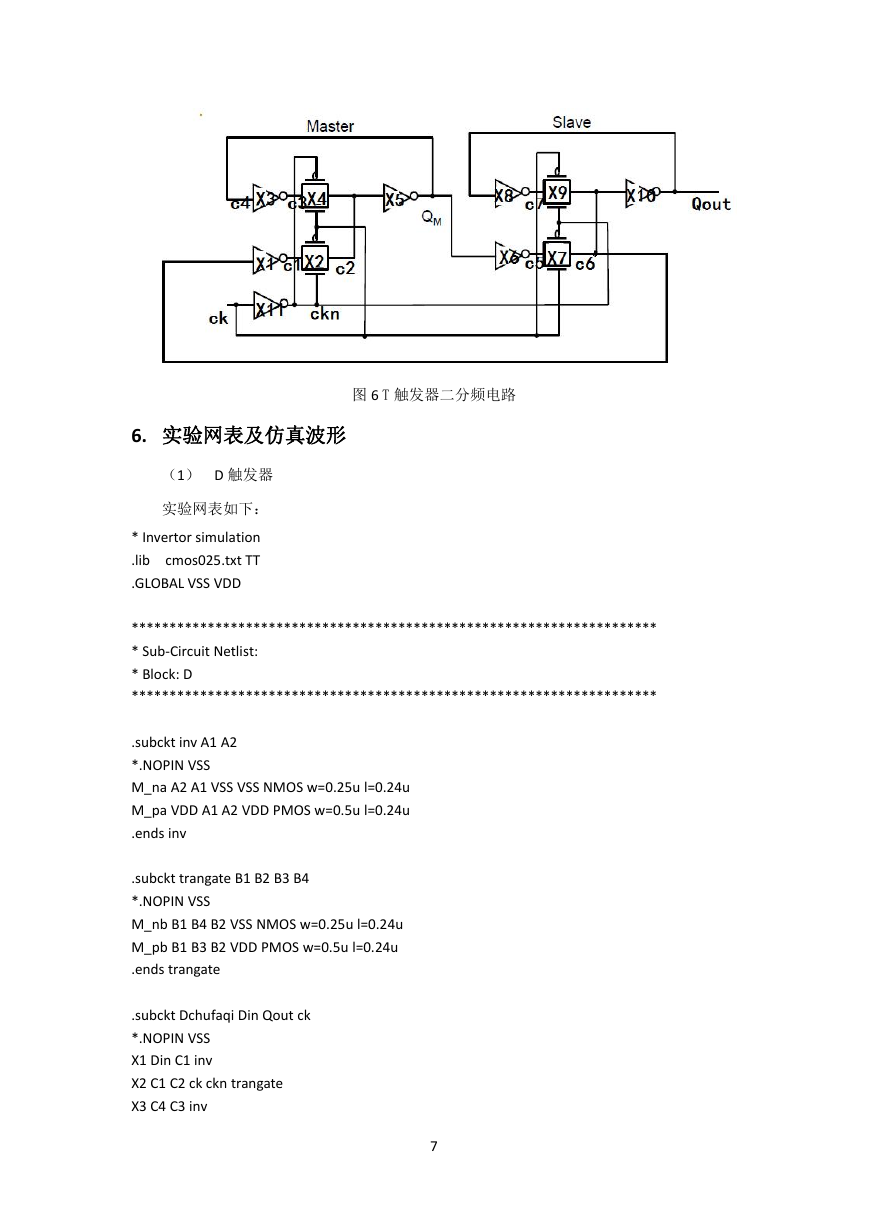

由于 N 取偶数,暂时先取 N=8.实际

。如下图所示:

总的延时时间与第一级本征延时之比为:

图 2 八级缓冲器

这里,考虑 N=4、N=6 和 N=10 的情形:

2

�

N=4,f=13.512

N=6,f=5.673

N=10,f=2.833

可以看出,N=8 确实能使延时最小,但与 N=6 与 N=10 的总延时数据差别不大。在对延

时要求不是特别严格的情况下,可以使用 N=6 甚至 N=4 代替,可大大节约版图的面积。

6. 实验网表及仿真波形

实验网表如下:

* Invertor simulation

.lib cmos025.txt TT

.GLOBAL VSS VDD

*********************************************************************

* Sub-Circuit Netlist:

* Block: buffer

********************************************************************

.subckt buffer OUT IN

*.NOPIN VSS

M_n1 A IN VSS VSS NMOS w=0.24u l=0.24u

M_p1 VDD IN A VDD PMOS w=0.48u l=0.24u

M_n2 B A VSS VSS NMOS w=0.882u l=0.24u

M_p2 VDD A B VDD PMOS w=1.764u l=0.24u

M_n3 C B VSS VSS NMOS w=3.243u l=0.24u

M_p3 VDD B C VDD PMOS w=6.486u l=0.24u

M_n4 D C VSS VSS NMOS w=11.920u l=0.24u

M_p4 VDD C D VDD PMOS w=23.841u l=0.24u

M_n5 E D VSS VSS NMOS w=43.818u l=0.24u

M_p5 VDD D E VDD PMOS w=87.636u l=0.24u

M_n6 F E VSS VSS NMOS w=161.068u l=0.24u

M_p6 VDD E F VDD PMOS w=322.137u l=0.24u

M_n7 G F VSS VSS NMOS w=592.066u l=0.24u

M_p7 VDD F G VDD PMOS w=1184.132u l=0.24u

M_n8 OUT G VSS VSS NMOS w=2176.357u l=0.24u

M_p8 VDD G OUT VDD PMOS w=4352.714u l=0.24u

CL OUT VSS 100PF

.ends buffer

3

�

x1 OUT IN buffer

*Power Supply

VDD VDD 0 2.5

VSS VSS 0 0

vin IN 0 pulse (0 2.5 0.1n 0.1n 0.1n 4.9n 10n)

.op

.option post ACCT NOMOD list ACOUT=0

.dc vin 0 2.5 0.01

.tran 1ns 10n

.end

.end

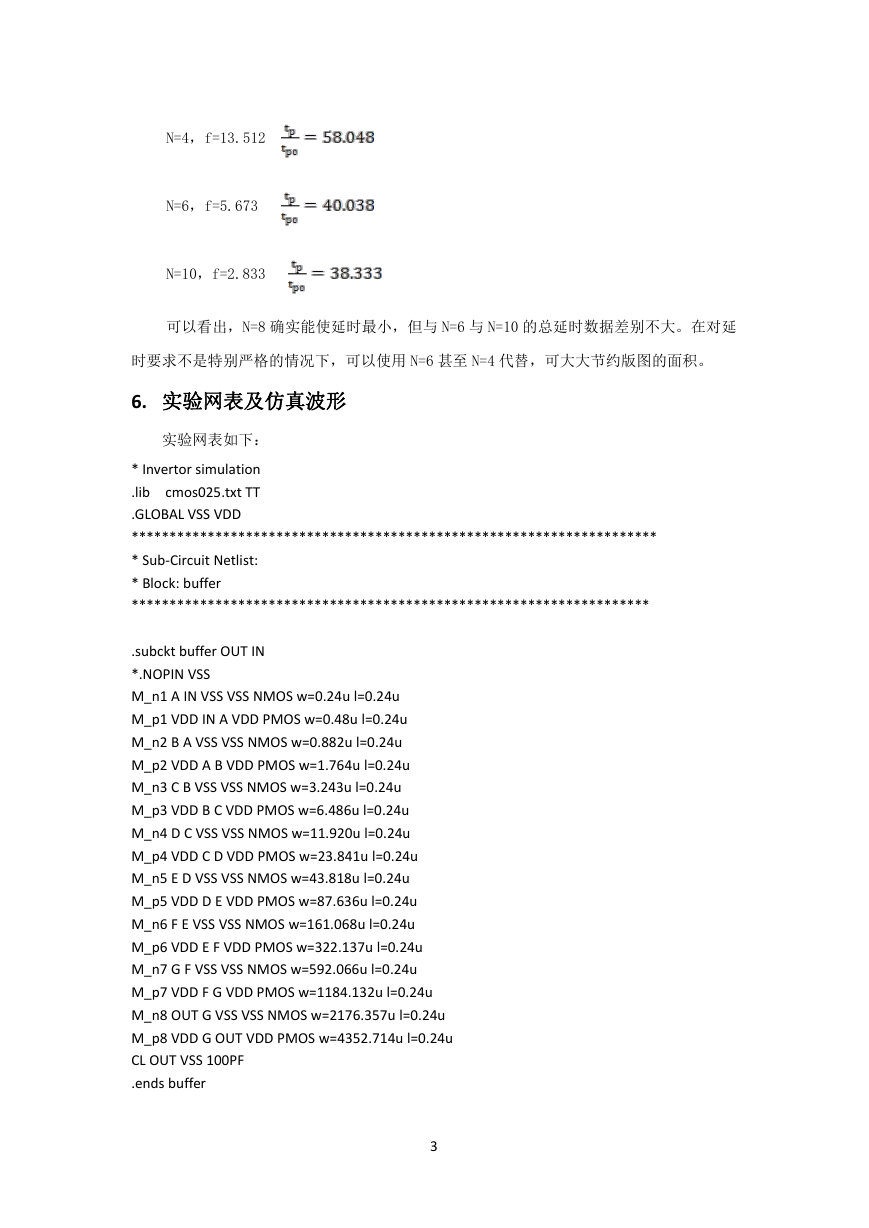

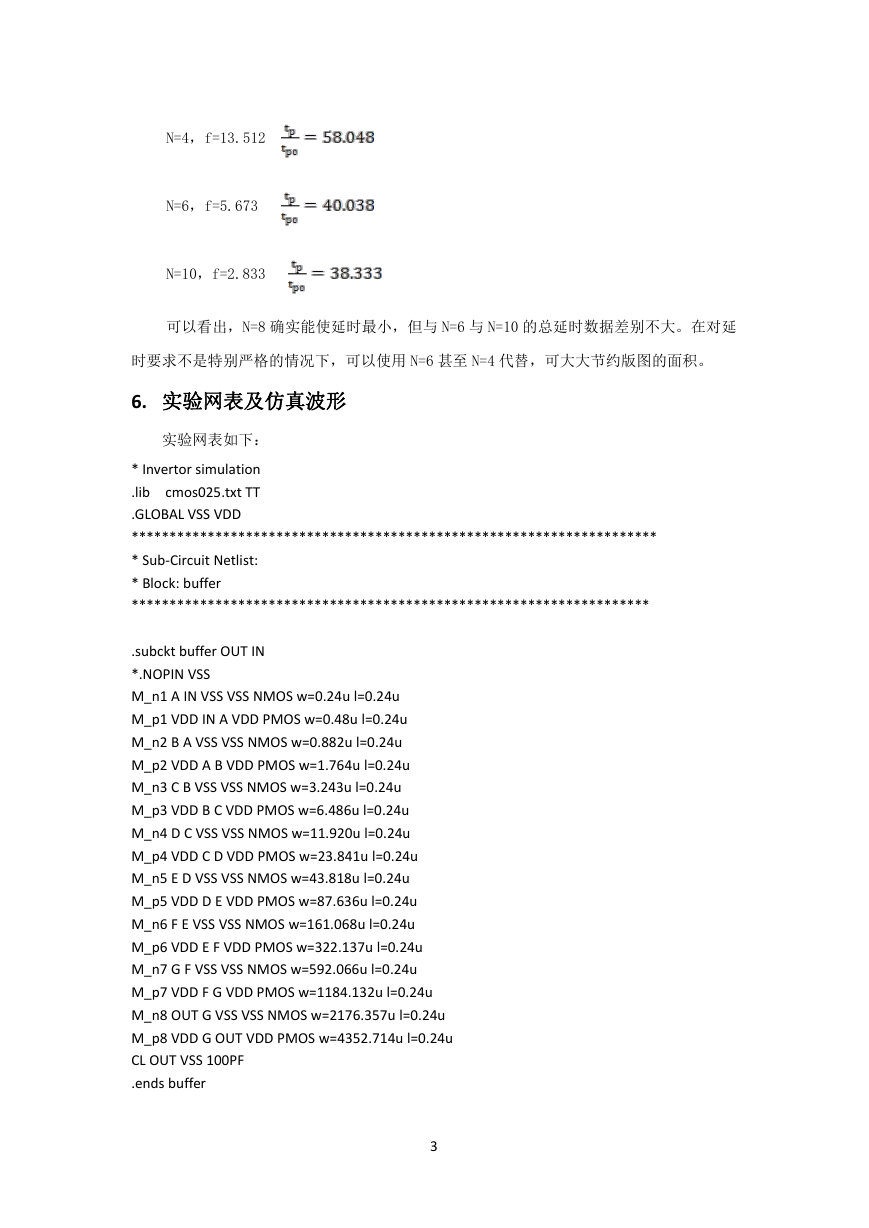

仿真波形如下:

图 3 8 级缓冲器的波形

两个标记如下:

实验结果分析:

传输延时:

4

�

+

实验二、D 触发器设计及输出延时优化

1. 实验目的

运用所学理论知识,完成一个 CMOS 工艺数字集成电路的设计,并用 HSPICE 软件验证

电路设计的正确性。加深对 MOS 晶体管理论、CMOS 数字时序电路的理解,掌握 MOS 晶

体管尺寸调整对时序电路性能参数影响的规律,设计正确的主从 D 触发器电路。

2. 实验要求

采用所学过的 CMOS D 触发器电路结构,设计一主从 D 触发器电路满足下列指标:

VDD=2.5V;

1).输出负载为 5 个标准尺寸(PMOS 晶体管 0.5um/0.24um,NMOS 晶体管 0.25um/0.24um)

的反相器时,传输延时小于 0.3ns(包括上升延时和下降延时);晶体管最小长度 L 为

0.24um,最小宽度为 0.24um。采用附录所给的晶体管模型。

2).D 触发器实现 T 触发器二分频电路功能,用 Hspice 验证所设计的电路的正确性。

3).假如输出端的负载为 40pF 的电容,请优化输出缓冲器电路,使得延时时间最短。

3. 实验材料

HSPICE 仿真软件。原理图输入工具 scad3,可选,用于生成 SPICE 网表。也可以自己编

写 HSPICE 网表程序。

4. 报告要求

独立完成电路结构设计和电路参数的调试,给出最终完成的电路图或者电路的 SPICE

网表。给出 HPSICE 仿真结果,分析瞬态仿真结果,表明所设计的 D 触发器电路达到实验要

5

�

求。

5. 实验参数计算

采用教科书中传输管实现的主从 D 触发器,所有晶体管均采用最小尺寸,将反相器及

传输管独立出来编写子电路模块,简化电路搭建和网表编写。

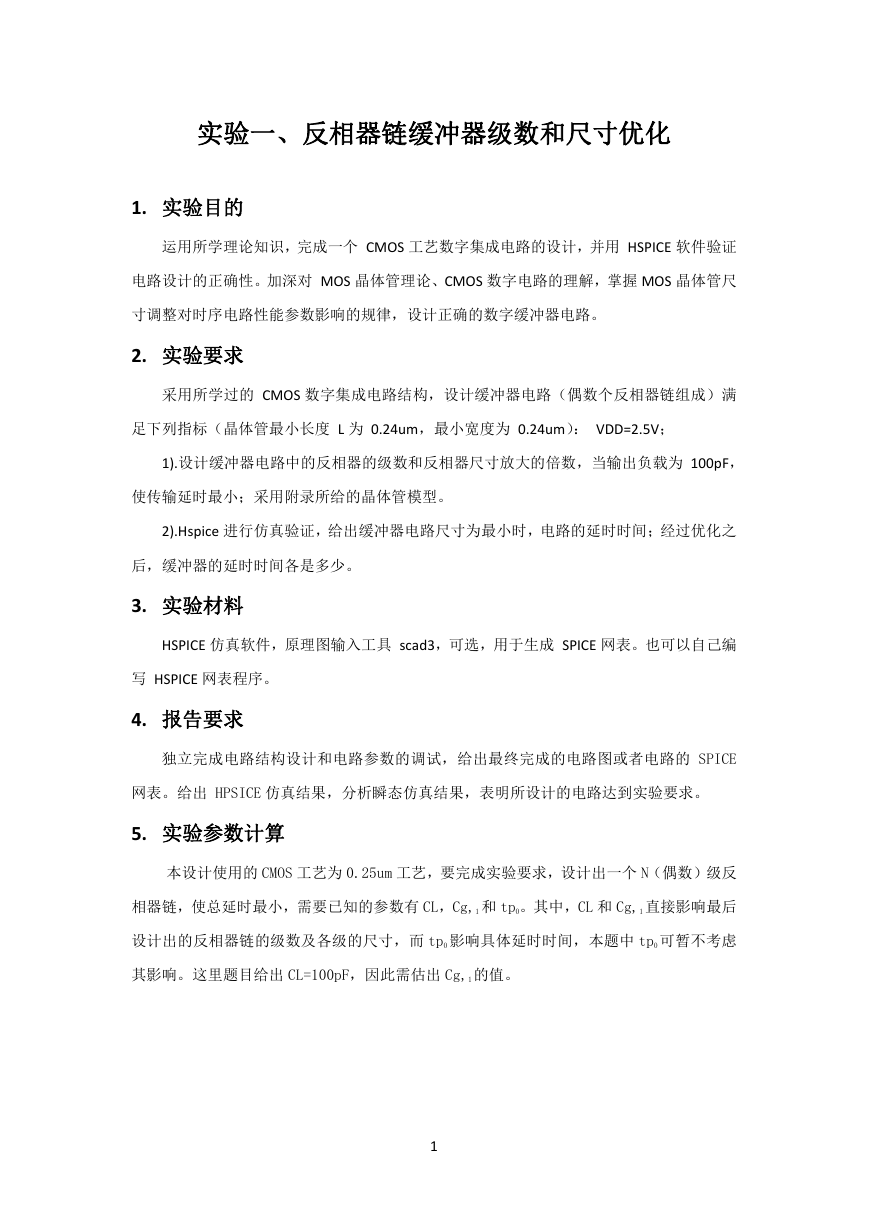

D 触发器实验电路图如下:

图 4 D 触发器实验电路图

(1) 当负载为 5 个标准尺寸的反相器时,实验电路图如下:

图 5 负载为 5 个标准尺寸的反相器时的 D 触发器

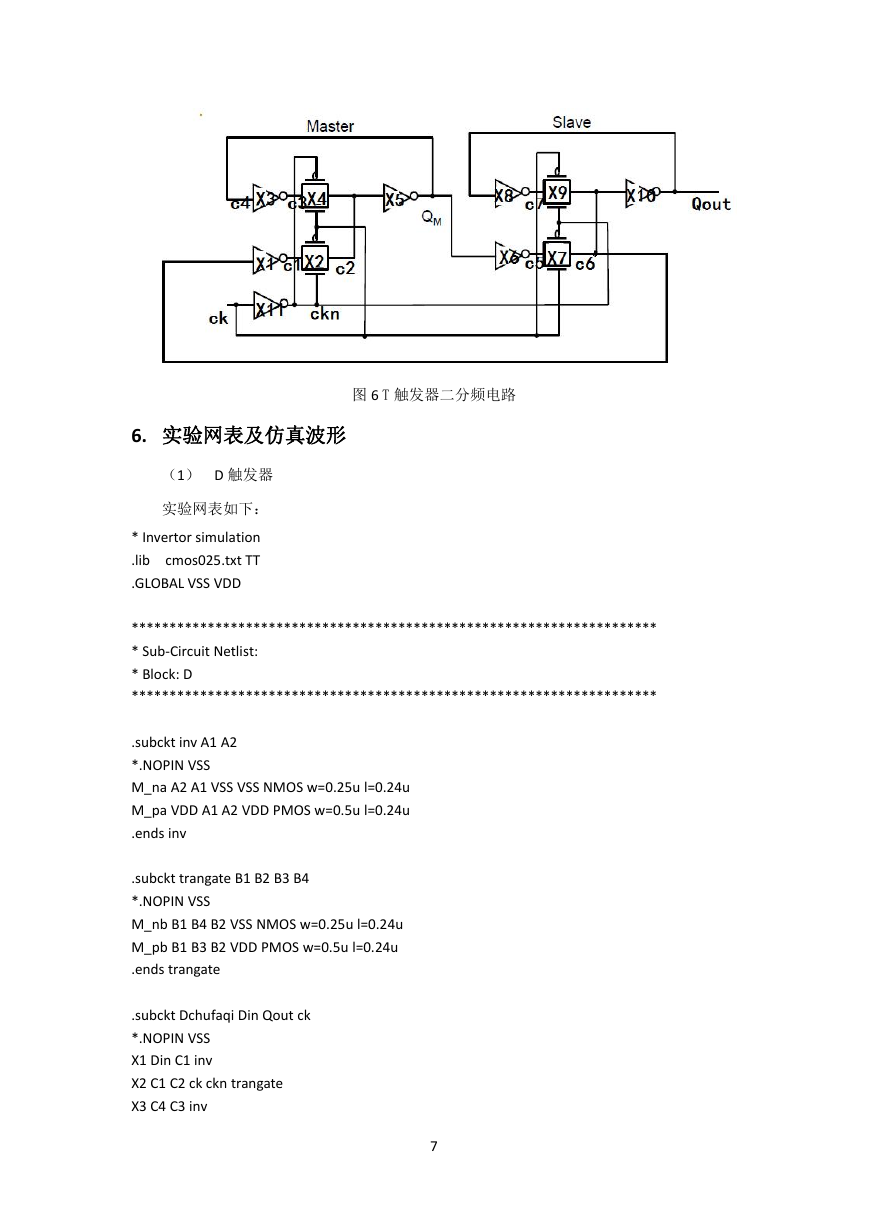

(2)D 触发器实现 T 触发器二分频电路功能。

将 D 触发器的!Q 端与 D 触发器的输入相连,输出 Qout 即对 ck 输入二分频。电路图如

下所示:

6

�

图 6 T 触发器二分频电路

6. 实验网表及仿真波形

(1) D 触发器

实验网表如下:

* Invertor simulation

.lib cmos025.txt TT

.GLOBAL VSS VDD

*********************************************************************

* Sub-Circuit Netlist:

* Block: D

*********************************************************************

.subckt inv A1 A2

*.NOPIN VSS

M_na A2 A1 VSS VSS NMOS w=0.25u l=0.24u

M_pa VDD A1 A2 VDD PMOS w=0.5u l=0.24u

.ends inv

.subckt trangate B1 B2 B3 B4

*.NOPIN VSS

M_nb B1 B4 B2 VSS NMOS w=0.25u l=0.24u

M_pb B1 B3 B2 VDD PMOS w=0.5u l=0.24u

.ends trangate

.subckt Dchufaqi Din Qout ck

*.NOPIN VSS

X1 Din C1 inv

X2 C1 C2 ck ckn trangate

X3 C4 C3 inv

7

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc