ISE 10.1Steps

1 new project

1. 双 击 桌 面 Xilinx ISE10.1 快 捷 方 式 打 开 ISE 工 程 管 理 器 (Project

Navigator)。

2. 打开 Project Navigator 后,选择 File → New Project ,弹出新建工程

对话框,填写工程名字,工程存放位置。注意,不要填写含有中文的名字,以免

发生错误。

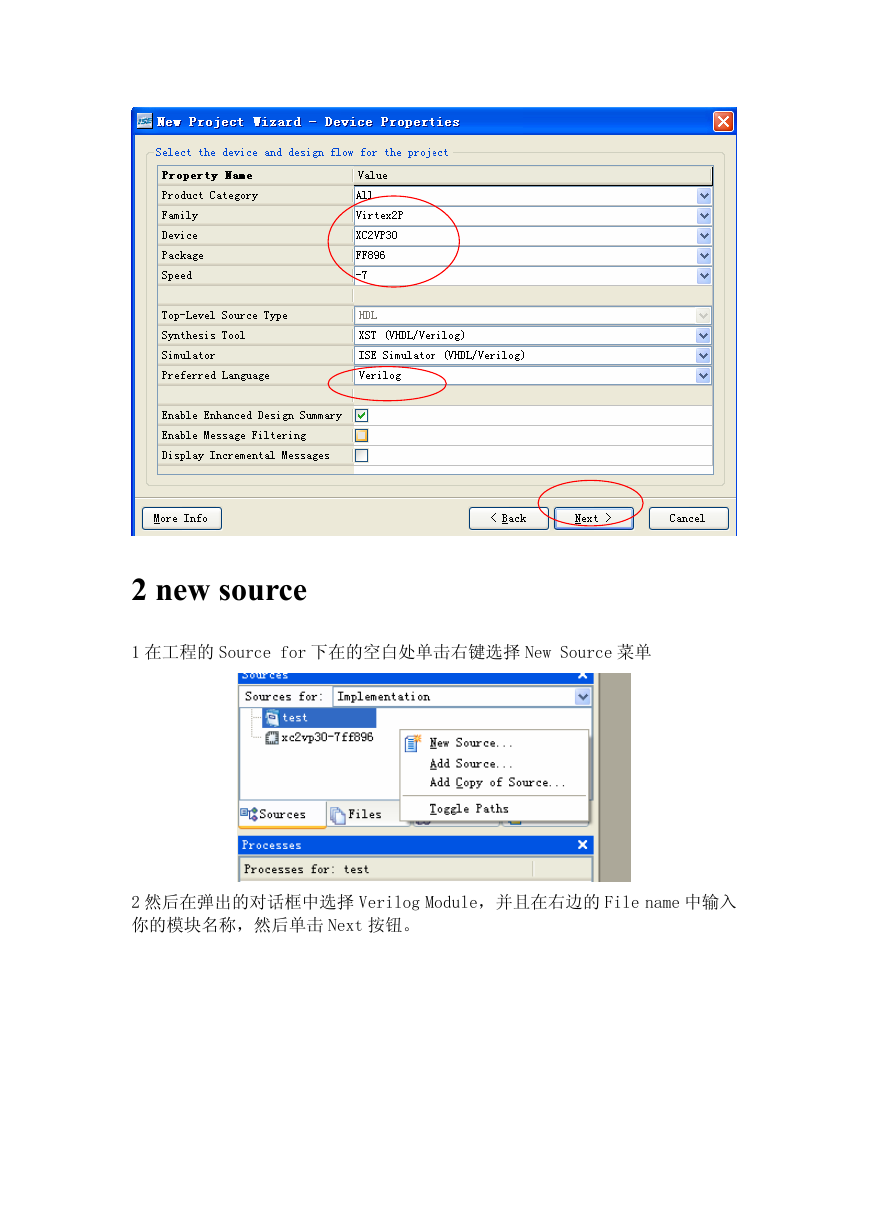

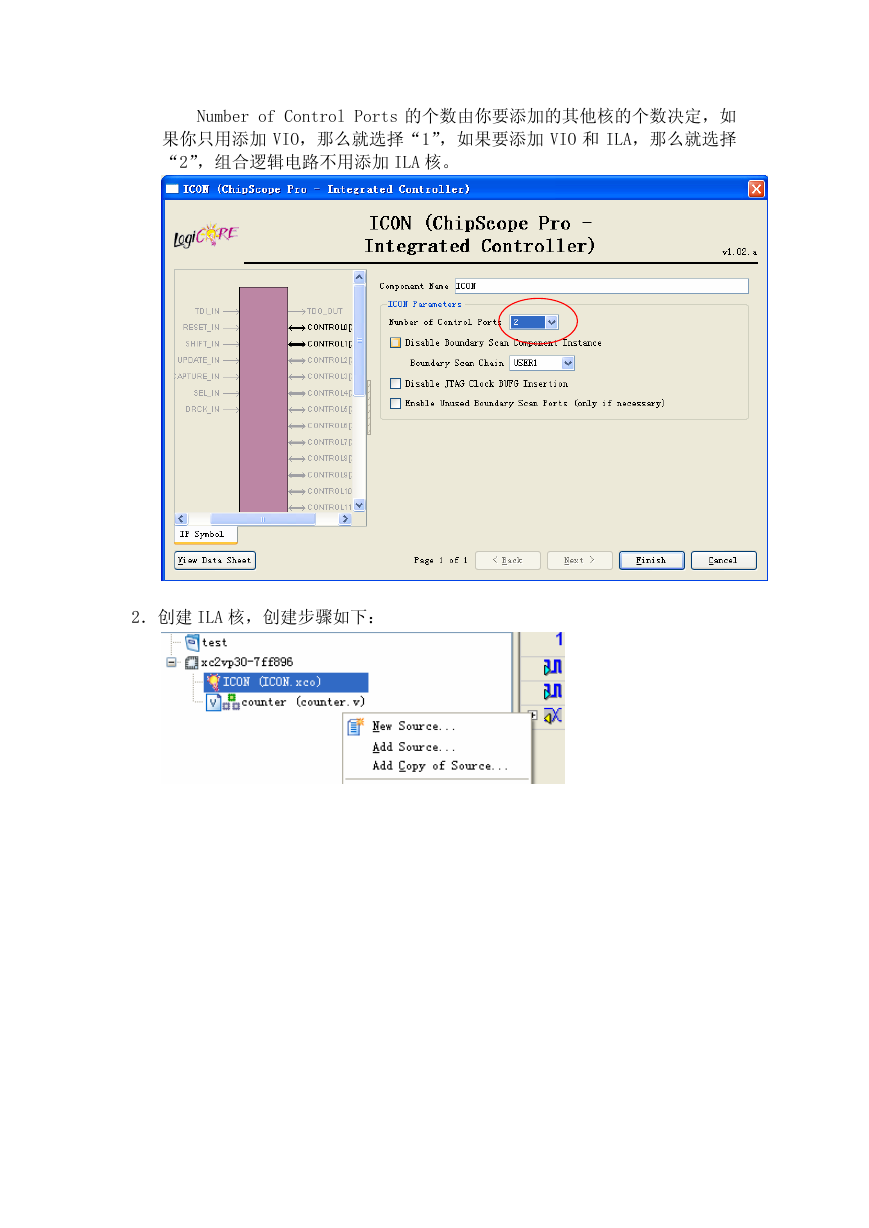

3.点击 Next 按钮,弹出器件特性对话框。Device Family 选择“Virtex2P”,

Device 选“XC2VP30 ,Package 选择 ff896,Speed 选 -7”,其他选择如下图所

示。其中这些选择由按 FPGA 开发板的型号来决定的。然后点击 NEXT,继续单击

ext 按钮,然后单击 Finish 按钮完成对工程的建立和基本设置。

N

�

2 new source

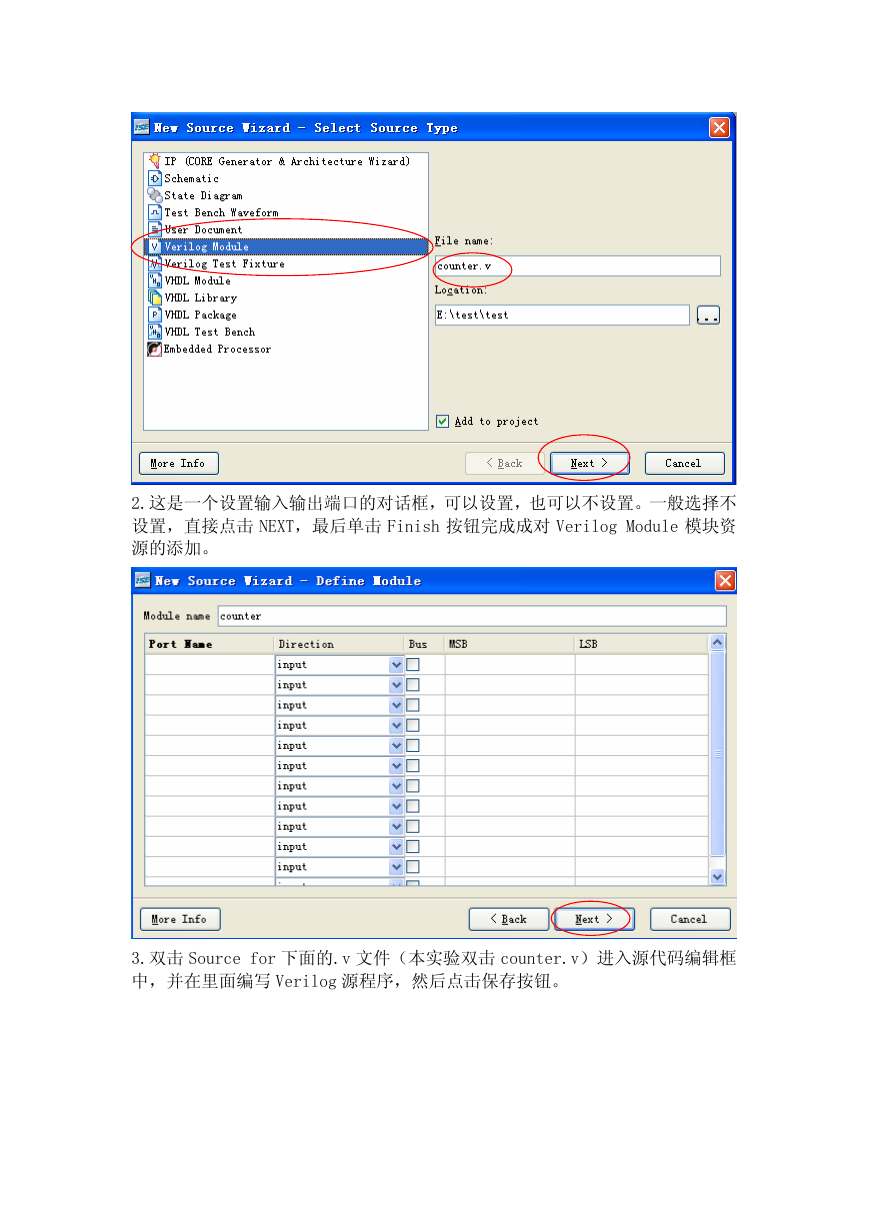

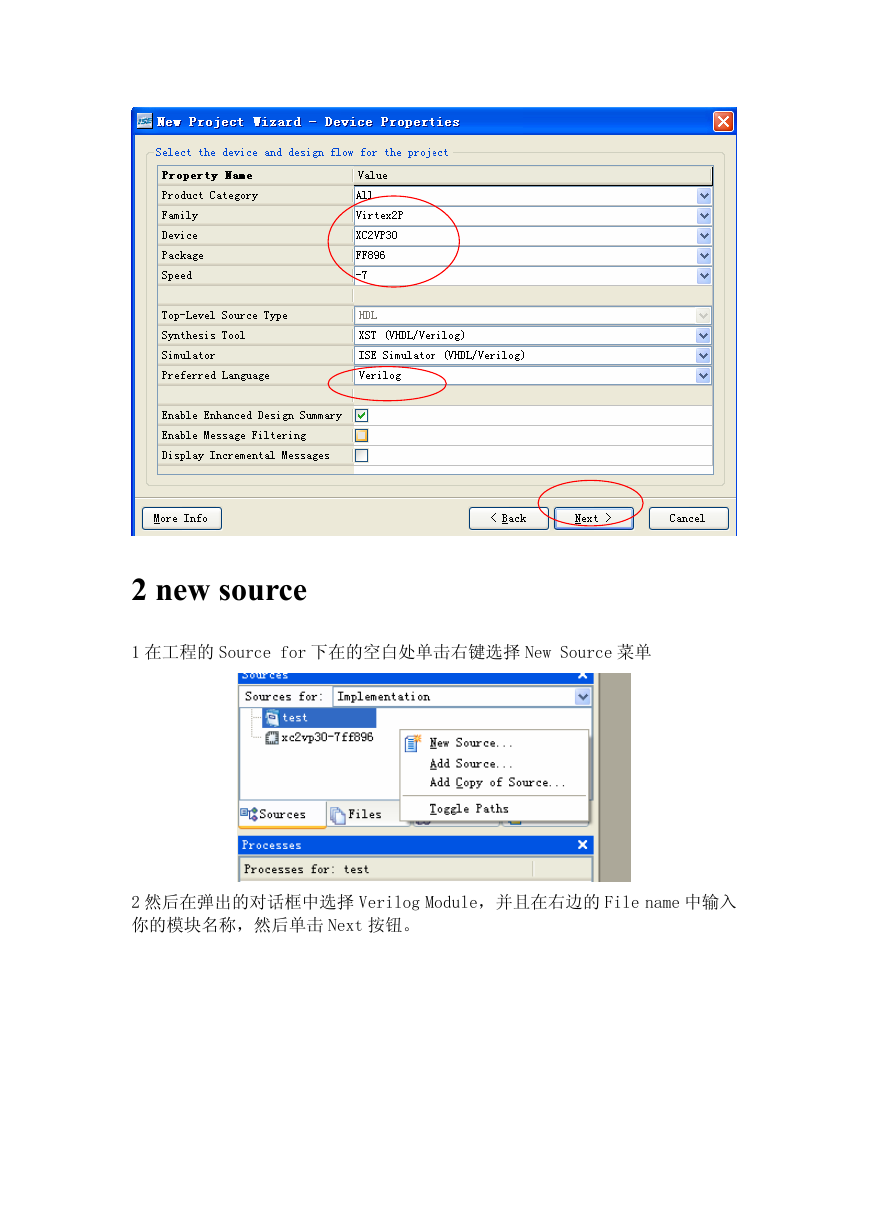

1 在工程的 Source for 下在的空白处单击右键选择 New Source 菜单

2 然后在弹出的对话框中选择 Verilog Module,并且在右边的 File name 中输入

你的模块名称,然后单击 Next 按钮。

�

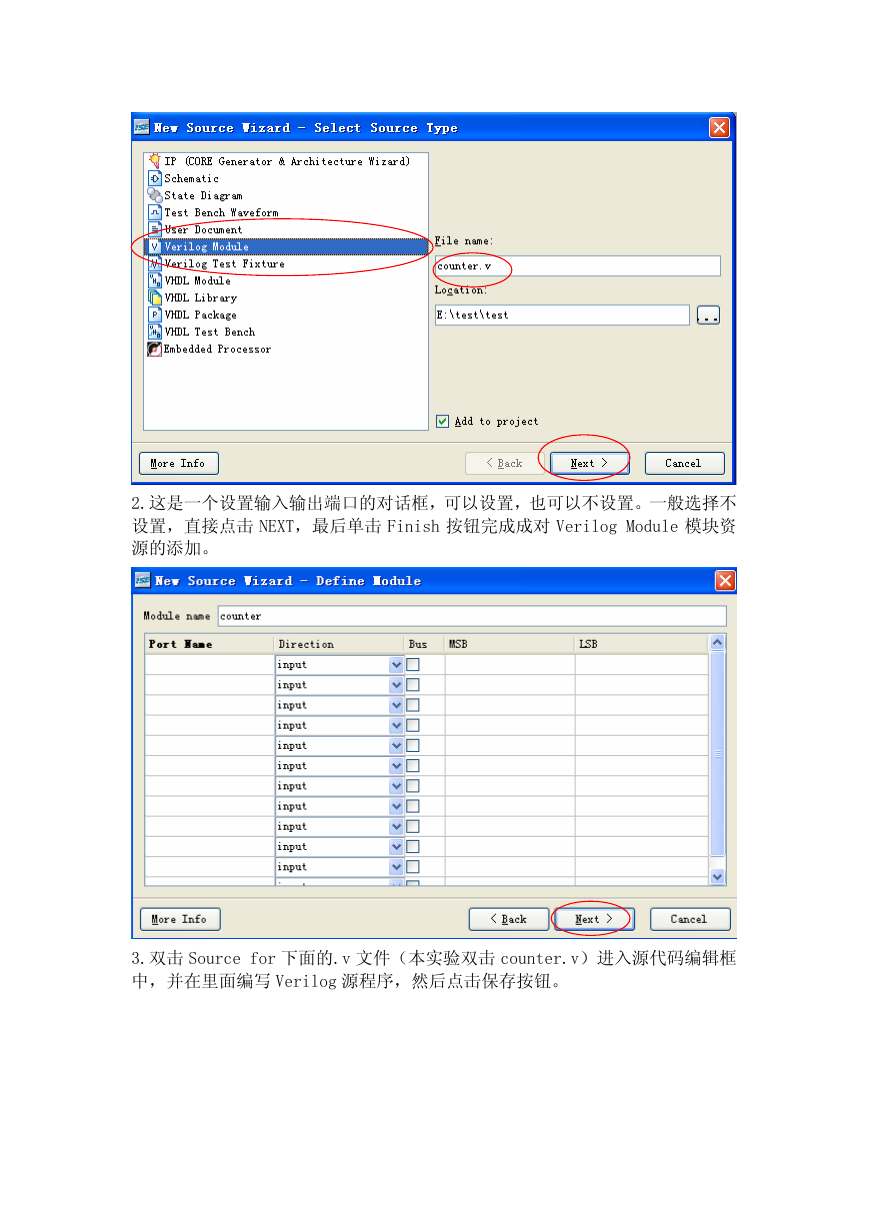

2.这是一个设置输入输出端口的对话框,可以设置,也可以不设置。一般选择不

设置,直接点击 NEXT,最后单击 Finish 按钮完成成对 Verilog Module 模块资

源的添加。

3.双击 Source for 下面的.v 文件(本实验双击 counter.v)进入源代码编辑框

中,并在里面编写 Verilog 源程序,然后点击保存按钮。

�

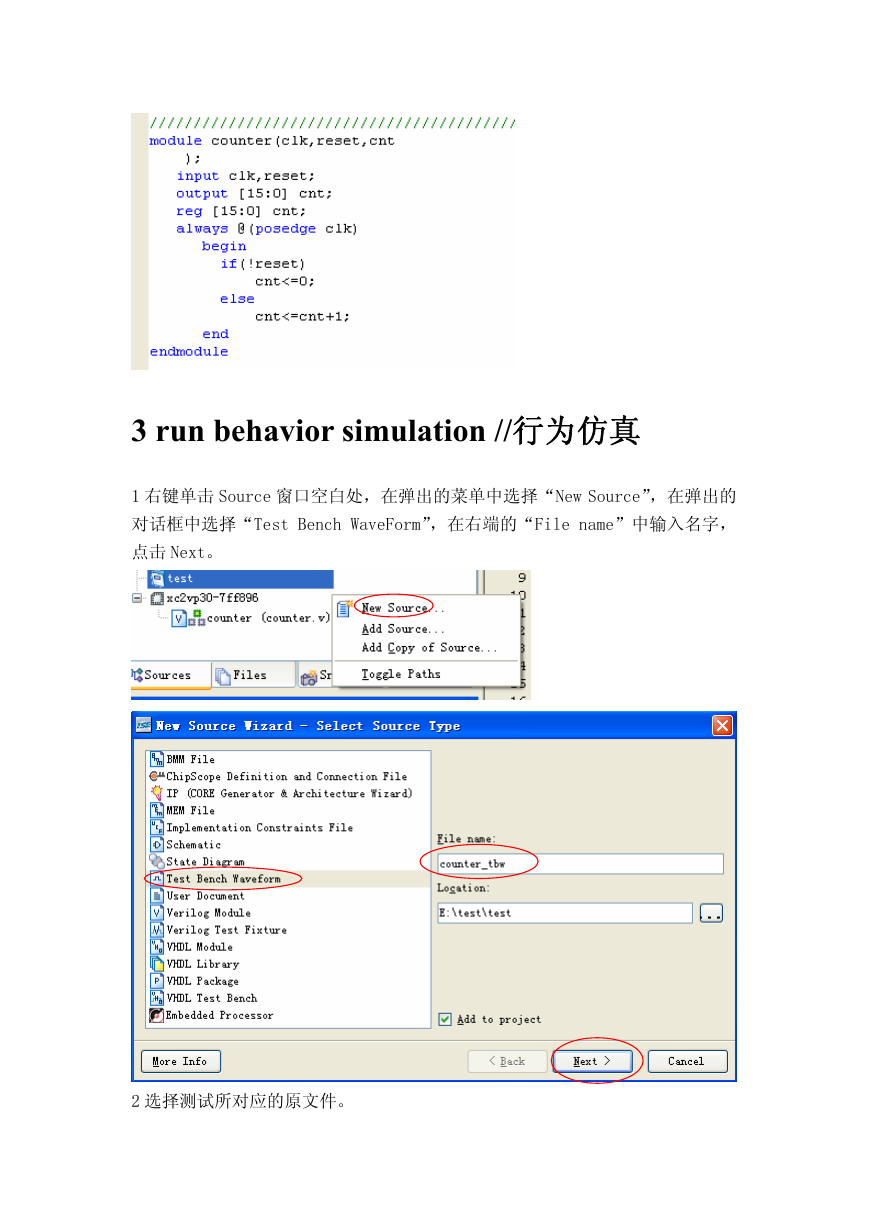

3 run behavior simulation //行为仿真

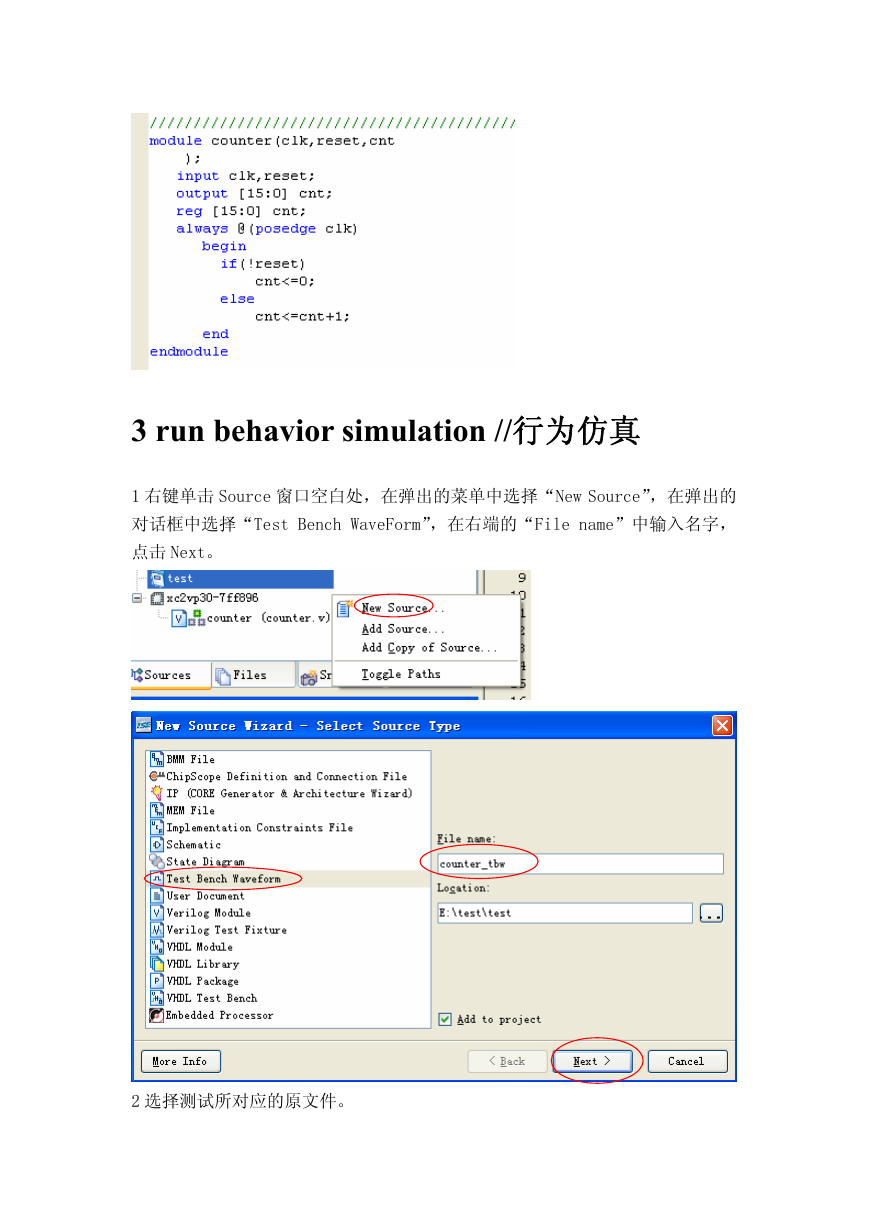

1 右键单击 Source 窗口空白处,在弹出的菜单中选择“New Source”,在弹出的

对话框中选择“Test Bench WaveForm”,在右端的“File name”中输入名字,

点击 Next。

2 选择测试所对应的原文件。

�

3.设置时钟参数,如果是组合逻辑电路,注意在 clock information 中选择

combinatorial 选项。

�

4.设置激励波形,在要设定的波形上,点击鼠标就可以设定波形。但是要注意,

设定的波形应该能检验你所设计的电路。

5.然后单击.tbw 文件,在 processes 窗口中双击“simulater behavioral model”

进得功能仿真。观察仿真结果,如果不正确,修改源代码,直到仿真结果满足设

计要求。

4 ChipScope

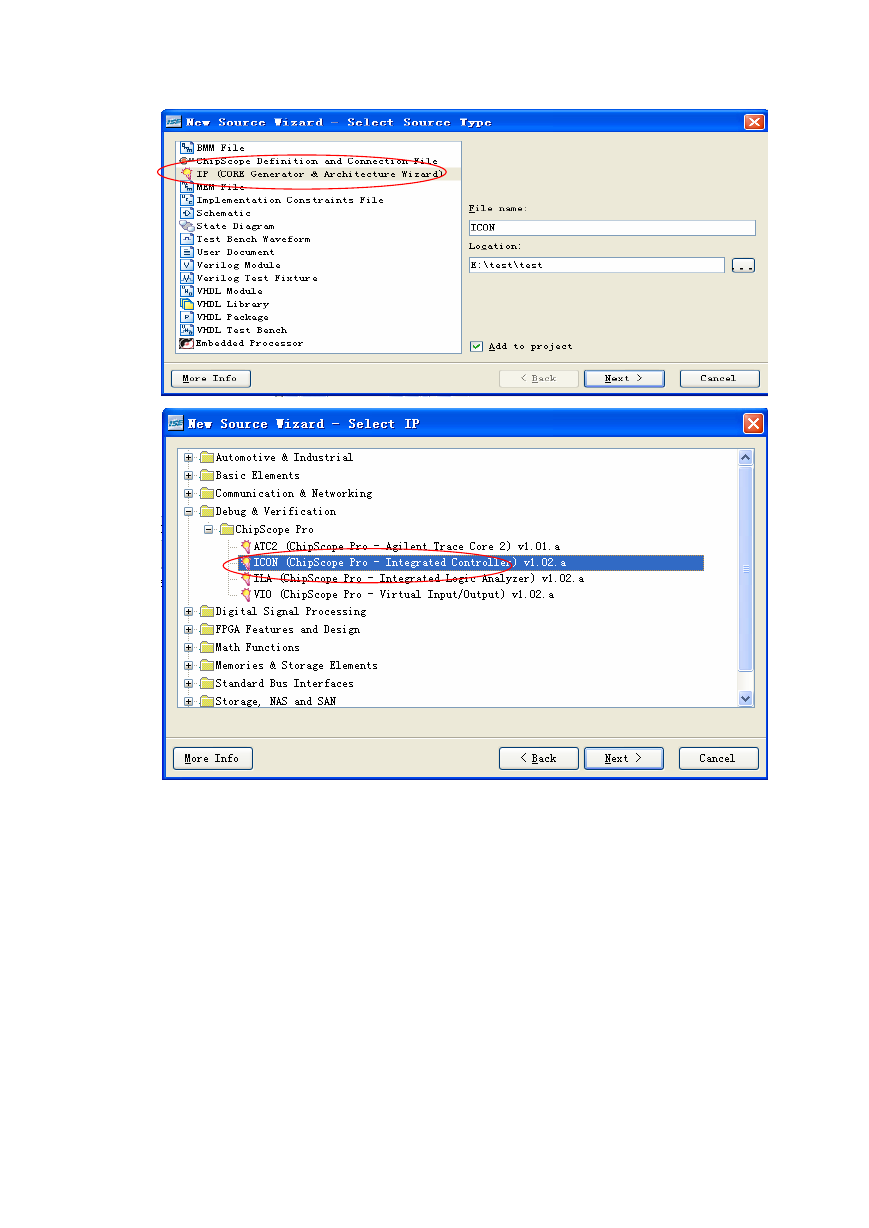

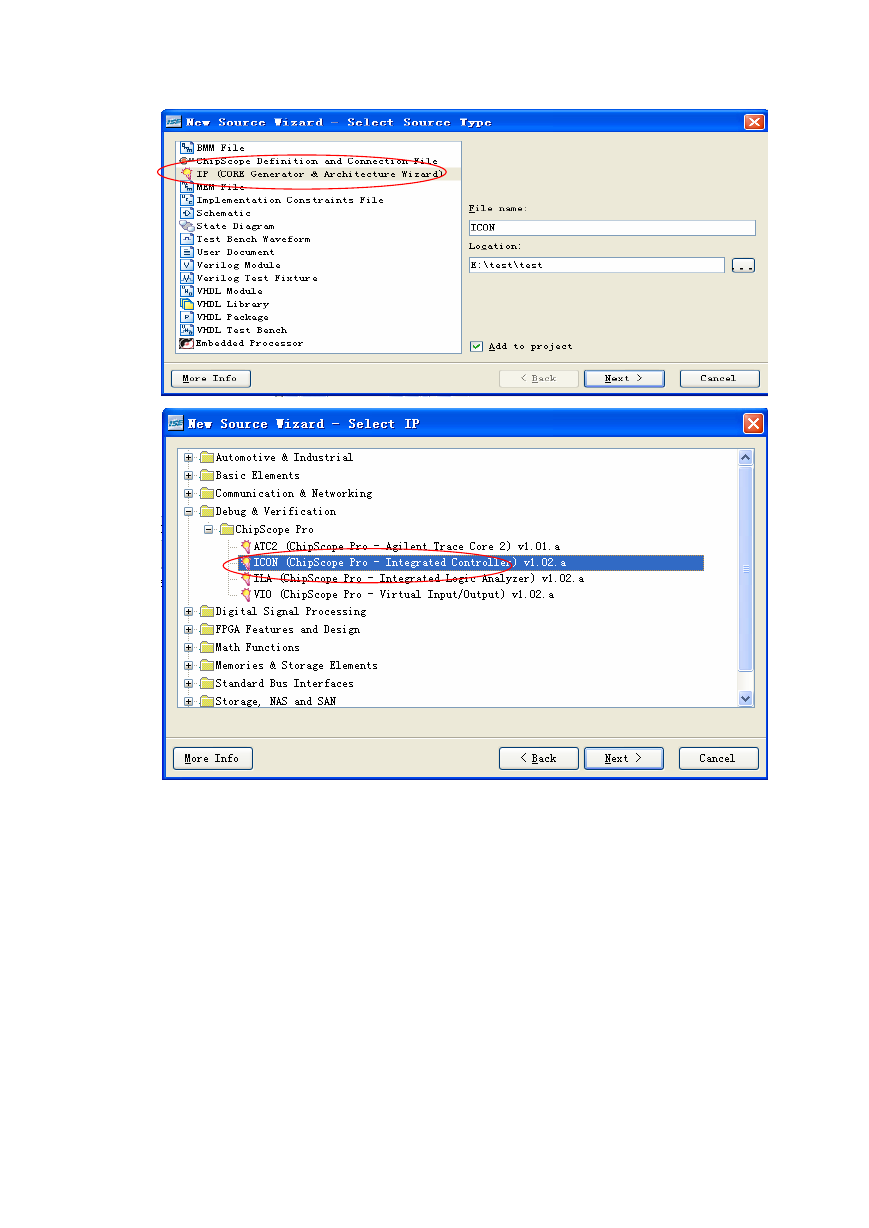

1.创建 ICON 核,创建步骤如下:

�

�

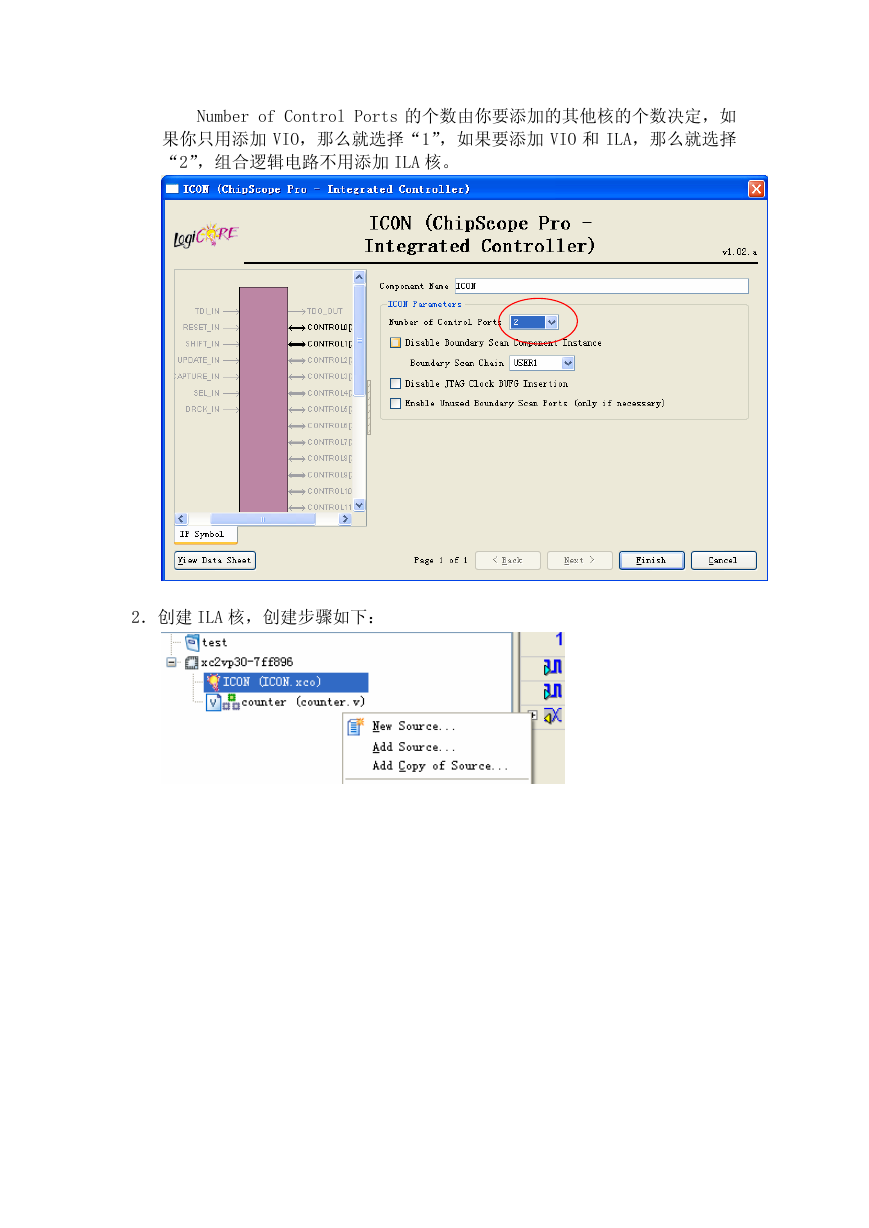

Number of Control Ports 的个数由你要添加的其他核的个数决定,如

果你只用添加 VIO,那么就选择“1”,如果要添加 VIO 和 ILA,那么就选择

“2”,组合逻辑电路不用添加 ILA 核。

2.创建 ILA 核,创建步骤如下:

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc