创新前沿

科技创新与应用

TechnologyInnovationandApplication

2017 年 36 期

基于 FPGA 配置的 AD9361 处理器应用方法研究

周星星,翟继强

(中国飞行试验研究院 改装部,陕西 西安710089 )

法的可行性和 适用性。

摘 要:设计基于 AD9361 的星载通信处理器前期验证系统架构,实现了基于 FPGA 的 AD9361 寄存器配置方法 ,并且通过测试验证了方

关键词:AD9361;星载处理载荷;FPGA 配置

中图分类号院TN927

文献标志码院A

文章编号院2095-2945渊2017冤36-0006-02

1 概述

随着通信卫星的发展,对卫星通信的抗干扰和多用户接

入能力、卫星星上处理能力以及处理算法提出了更高的要求。

为提高产品的市场竞争力,一方面需要提前对处理器协议 和

算法进行充分验证,在保证产品的性能和可靠性的基础上,缩

短研制周期,降低设计风险;另一方面需在较短的时间内对算

法进行更改验证,以满足用户日趋复杂 的需求,降低研发成

本。

现阶段,大多数软件无线电平台利用离 散器件进行搭建,

然而其功耗大,系统成本高,需要设计人员 有很丰富的硬件设

计和射频信号处理经验。目前,星载处理协议变化多样、用户

需求不断更新 ,为了缩短开 发周期,降低设计 成本,传统的软

件无线电设计方案不能 够满足要求 。ADI 公司的 AD9361 集

RF 前端与灵活的混合信 号基带部 分为一体 ,集成频率合成

器,为处理器提供可配置数字接口,简化了设计的 导入。将

AD9361 应用于星载通信处理 有效载荷的设计验证 能够满足

成射频捷变收发器,具有很强的可编程性和宽带能力,器件集

目前设计变化的需求。

收器具有先进的噪声系数和线性度,可实现高调制精度与超

2AD9361 介绍

AD9361 为 10mm伊10mm,144 球芯片级封装,球栅阵列

(CSP_BGA),它是面向 3G 和 4G 基站应用的高性能高集成度

的 射 频(RF)捷 变 收 发 器(AgileTransceiver ),集 成了 12 位

ADC 和 DAC,支持 TDD 和 FDD[1]。其两个独立的直接转换接

低噪 音。每个接 收器(RX)子系统包括独立的自动增益控制

(AGC)、DC 偏移校正、正交校正、数字滤波,从而减轻了数字

基带的负担。AD9361 还具有可以从外部控制的,灵活的手动

增益模式(MGC)。每个通道有两个高动态范围 ADC,可将接

收到的 I 和 Q 信号数字 化,并通过可配置 的抽取滤 波器和

128 抽头有限脉冲响应(FIR)滤波器,产生一个 12 位的输出

信号(采样率可配置)。

主板上的发射(TX)功率监视器可以用 作功率检测器,可

实现高度精确的发射功率测量。其完全集成的锁相环(PLL)可

为所有的接收和发送通道提供低功耗的小数 N 分频合成。

AD9361 的核可以直接从一个 1.3V 稳压器上供电。AD9361 主

要性能参数如表 1 所示。

3 基于 AD9361 的星载处理设备验证方案

将 AD9361 应用在星载处理设备验证中 ,主要是针对卫

星通信协议和算法进行验证[2]。

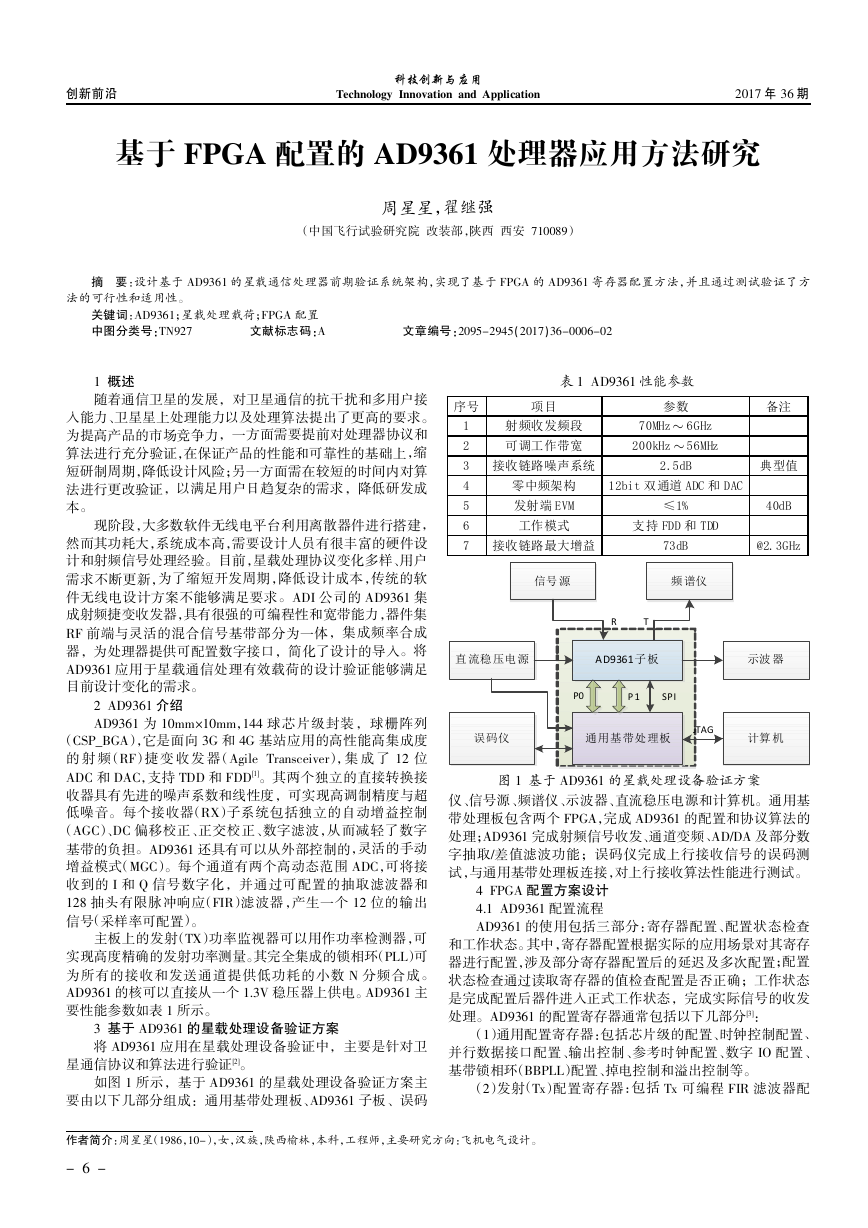

如图 1 所示,基于 AD9361 的星载处理设备验证方案主

要由以下几部分组成:通用基带处理板、AD9361 子板、误码

作者简介:周星星(1986,10-),女,汉族,陕西榆林,本科,工程师,主要研究方向:飞机电气设计。

6-

-

表1AD9361 性能参数

项目

参数

70MHz: 6GHz

200kHz : 56MHz

2.5dB

备注

典型值

序号

1

2

射频收发频段

可调工作带宽

3 接收链路噪声系统

4

5

6

零中频架构

12bit 双通道 ADC 和 DAC

发射端 EVM

工作模式

≤1%

40dB

支持 FDD 和 TDD

7 接收链路 最大增益

73dB

@2.3GHz

信号 源

频 谱仪

R

T

直流稳 压电 源

AD9361 子板

示波 器

P0

P1

SPI

误码仪

通用基带 处理板

JTAG

计算 机

图 1 基于 AD9361 的星载处理设备验证方案

仪、信号源、频谱仪、示波器、直流稳压电源和计算机。通用基

带处理板包含两个 FPGA,完成 AD9361 的配置和协议算法的

处理;AD9361 完成射频信号收发、通道变频、AD/DA 及部分数

字抽取/差值滤波功能 ;误码仪完成 上行 接收信 号的 误码 测

试,与通用基带处理板连接,对上行接收算法性能进行测试。

4FPGA 配置方案设计

4.1AD9361 配置流程

AD9361 的使用包括三部分:寄存器配置、配置状态检查

和工作状态。其中,寄存器配置根据实际的应用场景对其寄存

器进行配置,涉及部分寄存器配置后的延迟及多次配置;配置

状态检查通过读取寄存器的值检查配置是否正确;工作状态

是完成配置后器件进入正式工作状态,完成实际信号的收发

处理。AD9361 的配置寄存器通常包括以下几部分[3]:

(1)通用配置寄存器:包括芯片级的配 置、时钟控制配置、

并行数据接口配置、输 出控制、参考时 钟配置、数 字 IO 配置、

基带锁相环(BBPLL)配置、掉电控制和溢出控制等。

(2)发射(Tx)配置寄存器:包括 Tx 可编程 FIR 滤波器配

�

科技创新与应用

TechnologyInnovationandApplication

创新前沿

2017 年 36 期

置、Tx 监控寄存器、Tx 功率和衰减控制、Tx 正交校准配置、Tx

DAC 寄存器、Tx 基带滤波器 BBF 配置等。

(3)接收(Rx)配置寄存器:包括 Rx 可编程 FIR 滤波器配

置、增益控制通用配置、外部 LNA 增益设置、AGC 增益表设

置、通用校准寄存器、接收 信号强 度指 示 RSSI 配置、Rx 正交

校准配置、LNA 寄存器配置、TIA 寄存器配置、BBF 寄存器配

置和 ADC 寄存器配置。

(4)模拟配置寄存器:包括 Rx 频率综合器配置 、Rx 本振

通用配置 、Tx 频 率综合器 配置 、DCXO 配 置、Tx 本振通 用配

置、数字测试寄存器和 DAC 测试寄存器配置等。

实际配置时,根据需求对涉及到的寄存器进行配置,其余

寄存器使用默认值即可。整个寄存器的配置通常分为以下几

4.2 方案设计

个部分,具体见表 2。

表 2 寄存器配置状态划分

配置内容

状态完成标志

图2 配置完成状态

配置是否正确。

另外还 可以 通过 chipscope 对寄存器进行读取 从而验 证

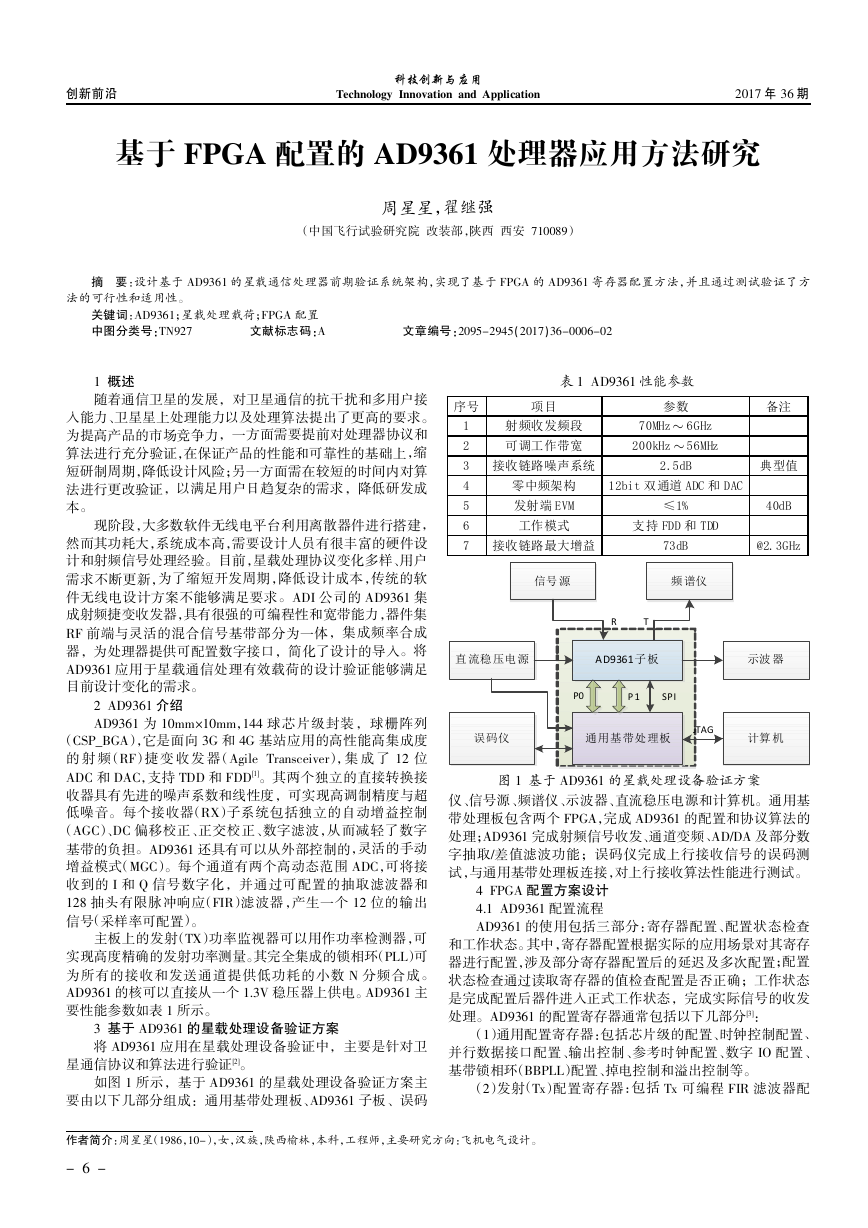

5 测试结果

测试 配 置 参数 :AD9361 内 部 40MHz 参 考 、 接 收 本 振

2.1GHz、发射本振 1.9GHz、发射信号 2.10098GHz、数字输出采

样率 30Msps、DDR 输出、FDD 工作模式、AGC 工作模式。按照

试时FPGA 只完成数字信号的转发,不对信号做再生处理。实

际应用还需要完成本振泄漏抑制 和 IQ 不平衡校准算法、信号

再生处理及上行误码测试等 功能。图 3 为单音环回测试的结

以上参数完成寄存器配置,通过对单音信号进行环回测试。测

果。

序号

配置

状态

1 S0

2 S1

3 S2

芯片级、时钟控制、

并行数据接口配置

掉电和溢出控制、

基带锁相环配置

Rx 和 Tx 的可编程

FIR 滤波器配置

4 S3

Rx RFPLL 校准

5 S4

Tx RFPLL 校准

Wait 20ms

Wait for BBPLL to lock

Wait 1ms

Wait for Rx RFPLL cp

cal to complete

Wait for Tx RFPLL cp

cal to complete

6 S5

7 S6

Rx 与 Tx 频率综合

Wait for Rx and Tx

器配置

RFPLL to lock

增益控制、Rx BBF

寄存器配置

Wait for Rx BBF to tune

8 S7 Tx BBF

寄存器配置 Wait for Tx BBF to tune

9 S8

Rx TIA 寄存器配置、

Wait for BB DC cal to

ADC 寄存器配置

complete

10 S9 Rx

射频 DC 寄存器配置

Wait for RF DC cal to

complete

11 S10

12 S11

Tx 功率和衰减控制、

Wait for Tx Quad cal to

Tx 正交校准配置

complete

Rx 正交校准配置

Wait for Rx Quad cal to

complete

此外,S12 状态为读状态,当所有寄存器都正 确配置完成

之后,进入S12 状态,并且一直处于此 状态,直到读状态 指示

read_int=0 为止。

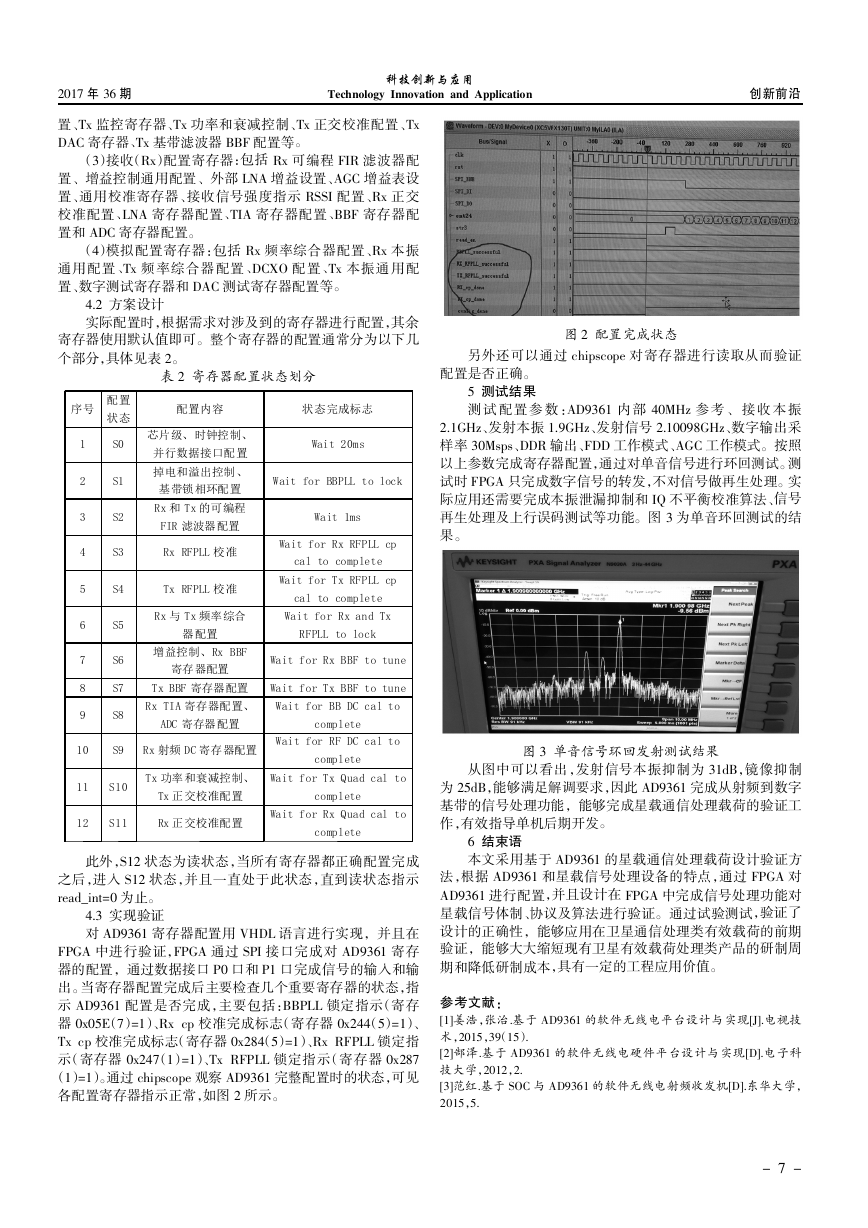

4.3 实现验证

对 AD9361 寄存器配置用 VHDL 语言进行实现,并且在

FPGA 中进行验证,FPGA 通过 SPI 接口完成对 AD9361 寄存

器的配置,通过数据接口P0 口和P1 口完成信号的输入和输

示 AD9361 配置是否完 成,主要包括:BBPLL 锁定指示(寄存

器 0x05E(7)=1)、Rxcp 校准完成标志(寄存器 0x244(5)=1)、

Txcp 校准完成标志(寄存器 0x284(5)=1)、RxRFPLL 锁定指

示(寄存器 0x247(1)=1)、TxRFPLL 锁定指示(寄存器 0x287

(1)=1)。通过 chipscope 观察 AD9361 完整配置时的状态,可见

各配置寄存器指示正常,如图 2 所示。

出。当寄存器配置完成后主要检查几个重要寄存器的状态,指

图 3 单音信号环回发射测试结果

从图中可以 看出 ,发射 信号本 振抑制为 31dB,镜像抑制

为 25dB,能够满足解调要求,因此 AD9361 完成从射频到数字

基带的信号处理功能,能够完成星载通信处理 载荷的验证工

作,有效指导单机后期开发。

6 结束语

本文采用基于 AD9361 的星载通信处理载荷设计验证方

法,根据 AD9361 和星载信号处理设备的特点,通过 FPGA 对

AD9361 进行配置,并且设计在 FPGA 中完成信号处理功能对

星载信号体制、协议及算法进行验证。通过试验测试,验证了

设计的正确性,能够应用在卫星通信处理 类有效载荷的前期

验证,能够大大缩短现有卫星有效载荷处理类产品的研制周

期和降低研制成本,具有一定的工程应用 价值。

参考文献院

[1]姜浩,张治.基于 AD9361 的软件无线电平台设计与 实现[J].电视技

术,2015,39(15).

[2]郜泽.基于 AD9361 的软件无线电硬件 平台设 计与实现[D].电子科

技大学,2012,2.

[3]范红.基于 SOC 与 AD9361 的软件无线电射频收发机[D].东华大学,

2015,5.

7-

-

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc