CADENCE

CADENCE

CADENCE

VIRTUSO/DIVA/DRACULA

芯片版图设计工具 VIRTUSO/DIVA/DRACULA

VIRTUSO/DIVA/DRACULA

入门手册...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

222

1、使用 VIRTUSO/ DIVA/DRACULA 之前的准备.................................................................................2

1.1、要找一台装有工具IC的计算机.........................................................................................2

1.2、要能连接到该计算机上.......................................................................................................2

2、工具 IC 的软件环境配置............................................................................................................... 3

2.1、创建工具IC的启动目录,即工作目录。.........................................................................3

2.3、将(.cdsinit和.cdsenv)拷贝到工具IC的启动目录..............................................................3

2.4、在工作目录下创建工艺库文件...........................................................................................3

2.5、启动工具IC,命令为icfb&...................................................................................................3

2.6、配置工艺库路径...................................................................................................................3

2.7、添加工艺提供的一些辅助库...............................................................................................4

2.8、添加MultipartPath..............................................................................................................5

2.9、安装PCELL..........................................................................................................................5

3、 开始一个新的设计---编辑电路图与版图................................................................................... 5

3.1、 新建一个设计库.................................................................................................................5

3.2、Attach库................................................................................................................................6

3.3、创建新设计...........................................................................................................................6

3.4、编辑电路图...........................................................................................................................7

3.5 编辑版图.................................................................................................................................8

3.6 可以根据习惯改变版图的层次显示特性.............................................................................9

3.7、完成版图编辑之后先保存再退出.....................................................................................10

4 版图的 DRC 检查...........................................................................................................................10

4.1、基于Diva的方式...............................................................................................................10

4.2、基于Dracula的方式..........................................................................................................10

5 、LVS.............................................................................................................................................. 12

5.1、准备版图的GDS文件.......................................................................................................12

5.2、准备电路网表.....................................................................................................................12

5.3、用LOGLVS转换电路网表成LVS要求格式....................................................................13

5.4、修改lvs的命令文件...........................................................................................................13

5.6、运行dracula来生成lvs任务的可执行文件....................................................................14

5.7、在控制台下,运行jxrun.com文件...................................................................................14

5.8、查看错误.............................................................................................................................14

5.9、修改.....................................................................................................................................14

6、PAD 相关.......................................................................................................................................14

6.1、准备pad库.........................................................................................................................15

6.2、导入pad版图的GDS文件...............................................................................................15

6.3、更新gds和cdl....................................................................................................................15

6.4、修改cdl...............................................................................................................................16

7、一些小经验................................................................................................................................... 16

8、附件清单....................................................................................................................................... 17

9、后记............................................................................................................................................... 17

�

adence

adence

adence

CCC

Virtuso/Diva/Dracula

Virtuso/Diva/Dracula

Virtuso/Diva/Dracula

芯 片 版 图 设 计 工 具

入门手册

(以上华 0.6um DPDM 工艺设计库为例)

Cadence 是一套功能强大的 EDA 软件,包含有诸如 IC、SE 等常用芯片设计工具。其

中 IC 是针对全定制芯片设计应用的。IC 本身仍是一套工具集。该手册主要讨论其中的全定

制版图设计工具 Virtuso/ Diva/Dracula 之使用方法。Diva 和 Dracula 用于版图检查及验证

,其中前者是基于 Xwindow 的方式,而后者是基于命令行的方式;Virtuso 中提供这两者的

相关接口。

采用 Virtuso/ Diva/Dracula 设计 芯片 大致 有如 下几 步: 准备 schmematic( 电路)、画

layout(版图)、作版图设计规则检查(DRC)、做电路与版图的一致性检查(LVS)和导出最终

版图的 gds 文件。

111

、使用、使用、使用

Virtuso/

Virtuso/

Virtuso/

Diva/Dracula

Diva/Dracula

Diva/Dracula

之前的准备

之前的准备

之前的准备

111

.111

、要找一台装有工具 ICICIC

的计算机

Virtuso 不能单独安装,所以只有在安装了 IC 的计算机上才能使用。

[[[

例]]]

用 Virtuso/Dracula.

eda 机房的 eda16 服务器 IC(ip:166.111.64.105)和 eda17(ip:166.111.64.106)都能使

111

.222

、要能连接到该计算机上

除非是在自己的计算机上安装有工具 IC,否则您必须保证能够从您的计算机远程登

录到装有工具 IC 的计算机上。

[[[

例]]]

a、向管理员申请用户

b、下载远程登录软件 Exceed,

以登录服务器 IC 来说明远程登录方法:

在本地计算机上安装;

远程登录配置:

在 开 始 菜 单 程 序 Hummingbird.Exceed.v7.1.MultilanguageExceedClient

Wizard 设定 xterm,Host:166.111.64.105,Host type: SUN(下拉菜单选择),其余

next 即可。

还可以采用 vnc 或 SSH Secure Shell Client 等远程终端方法登录。

c、完成登录。

『注意』也可使用其他的远程登陆软件连接服务器;不同的服务器所需的软件设置

均有所不同,配置细节请咨询曾经使用过该服务器的师兄师姐。

�

222

、工具、工具、工具

ICICIC

的软件环境配置

的软件环境配置

的软件环境配置

222

.111

、创建工具 ICICIC

的启动目录,即工作目录。

[[[

例]]]

:mkdir project↙

222

.333

(.cdsinit)

、将(.cdsinit)

(.cdsinit)

拷贝到工具 ICICIC

的启动目录

将 IC 工具中自带的.cdsinit 文件拷贝过来

1. 执行命令

instdir↙

得到 IC 的安装目录

eda16 中得到的目录为

/net/eda450/disk1/cadence/IC5.0/tools.sun4v/dfII

.cdsinit 文件在 上面得到目录下的 cdsuser 目录中将其 copy 到自己的根目

录下(例如:

cd /net/eda450/disk1/cadence/IC5.0/tools.sun4v/dfII↙

cp ./cdsuser/.cdsinit ~/

/home/ldm0345)

2.

这样,在原理图和版图界面中就可以使用快捷键了

222

.444

(techfile.tf)

、将库文件(techfile.tf)

(techfile.tf)

(display.drf)

及显示初始化文件(display.drf)

(display.drf)

拷

贝至工作目录

通过 FTP 上传(用户名和密码为 dea 机房的帐号和密码)

上传到目录: ~/project 中

222

.555

、启动工具 IC,IC,IC,

命令为 icfb&icfb&icfb&

[[[

例]]]

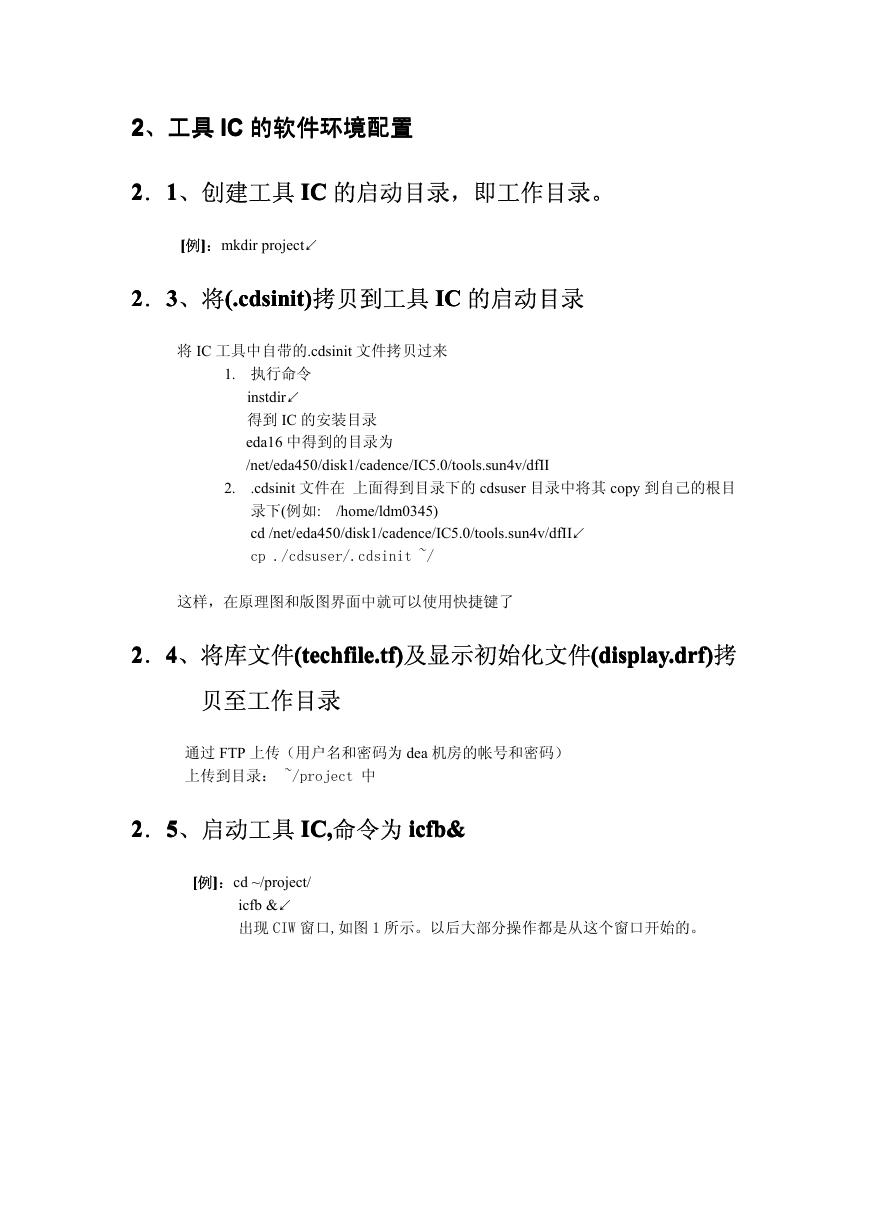

:cd ~/project/

icfb &↙

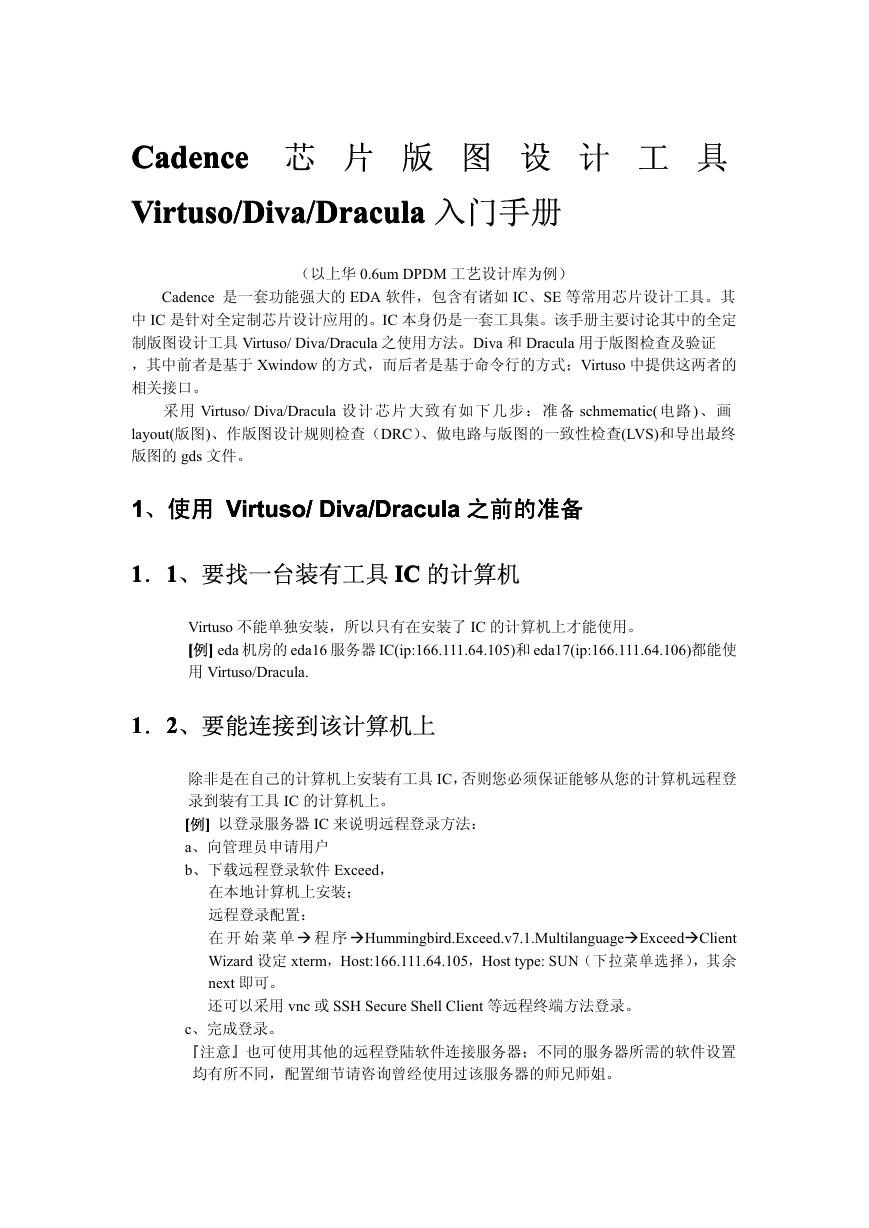

出现 CIW 窗口,如图 1 所示。以后大部分操作都是从这个窗口开始的。

�

图 1 CIW 窗口

222

.666

、配置工艺库路径

在 Library Path Editor 中指定工艺库路径。该步的操作结果将保存到工作目录

下的 cds.lib 文件中。

『注意 1』:所有的库或其他任何一个设计目录要被 4)所启动的 CIW 所使用,都必

须使用前先在工作目录下的 cds.lib 文件作定义,指明其引用名称(在 cadence

环境中的标识名)及绝对路径。

『注意 2』为了能使用 Cadence 自带的一些库(如画电路图时的 Basic symbols),

需 要 在 cds.lib 文 件 的 开 头 部 分 添 加 “INCLUDE

< 工 具 IC 的 安 装 目 录

>/share/cdssetup/cds.lib” . 在命令行中输入 instdir 可查看工具 IC 的可执行程序所

在 目 录 。 [[[

可 得 到 :

/usr/cadence/ic5033/tools.lnx86/dfII

3/3/3/

,,,

/usr/cadence/ic5033/tools.lnx86/dfII

/usr/cadence/ic5033/tools.lnx86/dfII

需要添加的内容为”””

/usr/cadence/ic503

的安装目录为/usr/cadence/ic503

/usr/cadence/ic503

instdir

上 命 令 行 模 式 输 入 instdir

instdir

/usr/cadence/ic5033/

/usr/cadence/ic5033/

/usr/cadence/ic5033/

share/cdssetup/cds.lib

”””

share/cdssetup/cds.lib

share/cdssetup/cds.lib

例 ]]]

ic_linux

在 线 路 组 ic_linux

ic_linux

,则工具 ICICIC

INCLUDE

INCLUDE

INCLUDE

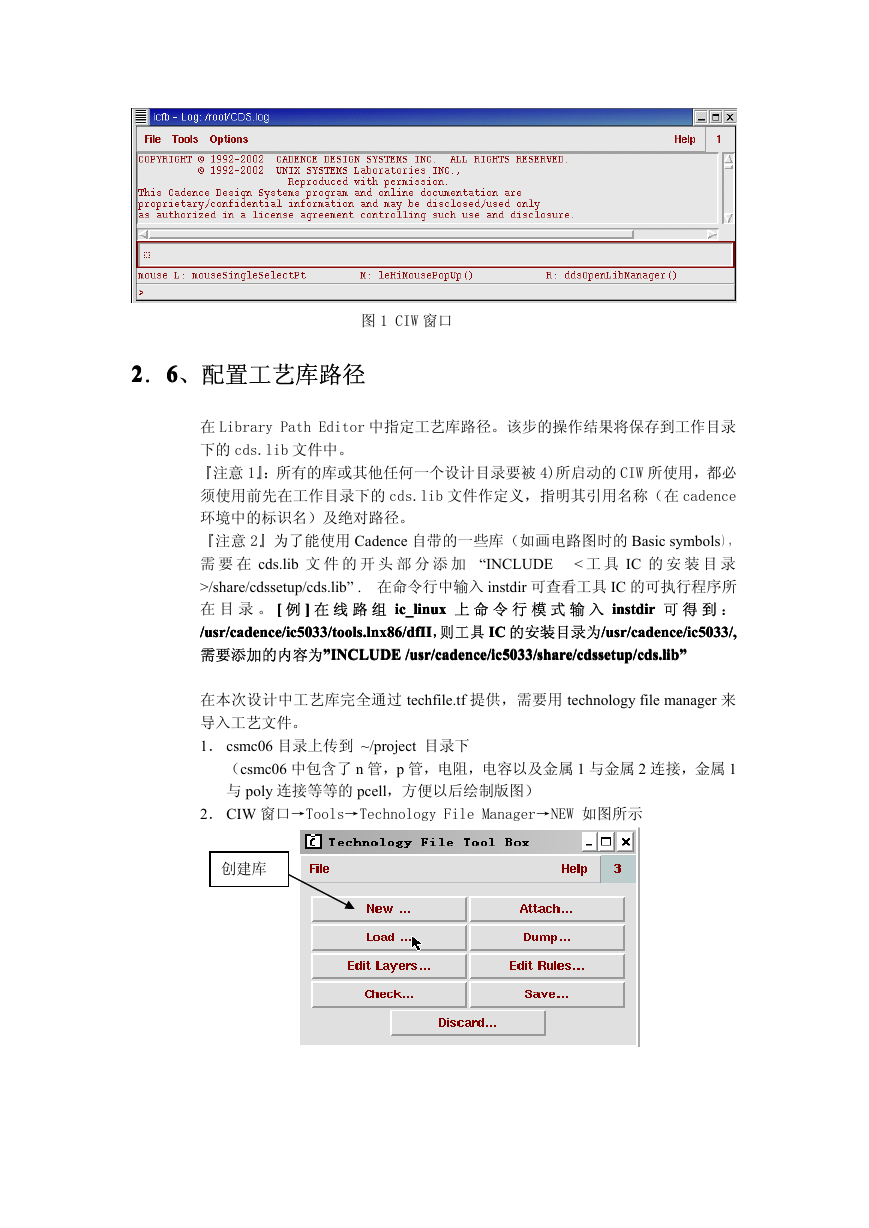

在本次设计中工艺库完全通过 techfile.tf 提供,需要用 technology file manager 来

导入工艺文件。

1. csmc06 目录上传到 ~/project 目录下

(csmc06 中包含了 n 管,p 管,电阻,电容以及金属 1 与金属 2 连接,金属 1

与 poly 连接等等的 pcell,方便以后绘制版图)

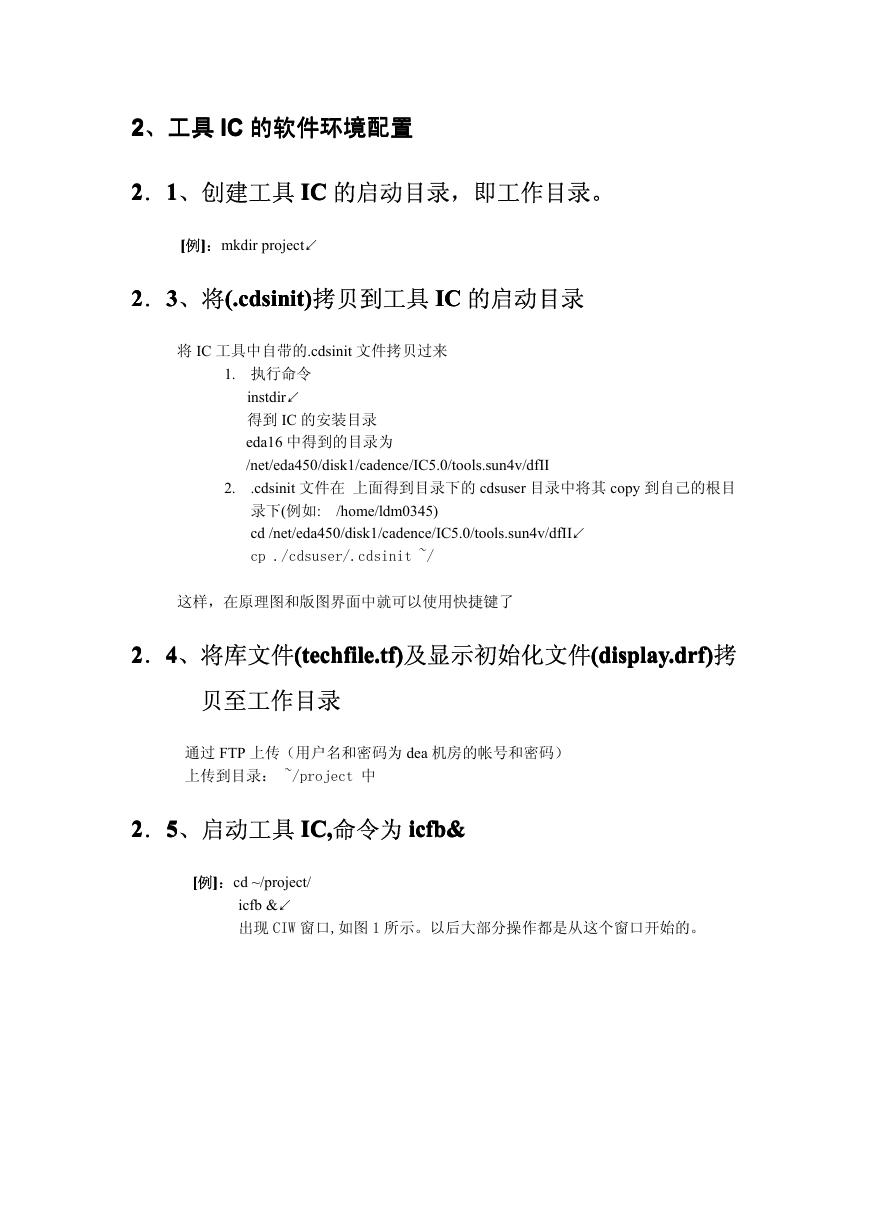

2. CIW 窗口→Tools→Technology File Manager→NEW 如图所示

创建库

�

在 Technology Library Name 中输入工艺库的名字, csmc06;在 Load ASCII

Technology File 中输入 techfile.tf 单击 OK,程序会将 techfile.tf 中的数据

导入至文件夹 csmc06 中。此时用 Library Path Editor 可以查看到刚才添加的库

文件。

如果还有其他的库文件,则在 technology file tool box 中选择 LOAD

在 ASCII Technology File 输入框 输入包含*.tf 的文件名(如 devices.tf)

在 Classes 多选项里,根据*.tf 中提供的内容以及期望导入的内容决定。

在 Technology Library 多选一框里,选择对应的库。

在多选一框下方,有 Merge Replace 二选一,选 Merge 则新导入的*.tf 库是补

充原有的库;选 Replace 则新导入的*.tf 将覆盖对应库的原有内容.

点击 OK 按钮 3、 开始一个新的设计---编辑电路图与版图

333

.111

、 新建一个设计库

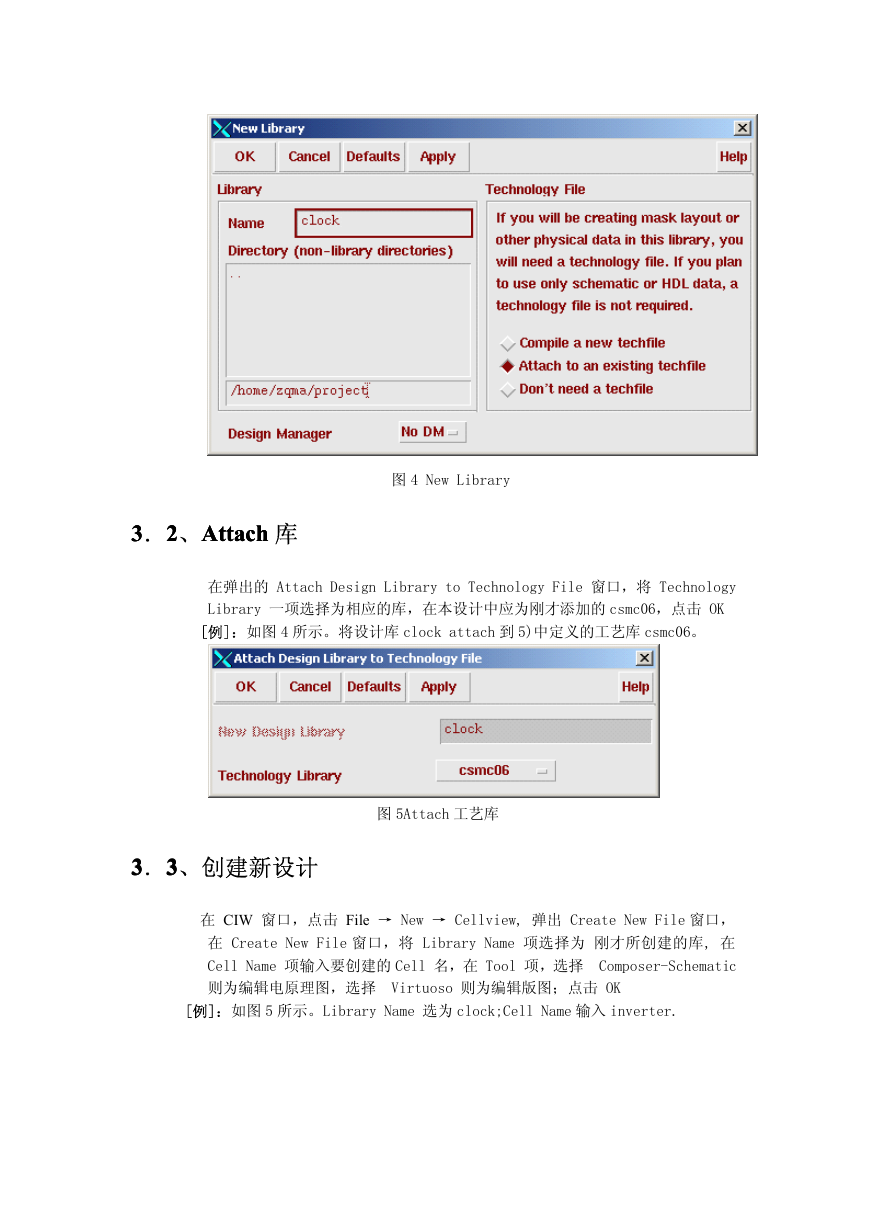

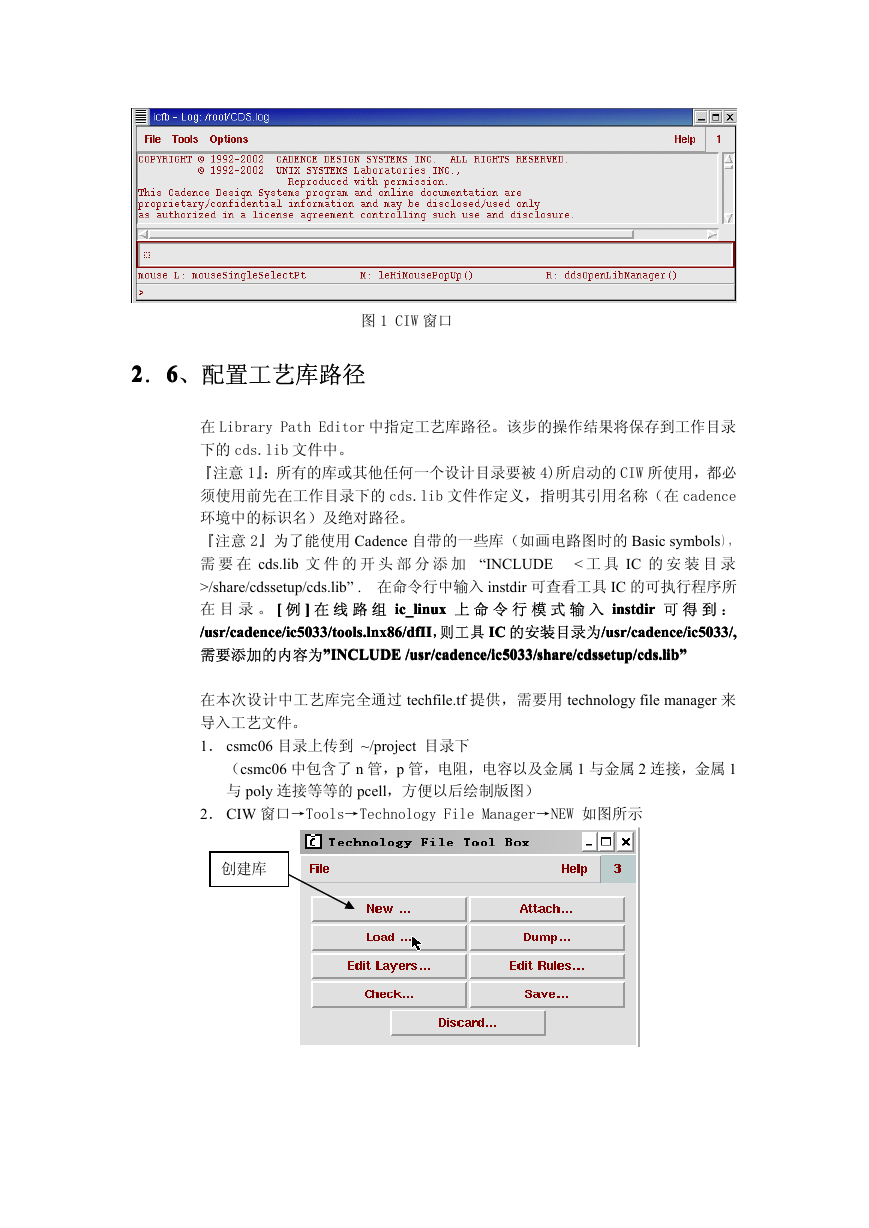

在 CIW 窗口,点击 File → New → Library 弹出 New Library 窗口. 在 Name

输入框中输入设计库名字,在右边 Technology File 处选择 Attach to an

existing techfile。点击 OK。 一般每个芯片设计都采用一个对应的设计库。然

后在这个设计库下面创建各个子模块。

[例]: 如图所示,创建 clock 设计库。

�

图 4 New Library

333

.222

Attach

、Attach

Attach

库

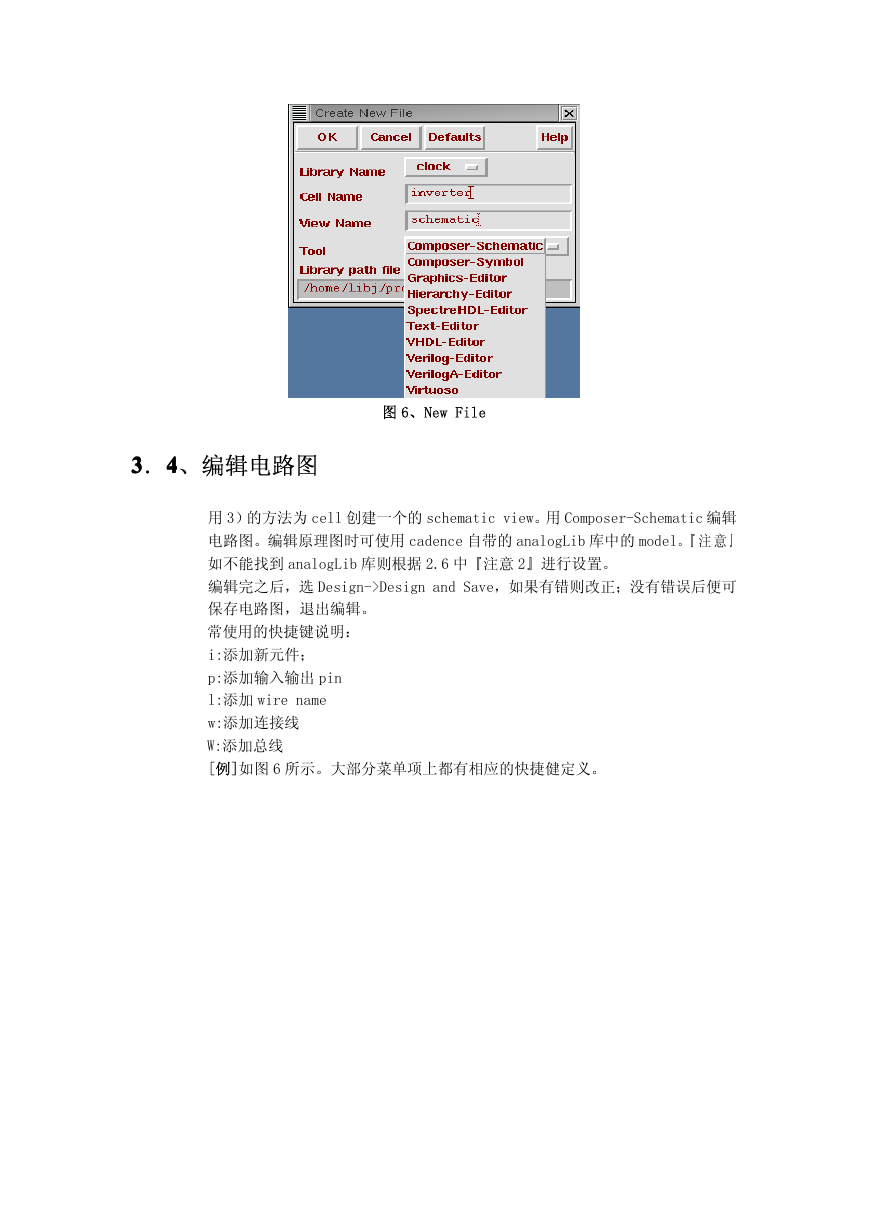

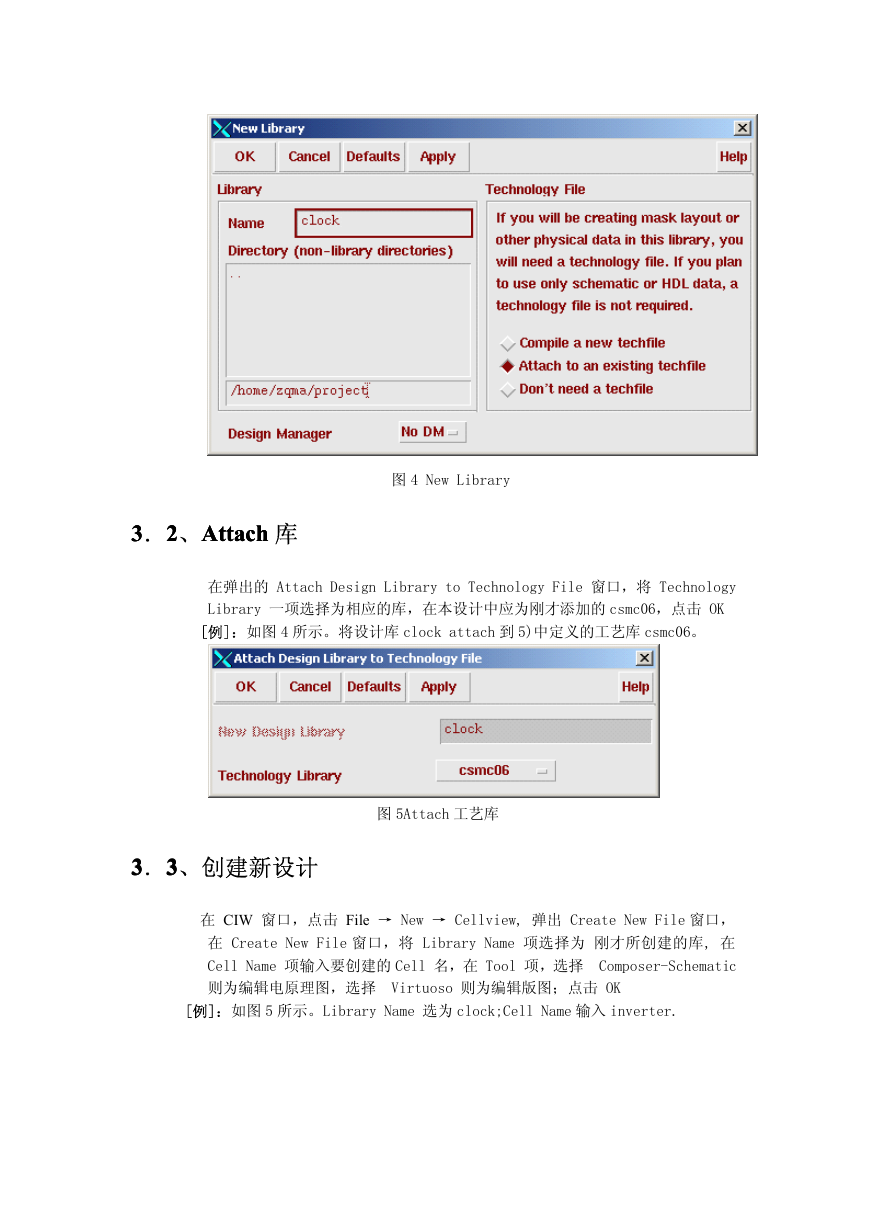

在弹出的 Attach Design Library to Technology File 窗口,将 Technology

Library 一项选择为相应的库,在本设计中应为刚才添加的 csmc06,点击 OK

[例]:如图 4 所示。将设计库 clock attach 到 5)中定义的工艺库 csmc06。

图 5Attach 工艺库

333

.333

、创建新设计

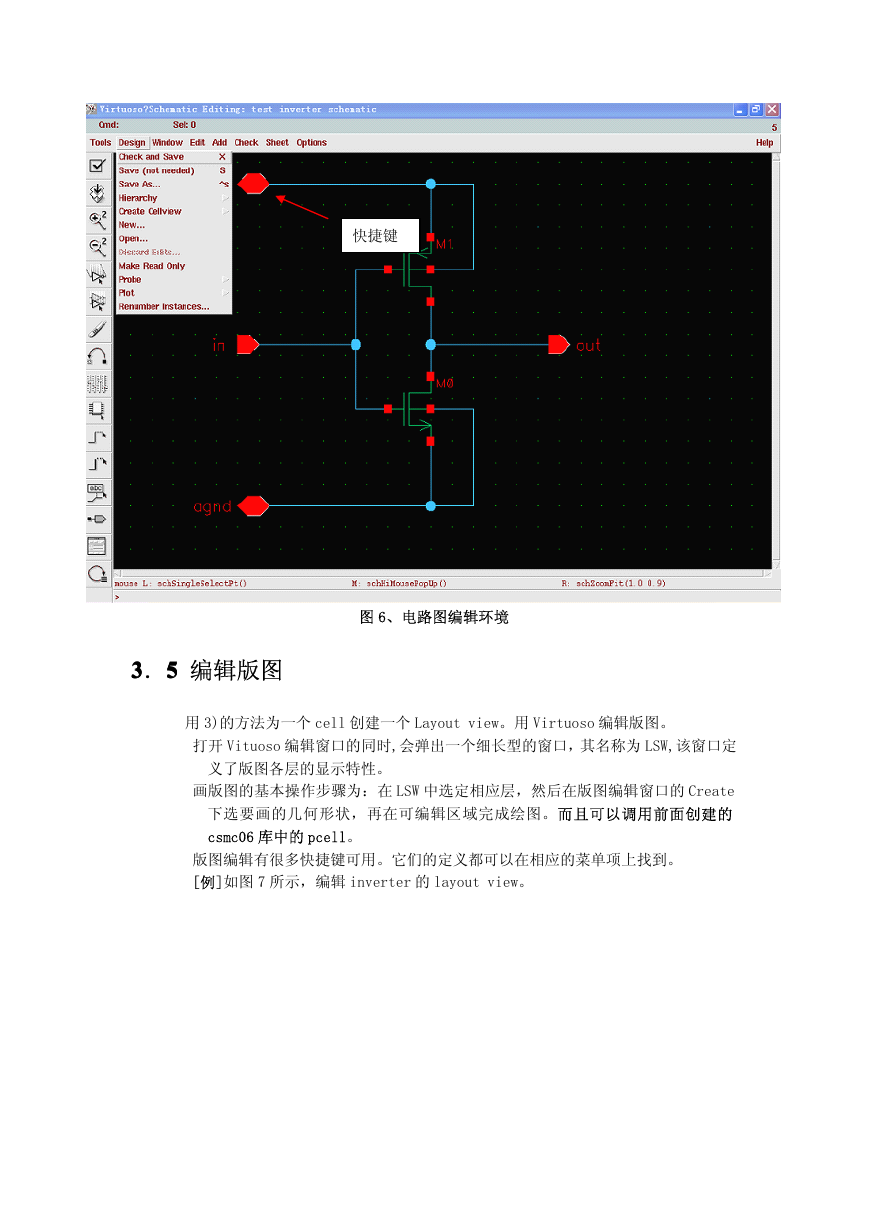

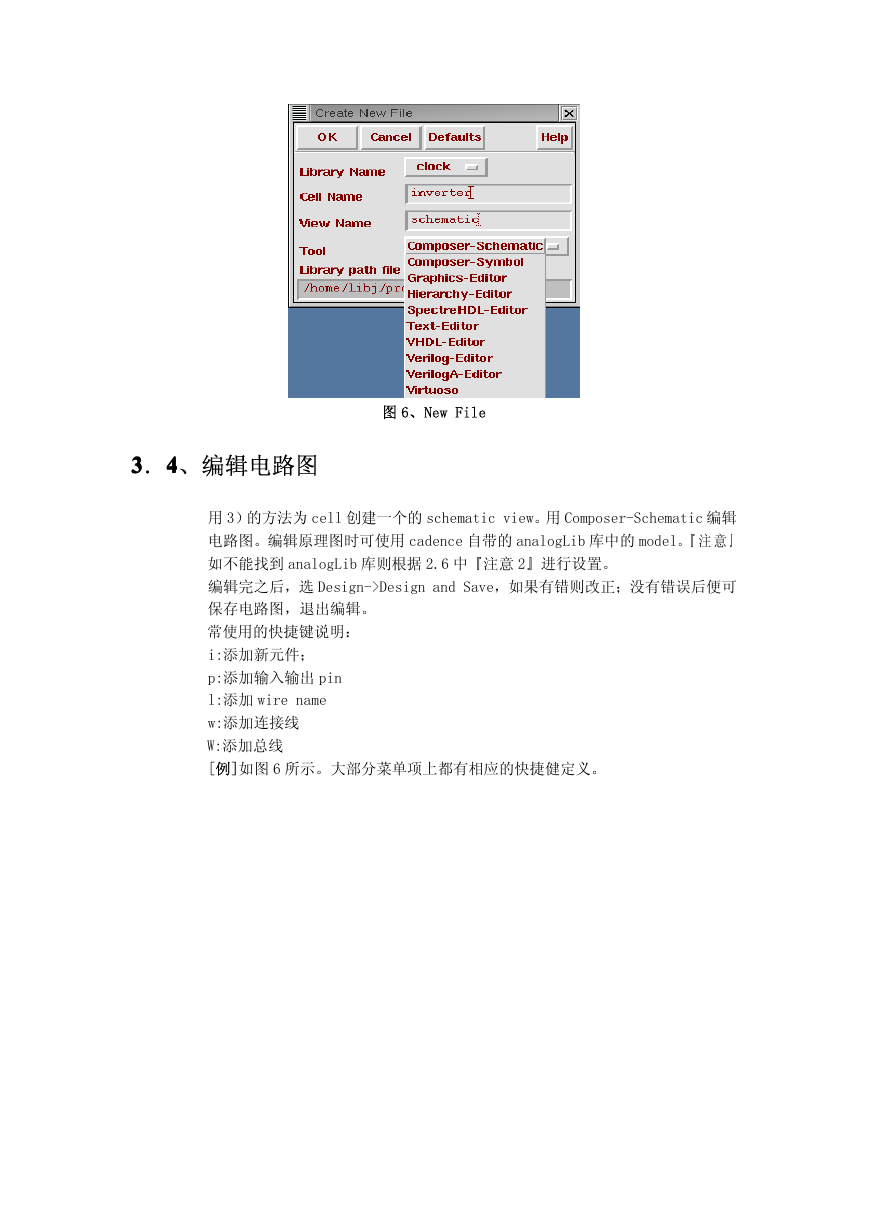

在 CIW 窗口,点击 File → New → Cellview, 弹出 Create New File 窗口,

在 Create New File 窗口,将 Library Name 项选择为 刚才所创建的库, 在

Cell Name 项输入要创建的 Cell 名,在 Tool 项,选择 Composer-Schematic

则为编辑电原理图,选择 Virtuoso 则为编辑版图;点击 OK

[例]:如图 5 所示。Library Name 选为 clock;Cell Name 输入 inverter.

�

图 6、New File

333

.444

、编辑电路图

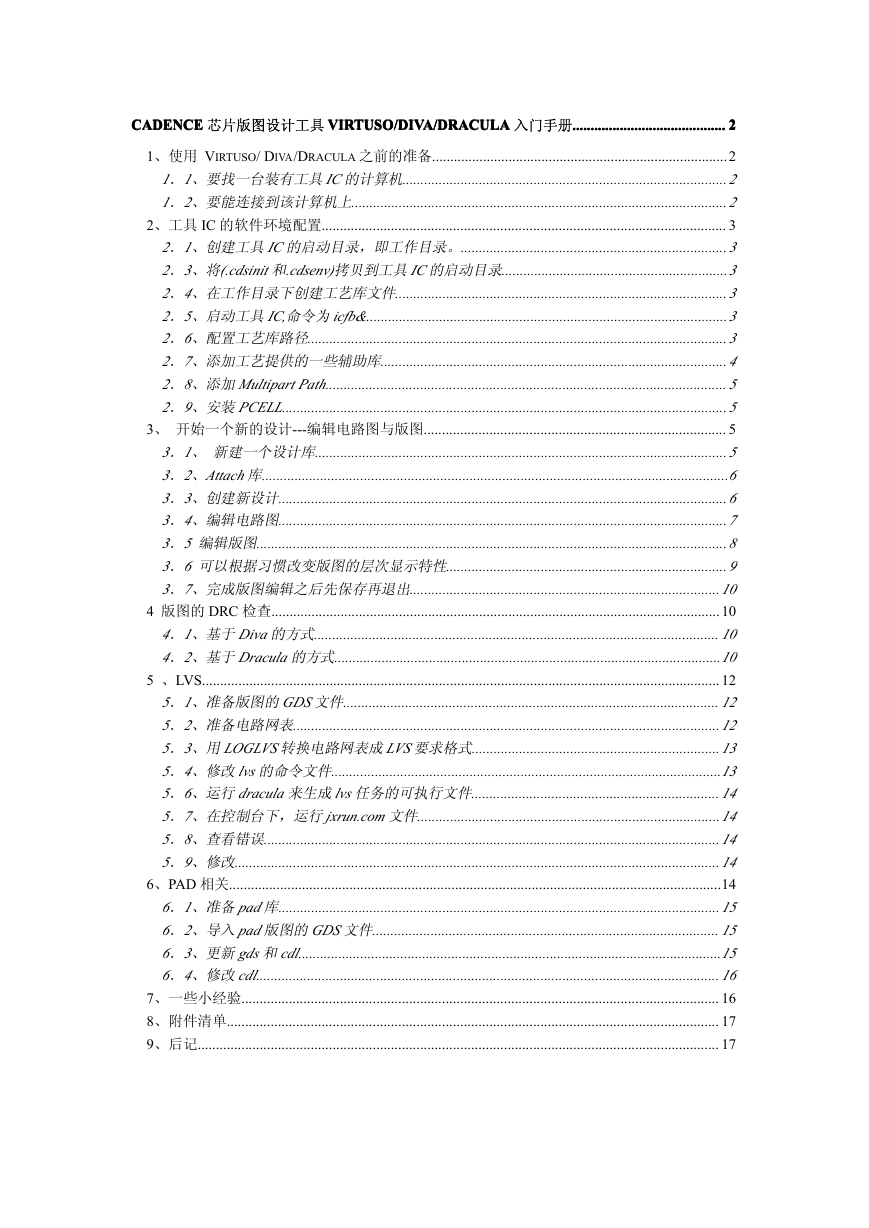

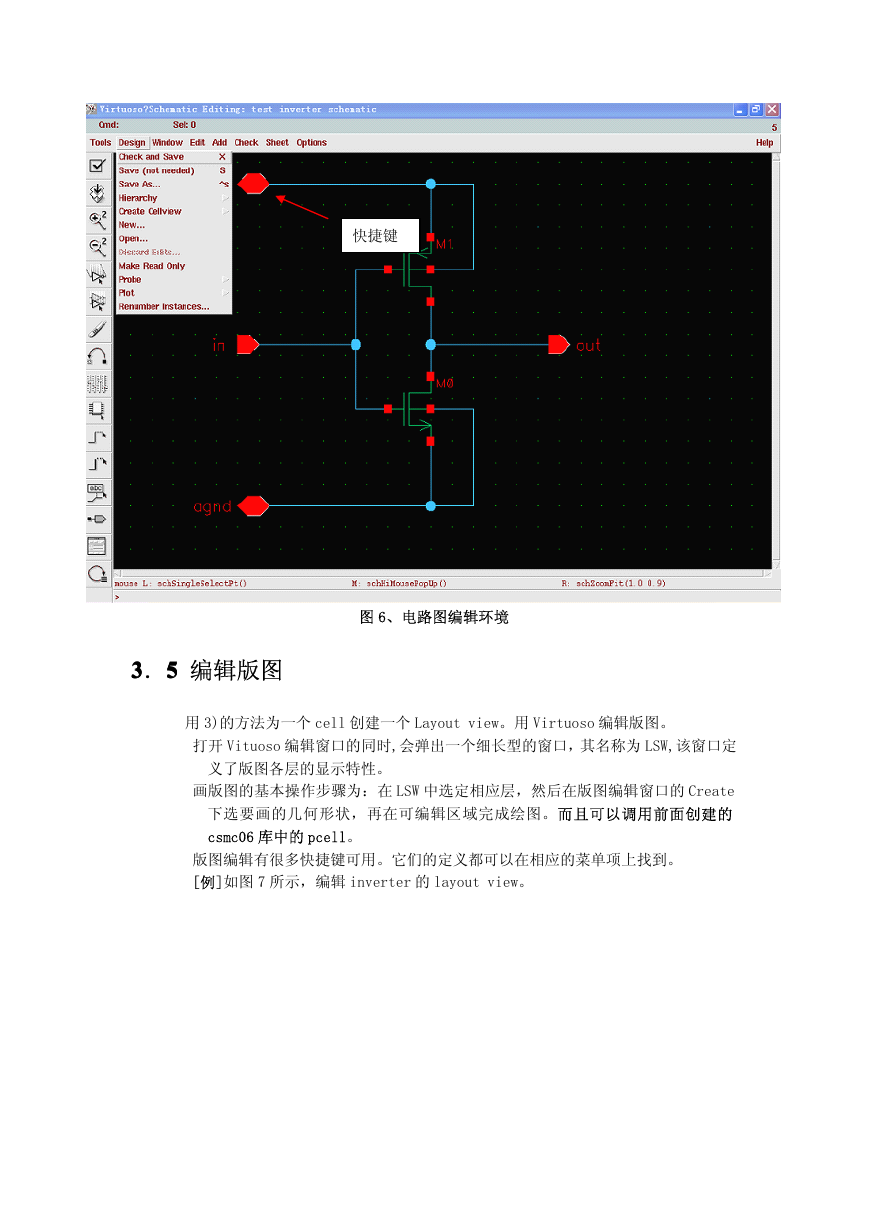

用 3)的方法为 cell 创建一个的 schematic view。用 Composer-Schematic 编辑

电路图。编辑原理图时可使用 cadence 自带的 analogLib 库中的 model。『 注 意 』

如不能找到 analogLib 库则根据 2.6 中『注意 2』进行设置。

编辑完之后,选 Design->Design and Save,如果有错则改正;没有错误后便可

保存电路图,退出编辑。

常使用的快捷键说明:

i:添加新元件;

p:添加输入输出 pin

l:添加 wire name

w:添加连接线

W:添加总线

[例]如图 6 所示。大部分菜单项上都有相应的快捷健定义。

�

快捷键

图 6、电路图编辑环境

333

.555

编辑版图

用 3)的方法为一个 cell 创建一个 Layout view。用 Virtuoso 编辑版图。

打开 Vituoso 编辑窗口的同时,会弹出一个细长型的窗口,其名称为 LSW,该窗口定

义了版图各层的显示特性。

画版图的基本操作步骤为:在 LSW 中选定相应层,然后在版图编辑窗口的 Create

下选要画的几何形状,再在可编辑区域完成绘图。而且可以调用前面创建的

csmc06 库中的 pcell。

版图编辑有很多快捷键可用。它们的定义都可以在相应的菜单项上找到。

[例]如图 7 所示,编辑 inverter 的 layout view。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc