Vivado Design Suite: AXI Reference Guide

Revision History

Table of Contents

Ch. 1: Introducing AXI for Vivado

Overview

What is AXI?

Summary of AXI4 Benefits

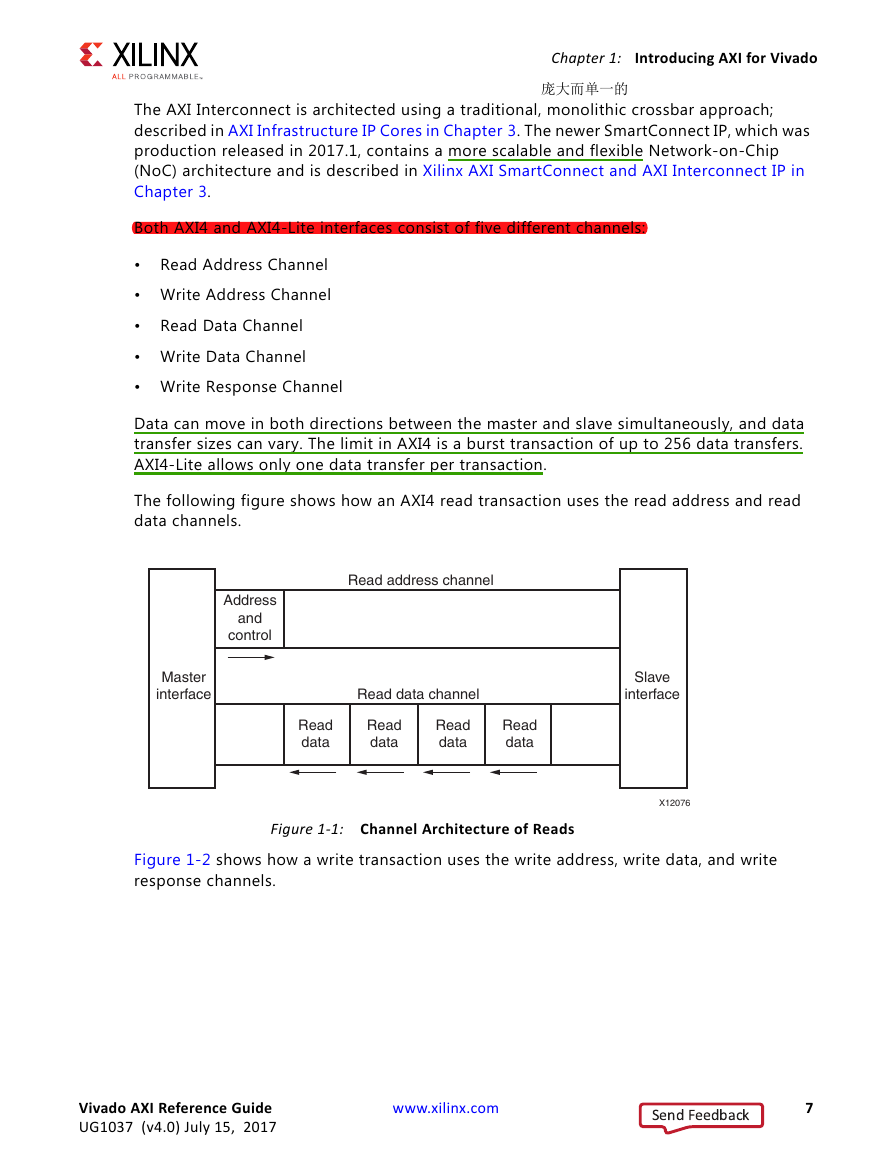

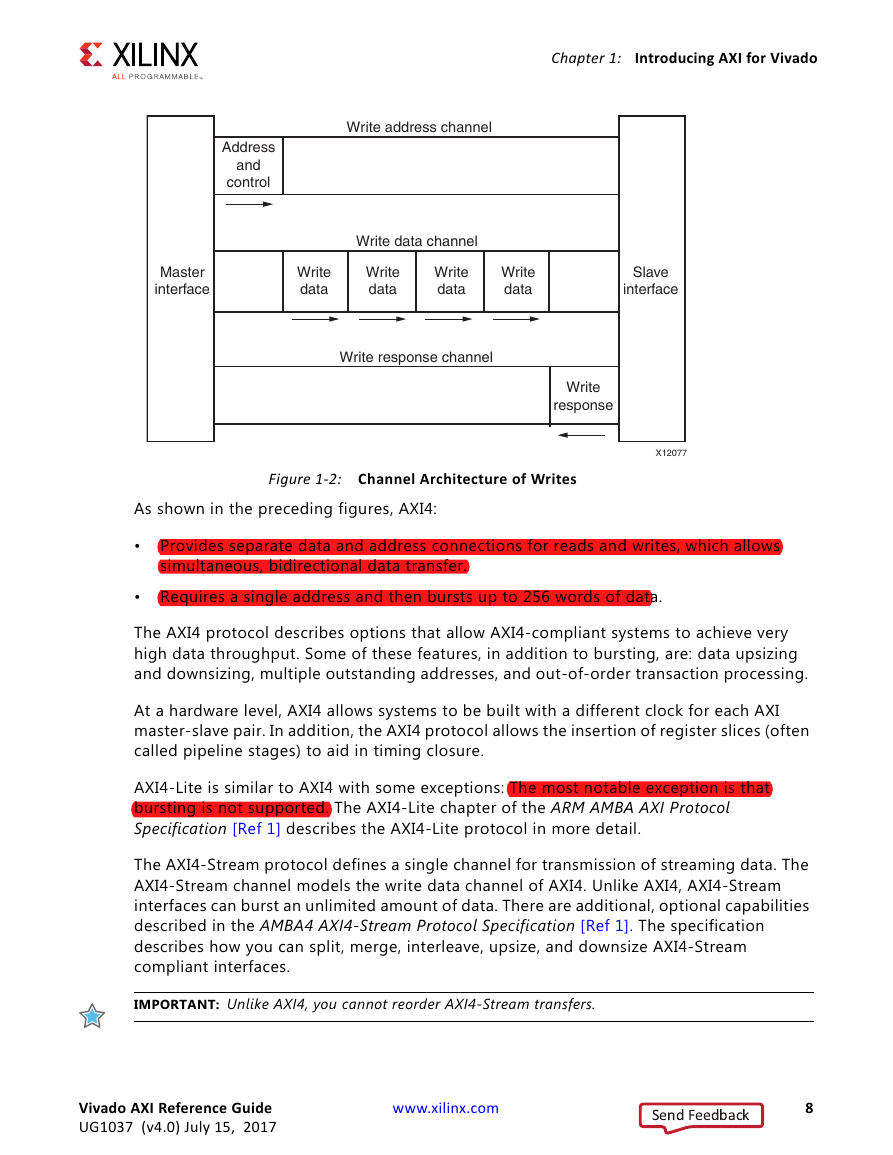

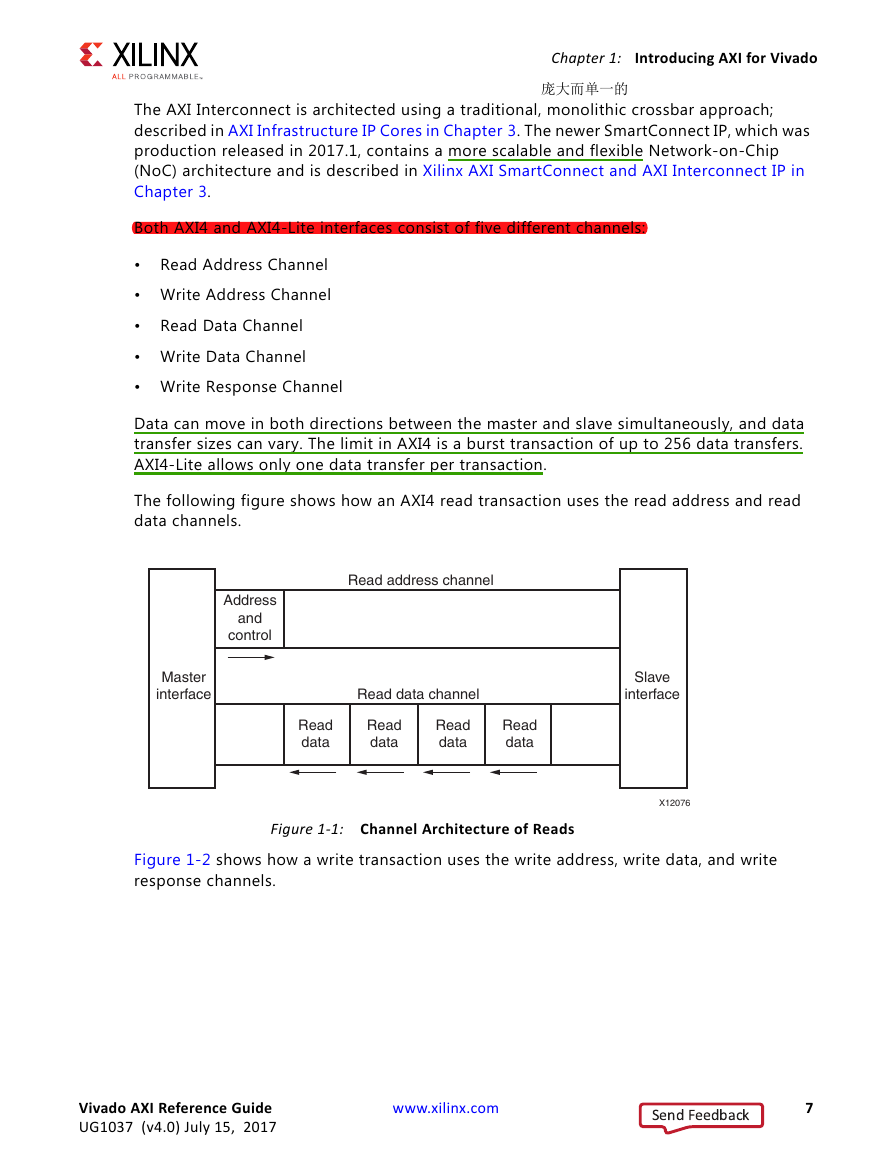

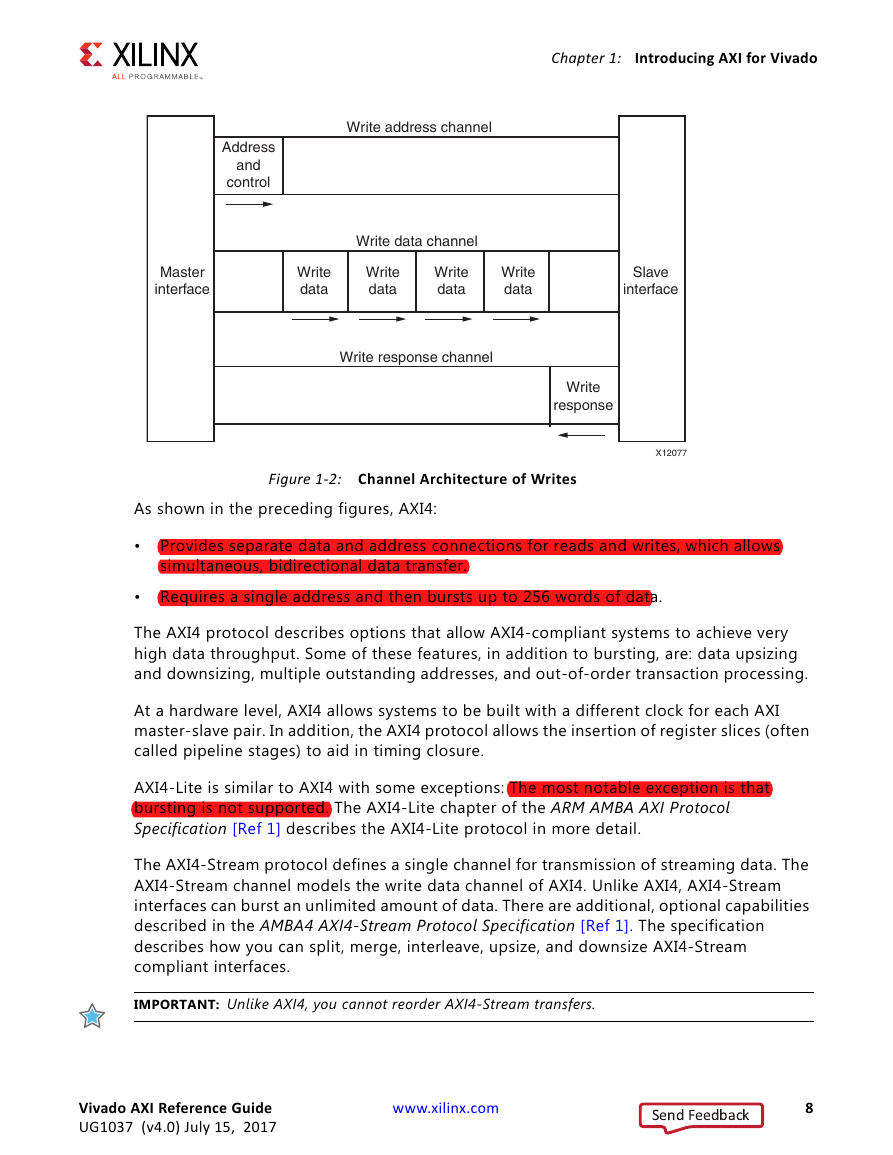

How AXI Works

Combining AXI4-Stream and Memory-Mapped Protocols

IP Interoperability

Data Interpretation

IP Compatibility

AXI4-Stream IP Interoperability

Quick Take Videos

Ch. 2: AXI Support in Xilinx Tools and IP

Introduction

Using Vivado AXI IP in RTL Projects

Using the Create and Package IP Wizard for AXI IP

Adding AXI IP to the IP Catalog Using Vivado IP Packager

Using Vivado IP Integrator to Assemble AXI IP

Using AXI IP in System Generator for DSP

Port Name Truncation

Port Groupings

Breaking Out Multichannel TDATA

Adding AXI Interfaces Using High Level Synthesis

HLS AXI4-Stream Interface

HLS AXI4-Lite Interface

HLS AXI4 Master Interface

Individual Data Transfers

Example 1:

Example 2:

Burst-Mode Transfers

Ch. 3: Samples of Vivado AXI IP and Xilinx Processors

Overview

AXI Infrastructure IP Cores

Xilinx AXI SmartConnect and AXI Interconnect IP

AXI Interconnect Core Features

AXI Interconnect Core Limitations

AXI Interconnect Core Use Models

Conversion Only

N-to-1 Interconnect

1-to-N Interconnect

N-to-M Interconnect (Sparse Crossbar Mode)

Cascading AXI Interconnect Cores Together

AXI SmartConnect IP

Feature Summary

AXI SmartConnect Core Limitations

AXI4-Stream Interconnect Core IP

AXI4-Stream Interconnect Core Features

AXI4-Stream Interconnect Core Diagram

AXI4-Stream Interconnect Core Use Models

Streaming Data Routing and Switching (Crossbar Mode)

Stream Multiplexing and De-multiplexing

AXI Virtual FIFO Controller

The AXI4-Stream interconnect can also perform local FIFO buffering, clock conversion, and width conversion to adapt the interface of the stream endpoints to the data path of the virtual FIFO controller and the AXI memory controller

DataMover

AXI4 DMA

AXI DMA Interfaces

Central DMA

AXI Central DMA Summary

AXI Central DMA Scatter Gather Feature

Central DMA Configurable Features

Video DMA

AXI VDMA Summary

VDMA AXI4 Interfaces

Simulating IP

Using Debug and IP

ILA

VIO

IBERT

JTAG-to-AXI

Performance Monitor IP

Protocol Checkers

AXI Verification IP

Features

Uses

AXI4-Stream Verification IP

Features

Overview

Zynq-7000 AP SoC Verification IP

Features

Additional Features

Limitations

MicroBlaze Debug Module

Zynq UltraScale+ MPSoC Processor Device

PS-PL AXI Interfaces

Zynq-7000 All Programmable SoC Processor IP

Choosing a Programmable Logic Interface

PL Interface Comparison Summary

Cortex-A9 CPU Using General Purpose Masters

PS DMA Controller (DMAC) Using General Purpose Masters

PL DMA Using AXI High-Performance (HP) Interface

PL DMA Using AXI ACP

PL DMA Using General Purpose AXI Slave (GP)

Memory Management Unit (MMU)

MicroBlaze Processor

Overview

MicroBlaze Features

Configurable MicroBlaze Feature Overview

MicroBlaze Memory Architecture

MicroBlaze Hardware AXI Exceptions

Using MicroBlaze AXI Instruction Cache

Using MicroBlaze AXI Data Cache

Using Victim Cache

MicroBlaze Stream Link Interfaces

Ch. 4: AXI Feature Adoption in Xilinx Devices

Introduction

Memory-Mapped IP Feature Adoption and Support

AXI4-Stream Adoption and Support

AXI4-Stream Signals

Numerical Data in an AXI4-Stream

Real Scalar Data Example

Complex Scalar Data Example

Vector Data Example

Sideband Signals

Events

TLAST Events

DSP and Wireless IP: AXI Feature Adoption

Video IP: AXI Feature Adoption

IP Using AXI4-Stream Video Protocol

Signal Interfaces

Input Slave Side Connectors

Output Master Side Signals

Clocking and ACLK

TDATA Structure

Clock Enable, ACLKEN

Reset Requirements, ARESETn

TKEEP and TSTRB

TID

TDEST

TUSER

Signaling Protocol

Channel Structure

READY/VALID Handshake

Guidelines on Driving VALID

Driving READY Guidelines

Interfacing to AXI4-Stream With No READY Signal

Start of Frame Signal - SOF

End Of Line Signal - EOL

Real Time Requirements

Data Format

AXI4-Stream Specific Parameterization

Encoding

Encoding Multiple Pixels

Dynamic TDATA Configuration

Ch. 5: Migrating to Xilinx AXI Protocols

Introduction

Migrating to AXI for IP Cores

Migrating IP Using the Vivado Create and Package Wizard

Using System Generator for DSP for Migrating IP

Migrating a Fast Simplex Link to AXI4-Stream

Master FSL to AXI4-Stream Signal Mapping

Slave FSL to AXI4-Stream Signal Mapping

Differences in Throttling

Migrating HDL Designs to use DSP IP with AXI4-Stream

DSP IP-Specific Migration Instructions

Demonstration Test Bench

Upgrading IP

Latency Changes

Mapping Previously Assigned Ports to An AXI4-Stream Video Protocol

High End Verification Solutions

Ch. 6: AXI System Optimization: Tips and Hints

Introduction

AXI System Optimization

Size/Area Optimization Guidelines

Timing and Fmax Optimization Guidelines

Throughput and Bandwidth Optimization Guidelines

Latency Optimization Guidelines

Ease of Use and Debug Optimization Guidelines

AXI4-based Vivado Multi-Ported Memory Controller: AXI4 System Optimization Example

AXI4 Vivado MPMC Overview

Initial Memory Controller Configuration

Initial AXI Interconnect Configuration

Clock Conversion Recommendation

AXI4 Master Configuration

Maximize Burst Length

No Narrow Burst Transactions

Pipeline Transactions

Single Thread Transactions

Refining the AXI Interconnect Configuration

Independently Configure Converter Banks

Timing Considerations

Setting Issuance and Acceptance Values to 2 or Higher

Adding a Processor to the AXI MPMC System

Considerations When Adding a Processor

Additional Potential Optimizations for AXI MPMC

AXI Interconnect: Shared Address Shared Data Mode

Separate IP Groups into Separate AXI Interconnect Subsystems

Debug and Analysis: Using AXI Debug Monitor and AXI Hardware Protocol Checkers

Floorplanning

AXI Verification IP

More Simple but Wider Interconnect and Memory Controller

Cascading Interconnects

Common Pitfalls Leading to AXI Systems of Poor Quality Results

Oversizing a Memory Controller

Incorrect Core Data Width or Core Clock for AXI Interconnect

Overuse of Register Slices

Skipping Simulation-Based Verification of New IP

Non-contiguous Mapping of Slave Devices in Cascaded Interconnect Scenarios

Optimizing AXI on Zynq-7000 AP SoC Processors

Considerations for High Performance AXI Interface Modules

Ch. 7: AXI4-Stream IP Interoperability: Tips and Hints

Introduction

Key Considerations

AXI4-Stream Protocol

Domain Usage Guidelines and Conventions

Video IP

DSP/Wireless IP

Communications IP

AXI Infrastructure IP

Domain-Specific Data Interpretation and Interoperability Guidelines

Video IP Layered Protocols

DSP/Wireless IP Layered Protocols

Communications IP Layered Protocols

AXI Infrastructure IP Layered Protocols

Appx. A: AXI Adoption Summary

Introduction

Global Signals

AXI4 and AXI4-Lite Signals

AXI4 and AXI4-Lite Write Address Channel Signals

AXI4 and AXI4-Lite Write Data Channel Signals

AXI4 and AXI4-Lite Write Response Channel Signals

AXI4 and AXI4-Lite Read Address Channel Signals

AXI4 and AXI4-Lite Read Data Channel Signals

AXI4-Stream Signal Summary

Appx. B: AXI Terminology

Terminology

Appx. C: Additional Resources and Legal Notices

Xilinx Resources

Solution Centers

Documentation Navigator and Design Hubs

Third-Party Documentation

Xilinx Documentation

Xilinx White Papers and Application Notes

General Xilinx References

Vivado Design Suite Video Tutorials

Please Read: Important Legal Notices

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc