问题提出:

现在的 MOS 驱动,有几个特别的需求,

1,低压应用

当使用 5V 电源,这时候如果使用传统的图腾柱结构,由于三极管的 be 有 0.7V

左右的压降,导致实际最终加在 gate 上的电压只有 4.3V。这时候,我们选用标

称 gate 电压 4.5V 的 MOS 管就存在一定的风险。

同样的问题也发生在使用 3V 或者其他低压电源的场合。

2,宽电压应用

输入电压并不是一个固定值,它会随着时间或者其他因素而变动。这个变动导致

PWM 电路提供给 MOS 管的驱动电压是不稳定的。

为了让 MOS 管在高 gate 电压下安全,很多 MOS 管内置了稳压管强行限制 gate

电压的幅值。在这种情况下,当提供的驱动电压超过稳压管的电压,就会引起较

大的静态功耗。

同时,如果简单的用电阻分压的原理降低 gate 电压,就会出现输入电压比较高

的时候,MOS 管工作良好,而输入电压降低的时候 gate 电压不足,引起导通不

够彻底,从而增加功耗。

3,双电压应用

在一些控制电路中,逻辑部分使用典型的 5V 或者 3.3V 数字电压,而功率部分使

用 12V 甚至更高的电压。两个电压采用共地方式连接。

这就提出一个要求,需要使用一个电路,让低压侧能够有效的控制高压侧的 MOS

管,同时高压侧的 MOS 管也同样会面对 1 和 2 中提到的问题。

在这三种情况下,图腾柱结构无法满足输出要求,而很多现成的 MOS 驱动 IC,

似乎也没有包含 gate 电压限制的结构。

于是我设计了一个相对通用的电路来满足这三种需求。

电路图如下:

�

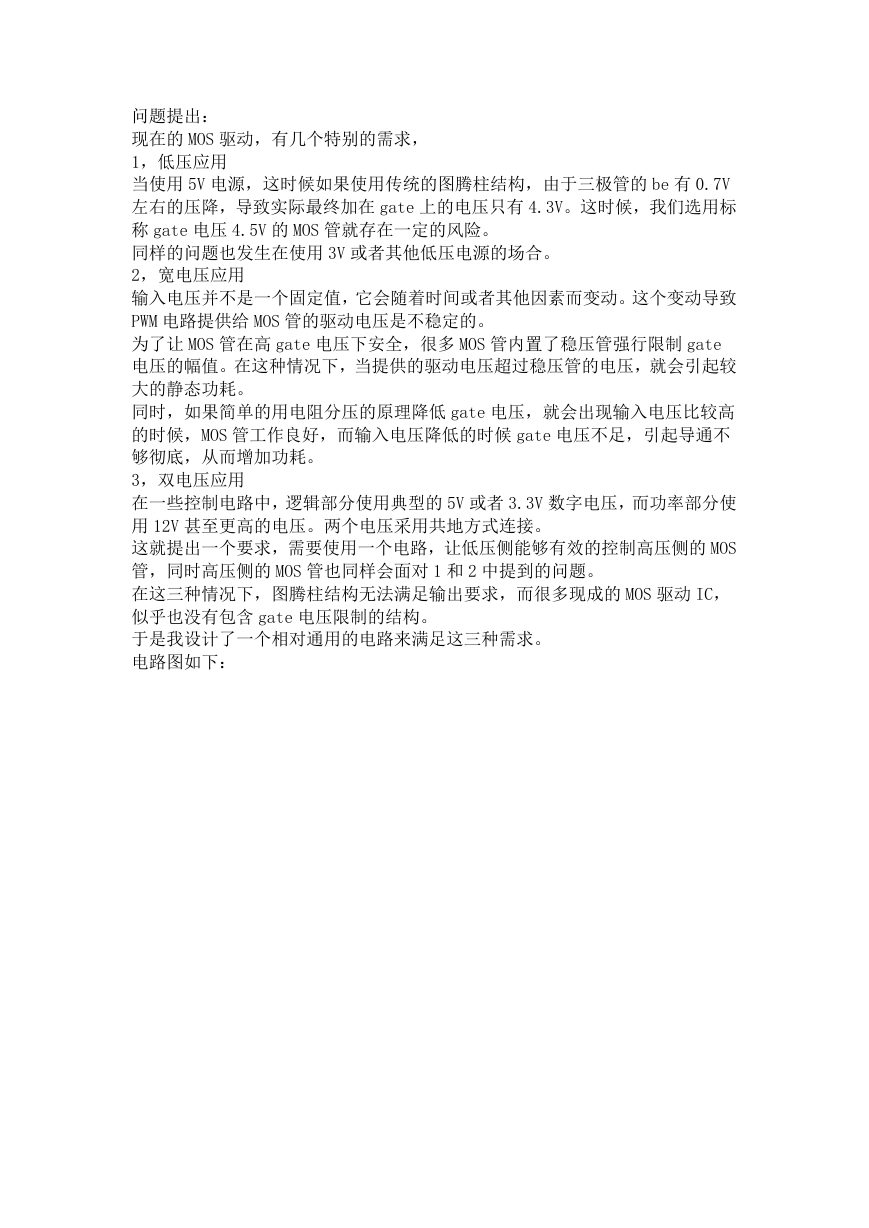

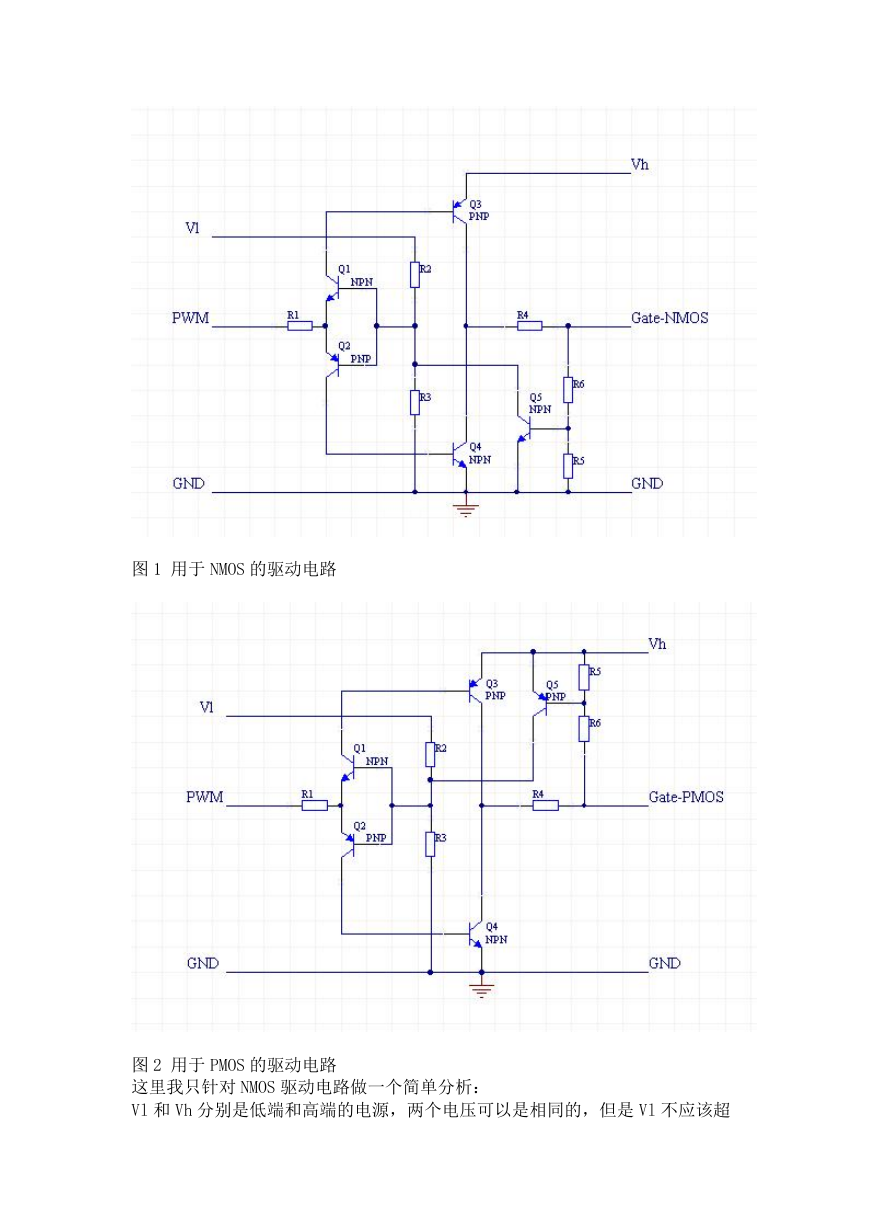

图 1 用于 NMOS 的驱动电路

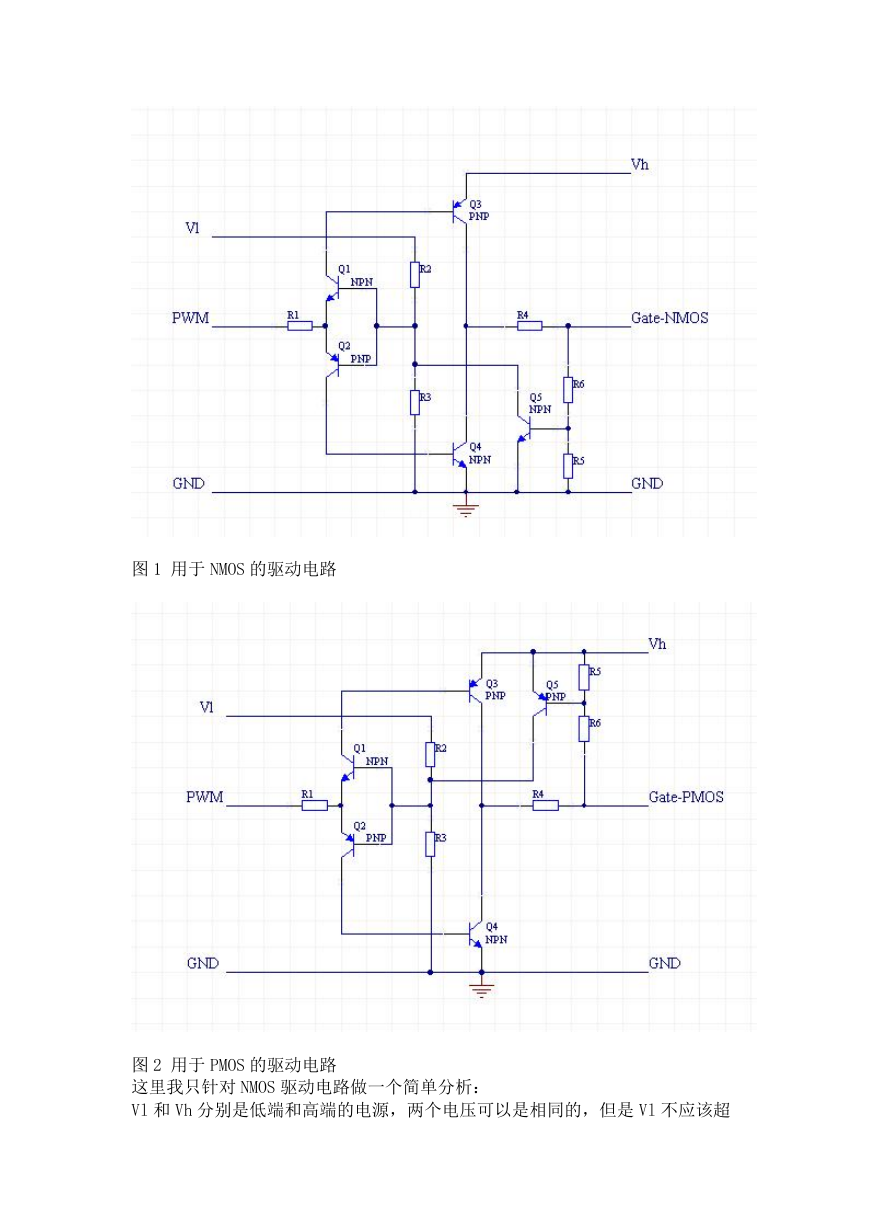

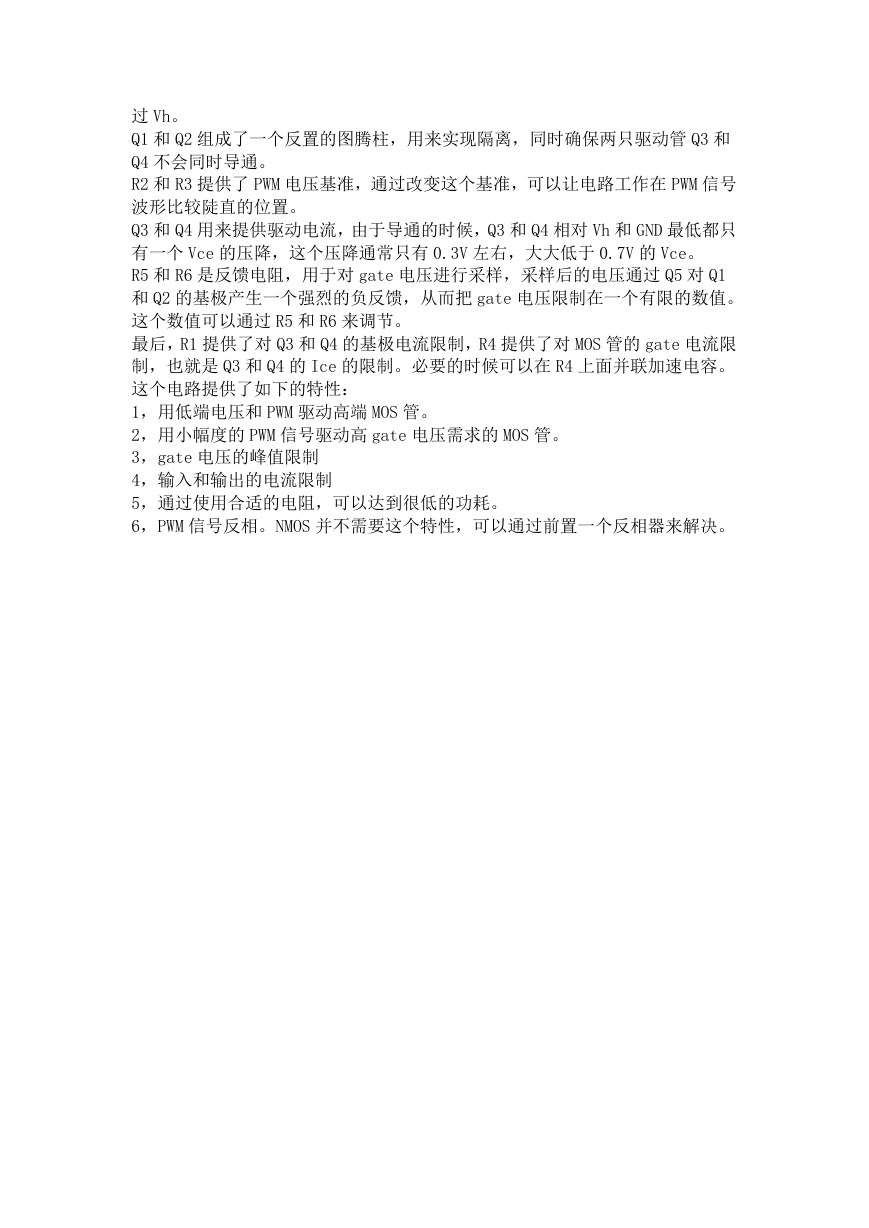

图 2 用于 PMOS 的驱动电路

这里我只针对 NMOS 驱动电路做一个简单分析:

Vl 和 Vh 分别是低端和高端的电源,两个电压可以是相同的,但是 Vl 不应该超

�

过 Vh。

Q1 和 Q2 组成了一个反置的图腾柱,用来实现隔离,同时确保两只驱动管 Q3 和

Q4 不会同时导通。

R2 和 R3 提供了 PWM 电压基准,通过改变这个基准,可以让电路工作在 PWM 信号

波形比较陡直的位置。

Q3 和 Q4 用来提供驱动电流,由于导通的时候,Q3 和 Q4 相对 Vh 和 GND 最低都只

有一个 Vce 的压降,这个压降通常只有 0.3V 左右,大大低于 0.7V 的 Vce。

R5 和 R6 是反馈电阻,用于对 gate 电压进行采样,采样后的电压通过 Q5 对 Q1

和 Q2 的基极产生一个强烈的负反馈,从而把 gate 电压限制在一个有限的数值。

这个数值可以通过 R5 和 R6 来调节。

最后,R1 提供了对 Q3 和 Q4 的基极电流限制,R4 提供了对 MOS 管的 gate 电流限

制,也就是 Q3 和 Q4 的 Ice 的限制。必要的时候可以在 R4 上面并联加速电容。

这个电路提供了如下的特性:

1,用低端电压和 PWM 驱动高端 MOS 管。

2,用小幅度的 PWM 信号驱动高 gate 电压需求的 MOS 管。

3,gate 电压的峰值限制

4,输入和输出的电流限制

5,通过使用合适的电阻,可以达到很低的功耗。

6,PWM 信号反相。NMOS 并不需要这个特性,可以通过前置一个反相器来解决。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc