FPGA 协议实现配置

WP-01132-1.1

白皮书

引言

Altera 新的器件配置模式——协议实现配置 (CvP),通过结合 PCI Express ®来配置

Altera 28-nm Arria ® V、Cyclone ® V 和 Stratix ® V FPGA 的内核架构。CvP 能够降低

产品成本,减小电路板面积,同时简化了软件应用模型,具备可靠的现场系统更新功

能。此外,嵌入式自治 PCIe IP 内核有助于确保设计满足 PCIe 上电时序要求,FPGA 内

核架构配置时间对其没有影响,保证了各种基于 PCIe 计算机平台上广泛的互操作性。

PCIe 技术替代了 PCI 成为处理器和被监控设备之间的标准控制平面接口。自从 2005 年

推出以来,FPGA 设计人员在 FPGA 和处理器之间已经广泛使用了 PCIe 接口。现在的

FPGA 包括嵌入式 PCIe 内核,它用作端点或者根端口。

直到最近,在对 FPGA 进行全面配置之前,嵌入式 PCIe 内核还不支持链路训练和总线

枚举功能。随着器件密度的提高,FPGA 配置时间也越来越长,很难在 PCIe 规范要求的

初始化时间之内完成 FPGA 的全面配置。

在 28-nm 系列器件推出后,Altera 支持从 FPGA 内核逻辑中单独配置 PCIe 硬核 IP,从

而解决了这一问题。该技术支持设计人员通过 PCIe 来配置 Altera Arria V、Cyclone

V 和 Stratix V FPGA 内核架构。CvP 器件编程新方法能够降低产品成本,减小电路板

面积,同时简化了软件应用模型,具备可靠的现场系统更新功能,如下所述:

■ 降低系统成本——CvP 避免了采用一个或者多个并行闪存器件,甚至是外部编程控

制器件。而且,CvP 支持设计人员将 FPGA 编程文件存储在通过 PCIe 链路与 FPGA 链

接的 CPU 存储器系统中。使用这一技术,只有 FPGA I/O 编程和 PCIe 内核参数存储

在闪存器件中,只需要更小更便宜的闪存器件。

■ 减少了对 FPGA 资源的占用——Stratix 系列器件一般需要数据通路较宽的闪存器件

来存储 FPGA 编程文件。相反,CvP 支持的 EPCS 和 EPCQ 器件需要较少的专用引脚。

■ 节省能源——可以根据用户应用参数,通过软件控制来装入低功耗临时 FPGA 镜像。

这一特性适用于电池供电的计算机系统。

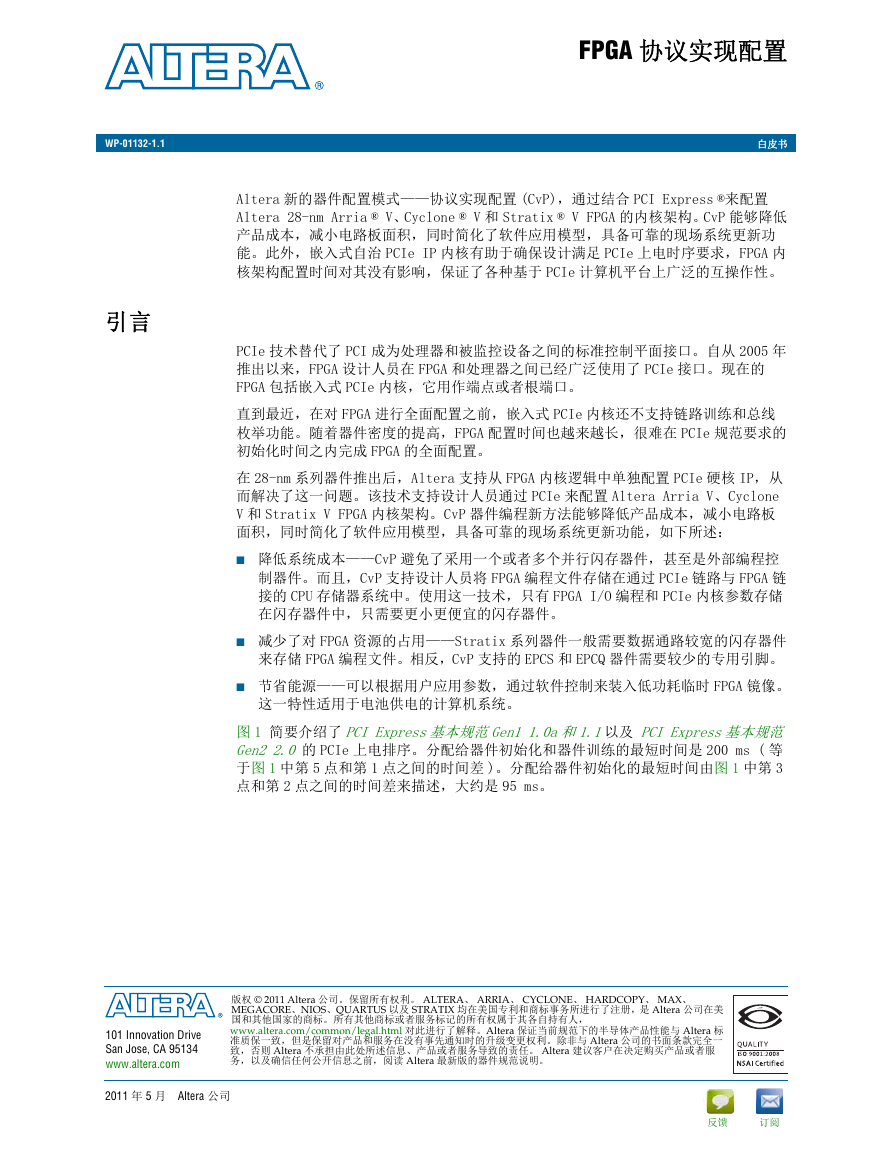

图 1 简要介绍了 PCI Express基本规范Gen1 1.0a和1.1以及 PCI Express基本规范

Gen2 2.0 的 PCIe 上电排序。分配给器件初始化和器件训练的最短时间是 200 ms ( 等

于图 1 中第 5 点和第 1 点之间的时间差 )。分配给器件初始化的最短时间由图 1 中第 3

点和第 2 点之间的时间差来描述,大约是 95 ms。

101 Innovation Drive

San Jose, CA 95134

www.altera.com

版权 © 2011 Altera 公司。保留所有权利。 ALTERA、 ARRIA、 CYCLONE、 HARDCOPY、 MAX、

MEGACORE、NIOS、QUARTUS 以及 STRATIX 均在美国专利和商标事务所进行了注册,是 Altera 公司在美

国和其他国家的商标。所有其他商标或者服务标记的所有权属于其各自持有人,

www.altera.com/common/legal.html 对此进行了解释。Altera 保证当前规范下的半导体产品性能与 Altera 标

准质保一致,但是保留对产品和服务在没有事先通知时的升级变更权利。除非与 Altera 公司的书面条款完全一

致,否则 Altera 不承担由此处所述信息、产品或者服务导致的责任。 Altera 建议客户在决定购买产品或者服

务,以及确信任何公开信息之前,阅读 Altera 最新版的器件规范说明。

2011 年 5 月 Altera 公司

反馈

订阅

�

第 2 页

自治 PCIe 硬核 IP

图 1.PCIe 上电时序波形

1. Power Stable

3.3 / 12 Volts

PERST#

>= 100 ms

>= 100 ms

~10 ms

Minimum Device

Initialization Time

2. Plug-In Card Voltage

Regulators Ramped Up

<= 20 ms

<= 5 ms

3. Link

Detection

PCIe Link State

Inactive

Training

Active (L0)

4. Link LTSSM Must

Enter Detect State

5. Link Must Accept First

Configuration Access

FPGA 器件在很小的体积中封装了更多的逻辑,因此,需要更多的时间采用专用内容对

较大的 FPGA 内核架构进行编程。在大型器件中,总配置时间会超过 95 ms。当端点器

件没有达到规 PCIe 范分配给它的 L0 时间时,端点不会响应软件配置访问操作 ( 第 5

点 ),主机 CPU 将不能识别这一端点。在这种情况下,主机 CPU 可能会忽略端点,系统

工作在没有端点的状态下。

自治 PCIe 硬核 IP

为克服这一失败发现机制,Altera 28-nm FPGA 支持在全面配置 FPGA 内核架构之前进

行嵌入式 PCIe 内核操作。通过在不到 95 ms 内初始化嵌入式 PCIe 内核以及器件 I/O

环,28-nm FPGA 嵌入式 PCIe 内核总是能够满足 PCIe 上电时序要求。这种单独的可配

置嵌入式 PCIe IP 内核被称为 “自治”。

以下序列定义了 PCIe 的 CvP 初始化周期:

1. 通过 PERST# 使嵌入式 PCIe 内核保持复位,在第 3 点开始 PCIe 链路发现和训练之

前释放。

2. 在 PCIe 链路完成训练阶段,达到 L0 状态后,FPGA 内核架构的其他部分开始编程。

3. 嵌入式 PCIe 端点内核到达 L0 状态后,主机操作系统 (OS) 开始访问 PCIe 内核的配

置空间寄存器 (CSR),完成配置写访问周期,它是系统初始化和发现过程的一部分

( 第 5 点 )。

4. 对于 FPGA 内核架构没有完全按照设计人员应用内容进行编程的情况 ( 换言之,还

没有达到 “用户模式”),自治 PCIe 内核以配置重试状态 (CRS) 操作进行响应,直

至 FPGA 内核架构被全部装入。

5. OS 正确的找到这一端点,尝试再次查询它直到正常工作为止。

6. 在 OS 确定端点失效之前,端点可以响应 CRS 一秒钟。换句话说,在这一器件初始

化模式中,分配给 FPGA 内核架构编程的时间不能超过一秒钟。

FGPA 协议实现配置

2011 年 5 月 Altera 公司

�

PCIe 总线上的 FPGA 内核架构编程

第 3 页

PCIe 总线上的 FPGA 内核架构编程

以下章节详细介绍了 CvP 和 PCIe 的使用。设计人员可以使用 CvP 通过 PCIe 装入最初

的 FPGA 内核架构镜像,然后,在运行时修改这一内核架构镜像,以满足应用需求。对

PCIe IP 内核外设进行编程后,链路训练进入相应的 PCIe 工作模式。

PCIe 链路完成训练并到达 L0 状态后,主机 CPU 可以通过 PCIe 对 FPGA 内核架构镜像进

行编程。

1 每片 28-nm FPGA 只有一个嵌入式 PCIe 内核能够进行 CvP,也只适用于用作端点的情况。

通过 PCIe 配置 FPGA 内核架构期间,所有非串化器 / 解串器 (SERDES) I/O 引脚被内部

弱上拉电阻置于高电平状态。在装入 CvP 内核架构镜像期间,所有其他高速 SERDES 引

脚实际上处于复位状态。之所以这样设计这些 I/O 分配,是为了在更新 FPGA 内核架构

配置期间保持 I/O 工作状态不变。使能 CvP 后,自治 PCIe 内核并不以 CRS 操作进行响

应,而是接受并响应 PCIe 配置和数据操作,以完成 FPGA 内核架构配置。

表 1.28-nm FPGA 配置模式

模式

状态

数据宽度 ( 位 )

已有

主动串行 (AS)

主动四路 (AQ)

被动串行 (PS)

已有

8 位快速被动并行 (FPP),使用闪存装入器。 已有

4、 16 或者 32 位 FPP,使用闪存装入器。

基于 JTAG

CvP 使用 PCIe

已有

新

新

新

1

4

1

8

4, 16, 32(1)

专用 JTAG 端口

1, 2, 4, 8(2)

注释:

(1) 仅 Stratix V 器件。

(2) PCIe 链路中的通路数量 (Gen1 x1、x2、x4 或者 x8 ; Gen2 x1、x2、x4 或者 x8 ; )

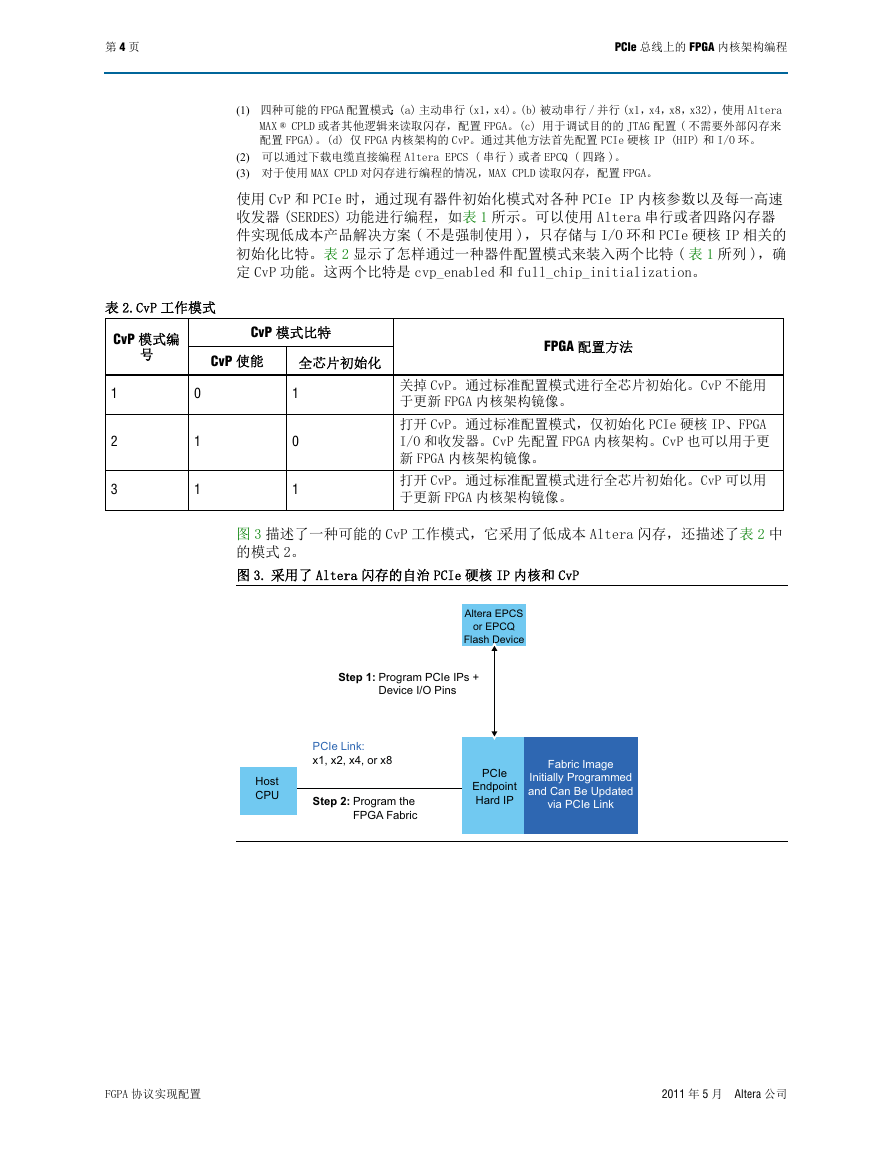

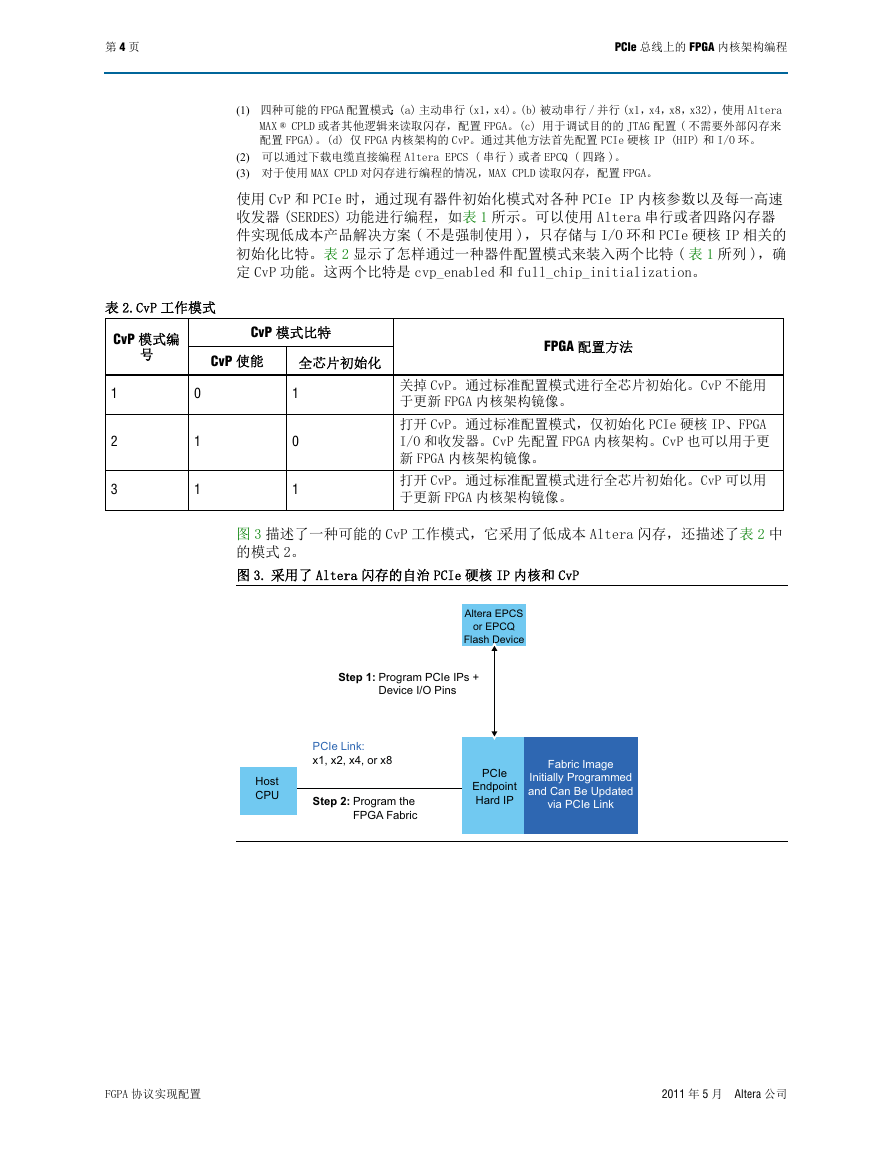

图 2 显示了 Stratix V 配置模式和闪存编程方法的高级表示。为简化这一图形表示,

结构图中组合了所有闪存模式。

图 2. 器件配置和闪存编程模式

USB Port

Download Cable

Direct EPCS or

EPCQ Flash

Programming

Flash Loader

and Parallel

Flash Programming

Host

CPU

Serial,

Quad,

or Parallel

Flash

Parallel

Program/Read

Max

CPLD

(Parallel

Flash

Loader)

a. AS, AP Device

Configuration

b. Passive Serial/

Quad/Parallel

Configuration

d. CvP

PCIe Port

PCIe

HIP

FPGA

Core Fabric

c. JTAG

Configuration

注释:

2011 年 5 月 Altera 公司

FGPA 协议实现配置

�

第 4 页

PCIe 总线上的 FPGA 内核架构编程

(1) 四种可能的 FPGA 配置模式:(a) 主动串行 (x1,x4)。(b) 被动串行 / 并行 (x1,x4,x8,x32),使用 Altera

MAX ® CPLD 或者其他逻辑来读取闪存,配置 FPGA。(c) 用于调试目的的 JTAG 配置 ( 不需要外部闪存来

配置 FPGA)。(d) 仅 FPGA 内核架构的 CvP。通过其他方法首先配置 PCIe 硬核 IP (HIP) 和 I/O 环。

(2) 可以通过下载电缆直接编程 Altera EPCS ( 串行 ) 或者 EPCQ ( 四路 )。

(3) 对于使用 MAX CPLD 对闪存进行编程的情况,MAX CPLD 读取闪存,配置 FPGA。

使用 CvP 和 PCIe 时,通过现有器件初始化模式对各种 PCIe IP 内核参数以及每一高速

收发器 (SERDES) 功能进行编程,如表 1 所示。可以使用 Altera 串行或者四路闪存器

件实现低成本产品解决方案 ( 不是强制使用 ),只存储与 I/O 环和 PCIe 硬核 IP 相关的

初始化比特。表 2 显示了怎样通过一种器件配置模式来装入两个比特 ( 表 1 所列 ),确

定 CvP 功能。这两个比特是 cvp_enabled 和 full_chip_initialization。

表 2.CvP 工作模式

CvP 模式编

号

CvP 模式比特

CvP 使能

全芯片初始化

1

2

3

0

1

1

1

0

1

FPGA 配置方法

关掉 CvP。通过标准配置模式进行全芯片初始化。CvP 不能用

于更新 FPGA 内核架构镜像。

打开 CvP。通过标准配置模式,仅初始化 PCIe 硬核 IP、FPGA

I/O 和收发器。CvP 先配置 FPGA 内核架构。CvP 也可以用于更

新 FPGA 内核架构镜像。

打开 CvP。通过标准配置模式进行全芯片初始化。CvP 可以用

于更新 FPGA 内核架构镜像。

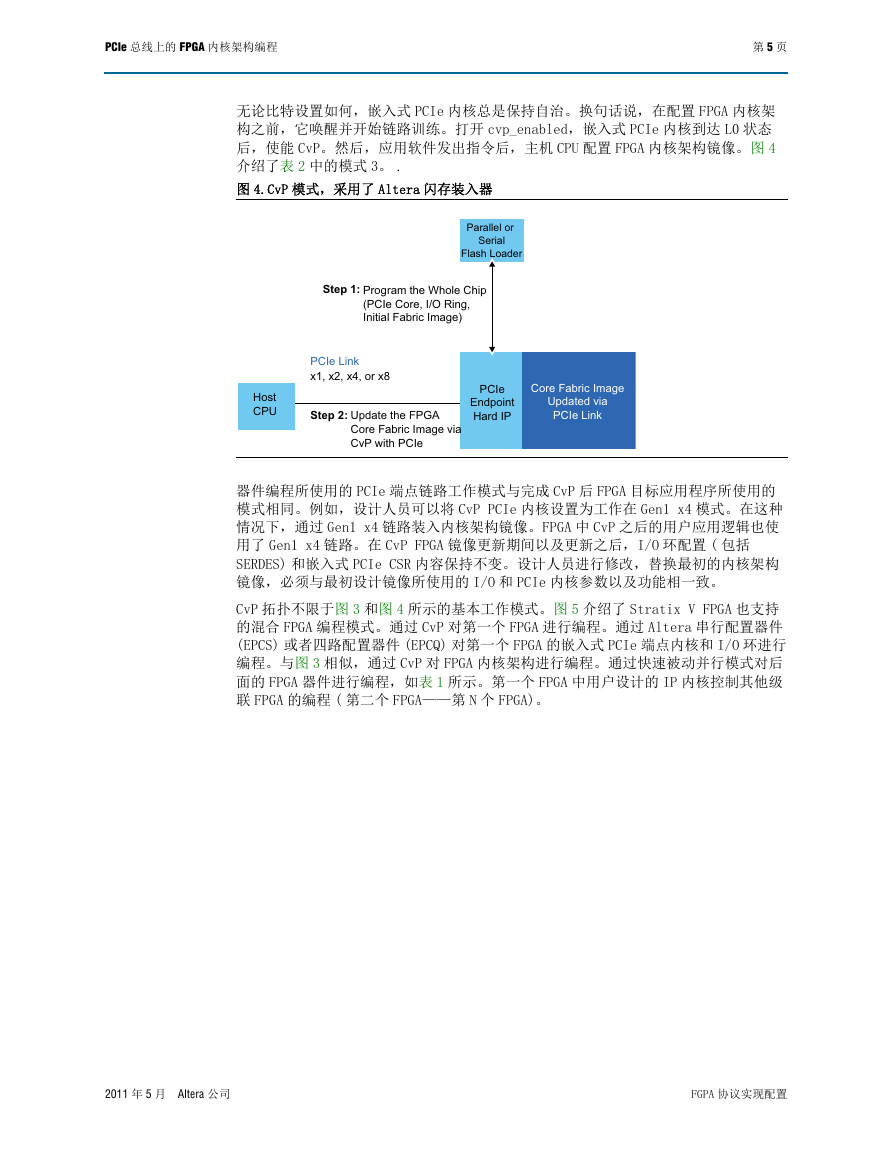

图 3 描述了一种可能的 CvP 工作模式,它采用了低成本 Altera 闪存,还描述了表 2 中

的模式 2。

图 3. 采用了 Altera 闪存的自治 PCIe 硬核 IP 内核和 CvP

Altera EPCS

or EPCQ

Flash Device

Step 1: Program PCIe IPs +

Device I/O Pins

Host

CPU

PCIe Link:

x1, x2, x4, or x8

Step 2: Program the

FPGA Fabric

PCIe

Endpoint

Hard IP

Fabric Image

Initially Programmed

and Can Be Updated

via PCIe Link

FGPA 协议实现配置

2011 年 5 月 Altera 公司

�

PCIe 总线上的 FPGA 内核架构编程

第 5 页

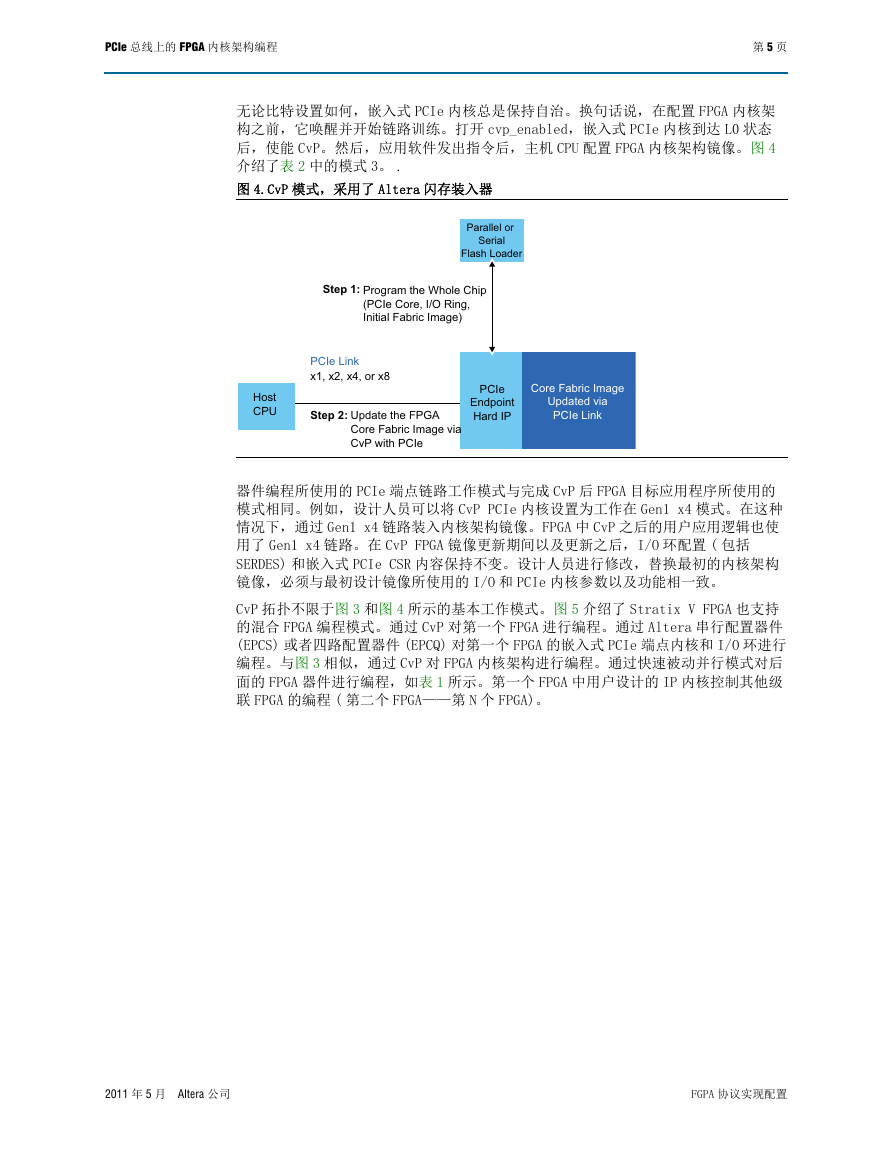

无论比特设置如何,嵌入式 PCIe 内核总是保持自治。换句话说,在配置 FPGA 内核架

构之前,它唤醒并开始链路训练。打开 cvp_enabled,嵌入式 PCIe 内核到达 L0 状态

后,使能 CvP。然后,应用软件发出指令后,主机 CPU 配置 FPGA 内核架构镜像。图 4

介绍了表 2 中的模式 3。 .

图 4.CvP 模式,采用了 Altera 闪存装入器

Parallel or

Serial

Flash Loader

Step 1: Program the Whole Chip

(PCIe Core, I/O Ring,

Initial Fabric Image)

PCIe Link

x1, x2, x4, or x8

Host

CPU

Step 2: Update the FPGA

Core Fabric Image via

CvP with PCIe

PCIe

Endpoint

Hard IP

Core Fabric Image

Updated via

PCIe Link

器件编程所使用的 PCIe 端点链路工作模式与完成 CvP 后 FPGA 目标应用程序所使用的

模式相同。例如,设计人员可以将 CvP PCIe 内核设置为工作在 Gen1 x4 模式。在这种

情况下,通过 Gen1 x4 链路装入内核架构镜像。FPGA 中 CvP 之后的用户应用逻辑也使

用了 Gen1 x4 链路。在 CvP FPGA 镜像更新期间以及更新之后,I/O 环配置 ( 包括

SERDES) 和嵌入式 PCIe CSR 内容保持不变。设计人员进行修改,替换最初的内核架构

镜像,必须与最初设计镜像所使用的 I/O 和 PCIe 内核参数以及功能相一致。

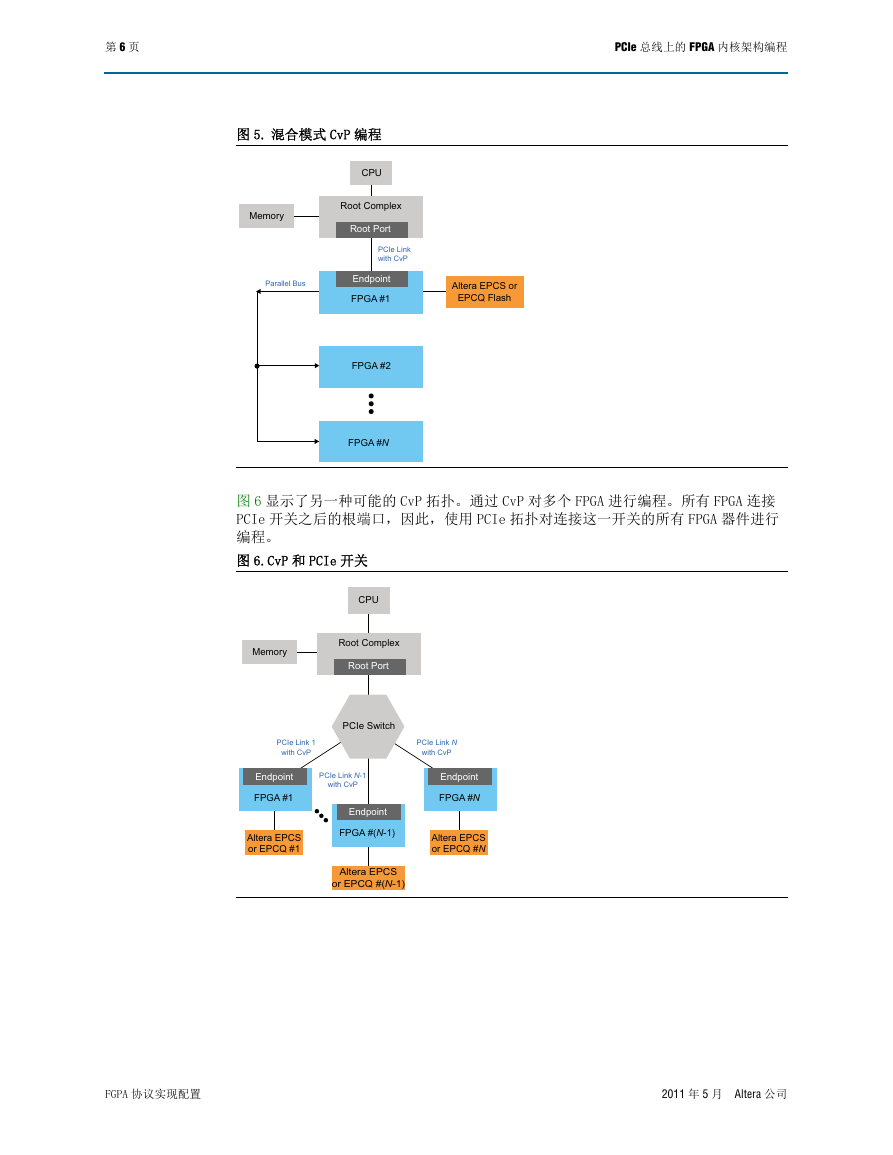

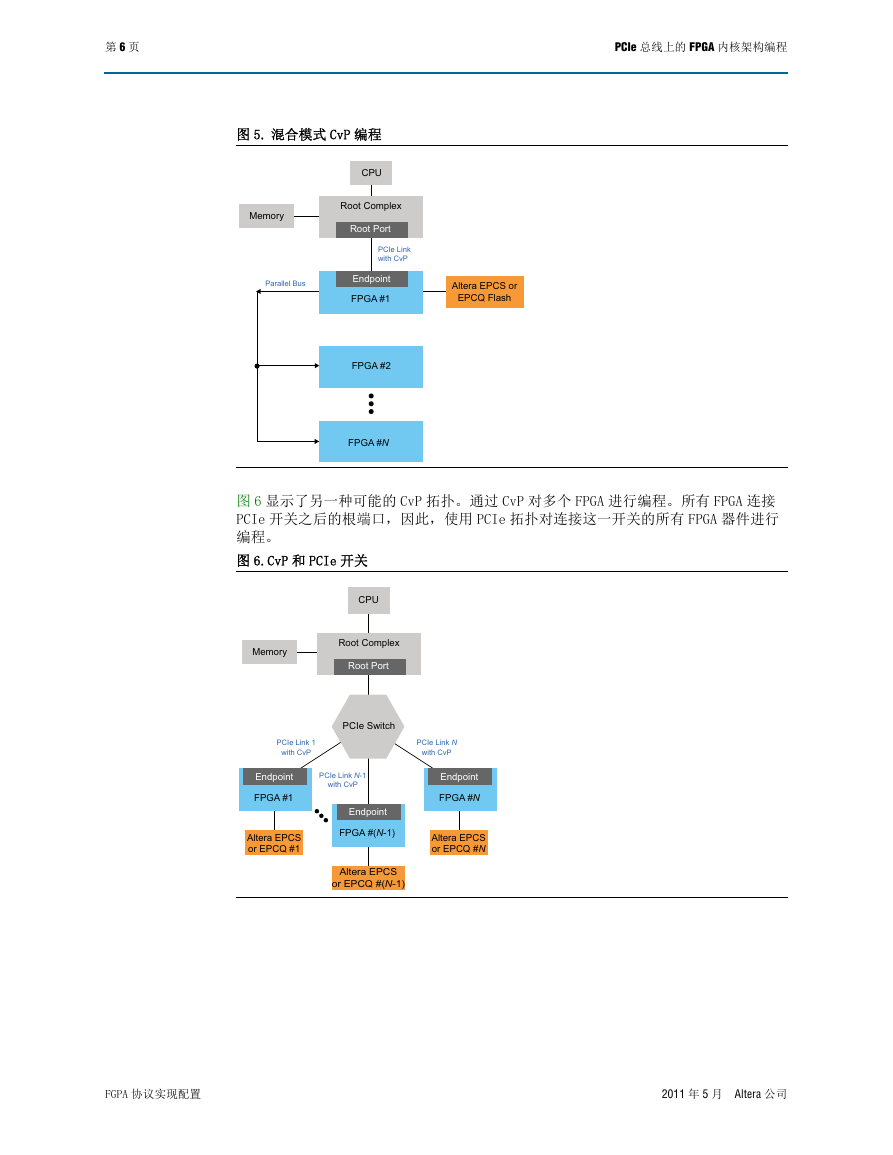

CvP 拓扑不限于图 3 和图 4 所示的基本工作模式。图 5 介绍了 Stratix V FPGA 也支持

的混合 FPGA 编程模式。通过 CvP 对第一个 FPGA 进行编程。通过 Altera 串行配置器件

(EPCS) 或者四路配置器件 (EPCQ) 对第一个 FPGA 的嵌入式 PCIe 端点内核和 I/O 环进行

编程。与图 3 相似,通过 CvP 对 FPGA 内核架构进行编程。通过快速被动并行模式对后

面的 FPGA 器件进行编程,如表 1 所示。第一个 FPGA 中用户设计的 IP 内核控制其他级

联 FPGA 的编程 ( 第二个 FPGA——第 N 个 FPGA)。

2011 年 5 月 Altera 公司

FGPA 协议实现配置

�

第 6 页

PCIe 总线上的 FPGA 内核架构编程

图 5. 混合模式 CvP 编程

Memory

Parallel Bus

CPU

Root Complex

Root Port

PCIe Link

with CvP

Endpoint

FPGA #1

FPGA #2

FPGA #N

Altera EPCS or

EPCQ Flash

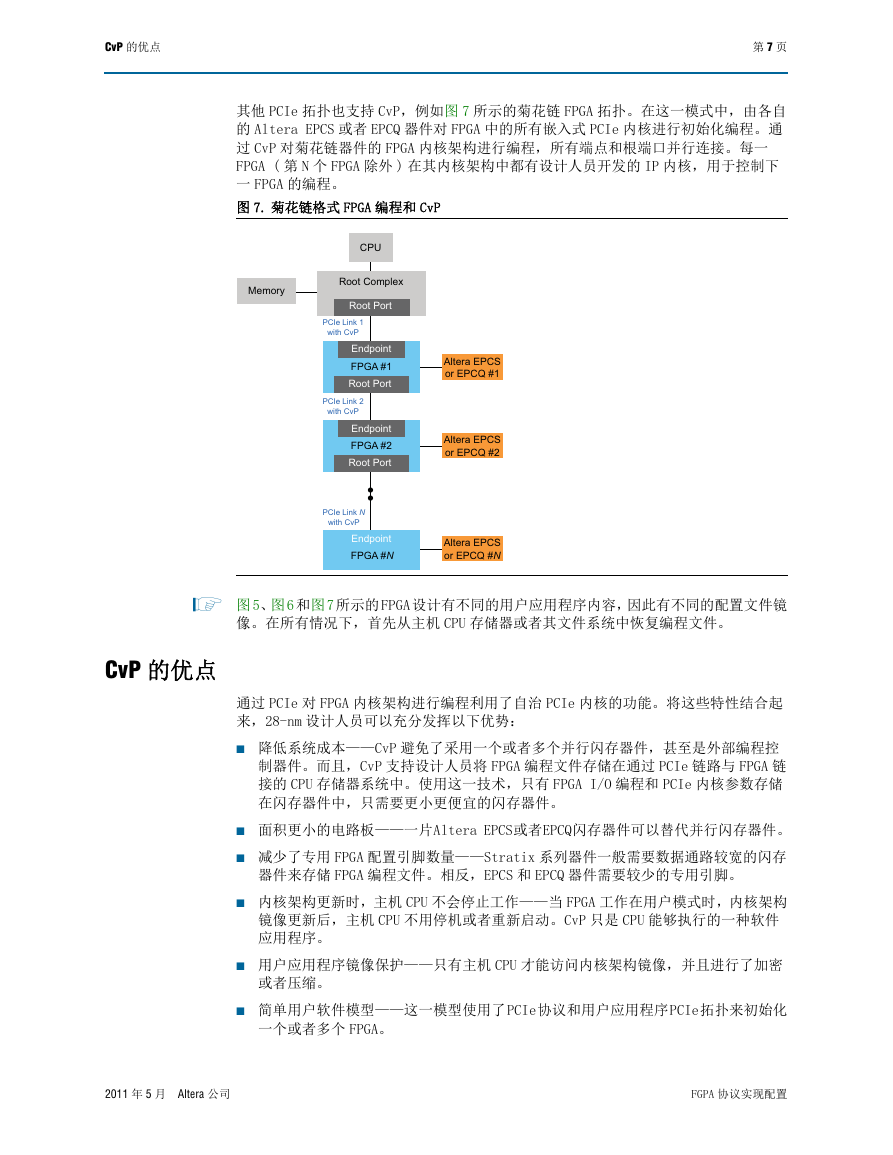

图 6 显示了另一种可能的 CvP 拓扑。通过 CvP 对多个 FPGA 进行编程。所有 FPGA 连接

PCIe 开关之后的根端口,因此,使用 PCIe 拓扑对连接这一开关的所有 FPGA 器件进行

编程。

图 6.CvP 和 PCIe 开关

CPU

Root Complex

Root Port

Memory

PCIe Switch

PCIe Link 1

with CvP

PCIe Link N

with CvP

Endpoint

FPGA #1

PCIe Link N-1

with CvP

Altera EPCS

or EPCQ #1

Endpoint

FPGA #(N-1)

Altera EPCS

or EPCQ #(N-1)

Endpoint

FPGA #N

Altera EPCS

or EPCQ #N

FGPA 协议实现配置

2011 年 5 月 Altera 公司

�

CvP 的优点

第 7 页

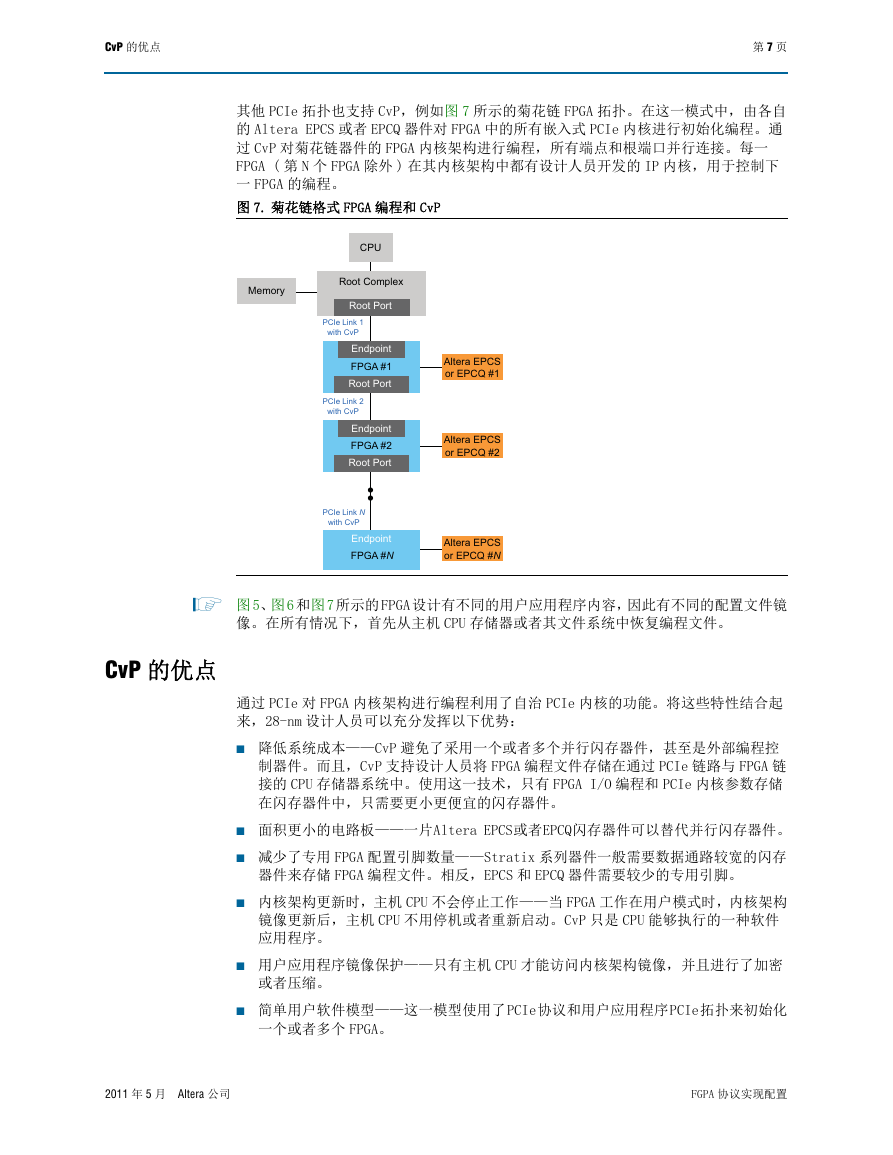

其他 PCIe 拓扑也支持 CvP,例如图 7 所示的菊花链 FPGA 拓扑。在这一模式中,由各自

的 Altera EPCS 或者 EPCQ 器件对 FPGA 中的所有嵌入式 PCIe 内核进行初始化编程。通

过 CvP 对菊花链器件的 FPGA 内核架构进行编程,所有端点和根端口并行连接。每一

FPGA ( 第 N 个 FPGA 除外 ) 在其内核架构中都有设计人员开发的 IP 内核,用于控制下

一 FPGA 的编程。

图 7. 菊花链格式 FPGA 编程和 CvP

Memory

CPU

Root Complex

Root Port

PCIe Link 1

with CvP

Endpoint

FPGA #1

Root Port

PCIe Link 2

with CvP

Endpoint

FPGA #2

Root Port

PCIe Link N

with CvP

Endpoint

FPGA #N

Altera EPCS

or EPCQ #1

Altera EPCS

or EPCQ #2

Altera EPCS

or EPCQ #N

1 图 5、图 6 和图 7 所示的 FPGA 设计有不同的用户应用程序内容,因此有不同的配置文件镜

像。在所有情况下,首先从主机 CPU 存储器或者其文件系统中恢复编程文件。

CvP 的优点

通过 PCIe 对 FPGA 内核架构进行编程利用了自治 PCIe 内核的功能。将这些特性结合起

来,28-nm 设计人员可以充分发挥以下优势:

■ 降低系统成本——CvP 避免了采用一个或者多个并行闪存器件,甚至是外部编程控

制器件。而且,CvP 支持设计人员将 FPGA 编程文件存储在通过 PCIe 链路与 FPGA 链

接的 CPU 存储器系统中。使用这一技术,只有 FPGA I/O 编程和 PCIe 内核参数存储

在闪存器件中,只需要更小更便宜的闪存器件。

■ 面积更小的电路板——一片Altera EPCS或者EPCQ闪存器件可以替代并行闪存器件。

■ 减少了专用 FPGA 配置引脚数量——Stratix 系列器件一般需要数据通路较宽的闪存

器件来存储 FPGA 编程文件。相反,EPCS 和 EPCQ 器件需要较少的专用引脚。

■ 内核架构更新时,主机 CPU 不会停止工作——当 FPGA 工作在用户模式时,内核架构

镜像更新后,主机 CPU 不用停机或者重新启动。CvP 只是 CPU 能够执行的一种软件

应用程序。

■ 用户应用程序镜像保护——只有主机 CPU 才能访问内核架构镜像,并且进行了加密

或者压缩。

■ 简单用户软件模型——这一模型使用了PCIe协议和用户应用程序PCIe拓扑来初始化

一个或者多个 FPGA。

2011 年 5 月 Altera 公司

FGPA 协议实现配置

�

第 8 页

CvP 工作

■ 节省能源——可以根据用户应用程序参数,通过软件控制来装入低功耗临时镜像。

这一特性适用于电池供电的便携式计算机系统。

CvP 工作

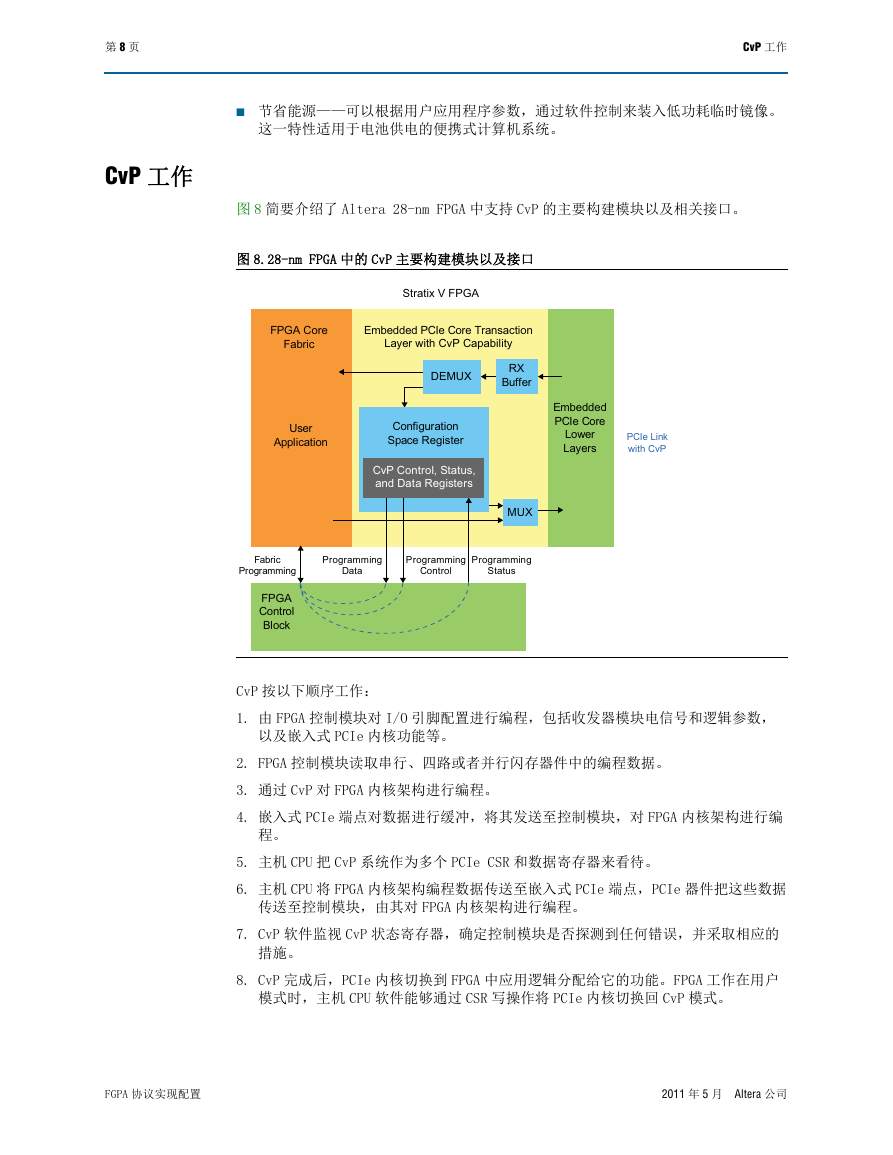

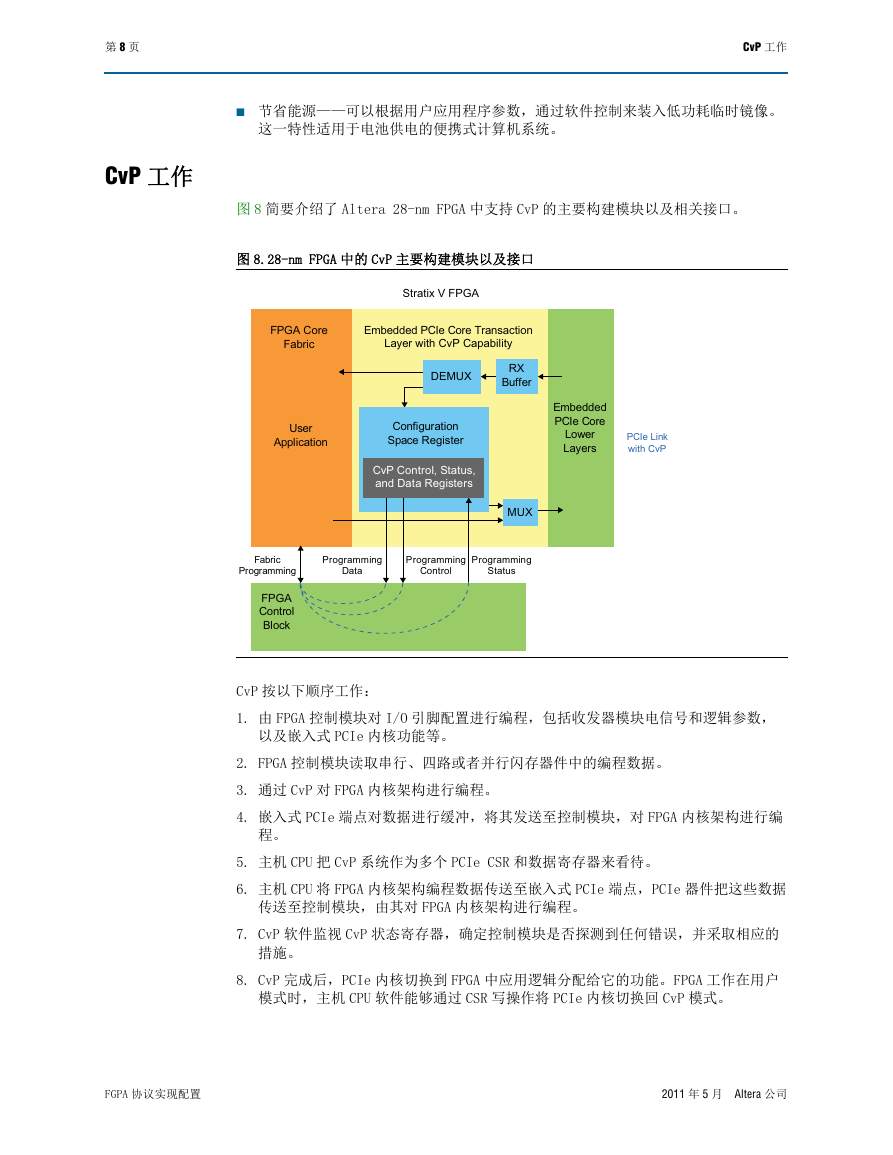

图 8 简要介绍了 Altera 28-nm FPGA 中支持 CvP 的主要构建模块以及相关接口。

图 8.28-nm FPGA 中的 CvP 主要构建模块以及接口

Stratix V FPGA

FPGA Core

Fabric

Embedded PCIe Core Transaction

Layer with CvP Capability

DEMUX

RX

Buffer

User

Application

Configuration

Space Register

CvP Control, Status,

and Data Registers

MUX

Fabric

Programming

Programming

Data

Programming

Control

Programming

Status

FPGA

Control

Block

CvP 按以下顺序工作:

Embedded

PCIe Core

Lower

Layers

PCIe Link

with CvP

1. 由 FPGA 控制模块对 I/O 引脚配置进行编程,包括收发器模块电信号和逻辑参数,

以及嵌入式 PCIe 内核功能等。

2. FPGA 控制模块读取串行、四路或者并行闪存器件中的编程数据。

3. 通过 CvP 对 FPGA 内核架构进行编程。

4. 嵌入式 PCIe 端点对数据进行缓冲,将其发送至控制模块,对 FPGA 内核架构进行编

程。

5. 主机 CPU 把 CvP 系统作为多个 PCIe CSR 和数据寄存器来看待。

6. 主机 CPU 将 FPGA 内核架构编程数据传送至嵌入式 PCIe 端点,PCIe 器件把这些数据

传送至控制模块,由其对 FPGA 内核架构进行编程。

7. CvP 软件监视 CvP 状态寄存器,确定控制模块是否探测到任何错误,并采取相应的

措施。

8. CvP 完成后,PCIe 内核切换到 FPGA 中应用逻辑分配给它的功能。FPGA 工作在用户

模式时,主机 CPU 软件能够通过 CSR 写操作将 PCIe 内核切换回 CvP 模式。

FGPA 协议实现配置

2011 年 5 月 Altera 公司

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc