编号: 1

电机控制综合课程设计

报告书

课

题:

基于 FPGA 的洗衣机控制器

院 (系):

机电工程学院

专

业:

电气工程及其自动化

学生姓名:

蒋岷君

学

号:

0800120313

题目类型:理论研究 实验研究 工程设计 工程技术研究 软件开

发

2011 年 7 月 6 日

1

�

前言

一、洗衣机控制器主要内容

l.任务要求和内容

设计制作一个洗衣机的正反转定时控制线路。

1)控制洗衣机的电机作如下运转

定时开始――正转 10S――暂停 5S――反转 10S――暂停 5S――定时到停止

定时未到

2)用 2 位七段数码管显示定时时间(S)。

2.洗衣机控制器的使用步骤:

(1)电路上电后,在 Start 拨码开关未闭合前可以由 UpKey 和 DownKey 按键开关

“+”“-”设置总的工作时间,确定洗衣机控制器工作允许时间。

(2)设定好允许工作时间后,闭合 Start 开关,洗衣机控制器开始工作。

(3)可以看见指示正转 LED 灯亮 10s,停转 LED 灯亮 5S,反转 LED 灯亮 10s,

停转 LED 亮 5s,如此反复直至工作允许时间为 0,蜂鸣器发出警报。

二、设计原理简介

洗衣机控制器的设计主要是时序控制和定时器的设计,由一片 FPGA 和外

围电路构成电器控制部分。FPGA 接收键盘的控制命令,控制洗衣机的正转、反

转、停机和定时时间为 0 报警的工作状态、控制并显示工作状态以及显示定时时

间。对 FPGA 芯片的编程采用模块化的 Verilog HDL (硬件描述语言)进行设计,

设计由分频模块,按键消抖模块,定时时间自减模块,时序中心控制模块,数码

管显示模块组成,顶层实现整个芯片的功能。顶层使用原理图实现,底层由

Verilog HDL 语句实现。

FPGA 的输入时钟为 20M hz,因此使用了分频模块输出 1hz 的方波给定时器

设定自减模块提供每 1s 自减 1 的信号,定时器模块输出的自减值输入给数码管

显示译码模块和时序控制模块,通过译码模块定时器的值可以在数码管上显示,

2

�

同时定时器的值输入到时序控制模块由此可以控制洗衣机的正转、反转、停机和

报警工作方式。通过按键消抖模块可以准确无抖动的设定定时器的工作时间。

目录

一 、前言···········································2

二、 目录 ·········································3

三 、正文 ··········································4

3.1 洗衣机控制器的整体框图及原理 ············4

3.2 洗衣机控制电路单元模块设计和仿真········5

3.2.1 按键消抖模块的设计················5

3.2.2 时钟分频模块的设计················6

3.2.3 定时器设定和自减模块的设计·········7

3.2.4 时序中心控制模块的设计·············8

3.2.5 数码管显示译码模块的设计···········9

四、电路调试···································11

五、结束语和心得体会····························12

六、参考文献··································13

七、附录······································13

7.1 FPGA 系统板部分原理图···················13

7.2 FPGA 系统板 PCB 图······················15

3

�

三、正文

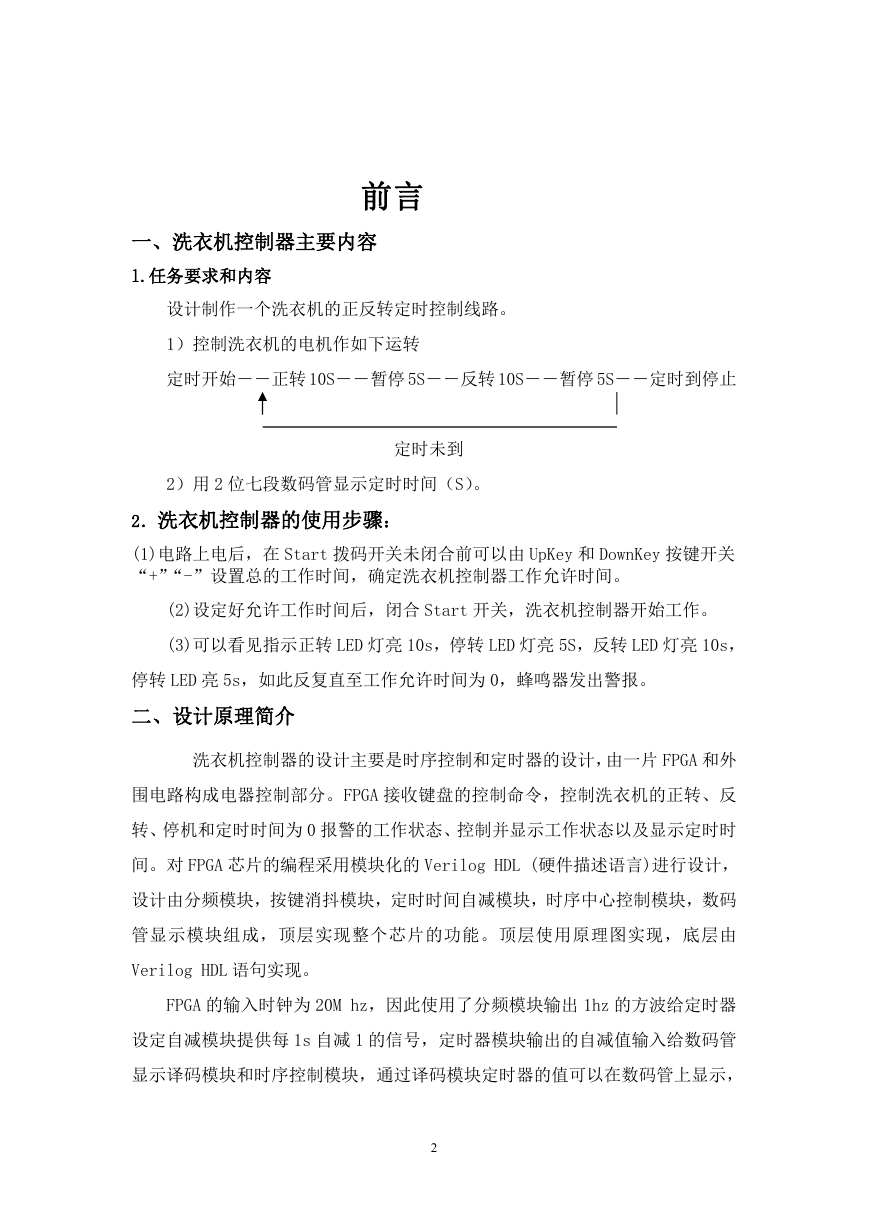

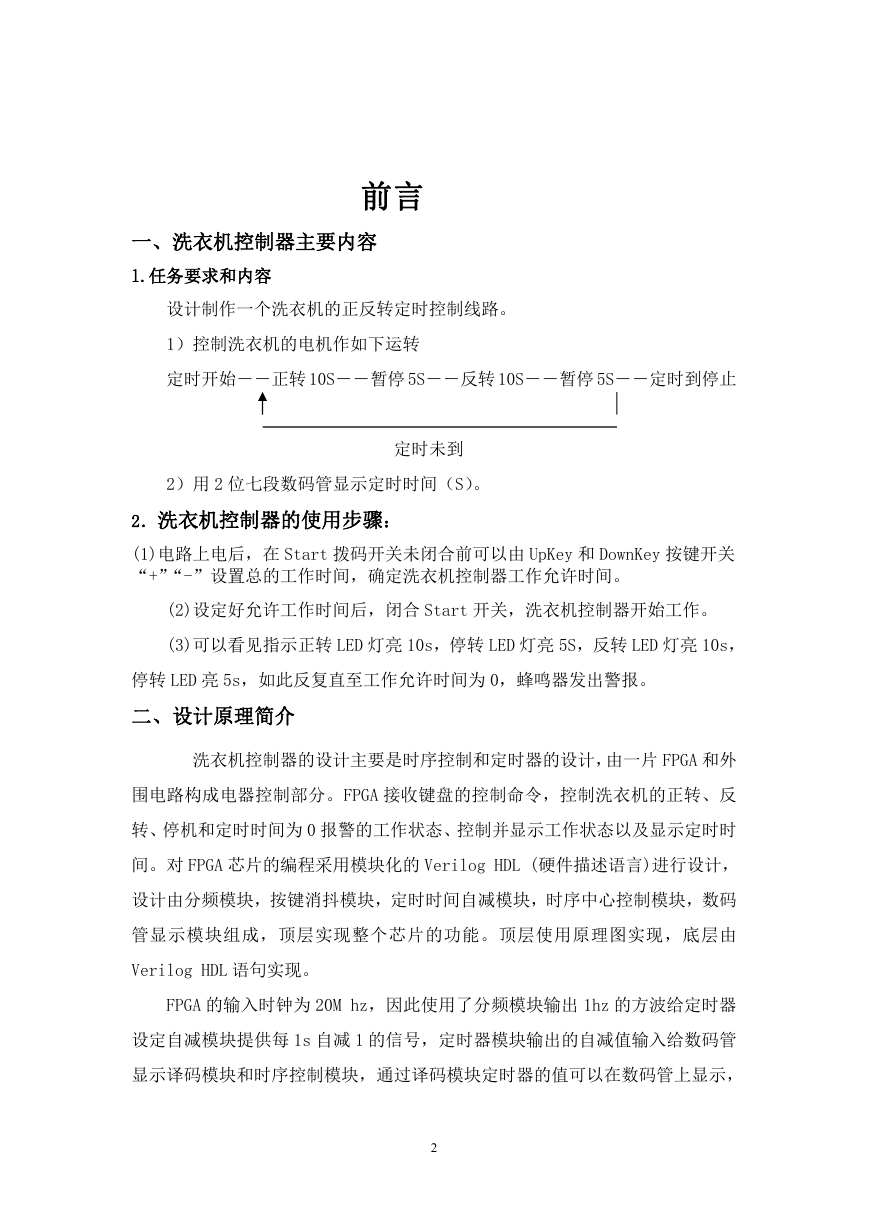

3.1 洗衣机控制器的整体框图及原理:

基于 fpga 的洗衣机控制器电路主要由五大模块组成,分别为按键消抖模块,时

钟分频模块,定时器设定和自减模块,时序中心控制模块,数码管显示译码模块。

具体电路如图 1 所示:

图 1

由于输入时钟为 20M hz,因此使用了分频模块输出 1hz 的方波(中间上方

模块)给定时器设定和自减模块(中间下方模块)提供每 1s 自减 1 的信号,定

时器模块输出的自减值输入给数码管显示译码模块(右下方模块)和时序控制模

4

�

块(右上模块),通过译码模块定时器的值可以在数码管上显示,同时定时器的

值输入到时序控制模块由此可以控制洗衣机的正转、反转、停机和报警工作方式。

按键消抖模块(左下方模块)的作用是为了消除按键抖动而设立的。

3.2、洗衣机控制电路单元模块设计和仿真

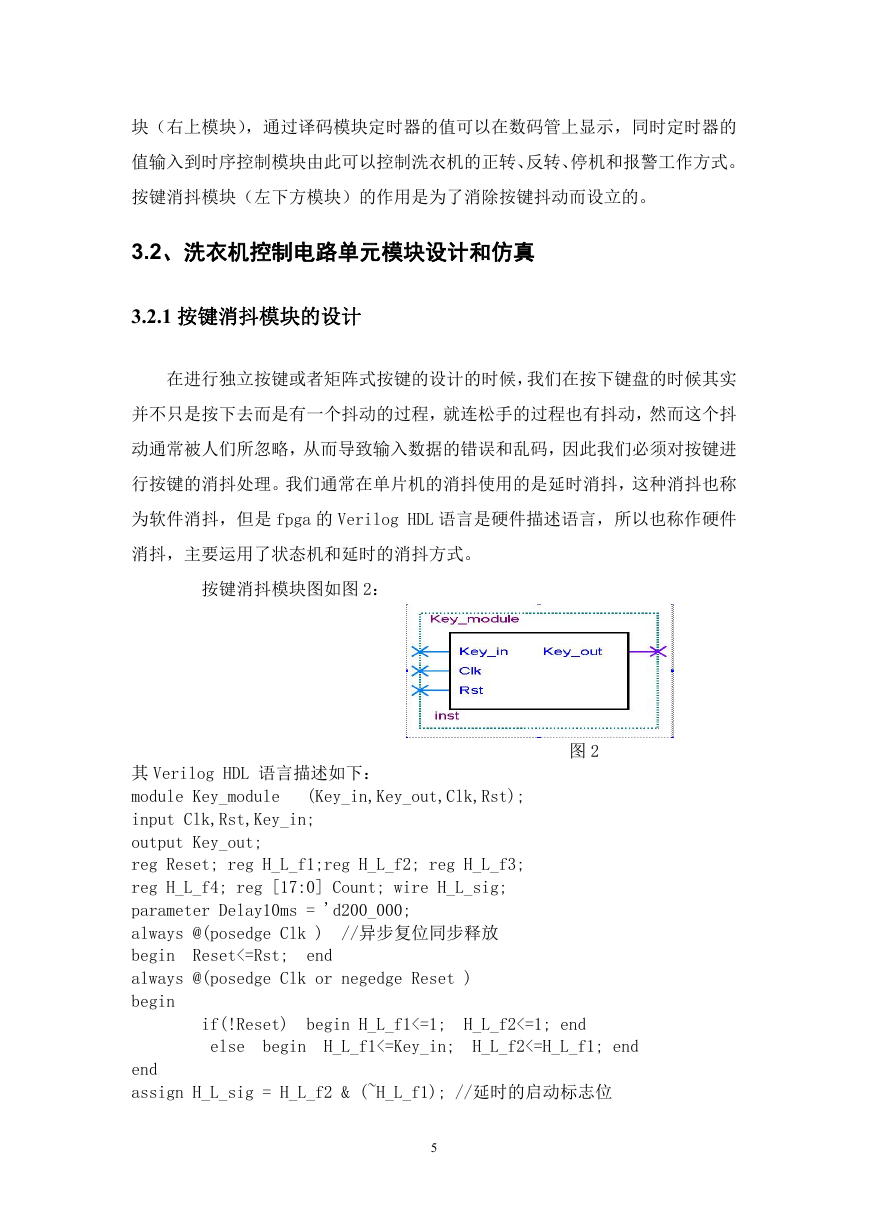

3.2.1 按键消抖模块的设计

在进行独立按键或者矩阵式按键的设计的时候,我们在按下键盘的时候其实

并不只是按下去而是有一个抖动的过程,就连松手的过程也有抖动,然而这个抖

动通常被人们所忽略,从而导致输入数据的错误和乱码,因此我们必须对按键进

行按键的消抖处理。我们通常在单片机的消抖使用的是延时消抖,这种消抖也称

为软件消抖,但是 fpga 的 Verilog HDL 语言是硬件描述语言,所以也称作硬件

消抖,主要运用了状态机和延时的消抖方式。

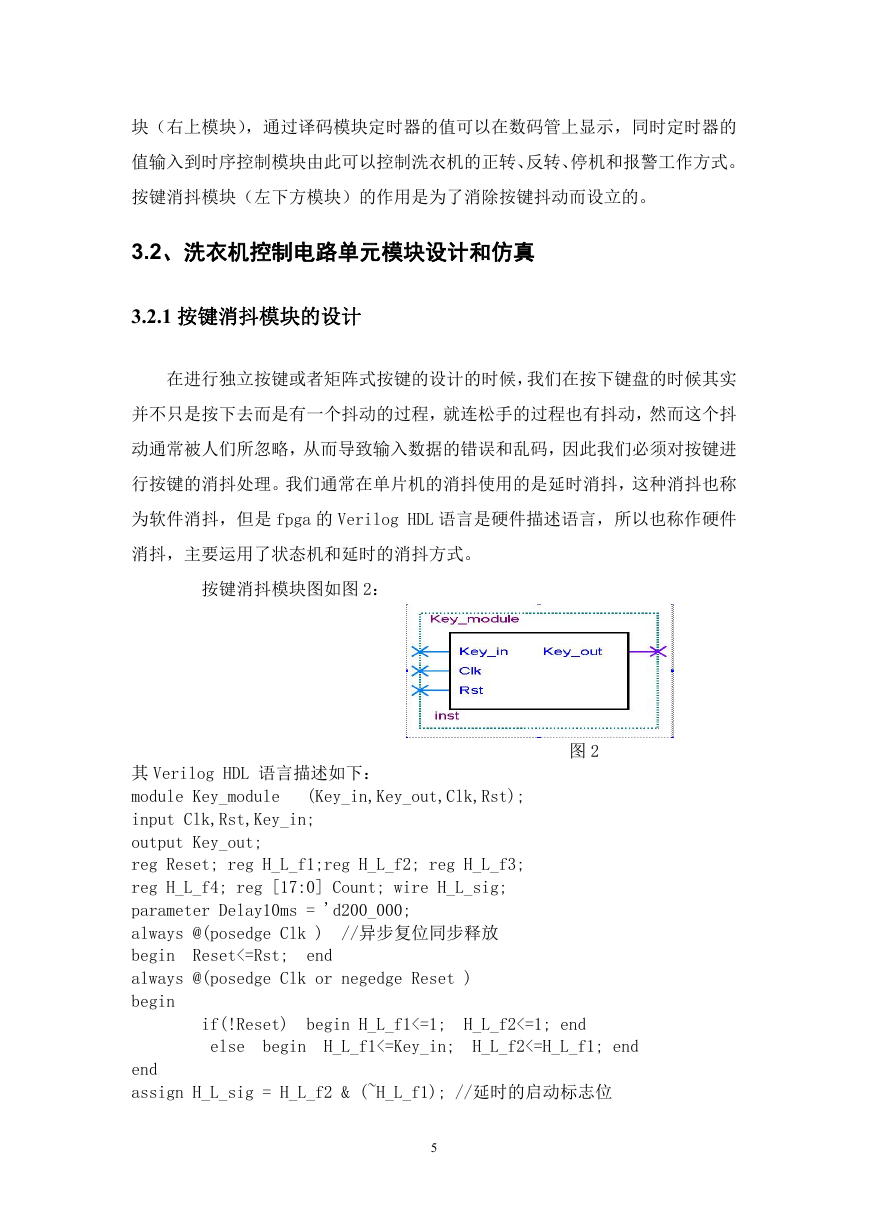

按键消抖模块图如图 2:

图 2

(Key_in,Key_out,Clk,Rst);

其 Verilog HDL 语言描述如下:

module Key_module

input Clk,Rst,Key_in;

output Key_out;

reg Reset; reg H_L_f1;reg H_L_f2; reg H_L_f3;

reg H_L_f4; reg [17:0] Count; wire H_L_sig;

parameter Delay10ms = 'd200_000;

always @(posedge Clk )

begin

always @(posedge Clk or negedge Reset )

begin

//异步复位同步释放

Reset<=Rst;

end

if(!Reset)

begin H_L_f1<=1;

H_L_f2<=1; end

else

begin

H_L_f1<=Key_in;

H_L_f2<=H_L_f1; end

end

assign H_L_sig = H_L_f2 & (~H_L_f1); //延时的启动标志位

5

�

always @(posedge Clk or negedge Reset )

begin

Count<=0;end

if(!Reset)begin

else if(Count == Delay10ms)begin Count<=0; end

else if(H_L_sig)

else begin

Count<=Count+1; end

begin

Count<=0; end

end

always @(posedge Clk or negedge Reset)

begin

if(!Reset) begin H_L_f3<=1;

end

else if(Count == Delay10ms)

begin H_L_f3<=Key_in;

end

end

always @(posedge Clk or negedge Reset )

begin

if(!Reset) begin

H_L_f4<=1; end

else begin H_L_f4<=H_L_f3; end

end

assign Key_out = H_L_f4 & (~H_L_f3);

endmodule

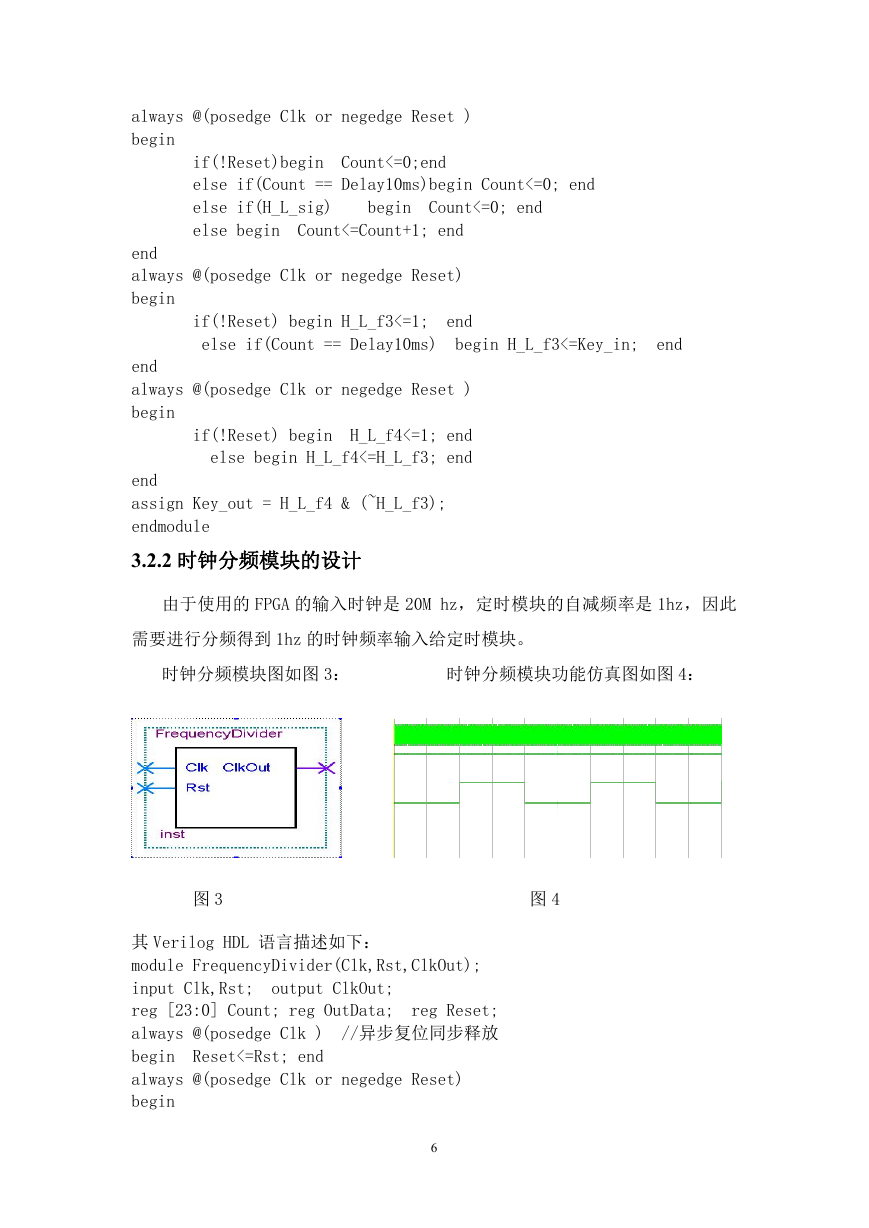

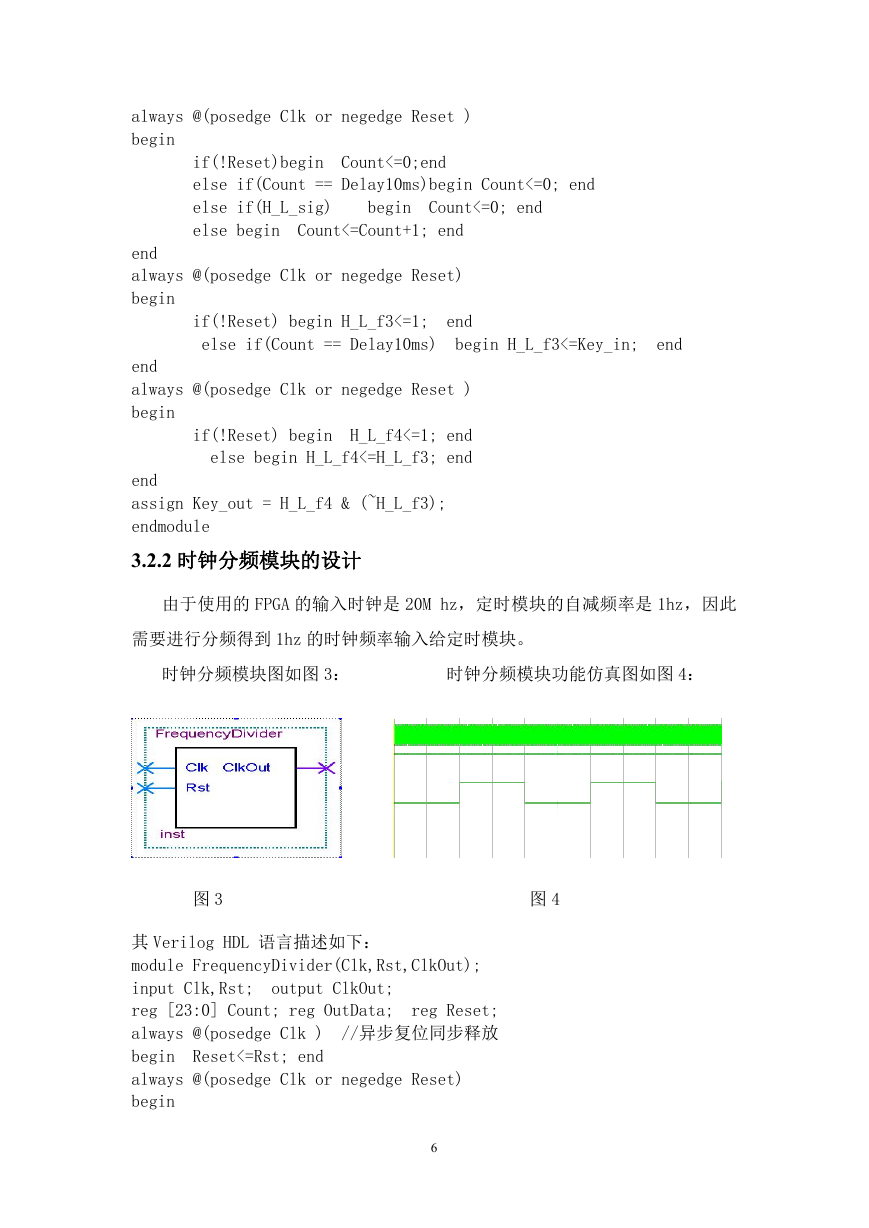

3.2.2 时钟分频模块的设计

由于使用的 FPGA 的输入时钟是 20M hz,定时模块的自减频率是 1hz,因此

需要进行分频得到 1hz 的时钟频率输入给定时模块。

时钟分频模块图如图 3:

时钟分频模块功能仿真图如图 4:

图 3

图 4

其 Verilog HDL 语言描述如下:

module FrequencyDivider(Clk,Rst,ClkOut);

output ClkOut;

input Clk,Rst;

reg [23:0] Count; reg OutData;

always @(posedge Clk )

begin

Reset<=Rst; end

always @(posedge Clk or negedge Reset)

begin

reg Reset;

//异步复位同步释放

6

�

if(!Reset)

else if(Count==24'd10_000_000)

begin

Count<=0; OutData<=0; end

begin

Count<=0;

OutData<=~OutData; end

else

begin

Count<=Count+1'd1; end

end

assign ClkOut=OutData;

endmodule

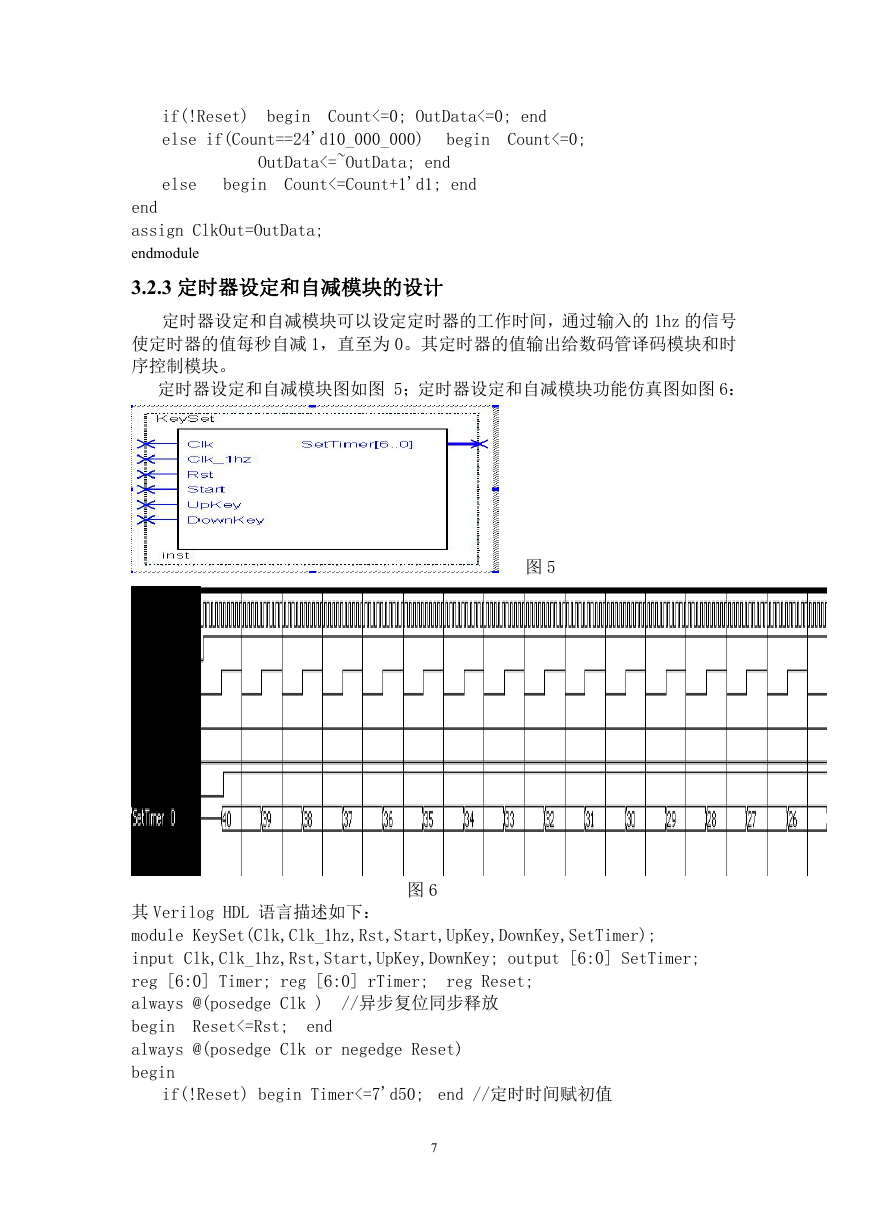

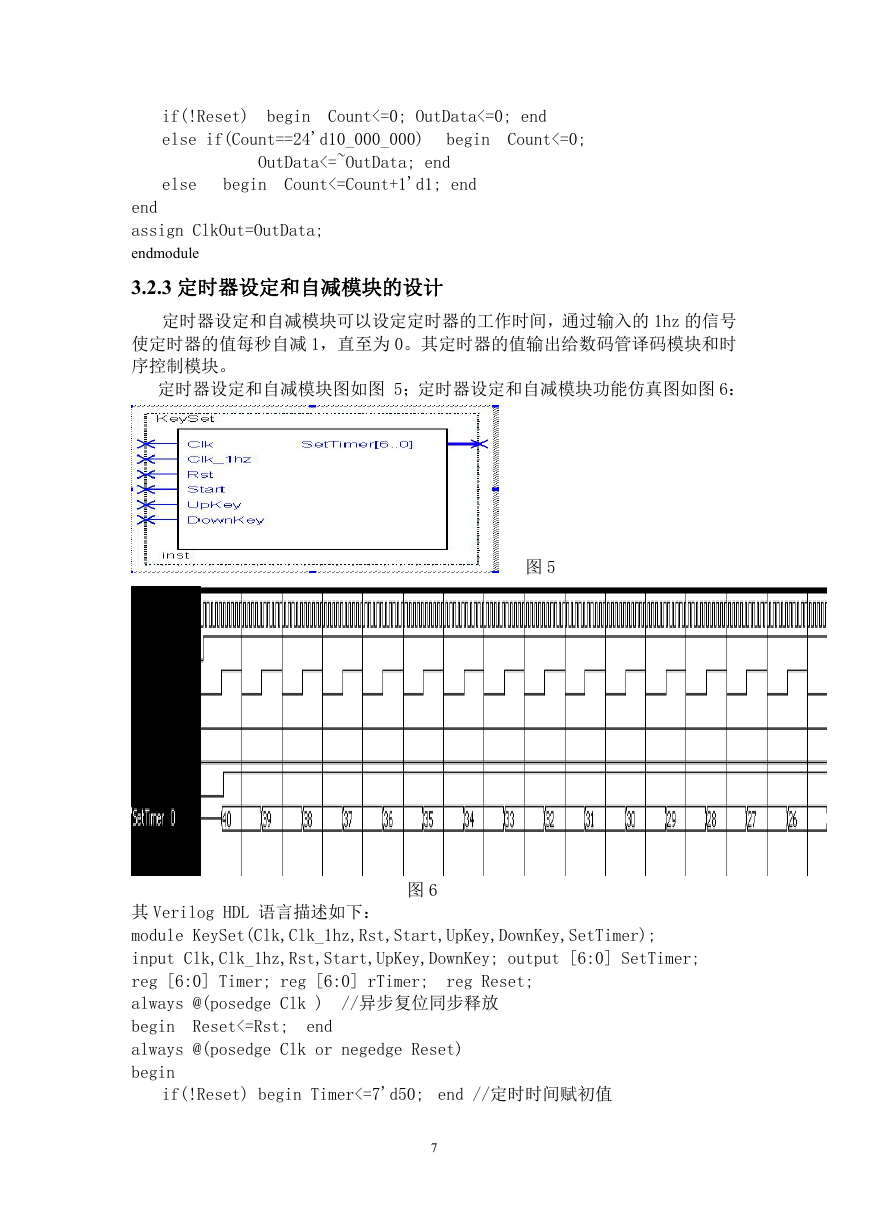

3.2.3 定时器设定和自减模块的设计

定时器设定和自减模块可以设定定时器的工作时间,通过输入的 1hz 的信号

使定时器的值每秒自减 1,直至为 0。其定时器的值输出给数码管译码模块和时

序控制模块。

定时器设定和自减模块图如图 5;定时器设定和自减模块功能仿真图如图 6:

图 5

图 6

其 Verilog HDL 语言描述如下:

module KeySet(Clk,Clk_1hz,Rst,Start,UpKey,DownKey,SetTimer);

input Clk,Clk_1hz,Rst,Start,UpKey,DownKey; output [6:0] SetTimer;

reg [6:0] Timer; reg [6:0] rTimer;

always @(posedge Clk )

begin

always @(posedge Clk or negedge Reset)

begin

//异步复位同步释放

Reset<=Rst;

reg Reset;

end

if(!Reset) begin Timer<=7'd50; end //定时时间赋初值

7

�

else if(Start) begin

else if(DownKey) begin Timer<=Timer-1'b1; end end

if(UpKey) begin Timer<=Timer+1'b1; end

// 时 间 减 一

end

always @(posedge Clk_1hz)

begin

//1s 信号输入

rTimer<=Timer;

if(rTimer==7'd0) begin

else

begin

rTimer<=rTimer-1'b1;

if(!Start)

begin

rTimer<=0;

end

//时间到 0 保持以免错误

end

end//每秒减一

end

assign SetTimer=rTimer;

endmodule

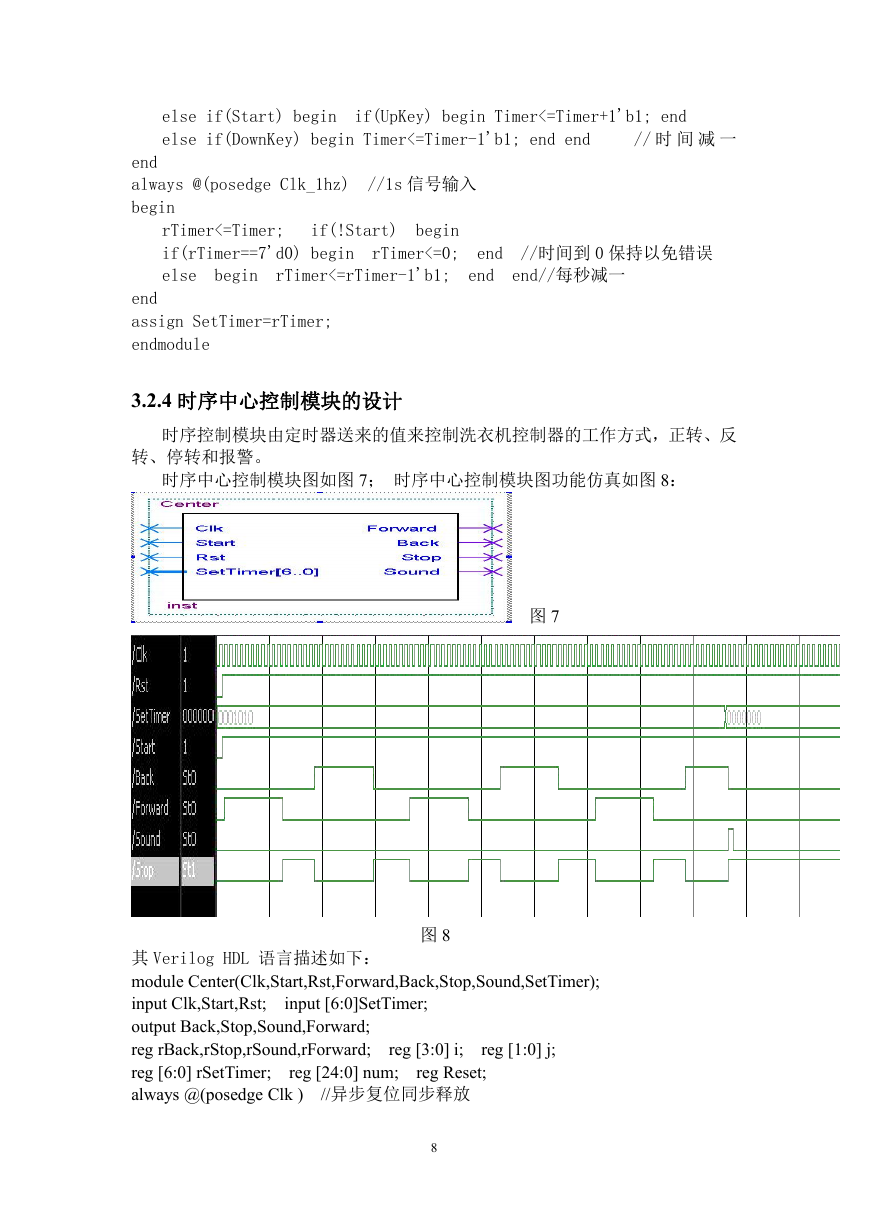

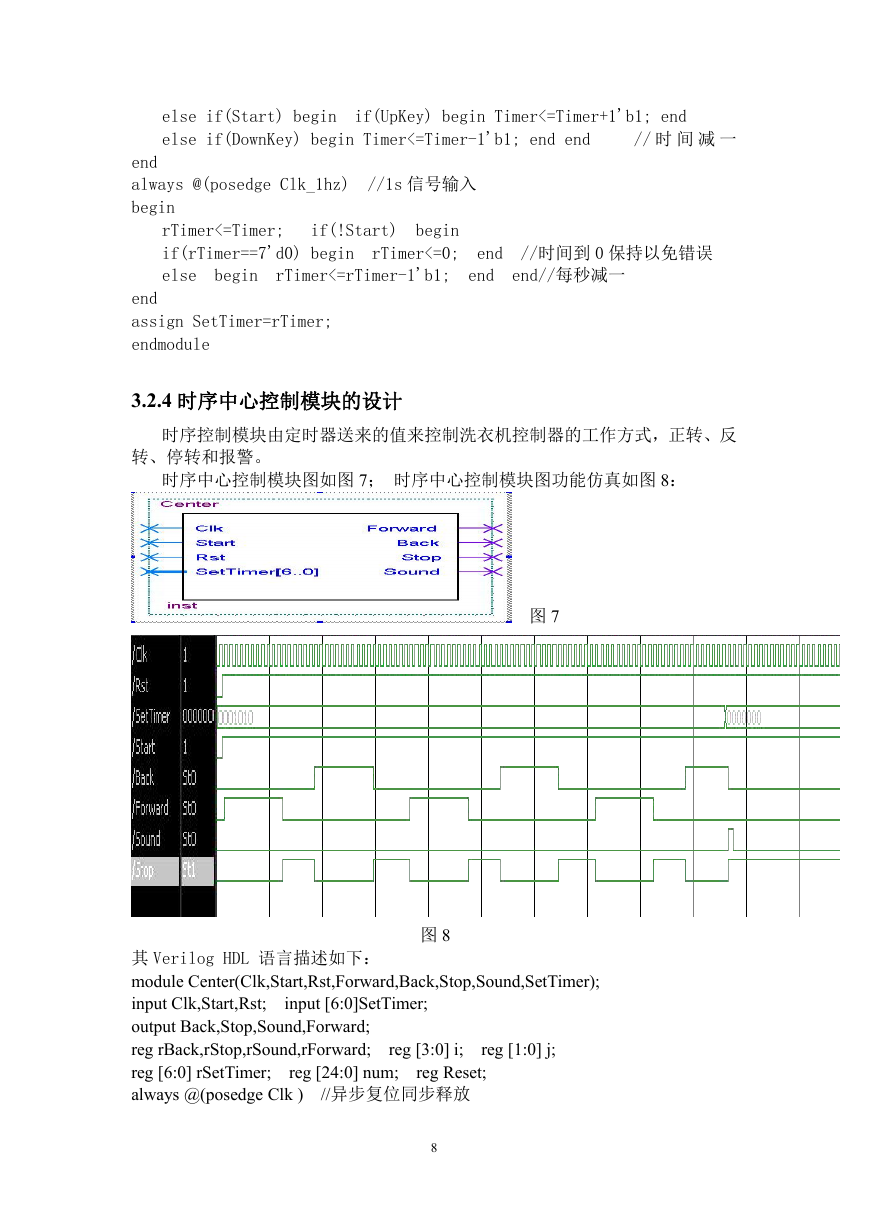

3.2.4 时序中心控制模块的设计

时序控制模块由定时器送来的值来控制洗衣机控制器的工作方式,正转、反

转、停转和报警。

时序中心控制模块图如图 7; 时序中心控制模块图功能仿真如图 8:

图 7

图 8

其 Verilog HDL 语言描述如下:

module Center(Clk,Start,Rst,Forward,Back,Stop,Sound,SetTimer);

input Clk,Start,Rst;

output Back,Stop,Sound,Forward;

reg rBack,rStop,rSound,rForward;

reg [6:0] rSetTimer;

always @(posedge Clk )

//异步复位同步释放

input [6:0]SetTimer;

reg [24:0] num;

reg Reset;

reg [3:0] i;

reg [1:0] j;

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc