现代计算机组成原理实验讲义

杭州康芯电子有限公司

www.kx-soc.com

�

目 录

前 言 .....................................................................................1

实验一 QUARTUSII EDA 工具与 VHDL 基础实验 ...................................................4

1-1. 应用 QuartusII 完成基本组合电路设计 ................................................4

1-2. 应用 QuartusII 完成基本时序电路的设计 ..............................................5

1-3. 设计含异步清 0 和同步时钟使能的加法计数器 ..........................................6

1-4. 7 段数码显示译码器设计 ............................................................7

1-5. 8 位数码扫描显示电路设计 ..........................................................8

1-6. 数控分频器的设计 ..................................................................9

1-7. 32 位并进/并出移位寄存器设计 .....................................................10

1-8. 在 QuartusII 中用原理图输入法设计 8 位全加器 .......................................10

1-9. 在 QuartusII 中用原理图输入法设计较复杂数字系统 ...................................11

1-10. 用 QuartusII 设计正弦信号发生器 ..................................................11

1-11. 8 位 16 进制频率计设计 ...........................................................13

1-12. 序列检测器设计 ..................................................................16

1-13. VHDL 状态机 A/D 采样控制电路实现 .................................................17

实验二 运算器组成实验 .....................................................................19

1.算术逻辑运算实验 ...................................................................19

2.带进位算术运算实验 .................................................................22

3. 移位运算器实验 .....................................................................23

实验三 存储器实验 .........................................................................24

1、FPGA 中 LPM_ROM 定制与读出实验 ......................................................24

2.FPGA 中 LPM_RAM 读写实验 ............................................................26

3.FIFO 定制与读/写实验 ...............................................................27

4.FPGA 与外部 16 位 RAM 接口实验 .......................................................28

实验四 微控制器实验 .......................................................................30

1 节拍脉冲发生器时序电路实验 ..........................................................30

2. 程序计数器 PC 与地址寄存器 AR 实验 ...................................................32

3.微控制器组成实验 ....................................................................33

实验五 总线控制实验 .......................................................................36

实验六 基本模型机设计与实现 ...............................................................38

实验七 带移位运算的模型机设计与实现 .......................................................47

实验八 复杂模型机的设计与实现 .............................................................52

实验九.较复杂 CPU 设计示例 ................................................................56

实验十.16 位精简指令 CPU 设计实验 .........................................................58

实验十一 32 位 NIOS CPU 嵌入式系统软硬件设计实验 ..........................................67

1 NIOS 软硬件开发流程 ................................................................67

3 SOPC 整体系统生成 ..................................................................72

4 Nios 硬件系统生成 ..................................................................72

实验十二 32 位 NIOS CPU 测控系统串口接收程序设计 ..........................................75

实验十三 GSM 短信模块程序设计 ............................................................75

实验十四 基于 32 位 NIOS CPU 的秒表程序设计 ...............................................76

实验十五 NIOS AVALON SLAVE 总线外设(PWM 模块)设计 ........................................79

实验十六 NIOS AVALON SLAVE 总线外设(数码管动态扫描显示模块)设计..........................79

实验十七 基于 NIOS 的 VGA 显示终端设计 .....................................................79

实验十八 DMA 应用和俄罗斯方块游戏设计 ....................................................80

实验十九 为 NIOS 嵌入式系统增加算法加速协处理模块控制指令 ..................................80

实验二十. 计算机体系结构实验 ..............................................................80

实验二十一. 89K51 单片机核应用系统软硬件设计实验 ..........................................80

8051/89C51 CPU 核及片上系统设计实验

- - 1

�

4-1 基本 CPU 软硬件设计

4-2 8051/89C51 单片机核,等精度频率计与液晶显示实验

4-3 8051/89C51 单片机核,等精度频率计与数码管显示实验

附录:GW48 EDA/SOPC 主系统使用说明 ........................................................89

- - 2

�

前 言

随着大规模集成电路技术和计算机技术的不断发展,在涉及通信、国防、工业自动化、计算机应用、

仪器仪表等领域的电子系统设计工作中,现场可编程(FPGA)技术含量正以惊人的速度上升。电子类的新

技术项目的开发也更多地依赖于 FPGA 技术的应用,特别是随着 VHDL 等硬件描述语言综合工具功能和

性能的提高,计算机中许多重要的元件,包括 CPU 都用硬件描述语言来设计和表达,许多 CPU(如 8051

单片机、8086 等),硬核嵌入式系统(如 ARM、Excalibue 系列 FPGA)、软核嵌入式系统(如 Nios),微

机 CPU,乃至整个计算机系统都用 FPGA 来实现,即所谓的单片系统:SOC 和 SOPC(System On a Chip、

System On a Programmerble Chip )。计算机和 CPU 的设计技术及其现方法进入了一个全新的时代!不但

如此,传统的 CPU 结构模式,纽曼结构和哈佛结构正在受到巨大的挑战。

例如,美国赢通系统公司(Wincom Systems)推出一款令人惊叹的服务器,其核心部分由 FPGA 完成

的超强功能 CPU。该系统工作能力超过 50 台戴尔或 IBM 计算机,或 Sun Microsytems 公司的服务器。该

服务器的处理速度要比传统服务器快 50 到 300 倍。我们知道,传统的个人电脑及服务器通常采用英特尔的

奔腾处理器或 SUN 公司的 SPARC 芯片作为中央处理单元,而赢通的这一产品却没有采用微处理器,而是

由 FPGA 芯片驱动。FPGA 芯片的运行速度比奔腾处理器慢,但可并行处理多项任务,而微处理器一次仅

能处理一项任务。因此,赢通公司的服务器只需配置几个价格仅为 2000 多美元的 FPGA 芯片,便可击败

SUN 公司的服务器或采用英特尔处理器的电脑。

50 多年前,匈牙利数学家纽曼(John von Neumann)提出了电脑的设计构想:通过中央处理器从存储

器中存取数据,并逐一处理各项任务。现在,通过采用 FPGA,SOPC 及顺序与并行方式相结合的软核嵌

入式系统取代传统微处理器,导致 Xlinx 的 CEO Willem Roelandts 所说的“由纽曼提出的电脑架构已经走

到尽头”,“可编程芯片将掀起下一轮应用高潮。

FPGA 芯片以操作灵活著称,可以重复擦写无限次,而微处理器均采用固定电路,只能进行一次设计。

设计人员可通过改变 FPGA 中晶体管的开关状态对电路进行重写,即重配置。从而,尽管 FPGA 芯片的时

钟频率要低于奔腾处理器,但是由于 FPGA 芯片可并行处理各种不同的运算,所以可完成许多复杂的任务。

例如网页显示,全球天气建模及基因组合核对等,而且处理速度比奔腾处理器或数字信号处理器快得多。

戴尔和 SUN 公司生产的某些标准服务器也采用了 ALTERA 公司的 FPGA 芯片。时代逻辑公司对这些

标准服务器加以改进之后,生产了一种用于基因研究的高速处理设备。时代逻辑公司总监 Christopher

Hoover 说该设备比原来的产品至少快 1000 倍。

美国的 Annapolis Micro Systems 公司在其电脑芯片电路板中也集成了 FPGA 芯片,以便提高其产品性

能。该公司首席执行官 Jane Donaldson 指出,相关产品的销售量与前两年相比翻了一番。

IBM 和 Xilinx 公司正在合力开发一种混合芯片,以整合前者的 PowerPC 微处理器和后者的 FPGA 芯

片。这种芯片的好处是:一台网络服务器的 FPGA 部分可以根据不同的标准进行订制,而不用为每个国家

开发一种新的芯片。

美国 Star Bridge Systems 公司也声称已在进行一项技术尝试,即采用 FPGA 芯片和该公司自己的 Viva

编程语言开发出“超级电脑(hypercomputer)”,对该超级电脑进行测试的美国国家航空航天局(NASA)

科学家表示“其运行速度无与伦比,这一产品的性能令人过目难忘”。

超级电脑是科技世界中的极品:售价奇高、速度飞快、集成了数以千计的微处理器。但这种超级电脑

也浪费了非常多的芯片资源,每个处理器只能进行单任务操作,大部分功能难以充分发挥。现在有了另一

种更为简洁的设计:设计工程师采用 FPGA 芯片来武装超级电脑,取代了原先大量的英特尔奔腾处理器。

经过使用硬件描述语言和相关软件语言的设计,FPGA 芯片可并行处理多项任务,从而使所有电路都能随

时发挥作用。又由于 FPGA 芯片可以反复编程培植,而且几乎可瞬时完成。例如可通过利用 FPGA 的重配

置功能,在某一时刻它可以用来预报全球天气状况,而下一时刻又可根据某公司做的主要利率对冲情况来

评估债券市场的风险,或是转而去做图象信息处理。

其它公司或机构的研究人员,如美国加州大学伯克利分校(University of California, Berkeley)和杨百

翰大学(Brigham Young University)的研究员也正在设计基于 FPGA 的电脑,这些电脑可在运行中实现动

- - 1

�

态重配置。这对定位危险目标等军事应用和面容识别一类的计算密集型安全应用十分有用。

不言而喻,全新的计算机设计技术和实现技术向传统的计算机组成原理的教学内容和实验方式提出尖

锐的挑战。相形之下,传统的计算机组成原理实验方式已显得十分不合时宜。显然,传统的实验方式,就

教学实验内容上看,与现代的计算机组成模式、理念、基本理论和构成形式及方案上都无任何吻合之处;

就实验方法上看,完全是一种脱离现代计算机实际组成技术和测试技术(现代测试技术包括 JTAG、嵌入

式逻辑分析仪等)的,由实验系统设计者一相情愿的构建,难免引出诸多对初学者产生误导的实验方法;

就实验模式和模型上看,与真实的现代计算机组成和构建方式相去更远。现代计算机,包括嵌入式系统绝

不可能是由一大堆独立的、低速的、传统逻辑器件连接而成,而是由硬件描述语言来表达,由 ASIC 或 FPGA

来实现的计算机系统;就教学实验内容上看,传统的计算机组成原理实验只能模拟普通 CPU 的工作,然而

现代计算机应用领域,RSIC 精简指令 CPU 的设计和应用正以前所未有的巨大规模向前发展,当前,无论

在开发技术的投入还是应用市场的开拓都远远超过了基于传统构架的 CPU(国内绝大多数学校仍然基于此

CPU 的教学)。

不久前,清华大学对美国一些知名大学计算机实验室(如斯坦富大学)的调研表明,那里计算机方面

的硬件实验,包括计算机组成原理实验早已不用那种传统接插式实验,而是全部采用 EDA 技术进行所有

的软硬件实验!!!

显然,使用大规模 FPGA、EDA 软件工具和 IEEE 标准硬件描述语言构建的现代计算机组成原理实验

系统取代传统的计算机组成原理实验已成为势在必行。

利用 FPGA 技术,在实验中能方便灵活地设计出简单完整的CPU模型机。基于查找表硬件结构的商

用 FPGA 是当前进行快速系统原型设计最流行的 ASIC 手段。ALTERA 的 ACEX 系列 FPGA 产品具有片上

EAB,可以构成构成各种类型的存储器结构,利用在其内部的 LPM 可以实现微程序控制和管理复杂逻辑

电路。

现代计算机组成原理实验为实验者提供了全新的学习平台,彻底克服传统组成原理实验项目与实际

CPU 设计技术完全脱钩,学用脱节,甚至误导的缺陷。让学生有机会接触到最新的计算机组成与设计方面

的知识,使学习与工程实际相结合。

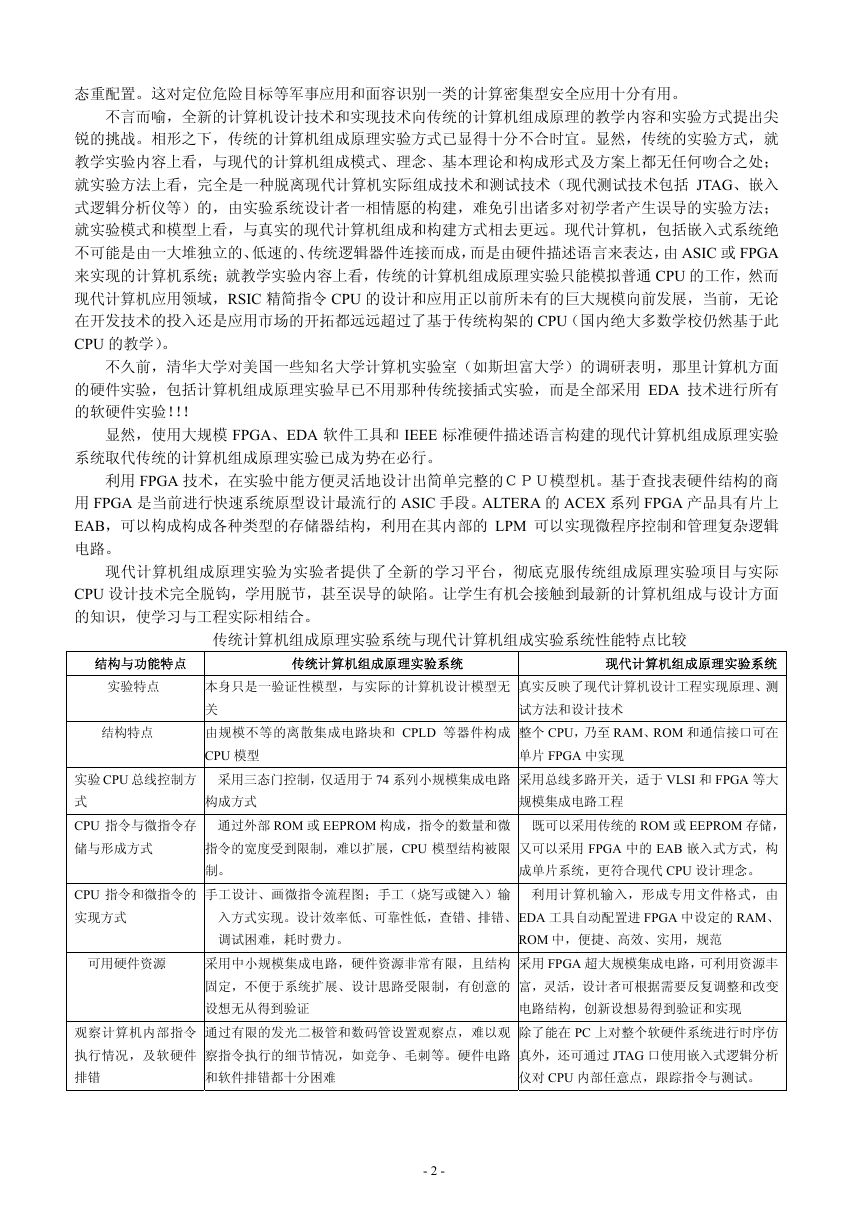

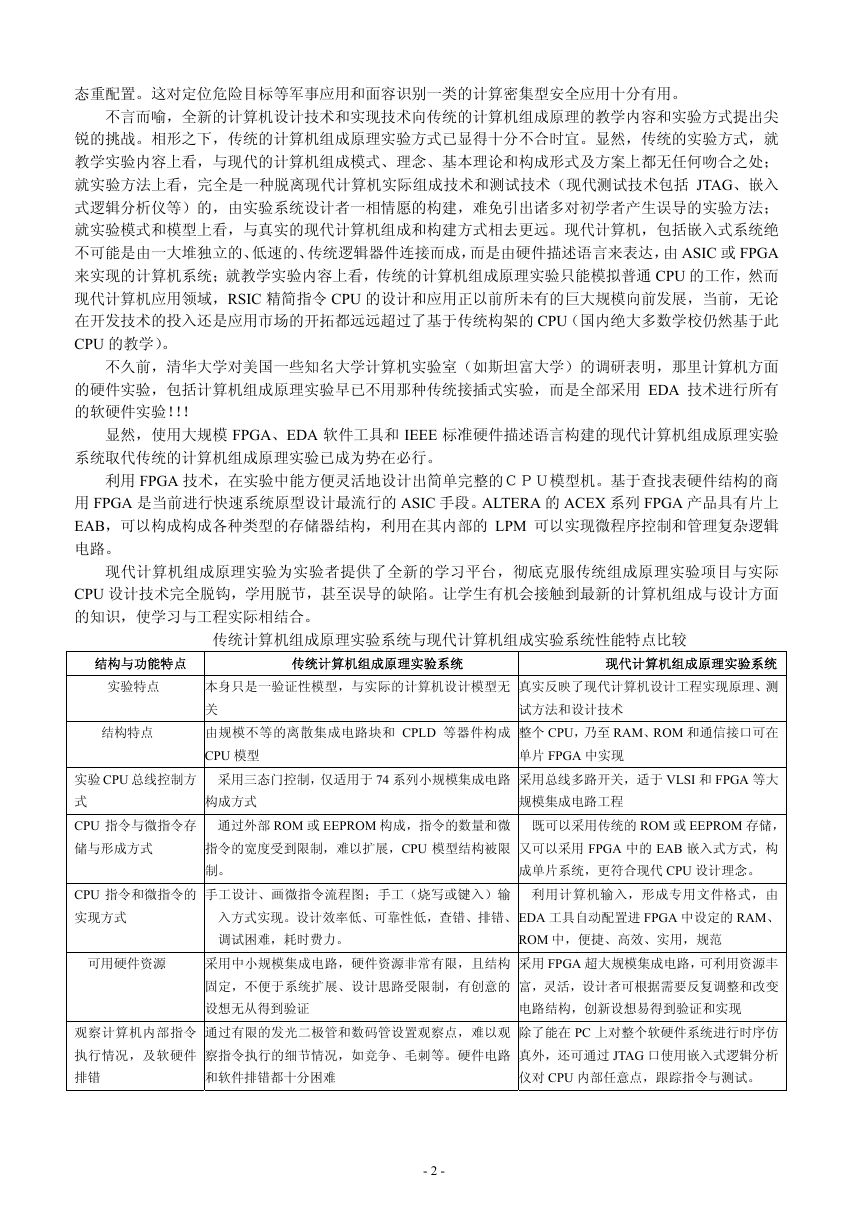

结构与功能特点

实验特点

结构特点

实验 CPU 总线控制方

式

CPU 指令与微指令存

储与形成方式

CPU 指令和微指令的

实现方式

传统计算机组成原理实验系统与现代计算机组成实验系统性能特点比较

传统计算机组成原理实验系统

现代计算机组成原理实验系统

本身只是一验证性模型,与实际的计算机设计模型无

关

由规模不等的离散集成电路块和 CPLD 等器件构成

CPU 模型

采用三态门控制,仅适用于 74 系列小规模集成电路

构成方式

真实反映了现代计算机设计工程实现原理、测

试方法和设计技术

整个 CPU,乃至 RAM、ROM 和通信接口可在

单片 FPGA 中实现

采用总线多路开关,适于 VLSI 和 FPGA 等大

规模集成电路工程

通过外部 ROM 或 EEPROM 构成,指令的数量和微

指令的宽度受到限制,难以扩展,CPU 模型结构被限

制。

既可以采用传统的 ROM 或 EEPROM 存储,

又可以采用 FPGA 中的 EAB 嵌入式方式,构

成单片系统,更符合现代 CPU 设计理念。

手工设计、画微指令流程图;手工(烧写或键入)输

入方式实现。设计效率低、可靠性低,查错、排错、

调试困难,耗时费力。

利用计算机输入,形成专用文件格式,由

EDA 工具自动配置进 FPGA 中设定的 RAM、

ROM 中,便捷、高效、实用,规范

采用 FPGA 超大规模集成电路,可利用资源丰

富,灵活,设计者可根据需要反复调整和改变

电路结构,创新设想易得到验证和实现

除了能在 PC 上对整个软硬件系统进行时序仿

真外,还可通过 JTAG 口使用嵌入式逻辑分析

仪对 CPU 内部任意点,跟踪指令与测试。

可用硬件资源

采用中小规模集成电路,硬件资源非常有限,且结构

固定,不便于系统扩展、设计思路受限制,有创意的

设想无从得到验证

观察计算机内部指令

通过有限的发光二极管和数码管设置观察点,难以观

执行情况,及软硬件

排错

察指令执行的细节情况,如竞争、毛刺等。硬件电路

和软件排错都十分困难

- - 2

�

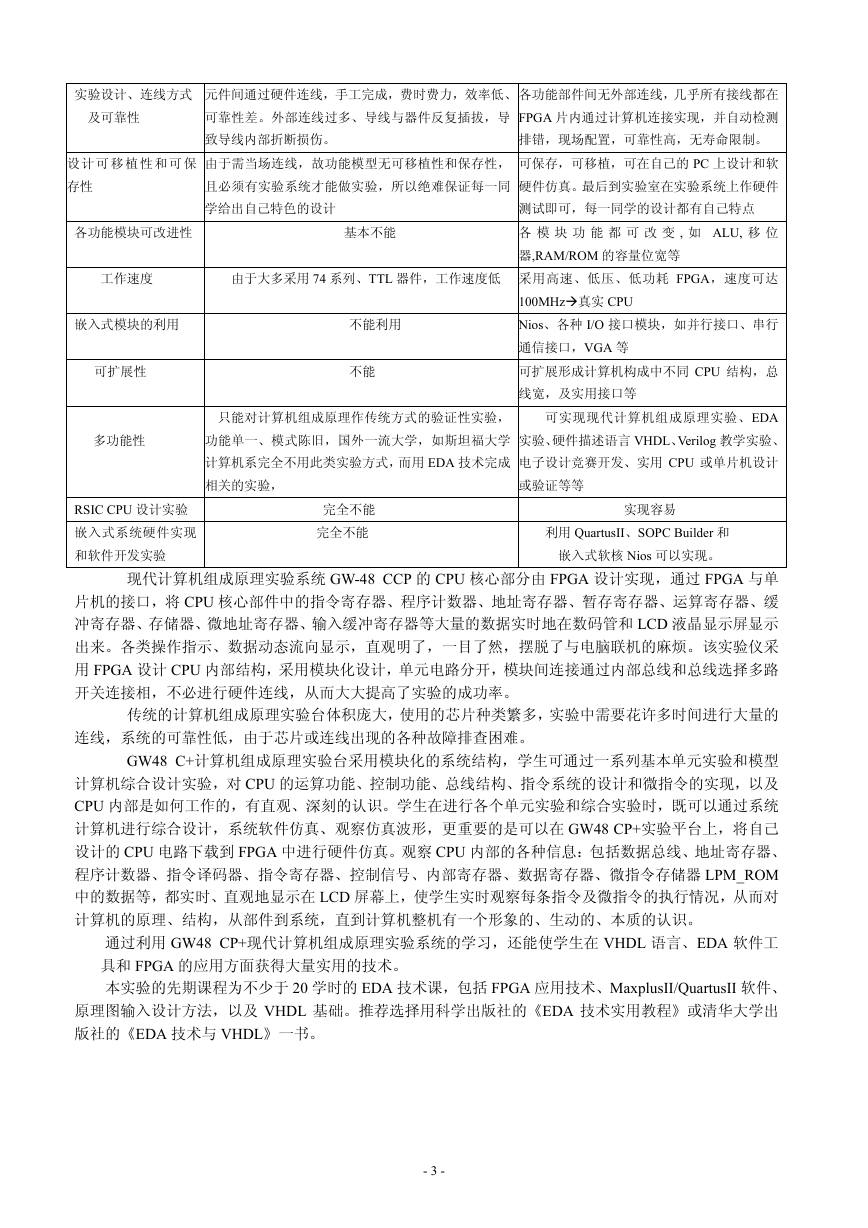

实验设计、连线方式

元件间通过硬件连线,手工完成,费时费力,效率低、

及可靠性

设 计 可 移 植 性 和 可 保

存性

可靠性差。外部连线过多、导线与器件反复插拔,导

致导线内部折断损伤。

由于需当场连线,故功能模型无可移植性和保存性,

且必须有实验系统才能做实验,所以绝难保证每一同

学给出自己特色的设计

各功能模块可改进性

基本不能

各功能部件间无外部连线,几乎所有接线都在

FPGA 片内通过计算机连接实现,并自动检测

排错,现场配置,可靠性高,无寿命限制。

可保存,可移植,可在自己的 PC 上设计和软

硬件仿真。最后到实验室在实验系统上作硬件

测试即可,每一同学的设计都有自己特点

各 模 块 功 能 都 可 改 变 , 如 ALU, 移 位

器,RAM/ROM 的容量位宽等

工作速度

由于大多采用 74 系列、TTL 器件,工作速度低 采用高速、低压、低功耗 FPGA,速度可达

嵌入式模块的利用

不能利用

可扩展性

不能

多功能性

RSIC CPU 设计实验

嵌入式系统硬件实现

和软件开发实验

只能对计算机组成原理作传统方式的验证性实验,

功能单一、模式陈旧,国外一流大学,如斯坦福大学

计算机系完全不用此类实验方式,而用 EDA 技术完成

相关的实验,

完全不能

完全不能

100MHz真实 CPU

Nios、各种 I/O 接口模块,如并行接口、串行

通信接口,VGA 等

可扩展形成计算机构成中不同 CPU 结构,总

线宽,及实用接口等

可实现现代计算机组成原理实验、EDA

实验、硬件描述语言 VHDL、Verilog 教学实验、

电子设计竞赛开发、实用 CPU 或单片机设计

或验证等等

实现容易

利用 QuartusII、SOPC Builder 和

嵌入式软核 Nios 可以实现。

现代计算机组成原理实验系统 GW-48 CCP 的 CPU 核心部分由 FPGA 设计实现,通过 FPGA 与单

片机的接口,将 CPU 核心部件中的指令寄存器、程序计数器、地址寄存器、暂存寄存器、运算寄存器、缓

冲寄存器、存储器、微地址寄存器、输入缓冲寄存器等大量的数据实时地在数码管和 LCD 液晶显示屏显示

出来。各类操作指示、数据动态流向显示,直观明了,一目了然,摆脱了与电脑联机的麻烦。该实验仪采

用 FPGA 设计 CPU 内部结构,采用模块化设计,单元电路分开,模块间连接通过内部总线和总线选择多路

开关连接相,不必进行硬件连线,从而大大提高了实验的成功率。

传统的计算机组成原理实验台体积庞大,使用的芯片种类繁多,实验中需要花许多时间进行大量的

连线,系统的可靠性低,由于芯片或连线出现的各种故障排查困难。

GW48 C+计算机组成原理实验台采用模块化的系统结构,学生可通过一系列基本单元实验和模型

计算机综合设计实验,对 CPU 的运算功能、控制功能、总线结构、指令系统的设计和微指令的实现,以及

CPU 内部是如何工作的,有直观、深刻的认识。学生在进行各个单元实验和综合实验时,既可以通过系统

计算机进行综合设计,系统软件仿真、观察仿真波形,更重要的是可以在 GW48 CP+实验平台上,将自己

设计的 CPU 电路下载到 FPGA 中进行硬件仿真。观察 CPU 内部的各种信息:包括数据总线、地址寄存器、

程序计数器、指令译码器、指令寄存器、控制信号、内部寄存器、数据寄存器、微指令存储器 LPM_ROM

中的数据等,都实时、直观地显示在 LCD 屏幕上,使学生实时观察每条指令及微指令的执行情况,从而对

计算机的原理、结构,从部件到系统,直到计算机整机有一个形象的、生动的、本质的认识。

通过利用 GW48 CP+现代计算机组成原理实验系统的学习,还能使学生在 VHDL 语言、EDA 软件工

具和 FPGA 的应用方面获得大量实用的技术。

本实验的先期课程为不少于 20 学时的 EDA 技术课,包括 FPGA 应用技术、MaxplusII/QuartusII 软件、

原理图输入设计方法,以及 VHDL 基础。推荐选择用科学出版社的《EDA 技术实用教程》或清华大学出

版社的《EDA 技术与 VHDL》一书。

- - 3

�

实验一 QuartusII EDA 工具与 VHDL 基础实验

本实验中所配的 13 个实验主要作为计算机组成原理实验的前期练习,以便熟悉 VHDL 语言、原理图

输入方法,以及 EDA 工具和 EDA 实验系统的使用方法。主要参考清华大学出版社的《EDA 技术与 VHDL》

或《现代计算机组成原理》一书。

实验内容和数量可根据实际需要选择,每一个实验,在所配的光盘中都有对应的实验示例和实验指导

课件。

1-1. 应用 QuartusII 完成基本组合电路设计

《示例程序和实验指导课件位置》:

\Experiments\Expmt1\chpt4\Ep1c6_41_mux21A\ 工程 mux21A

(1) 实验目的:熟悉 QuartusⅡ的 VHDL 文本设计流程全过程,学习简单组合电路的设计、多层次电路

设计、仿真和硬件测试。

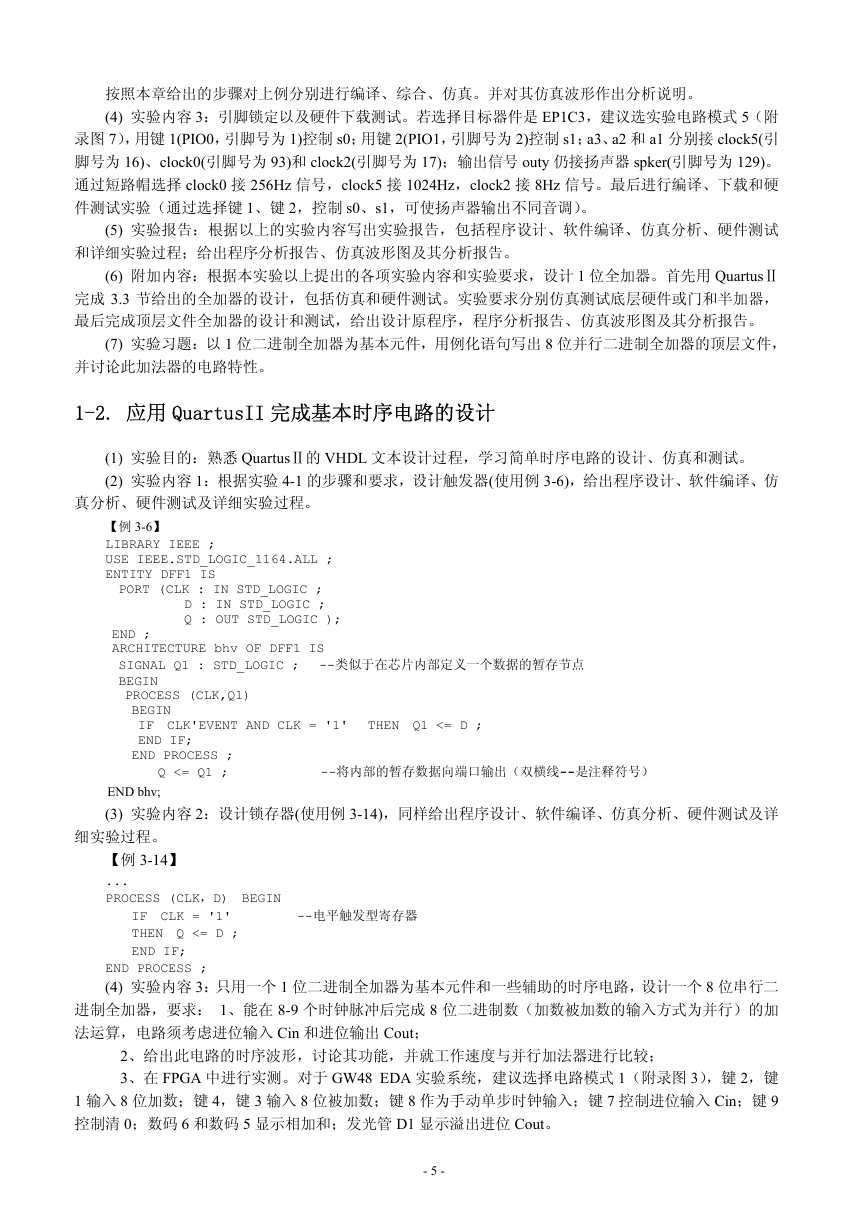

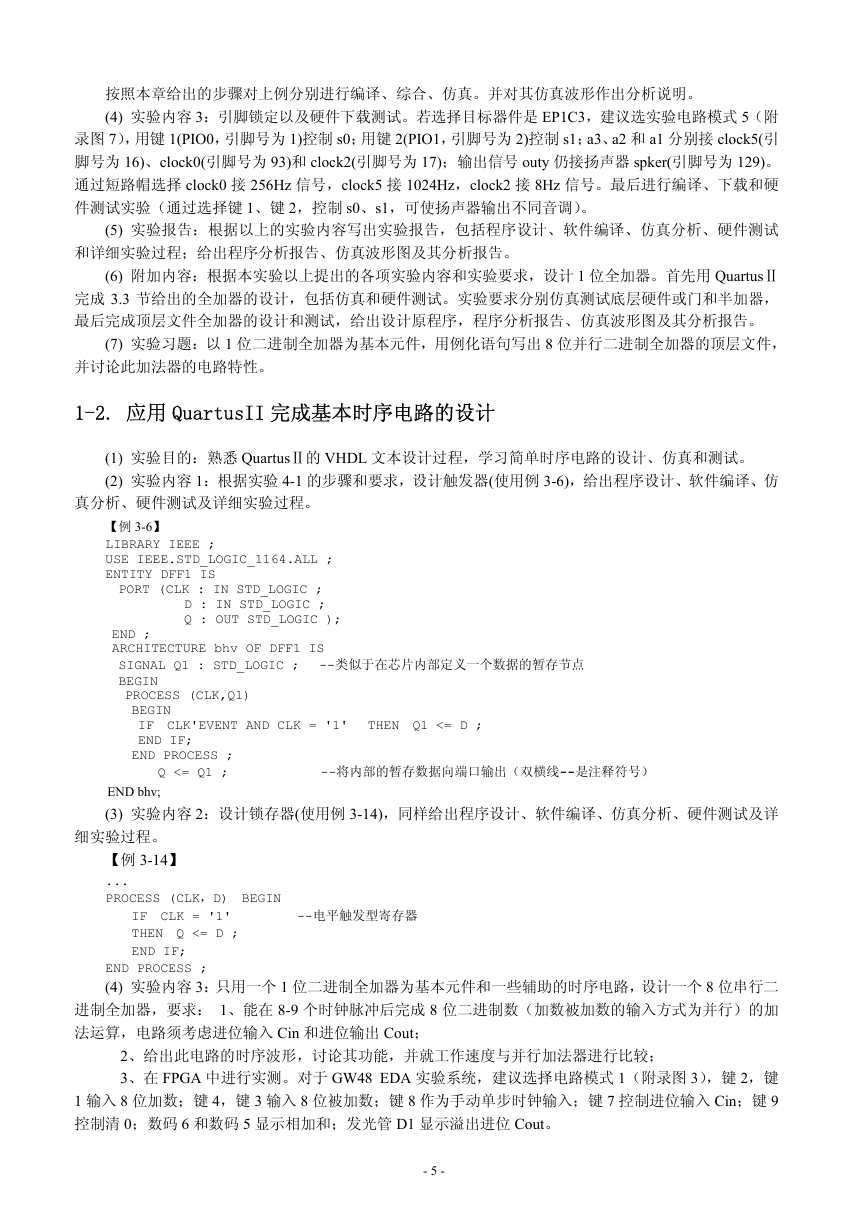

(2) 实验内容 1:首先利用 QuartusⅡ完成 2 选 1 多路选择器(例 3-3)的文本编辑输入(mux21a.vhd)和

仿真测试等步骤,给出图 3-3 所示的仿真波形。最后在实验系统上进行硬件测试,验证本项设计的功能。

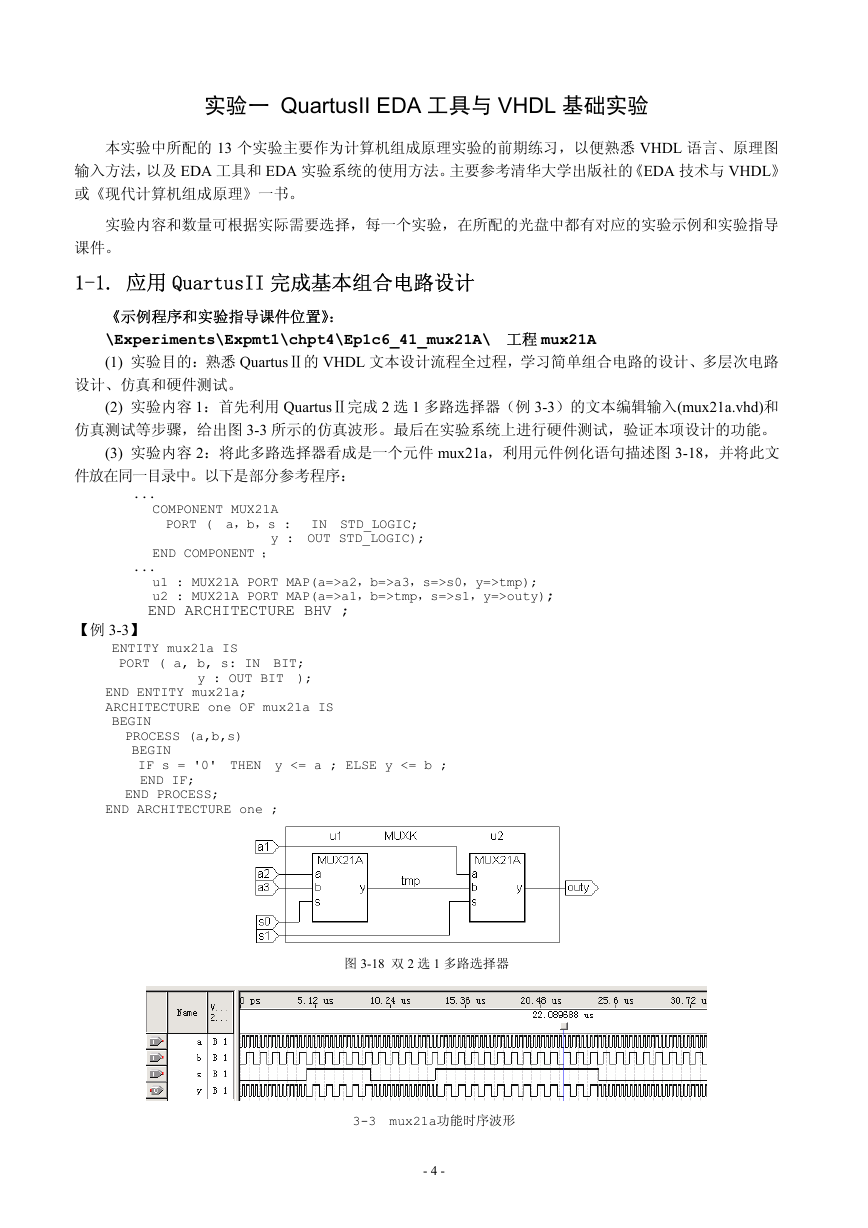

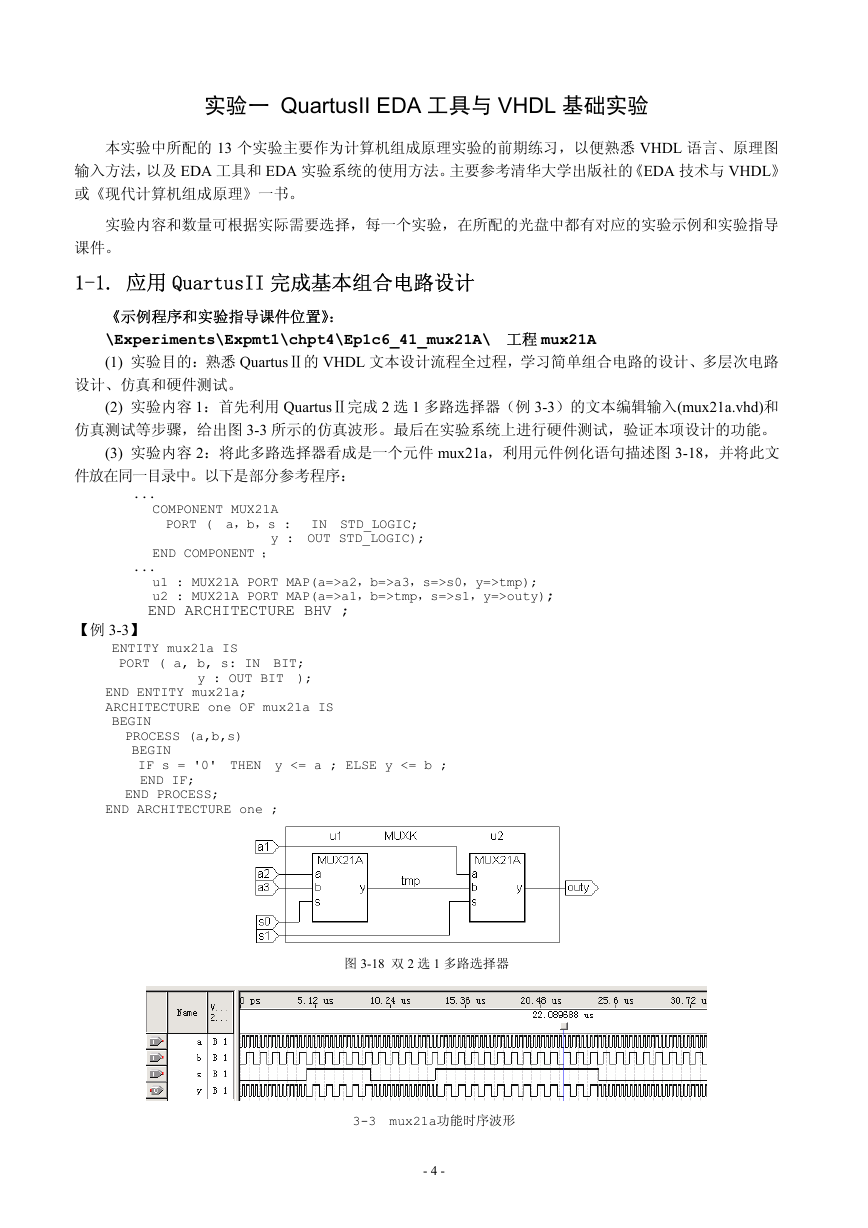

(3) 实验内容 2:将此多路选择器看成是一个元件 mux21a,利用元件例化语句描述图 3-18,并将此文

件放在同一目录中。以下是部分参考程序:

...

COMPONENT MUX21A

PORT ( a,b,s : IN STD_LOGIC;

y : OUT STD_LOGIC);

END COMPONENT ;

...

u1 : MUX21A PORT MAP(a=>a2,b=>a3,s=>s0,y=>tmp);

u2 : MUX21A PORT MAP(a=>a1,b=>tmp,s=>s1,y=>outy);

END ARCHITECTURE BHV ;

【例 3-3】

ENTITY mux21a IS

PORT ( a, b, s: IN BIT;

y : OUT BIT );

END ENTITY mux21a;

ARCHITECTURE one OF mux21a IS

BEGIN

PROCESS (a,b,s)

IF s = '0' THEN y <= a ; ELSE y <= b ;

END PROCESS;

END ARCHITECTURE one ;

BEGIN

END IF;

图 3-18 双 2 选 1 多路选择器

3-3 mux21a功能时序波形

- - 4

�

按照本章给出的步骤对上例分别进行编译、综合、仿真。并对其仿真波形作出分析说明。

(4) 实验内容 3:引脚锁定以及硬件下载测试。若选择目标器件是 EP1C3,建议选实验电路模式 5(附

录图 7),用键 1(PIO0,引脚号为 1)控制 s0;用键 2(PIO1,引脚号为 2)控制 s1;a3、a2 和 a1 分别接 clock5(引

脚号为 16)、clock0(引脚号为 93)和 clock2(引脚号为 17);输出信号 outy 仍接扬声器 spker(引脚号为 129)。

通过短路帽选择 clock0 接 256Hz 信号,clock5 接 1024Hz,clock2 接 8Hz 信号。最后进行编译、下载和硬

件测试实验(通过选择键 1、键 2,控制 s0、s1,可使扬声器输出不同音调)。

(5) 实验报告:根据以上的实验内容写出实验报告,包括程序设计、软件编译、仿真分析、硬件测试

和详细实验过程;给出程序分析报告、仿真波形图及其分析报告。

(6) 附加内容:根据本实验以上提出的各项实验内容和实验要求,设计 1 位全加器。首先用 QuartusⅡ

完成 3.3 节给出的全加器的设计,包括仿真和硬件测试。实验要求分别仿真测试底层硬件或门和半加器,

最后完成顶层文件全加器的设计和测试,给出设计原程序,程序分析报告、仿真波形图及其分析报告。

(7) 实验习题:以 1 位二进制全加器为基本元件,用例化语句写出 8 位并行二进制全加器的顶层文件,

并讨论此加法器的电路特性。

1-2. 应用 QuartusII 完成基本时序电路的设计

(1) 实验目的:熟悉 QuartusⅡ的 VHDL 文本设计过程,学习简单时序电路的设计、仿真和测试。

(2) 实验内容 1:根据实验 4-1 的步骤和要求,设计触发器(使用例 3-6),给出程序设计、软件编译、仿

真分析、硬件测试及详细实验过程。

【例 3-6】

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ;

ENTITY DFF1 IS

PORT (CLK : IN STD_LOGIC ;

D : IN STD_LOGIC ;

Q : OUT STD_LOGIC );

END ;

ARCHITECTURE bhv OF DFF1 IS

SIGNAL Q1 : STD_LOGIC ; --类似于在芯片内部定义一个数据的暂存节点

BEGIN

PROCESS (CLK,Q1)

BEGIN

IF CLK'EVENT AND CLK = '1' THEN Q1 <= D ;

END IF;

END PROCESS ;

Q <= Q1 ; --将内部的暂存数据向端口输出(双横线--是注释符号)

END bhv;

(3) 实验内容 2:设计锁存器(使用例 3-14),同样给出程序设计、软件编译、仿真分析、硬件测试及详

细实验过程。

【例 3-14】

...

PROCESS (CLK,D) BEGIN

IF CLK = '1' --电平触发型寄存器

THEN Q <= D ;

END IF;

END PROCESS ;

(4) 实验内容 3:只用一个 1 位二进制全加器为基本元件和一些辅助的时序电路,设计一个 8 位串行二

进制全加器,要求: 1、能在 8-9 个时钟脉冲后完成 8 位二进制数(加数被加数的输入方式为并行)的加

法运算,电路须考虑进位输入 Cin 和进位输出 Cout;

2、给出此电路的时序波形,讨论其功能,并就工作速度与并行加法器进行比较;

3、在 FPGA 中进行实测。对于 GW48 EDA 实验系统,建议选择电路模式 1(附录图 3),键 2,键

1 输入 8 位加数;键 4,键 3 输入 8 位被加数;键 8 作为手动单步时钟输入;键 7 控制进位输入 Cin;键 9

控制清 0;数码 6 和数码 5 显示相加和;发光管 D1 显示溢出进位 Cout。

- - 5

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc