函数发生器的设计(硬件)

摘要

DDS 是一种全数字化的频率合成器,由相位累加器、波形 ROM、D/A 转换器

和低通滤波器构成。时钟频率给定后,输出信号的频率取决于频率控制字,频

率分辨率取决于累加器位数,相位分辨率取决于 ROM 的地址线位数,幅度量化

噪声取决于 ROM 的数据位字长和 D/A 转换器位数。

DDS 有如下优点:⑴ 频率分辨率高,输出频点多,可达 个频点(N 为相位

累加器位数);⑵频率切换速度快,可达 us 量级;⑶ 频率切换时相位连续;⑷

可以输出宽带正交信号;⑸ 输出相位噪声低,对参考频率源的相位噪声有改善

作用;⑹可以产生任意波形;⑺ 全数字化实现,便于集成,体积小,重量轻,

因此八十年代以来各国都在研制和发展各自的 DDS 产品,如美国 QUALCOMM 公司

的 Q2334,Q2220;STANFORD 公司的 STEL-1175,STEL-1180;AD 公司的 AD7008,

AD9850,AD9854等。这些 DDS 芯片的时钟频率从几十兆赫兹到几百兆赫兹不等,

芯片从一般功能到集成有 D/A 转换器和正交调制器。采用 FPGA 设计了任意波形

发生器(三角波,锯齿波,调频波,调相波,调幅波等)。完成了硬件方面的设

计。

关键词:直接数字频率合成 任意波形发生器 现场可编程门阵列 硬件部分

�

Function Generator Design(Hardware)

Abstraet

DDS is an all-digital frequency synthesizer, the phase accumulator, waveform

ROM, D / A converter and low pass filter constituted. Given clock frequency, the

output signal frequency depends on the frequency control word,

the median

frequency resolution depends on the accumulator, the phase resolution depends on the

median line of the address ROM, amplitude quantization noise depends on the ROM

data bit word length and D / A converter bits.

DDS has the following advantages: ⑴ high frequency resolution, the output

frequency and more, up to a frequency (N is the phase accumulator bits).⑵ frequency

switching speed and magnitude of up to us.⑶ phase continuous frequency

switching.⑷ broadband quadrature signal can be output. ⑸ output phase noise and

low phase noise reference frequency source can alleviate. ⑹ can generate arbitrary

waveforms. ⑺ all-digital implementation, easy integration, small size, light weight,

so since the eighties research and development of all countries in the respective DDS

products, such as the United States Q2334, Q2220, STEL-1175, STEL-1180, AD's

AD7008, AD9850, AD9854 and so on. The DDS chip's clock frequency from several

megahertz to several megahertz Hz range, the chip features from the general to

integrated D/A converters and quadrature modulator. FPGA design with arbitrary

waveform generator (triangle wave, sawtooth wave, FM waves, phase modulation

wave, amplitude, etc.). Completed the hardware design.

Keywords: direct digital

field programmable gate array

arbitrary waveform generator

frequency synthesis

hardware

�

目

录

第一章 绪论 ····································································································1

1.1 频率合成的发展历程 ·················································································1

1.2 频率合成器的指标 ····················································································1

1.3 直接数字频率合成技术的现状与应用 ··························································· 3

第二章 直接频率合成的原理及技术分析 ························································· 5

2.1 DDS 的基本原理 ·······················································································5

2.2 DDS 的优点和缺点 ····················································································5

第三章 DDS 频谱分析以及散杂抑制 ································································· 7

3.1 理想的 DDS 频谱 ·······················································································7

3.2 非理想状态下的散杂以及抑制方法 ······························································7

第四章 DDS 芯片 AD9854 及其接口电路设计 ··················································· 10

4.1 AD9854 基本结构和工作原理 ···································································· 10

4.2 AD9854 的工作模式及引脚功能 ··································································11

4.3 AD9854 的外围扩展 ·················································································12

第五章 多波形发生器各个模块的设计 ··························································· 14

5.1 FPGA 的概述 ··························································································14

5.2 控制模块设计 ······················································································· 15

5.3 相位累加器的设计 ················································································· 16

5.4 波形 RAM 的设计 ···················································································· 16

5.5 D/A 转换器电路的设计 ············································································ 17

第六章 DDS 任意波形函数信号发生器的硬件电路设计与调试 ·························19

6.1 DDS 任意波形发生器的总体结构 ································································19

6.2 DDS 任意波形发生器各模块的功能及实现 ····················································20

6.3 硬件的制作与调试 ·················································································· 25

第七章 结论 ·································································································· 28

参考文献 ········································································································29

致 谢 ········································································································· 30

�

天津理工大学 2010 届本科毕业设计说明书

第一章 绪论

1.1 频率合成的发展历程[1]

频率合成技术起源于上世纪30年代,早期把频率合成技术定义为将一个或多个高精度和

高稳定度的基准源,经过混频、倍频和分频等加、减、乘、除运算,产生其它高精度和高稳

定度频率源的一种技术,可见,频率合成器的实质是一个频率转换装置。现代频率合成器主

要有直接式和间接式两种。

早期的频率合成器是由一组晶体组成的晶体振荡器,要输出多少个频率点,就需要多少

个晶体。频率的切换由人工来完成,频率的准确度和稳定度主要由晶体来决定,很少与电路

有关。后来,这种合成方法被非相干合成的方法所替代。非相干合成法虽然也使用了晶体,

但它的工作方式是以少量的晶体产生许多频率。与早期的合成方式相比,成本降低了,而稳

定性提高了。但是此项任务非常复杂,而且成本高,不经济,所以后来科学家又提出了相干

合成法。相干合成法是由一个准确度和稳定度达到要求的参考源产生许多频率的方法。非相

干合成法用了许多晶体振荡器,而相干合成只使用一个参考频率源,因此,在相干合成装置

中,输出频率的稳定度和准确度与参考源相同。最早的相干合成法就是直接式频率合成

(Direct Frepuency Synthesis)。

直接式频率合成器可分为直接模拟式和直接数字式(DDS)。直接式频率合成器的优点是频

速度快、相位噪声低等,但结构复杂、且输出频谱中杂散较多。上世纪70年代初,Tierney

等人发表关于新型数字频率合成器的研究成果,第一次提出了DDS概念。由于DDS具有超宽的

相对带宽、超高的捷变速度、超细的分辨力且输出相位连续,可以输出宽带的正交信号、可

编程、全数字化、便于单片集成等优越性能,因此在短短二十年时间里,得到了飞速的发展,

其应用也越来越广泛。目前市场上性能优良的DDS产品不断推出,主要有AD公司的系列产品(如

AD9858,最高时钟可达10Hz,控制灵活,输出波形丰富等)。我们选用的DDS芯片BTDS52其时

钟频率高达2.5GHz。

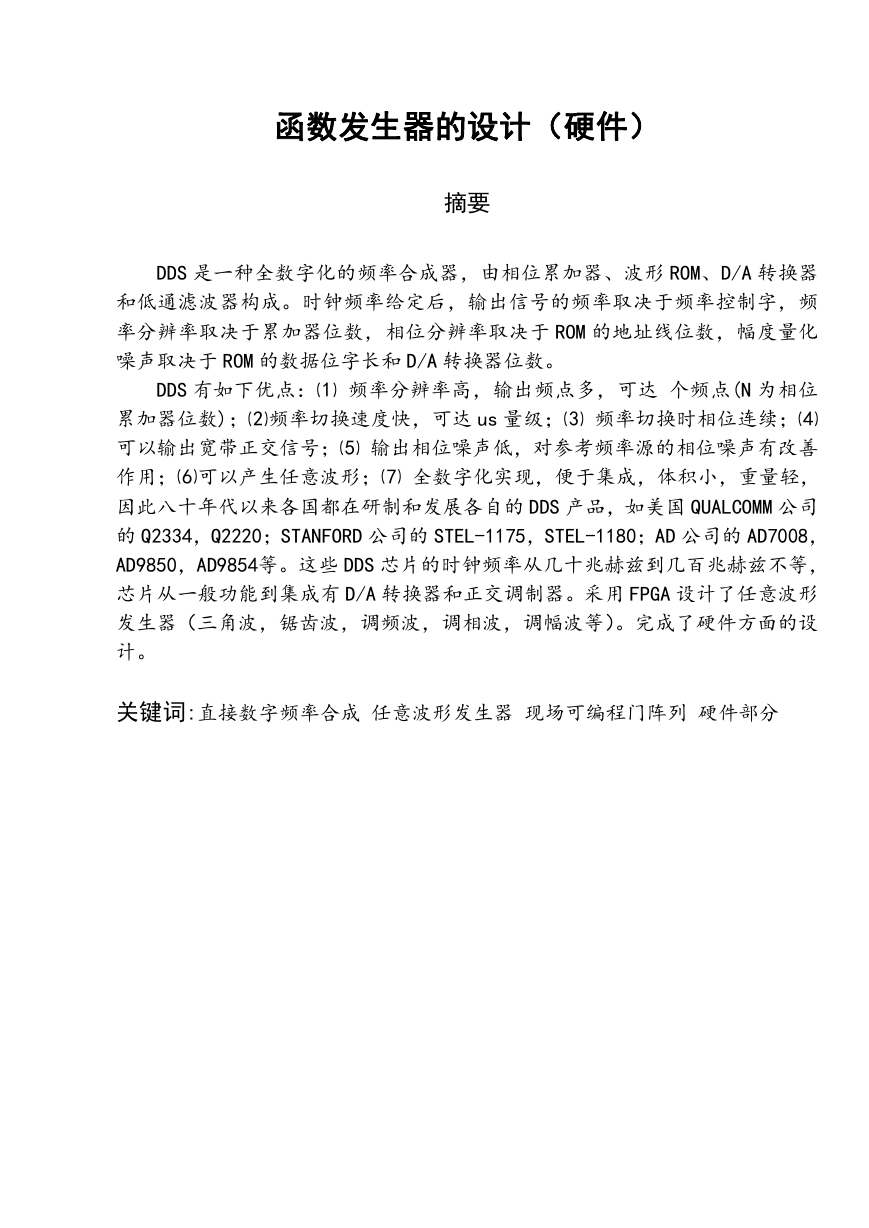

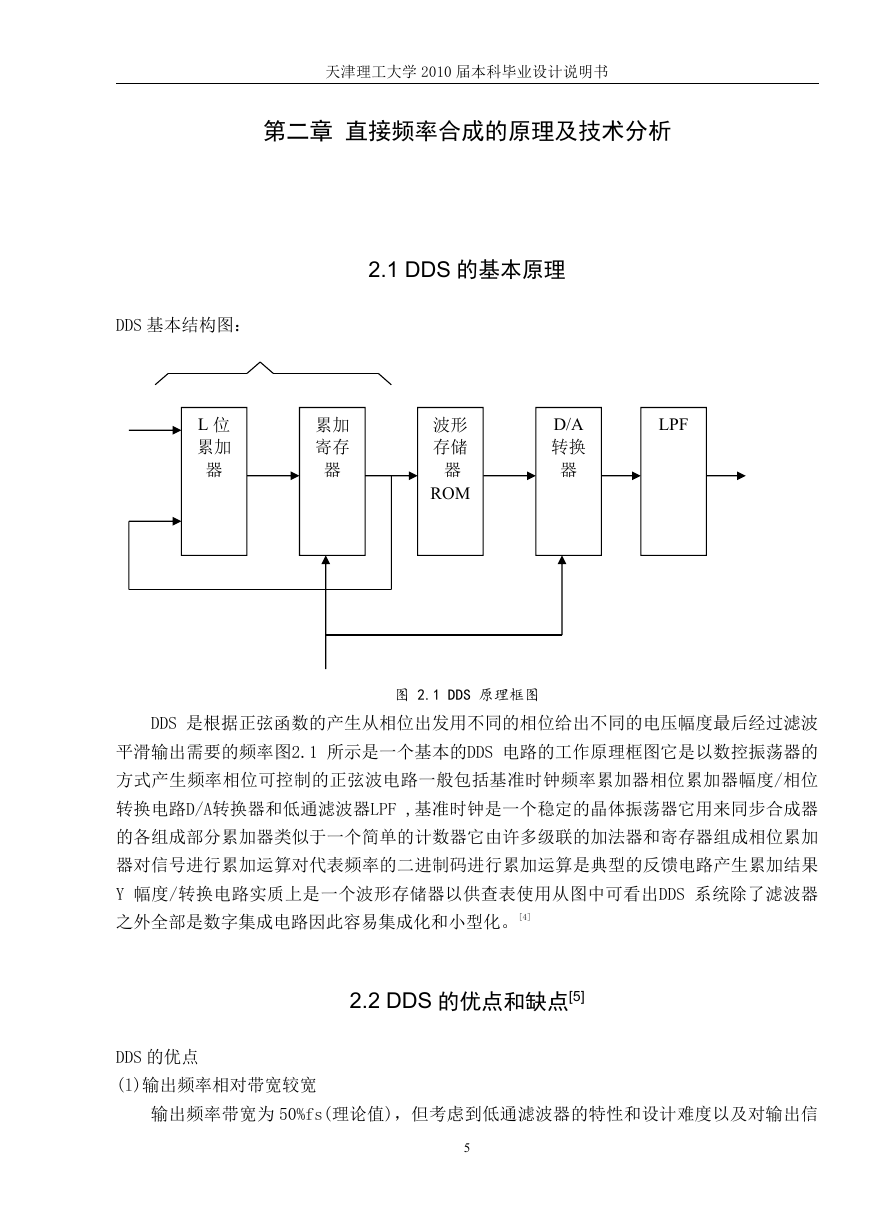

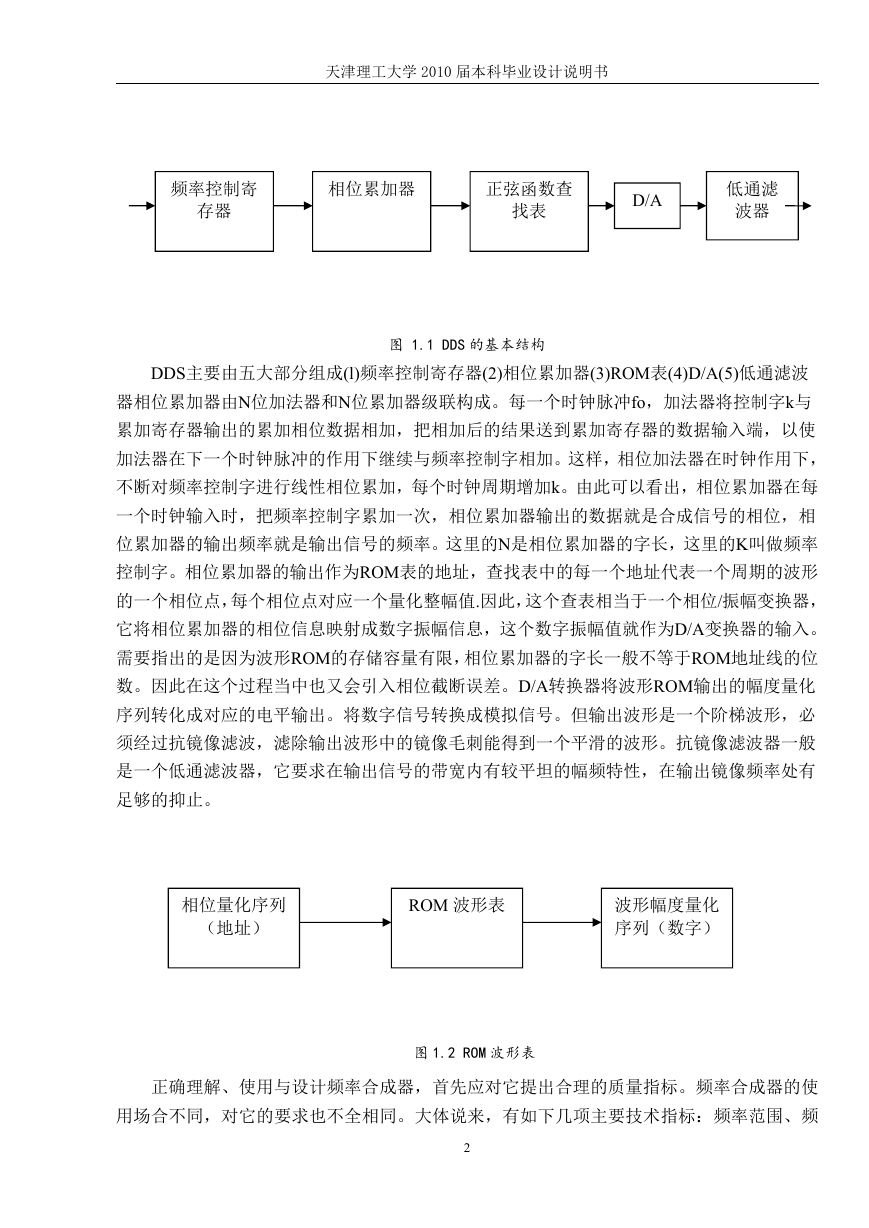

DDS 的基本结构

1.2 频率合成器的指标[2]

1

�

天津理工大学 2010 届本科毕业设计说明书

频率控制寄

相位累加器

正弦函数查

存器

找表

D/A

低通滤

波器

图 1.1 DDS 的基本结构

DDS主要由五大部分组成(l)频率控制寄存器(2)相位累加器(3)ROM表(4)D/A(5)低通滤波

器相位累加器由N位加法器和N位累加器级联构成。每一个时钟脉冲fo,加法器将控制字k与

累加寄存器输出的累加相位数据相加,把相加后的结果送到累加寄存器的数据输入端,以使

加法器在下一个时钟脉冲的作用下继续与频率控制字相加。这样,相位加法器在时钟作用下,

不断对频率控制字进行线性相位累加,每个时钟周期增加k。由此可以看出,相位累加器在每

一个时钟输入时,把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位,相

位累加器的输出频率就是输出信号的频率。这里的N是相位累加器的字长,这里的K叫做频率

控制字。相位累加器的输出作为ROM表的地址,查找表中的每一个地址代表一个周期的波形

的一个相位点,每个相位点对应一个量化整幅值.因此,这个查表相当于一个相位/振幅变换器,

它将相位累加器的相位信息映射成数字振幅信息,这个数字振幅值就作为D/A变换器的输入。

需要指出的是因为波形ROM的存储容量有限,相位累加器的字长一般不等于ROM地址线的位

数。因此在这个过程当中也又会引入相位截断误差。D/A转换器将波形ROM输出的幅度量化

序列转化成对应的电平输出。将数字信号转换成模拟信号。但输出波形是一个阶梯波形,必

须经过抗镜像滤波,滤除输出波形中的镜像毛刺能得到一个平滑的波形。抗镜像滤波器一般

是一个低通滤波器,它要求在输出信号的带宽内有较平坦的幅频特性,在输出镜像频率处有

足够的抑止。

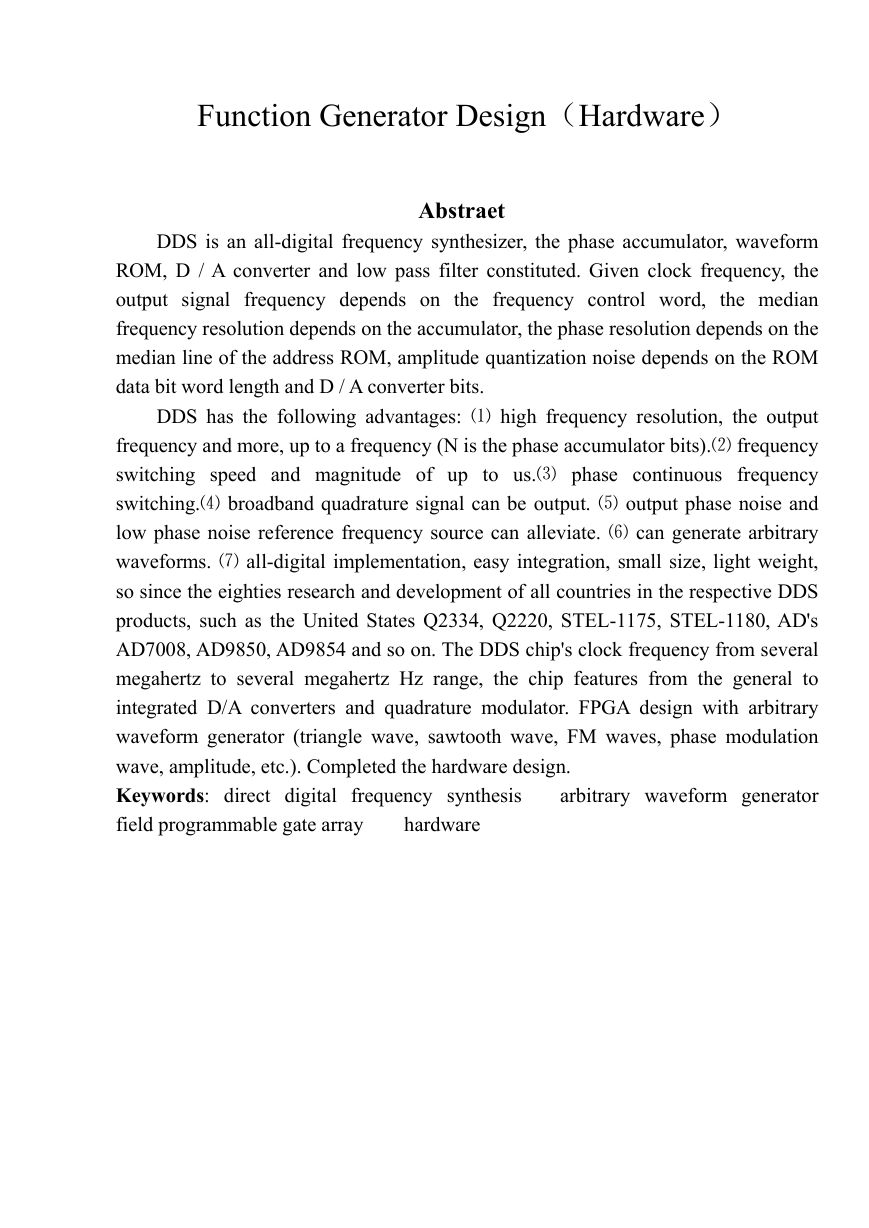

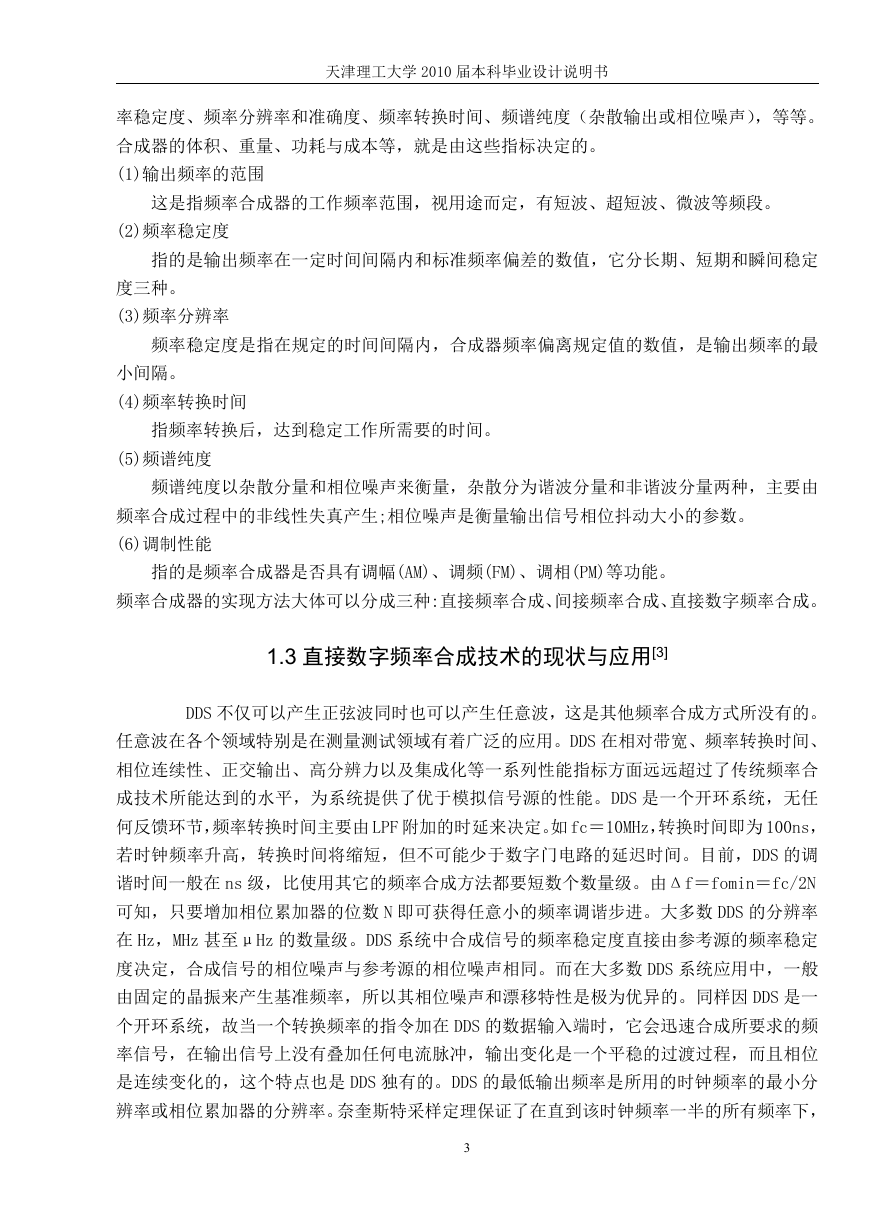

相位量化序列

(地址)

ROM 波形表

波形幅度量化

序列(数字)

正确理解、使用与设计频率合成器,首先应对它提出合理的质量指标。频率合成器的使

用场合不同,对它的要求也不全相同。大体说来,有如下几项主要技术指标:频率范围、频

图 1.2 ROM 波形表

2

�

天津理工大学 2010 届本科毕业设计说明书

率稳定度、频率分辨率和准确度、频率转换时间、频谱纯度(杂散输出或相位噪声),等等。

合成器的体积、重量、功耗与成本等,就是由这些指标决定的。

(1)输出频率的范围

这是指频率合成器的工作频率范围,视用途而定,有短波、超短波、微波等频段。

(2)频率稳定度

指的是输出频率在一定时间间隔内和标准频率偏差的数值,它分长期、短期和瞬间稳定

度三种。

(3)频率分辨率

频率稳定度是指在规定的时间间隔内,合成器频率偏离规定值的数值,是输出频率的最

小间隔。

(4)频率转换时间

指频率转换后,达到稳定工作所需要的时间。

(5)频谱纯度

频谱纯度以杂散分量和相位噪声来衡量,杂散分为谐波分量和非谐波分量两种,主要由

频率合成过程中的非线性失真产生;相位噪声是衡量输出信号相位抖动大小的参数。

(6)调制性能

指的是频率合成器是否具有调幅(AM)、调频(FM)、调相(PM)等功能。

频率合成器的实现方法大体可以分成三种:直接频率合成、间接频率合成、直接数字频率合成。

1.3 直接数字频率合成技术的现状与应用[3]

DDS 不仅可以产生正弦波同时也可以产生任意波,这是其他频率合成方式所没有的。

任意波在各个领域特别是在测量测试领域有着广泛的应用。DDS 在相对带宽、频率转换时间、

相位连续性、正交输出、高分辨力以及集成化等一系列性能指标方面远远超过了传统频率合

成技术所能达到的水平,为系统提供了优于模拟信号源的性能。DDS 是一个开环系统,无任

何反馈环节,频率转换时间主要由 LPF 附加的时延来决定。如 fc=10MHz,转换时间即为 100ns,

若时钟频率升高,转换时间将缩短,但不可能少于数字门电路的延迟时间。目前,DDS 的调

谐时间一般在 ns 级,比使用其它的频率合成方法都要短数个数量级。由Δf=fomin=fc/2N

可知,只要增加相位累加器的位数 N 即可获得任意小的频率调谐步进。大多数 DDS 的分辨率

在 Hz,MHz 甚至μHz 的数量级。DDS 系统中合成信号的频率稳定度直接由参考源的频率稳定

度决定,合成信号的相位噪声与参考源的相位噪声相同。而在大多数 DDS 系统应用中,一般

由固定的晶振来产生基准频率,所以其相位噪声和漂移特性是极为优异的。同样因 DDS 是一

个开环系统,故当一个转换频率的指令加在 DDS 的数据输入端时,它会迅速合成所要求的频

率信号,在输出信号上没有叠加任何电流脉冲,输出变化是一个平稳的过渡过程,而且相位

是连续变化的,这个特点也是 DDS 独有的。DDS 的最低输出频率是所用的时钟频率的最小分

辨率或相位累加器的分辨率。奈奎斯特采样定理保证了在直到该时钟频率一半的所有频率下,

3

�

天津理工大学 2010 届本科毕业设计说明书

DAC 都可以再现信号,即 DDS 频率的上限 fomax 由合成器的最大时钟频率 fc 决定(fomax=

fc/2)。DDS 中几乎所有的部件都属于数字信号处理器件,除 DAC 和滤波器外,无需任何调整,

从而降低了成本,简化了生产设备。

近几年超高速数字电路的发展以及对 DDS 的深入研究其已广泛应用于通讯、导航、雷达、

遥控遥测、电子对抗以及现代化的仪器仪表工业等领域。

4

�

天津理工大学 2010 届本科毕业设计说明书

第二章 直接频率合成的原理及技术分析

2.1 DDS 的基本原理

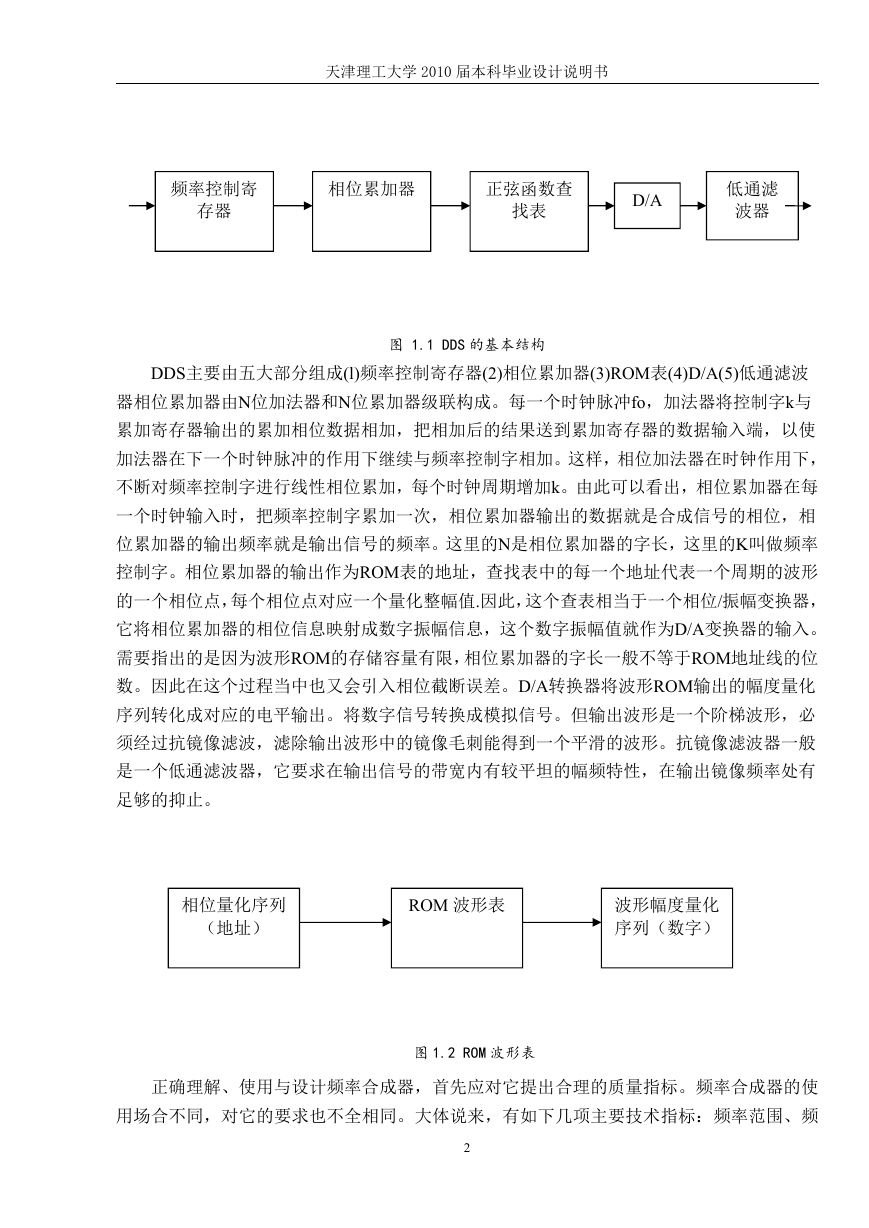

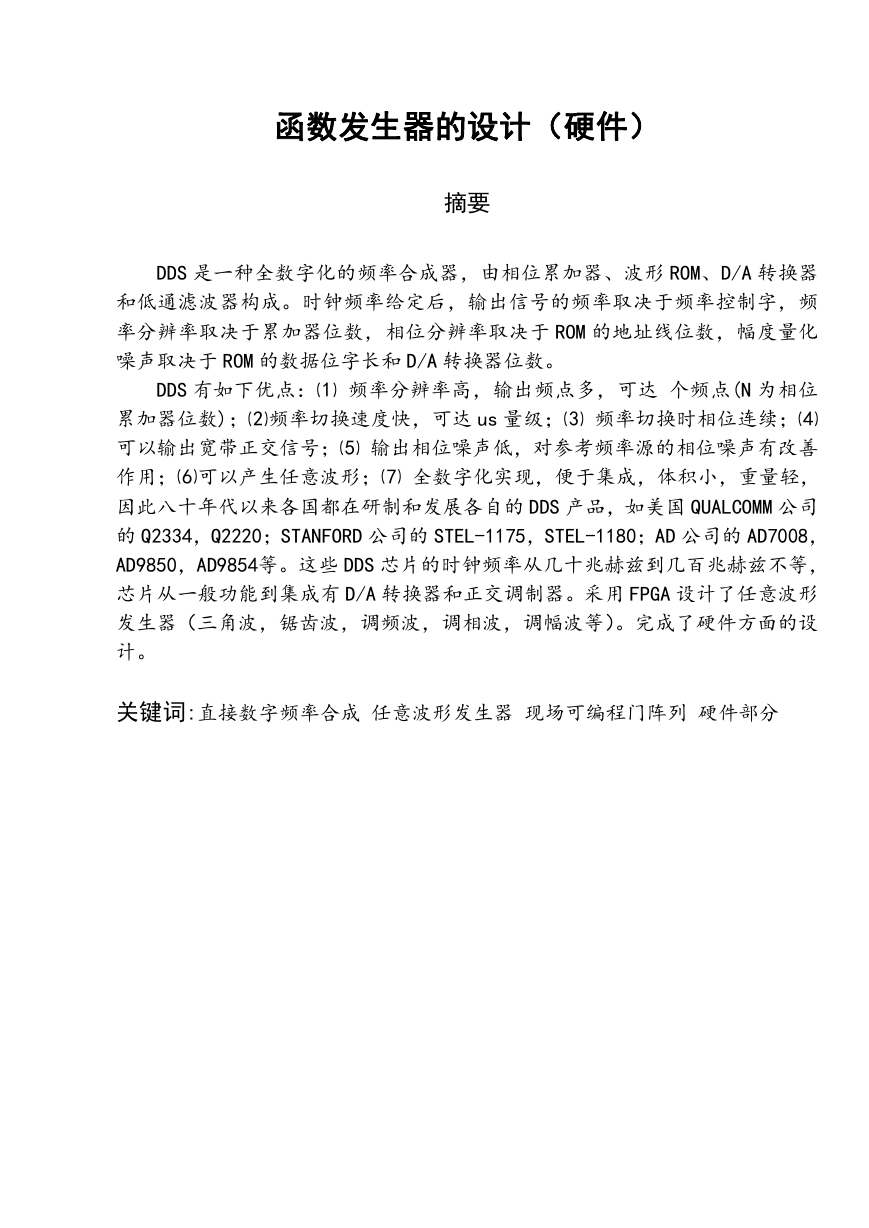

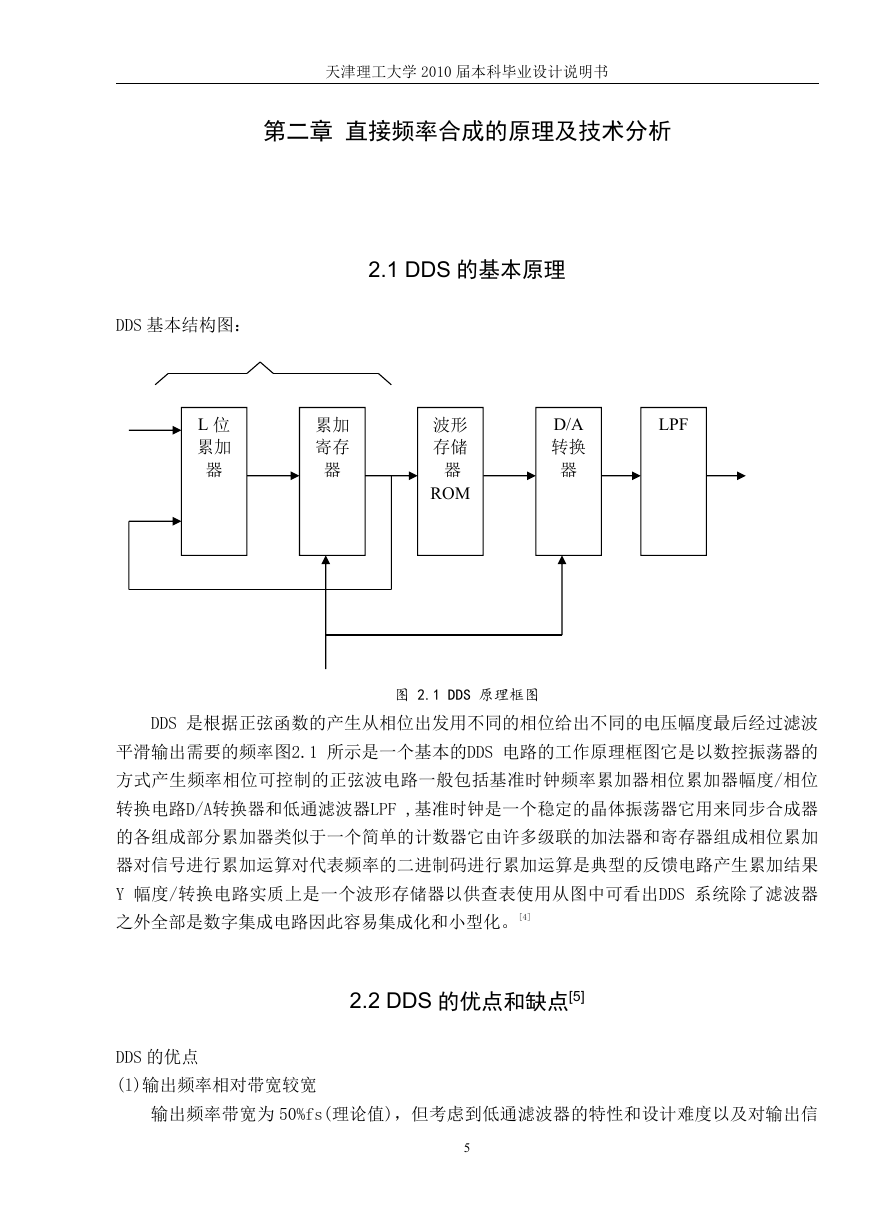

DDS 基本结构图:

L 位

累加

器

累加

寄存

器

波形

存储

器

ROM

LPF

D/A

转换

器

图 2.1 DDS 原理框图

DDS 是根据正弦函数的产生从相位出发用不同的相位给出不同的电压幅度最后经过滤波

平滑输出需要的频率图2.1 所示是一个基本的DDS 电路的工作原理框图它是以数控振荡器的

方式产生频率相位可控制的正弦波电路一般包括基准时钟频率累加器相位累加器幅度/相位

转换电路D/A转换器和低通滤波器LPF ,基准时钟是一个稳定的晶体振荡器它用来同步合成器

的各组成部分累加器类似于一个简单的计数器它由许多级联的加法器和寄存器组成相位累加

器对信号进行累加运算对代表频率的二进制码进行累加运算是典型的反馈电路产生累加结果

Y 幅度/转换电路实质上是一个波形存储器以供查表使用从图中可看出DDS 系统除了滤波器

之外全部是数字集成电路因此容易集成化和小型化。[4]

2.2 DDS 的优点和缺点[5]

DDS 的优点

(l)输出频率相对带宽较宽

输出频率带宽为 50%fs(理论值),但考虑到低通滤波器的特性和设计难度以及对输出信

5

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc