第 10 卷 第 3 期 电路与系统学报 Vol.10 No.3

2005 年 6 月 JOURNAL OF CIRCUITS AND SYSTEMS June, 2005

文章编号:1007-0249 (2005) 03-0076-04

基于 FPGA 的高阶全数字锁相环的设计与实现*

单长虹, 王彦, 陈文光, 陈忠泽

(南华大学 电气工程学院,湖南 衡阳 421001)

摘要:提出了一种实现高阶全数字锁相环的新方法。该锁相环以数字比例积分控制取代了传统的一些数字环路滤

波控制方法,具有电路结构简单、控制灵活、跟踪精度高、环路性能好和易于集成的特点。文中介绍了该高阶全数字

锁相环的系统结构和工作原理,对其性能进行了理论分析和计算机仿真。应用 EDA 技术设计了该系统,并用 FPGA

实现了其硬件电路。仿真和硬件测试结果证实了该设计的正确性。

关键词:全数字锁相环;比例积分;EDA;计算机仿真

中图分类号:TN914.3

文献标识码:A

1 引言

锁相环在通信、雷达、测量和自动化控制等领域应用极为广泛,已经成为各种电子设备中必不可

少的基本部件。随着电子技术向数字化方向发展,需要采用数字方式实现信号的锁相处理。因此,对

全数字锁相环的研究和应用得到了越来越多的关注[1,2]。

传统的数字锁相环系统是希望通过采用具有低通特性的环路滤波器,获得稳定的振荡控制数据。

对于高阶全数字锁相环,其数字滤波器常常采用基于 DSP 的运算电路。这种结构的锁相环,当环路带

宽很窄时,环路滤波器的实现将需要很大的电路量,这给专用集成电路的应用和片上系统 SOC(system

on chip)的设计带来一定困难[3]。另一种类型的全数字锁相环是采用脉冲序列低通滤波计数电路作为

环路滤波器,如随机徘徊序列滤波器、先 N 后 M 序列滤波器等[4,5]。这些电路通过对鉴相模块产生的

相位误差脉冲进行计数运算,获得可控振荡器模块的振荡控制参数。由于脉冲序列低通滤波计数方法

是一个比较复杂的非线性处理过程,难以进行线性近似,因此,无法采用系统传递函数的分析方法确

定锁相环的设计参数。不能实现对高阶数字锁相环性能指标的解藕控制和分析,无法满足较高的应用

需求。

本文提出了一种基于比例积分(PI)控制算法的高阶全数字锁相环[6,7]。给出了该锁相系统的具体

结构,建立了系统数学模型,并对其系统性能进行了理论分析。采用 MATLAB 软件对系统进行了仿

真实验。应用 EDA 技术设计了该锁相系统,并用 FPGA 予以实现。

2 全数字锁相环的结构

及工作原理

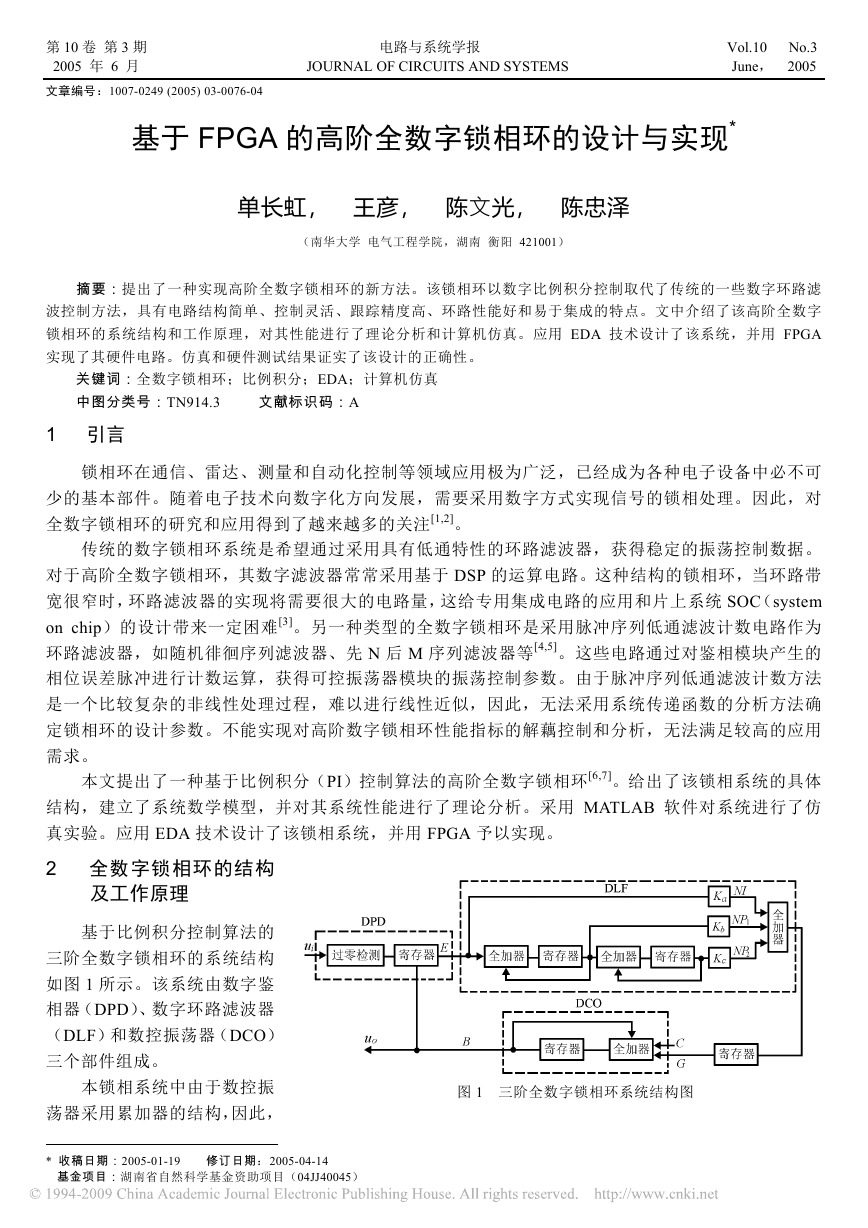

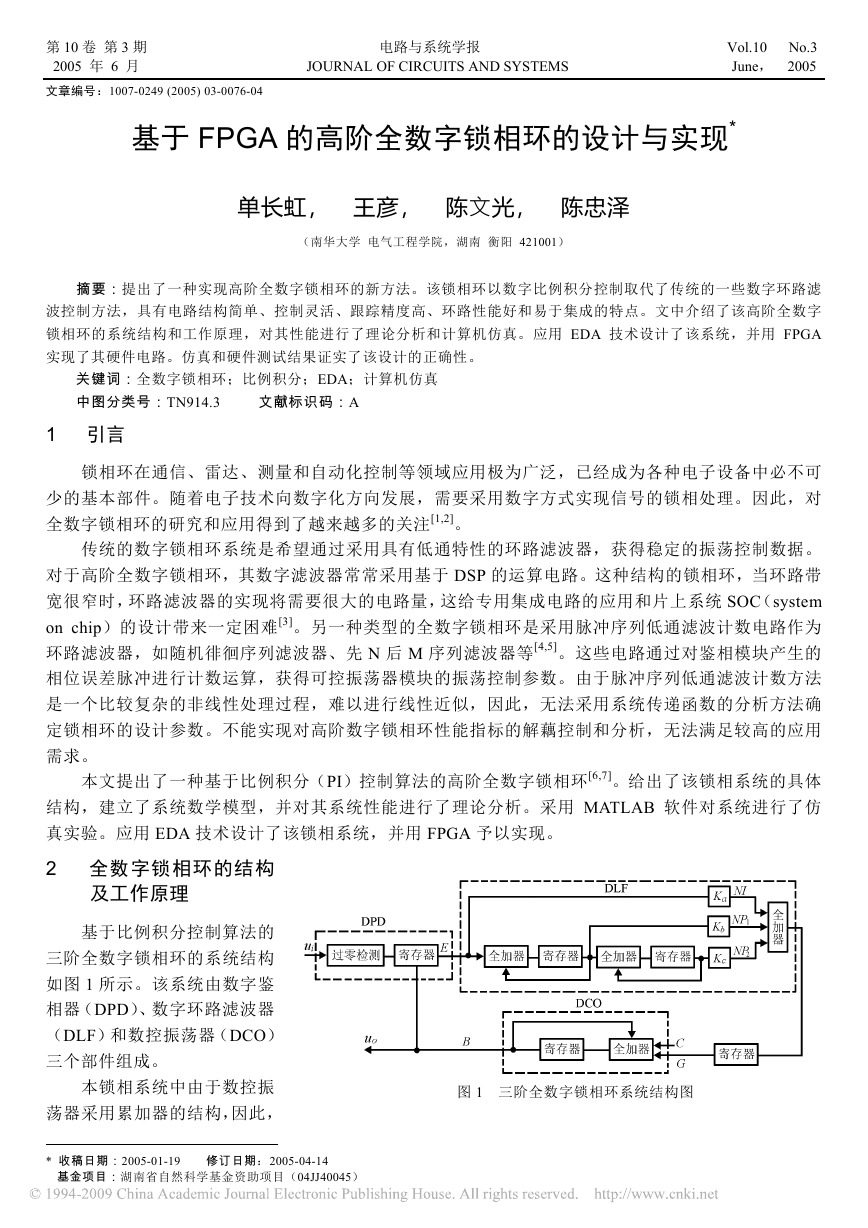

基于比例积分控制算法的

三阶全数字锁相环的系统结构

如图 1 所示。该系统由数字鉴

相器(DPD)、数字环路滤波器

(DLF)和数控振荡器(DCO)

三个部件组成。

本锁相系统中由于数控振

荡器采用累加器的结构,因此,

* 收稿日期:2005-01-19 修订日期:2005-04-14

基金项目:湖南省自然科学基金资助项目(04JJ40045)

图 1 三阶全数字锁相环系统结构图

�

第 3 期 单长虹等:基于 FPGA 的高阶全数字锁相环的设计与实现 77

累加器输出的并行码就是数控振荡器的输出相位码 B,它反映了输入信号和输出信号之间的瞬时相位

差。鉴相器中的寄存器是由一组 D 触发器构成。DCO 的输出相位码 B 并行送到 D 触发器的 D 端,在

输入信号的正向过零点对 D 触发器采样,D 触发器组的输出 E 就表示该采样时刻的瞬时相位差,从而

完成了数字鉴相功能。

数字环路滤波器的主要作用是抑制噪声及高频分量,并且控制着环路相位校正的速度与精度。为

了提高锁相系统的性能,设计了基于 PI 控制算法的二阶数字滤波器。其工作原理是对鉴相器输出的相

位误差信号经一阶积分环节、二阶积分环节和比例环节调节后,分别产生积分控制参数 NP1 和 NP2,

以及比例控制参数 NI,然后取这三个控制参数之和作为数控振荡器的控制参数。为使 DLF 输出的控

制码组在同一瞬间并行送入 DCO,在这两个环路部件之间接入一缓冲寄存器。

数控振荡器是由全加器和寄存器构成的累加器组成。若累加器位长为 N,则低位输入端 NL 接 DLF

的控制码组 G,高位 NH 接 DCO 自由振荡频率 0f 的控制码组 C(该参数可由设计者设定)。当控制码

组 G 均为‘0’时,DCO 输出端最高位 AN 的输出信号的频率便是 DCO 的自由振荡频率 0f 。在环路锁

定过程中,控制码组 G 不是全为零,此时累加器的累加结果将进位而改变累加器的分频系数,从而改

变 DCO 输出信号的频率,实现比例积分控制参数对本地估算信号的控制作用,最终达到锁相的目的。

3 数字锁相环系统性能的理论分析

3.1 锁相环的系统结构

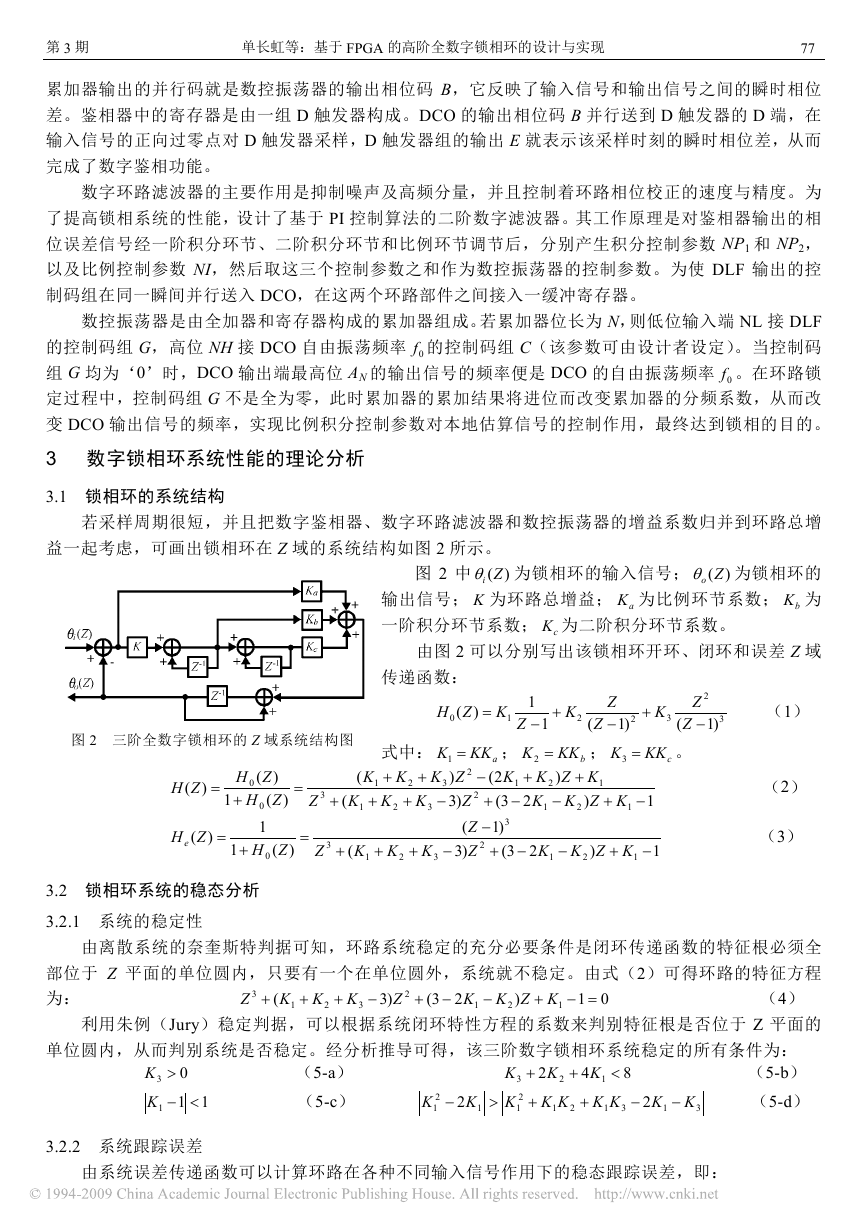

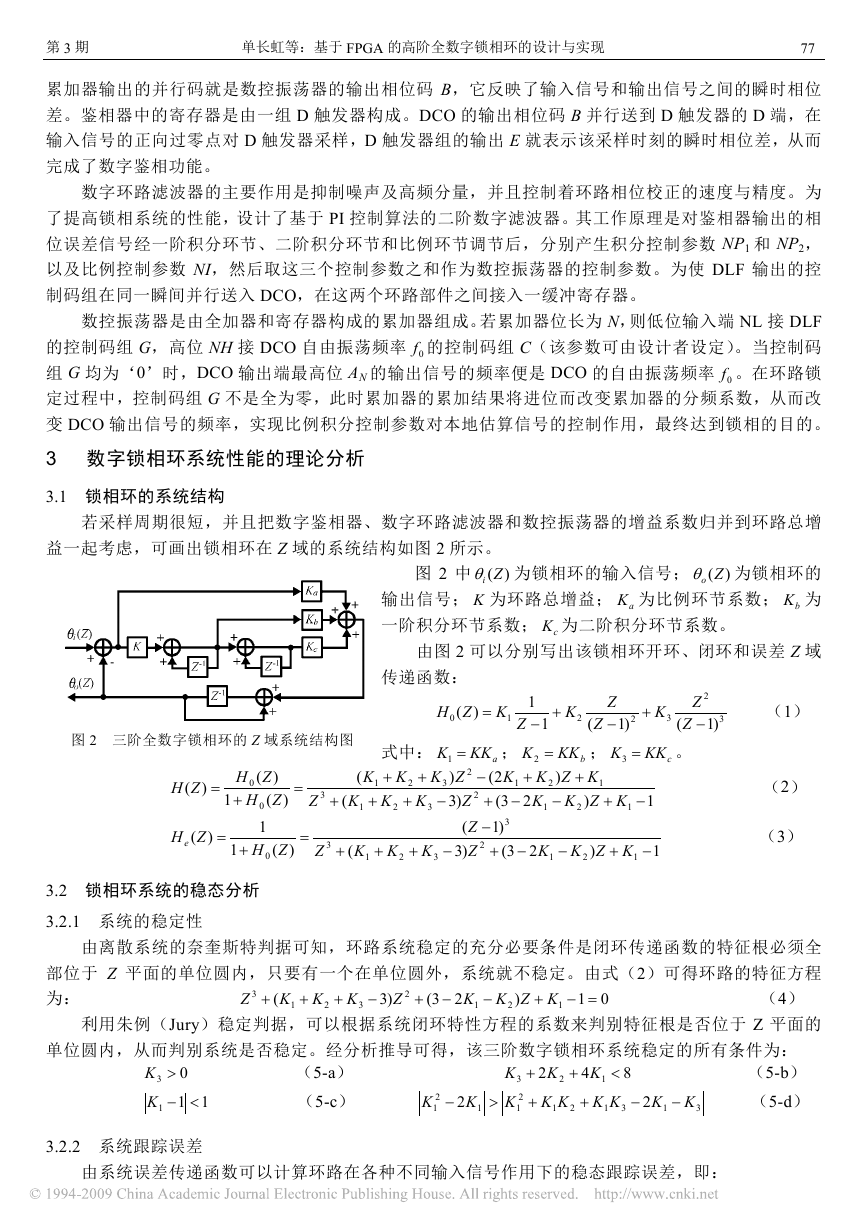

若采样周期很短,并且把数字鉴相器、数字环路滤波器和数控振荡器的增益系数归并到环路总增

益一起考虑,可画出锁相环在 Z 域的系统结构如图 2 所示。

图 2 中 )

(Ziθ 为锁相环的输入信号;

(Zoθ 为锁相环的

输出信号; K 为环路总增益; aK 为比例环节系数; bK 为

一阶积分环节系数; cK 为二阶积分环节系数。

)

由图 2 可以分别写出该锁相环开环、闭环和误差 Z 域

传递函数:

图 2 三阶全数字锁相环的 Z 域系统结构图

ZH

(

)

=

1

ZH e

(

)

=

)

ZH

)

(

0

ZH

(

+

0

1

ZH

(

+

0

1

=

3

Z

+

(

(

K

K

1

+

1

式中:

+

+

K

K

K

2

+

3

2

=

)

3

Z

+

(

K

+

K

2

1

+

K

ZH

(

0

1

2

2

)

(

=

+

Z

K

K

Z

)1

−

K =3

1

Z

1

−

bKK

aKK

K =2

;

;

K

KZK

2

)

2(

+

−

+

1

2

K

KZK

2

23(

)

+

−

−

3

)1

−

2

23(

+

1

+

KZK

K

+

−

−

)

2

1

1

2

K =1

ZK

)

3

Z

)3

−

Z

(

Z

)3

−

3

(1)

3

2

)1

Z

Z

(

−

。

+

K

3

cKK

(2)

−

1

1

(3)

−

1

1

3.2 锁相环系统的稳态分析

3.2.1 系统的稳定性

由离散系统的奈奎斯特判据可知,环路系统稳定的充分必要条件是闭环传递函数的特征根必须全

部位于 Z 平面的单位圆内,只要有一个在单位圆外,系统就不稳定。由式(2)可得环路的特征方程

为:

(4)

KZK

01

=−

23(

)3

K

K

K

K

Z

Z

+

−

−

+

−

+

+

+

(

)

2

3

1

2

1

1

2

3

利用朱例(Jury)稳定判据,可以根据系统闭环特性方程的系数来判别特征根是否位于 Z 平面的

单位圆内,从而判别系统是否稳定。经分析推导可得,该三阶数字锁相环系统稳定的所有条件为:

(5-b)

8

(5-d)

2

−

(5-a)

>

(5-c)

K

2

2

KK

K

<

1

KK

3 >K

<−K

111

K

K

+

+

4

+

3

2

1

K

K

K

K

2

1

−

−

+

2

0

3

1

3

1

2

1

1

3.2.2 系统跟踪误差

由系统误差传递函数可以计算环路在各种不同输入信号作用下的稳态跟踪误差,即:

�

78 电路与系统学报 第 10 卷

Z

−

()1

φ

Z

)

(6)

)

(

φ

=∞

lim

[(

Z

1

→

Z

ZH

)

(

(

e θ

i

(Ziθ 为 输入信号 ,

Z

(

φ

)

)

⋅

)

=

式中:

。

(ZHe 为锁相 系 统误差传递 函

数。由式(6)所求得的本系统对应于各种典型相位输入

信号的稳态跟踪误差列于表 1。

)

由表 1 可知,本锁相系统对于相位阶跃、频率阶跃

和频率斜升输入信号的稳态跟踪误差为零。

4 锁相系统的设计实现与仿真

表 1 锁相系统稳态相位误差

典型相位输入 θ(t),t≥0

θi(Z)

(∞φ

)

相位阶跃

频率阶跃

频率斜升

θ0

tv0

1

ta

02

2

θ

0

Z

−Z

1

Tv

0

Z

( −Z

2

)1

0

2

ZZTa

(

+

)1

−

3

(2

Z

)1

0

0

0

依据图 1 锁相环系统的结构,利用 Xilinx 公司的 ISE 设计软件,采用自顶向下的模块化设计方法,

用 VHDL 对全数字锁相环的各个部件分别进行编程设计,然后对该系统做综合设计和仿真[8]。最后,

采用 Xilinx 公司的 sparnⅡ系列的 FPGA 器件实现了锁相系统的硬件功能。

表 2 三阶 DPLL 系统稳定性分析结果

A2

0.875

0.875

0.875

0.750

A3

0.234

0.234

0.234

0.438

A4 系统状态

0.235 不稳定

0.234

临界

稳定

0.233

0.406

稳定

K1

2-3

2-3

2-3

2-2

K2

2-11

2-6

2-6

2-3

K3

2-10

2-9

2-11

2-11

A1

0.500

0.533

0.532

1.250

本锁相系统的设计参数如下:鉴相器中 D 触发

器的位长为 16;DLF 内二个积分环节中累加器的位

长均为 16;DCO 中累加器的位长为 24,累加器的

时钟频率 clkf 为 8MHz,比例积分控制码组的字长

G=14,自由振荡频率 0f 控制码组的字长 C=10。

选择不同的比例系数 aK 和积分系数 bK 、 cK ,

可以改变 1K 、 2K 、 3K 的参数值,进而可根据本锁相系统的稳定条件式(5),判断系统是否稳定。表

2 列出了几种典型参数所对应的锁相系统稳定性分析结果。表 2 中设

;

A

3

A

;

4

11

−

KK

= K

;

A

2

A

1

K

K

K

+

+

=

+

−

2

1

4

2

3

2

1

1

2

3

1

1

2

=

=

+

−

2

1

K

K

2K

KK

。

K

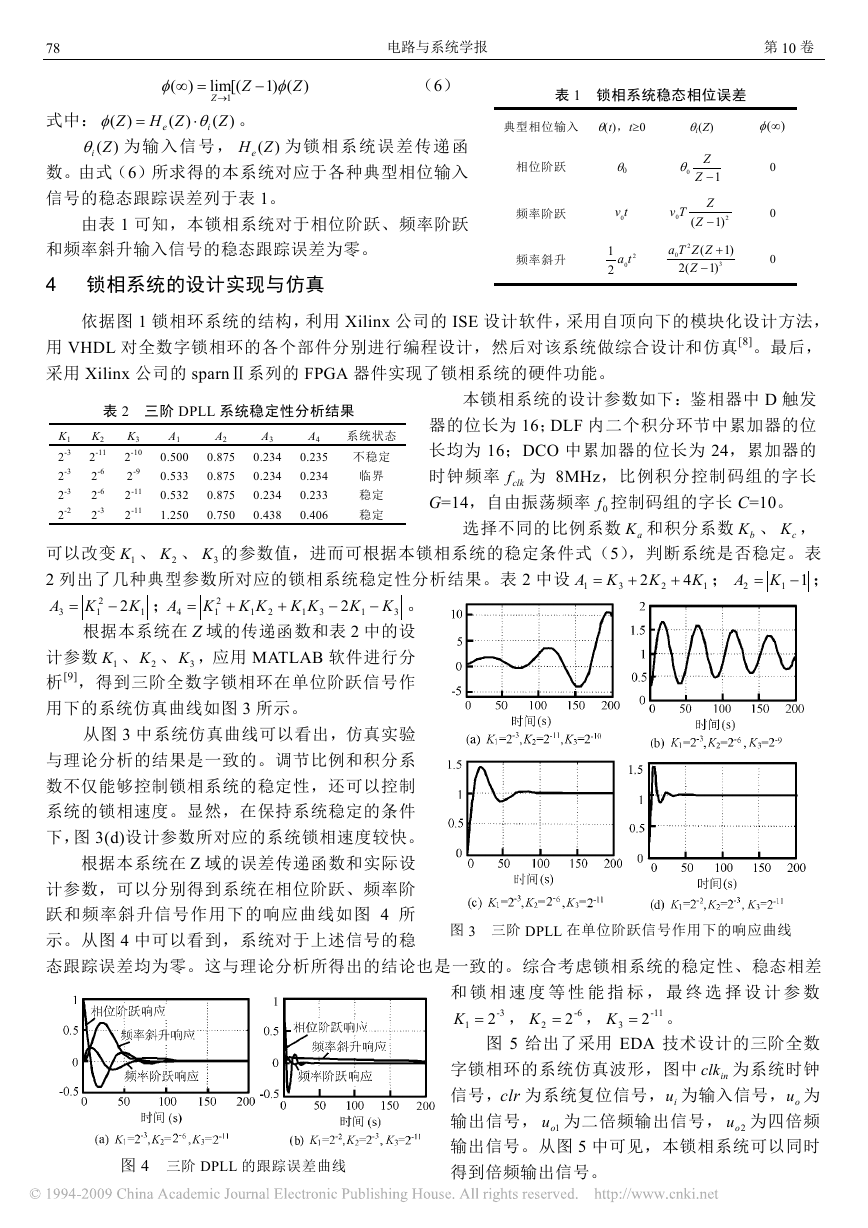

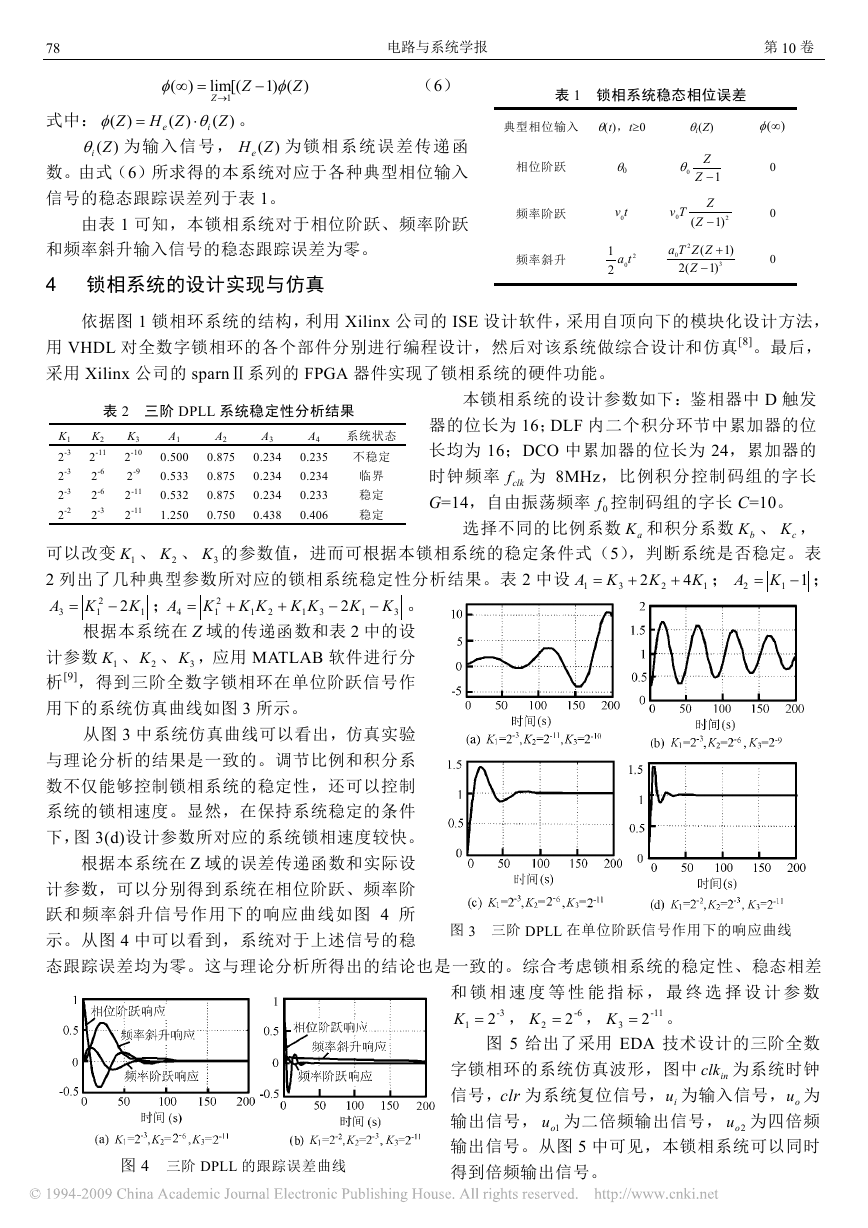

根据本系统在 Z 域的传递函数和表 2 中的设

计参数 1K 、 2K 、 3K ,应用 MATLAB 软件进行分

析[9],得到三阶全数字锁相环在单位阶跃信号作

用下的系统仿真曲线如图 3 所示。

K

−

1

3

从图 3 中系统仿真曲线可以看出,仿真实验

与理论分析的结果是一致的。调节比例和积分系

数不仅能够控制锁相系统的稳定性,还可以控制

系统的锁相速度。显然,在保持系统稳定的条件

下,图 3(d)设计参数所对应的系统锁相速度较快。

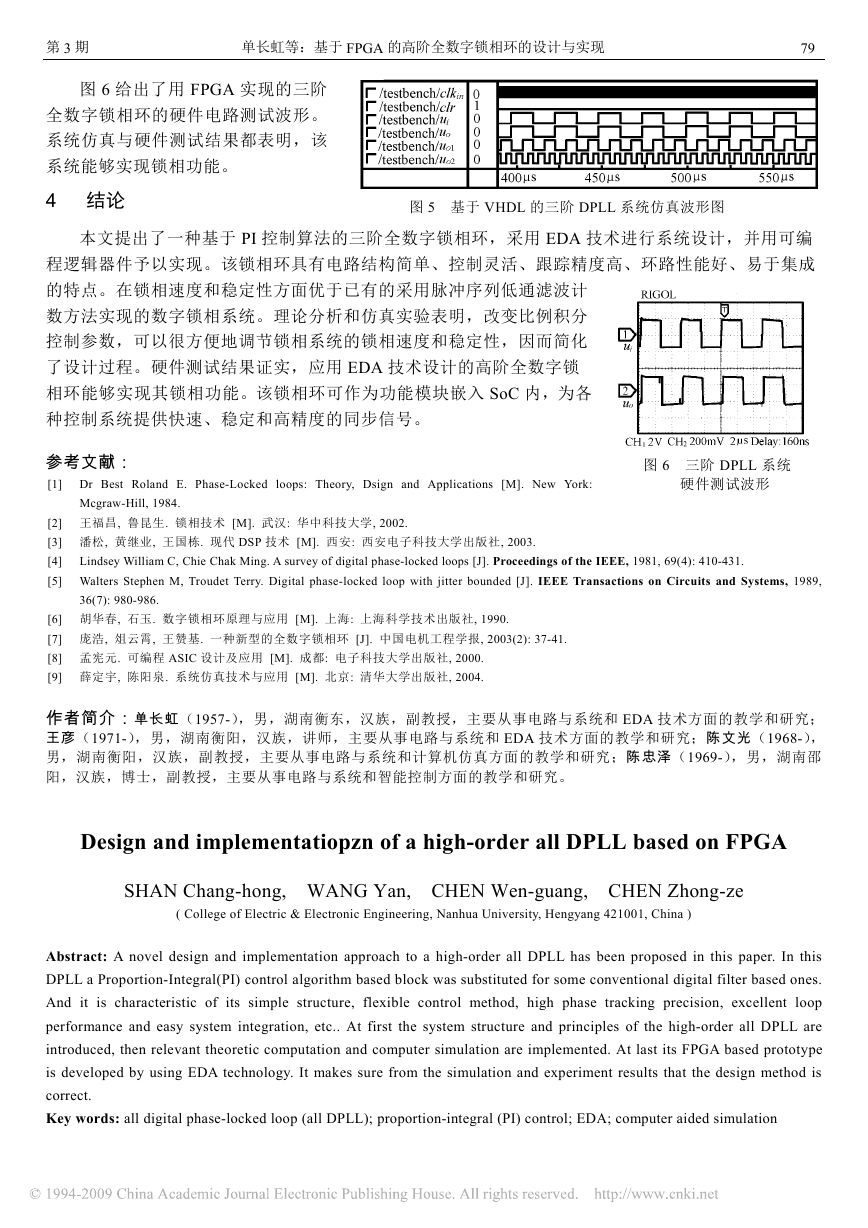

根据本系统在 Z 域的误差传递函数和实际设

计参数,可以分别得到系统在相位阶跃、频率阶

跃和频率斜升信号作用下的响应曲线如图 4 所

示。从图 4 中可以看到,系统对于上述信号的稳

态跟踪误差均为零。这与理论分析所得出的结论也是一致的。综合考虑锁相系统的稳定性、稳态相差

图 3 三阶 DPLL 在单位阶跃信号作用下的响应曲线

和 锁 相 速 度 等 性 能 指 标 , 最 终 选 择 设 计 参 数

2=K

2=K

2=K

。

,

,

-11

-3

-6

1

2

3

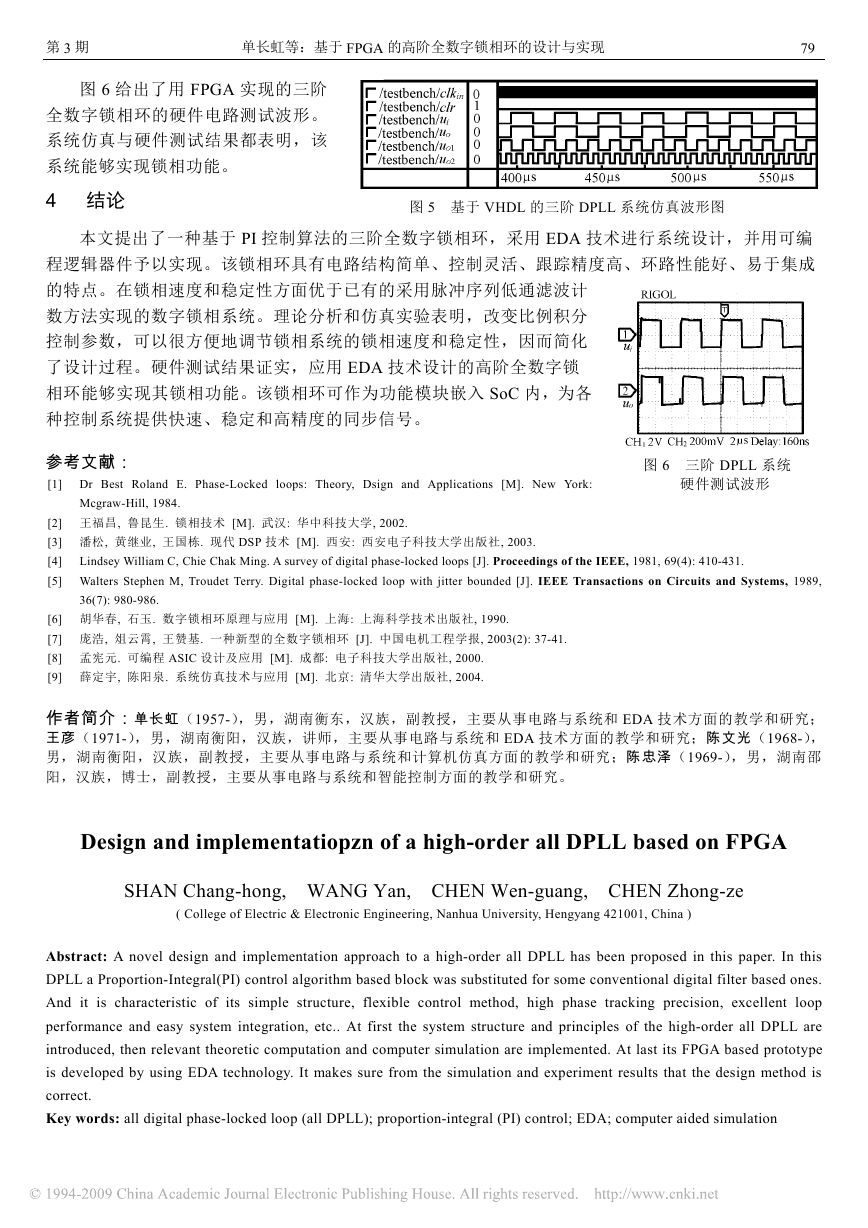

图 5 给出了采用 EDA 技术设计的三阶全数

clk 为系统时钟

字锁相环的系统仿真波形,图中 in

信号,clr 为系统复位信号, iu 为输入信号, ou 为

输出信号, 1ou 为二倍频输出信号, 2ou 为四倍频

输出信号。从图 5 中可见,本锁相系统可以同时

得到倍频输出信号。

图 4 三阶 DPLL 的跟踪误差曲线

�

第 3 期 单长虹等:基于 FPGA 的高阶全数字锁相环的设计与实现 79

图 6 给出了用 FPGA 实现的三阶

全数字锁相环的硬件电路测试波形。

系统仿真与硬件测试结果都表明,该

系统能够实现锁相功能。

4 结论

图 5 基于 VHDL 的三阶 DPLL 系统仿真波形图

本文提出了一种基于 PI 控制算法的三阶全数字锁相环,采用 EDA 技术进行系统设计,并用可编

程逻辑器件予以实现。该锁相环具有电路结构简单、控制灵活、跟踪精度高、环路性能好、易于集成

的特点。在锁相速度和稳定性方面优于已有的采用脉冲序列低通滤波计

数方法实现的数字锁相系统。理论分析和仿真实验表明,改变比例积分

控制参数,可以很方便地调节锁相系统的锁相速度和稳定性,因而简化

了设计过程。硬件测试结果证实,应用 EDA 技术设计的高阶全数字锁

相环能够实现其锁相功能。该锁相环可作为功能模块嵌入 SoC 内,为各

种控制系统提供快速、稳定和高精度的同步信号。

参考文献:

[1] Dr Best Roland E. Phase-Locked loops: Theory, Dsign and Applications [M]. New York:

图 6 三阶 DPLL 系统

硬件测试波形

Mcgraw-Hill, 1984.

[2] 王福昌, 鲁昆生. 锁相技术 [M]. 武汉: 华中科技大学, 2002.

[3] 潘松, 黄继业, 王国栋. 现代 DSP 技术 [M]. 西安: 西安电子科技大学出版社, 2003.

[4] Lindsey William C, Chie Chak Ming. A survey of digital phase-locked loops [J]. Proceedings of the IEEE, 1981, 69(4): 410-431.

[5] Walters Stephen M, Troudet Terry. Digital phase-locked loop with jitter bounded [J]. IEEE Transactions on Circuits and Systems, 1989,

36(7): 980-986.

[6] 胡华春, 石玉. 数字锁相环原理与应用 [M]. 上海: 上海科学技术出版社, 1990.

[7] 庞浩, 俎云霄, 王赞基. 一种新型的全数字锁相环 [J]. 中国电机工程学报, 2003(2): 37-41.

[8] 孟宪元. 可编程 ASIC 设计及应用 [M]. 成都: 电子科技大学出版社, 2000.

[9] 薛定宇, 陈阳泉. 系统仿真技术与应用 [M]. 北京: 清华大学出版社, 2004.

作者简介:单长虹(1957-),男,湖南衡东,汉族,副教授,主要从事电路与系统和 EDA 技术方面的教学和研究;

王彦(1971-),男,湖南衡阳,汉族,讲师,主要从事电路与系统和 EDA 技术方面的教学和研究;陈文光(1968-),

男,湖南衡阳,汉族,副教授,主要从事电路与系统和计算机仿真方面的教学和研究;陈忠泽(1969-),男,湖南邵

阳,汉族,博士,副教授,主要从事电路与系统和智能控制方面的教学和研究。

Design and implementatiopzn of a high-order all DPLL based on FPGA

SHAN Chang-hong, WANG Yan, CHEN Wen-guang, CHEN Zhong-ze

( College of Electric & Electronic Engineering, Nanhua University, Hengyang 421001, China )

Abstract: A novel design and implementation approach to a high-order all DPLL has been proposed in this paper. In this

DPLL a Proportion-Integral(PI) control algorithm based block was substituted for some conventional digital filter based ones.

And it is characteristic of its simple structure, flexible control method, high phase tracking precision, excellent loop

performance and easy system integration, etc.. At first the system structure and principles of the high-order all DPLL are

introduced, then relevant theoretic computation and computer simulation are implemented. At last its FPGA based prototype

is developed by using EDA technology. It makes sure from the simulation and experiment results that the design method is

correct.

Key words: all digital phase-locked loop (all DPLL); proportion-integral (PI) control; EDA; computer aided simulation

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc