封面

Notice

关于CMOS器件的注意事项

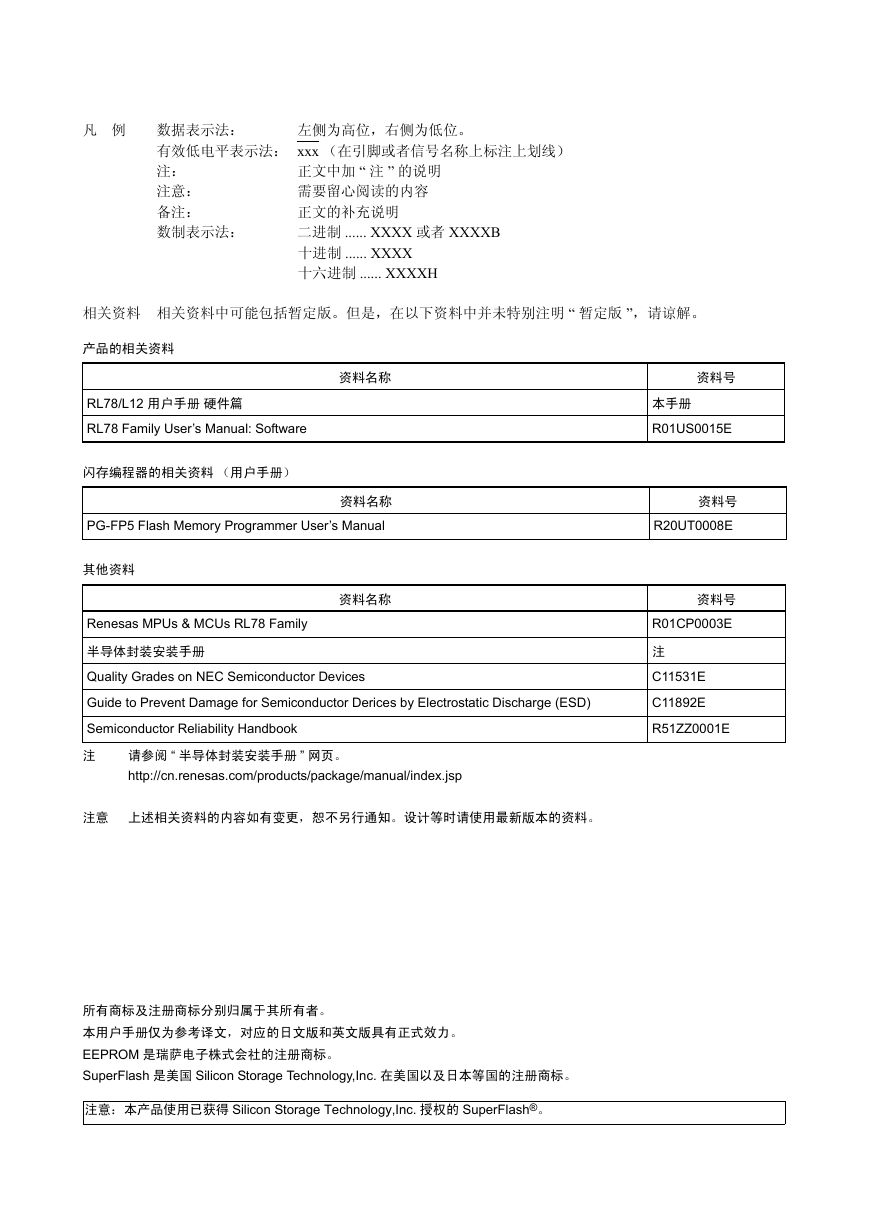

本手册的使用方法

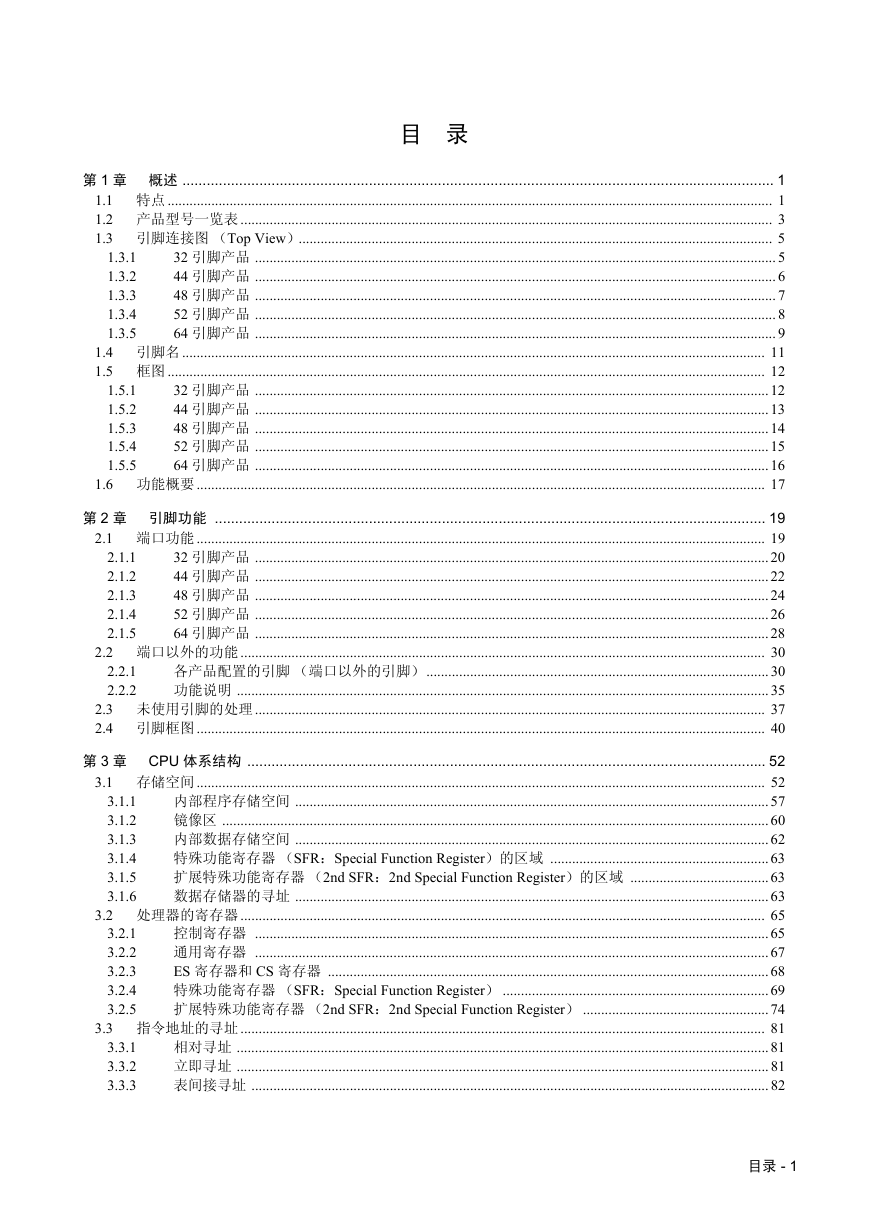

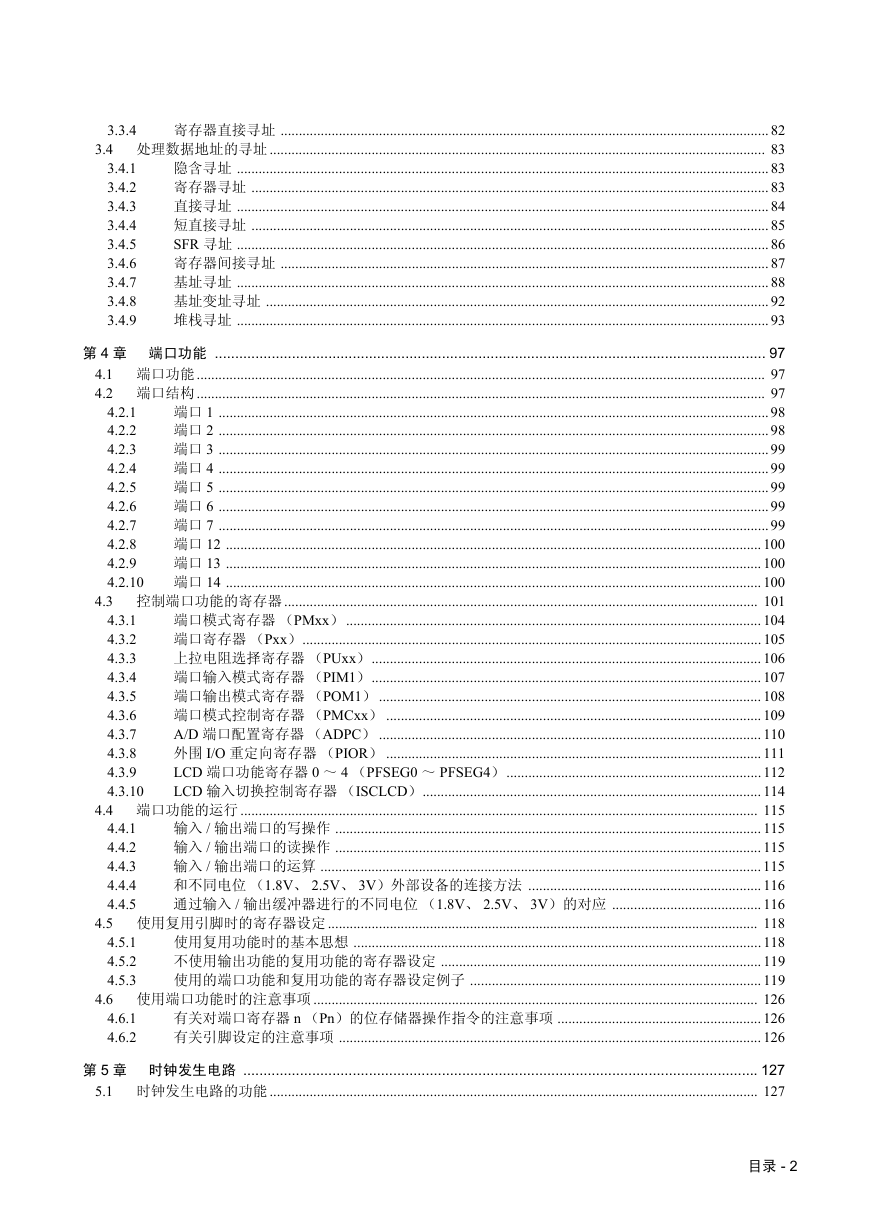

目录

第1章 概述

1.1 特点

1.2 产品型号一览表

1.3 引脚连接图(Top View)

1.3.1 32引脚产品

1.3.2 44引脚产品

1.3.3 48引脚产品

1.3.4 52引脚产品

1.3.5 64引脚产品

1.4 引脚名

1.5 框图

1.5.1 32引脚产品

1.5.2 44引脚产品

1.5.3 48引脚产品

1.5.4 52引脚产品

1.5.5 64引脚产品

1.6 功能概要

第2章 引脚功能

2.1 端口功能

2.1.1 32引脚产品

2.1.2 44引脚产品

2.1.3 48引脚产品

2.1.4 52引脚产品

2.1.5 64引脚产品

2.2 端口以外的功能

2.2.1 各产品配置的引脚(端口以外的引脚)

2.2.2 功能说明

2.3 未使用引脚的处理

2.4 引脚框图

第3章 CPU体系结构

3.1 存储空间

3.1.1 内部程序存储空间

3.1.2 镜像区

3.1.3 内部数据存储空间

3.1.4 特殊功能寄存器(SFR:Special Function Register)的区域

3.1.5 扩展特殊功能寄存器(2nd SFR:2nd Special Function Register)的区域

3.1.6 数据存储器的寻址

3.2 处理器的寄存器

3.2.1 控制寄存器

3.2.2 通用寄存器

3.2.3 ES寄存器和CS寄存器

3.2.4 特殊功能寄存器(SFR:Special Function Register)

3.2.5 扩展特殊功能寄存器(2nd SFR:2nd Special Function Register)

3.3 指令地址的寻址

3.3.1 相对寻址

3.3.2 立即寻址

3.3.3 表间接寻址

3.3.4 寄存器直接寻址

3.4 处理数据地址的寻址

3.4.1 隐含寻址

3.4.2 寄存器寻址

3.4.3 直接寻址

3.4.4 短直接寻址

3.4.5 SFR寻址

3.4.6 寄存器间接寻址

3.4.7 基址寻址

3.4.8 基址变址寻址

3.4.9 堆栈寻址

第4章 端口功能

4.1 端口功能

4.2 端口结构

4.2.1 端口1

4.2.2 端口2

4.2.3 端口3

4.2.4 端口4

4.2.5 端口5

4.2.6 端口6

4.2.7 端口7

4.2.8 端口12

4.2.9 端口13

4.2.10 端口14

4.3 控制端口功能的寄存器

4.3.1 端口模式寄存器(PMxx)

4.3.2 端口寄存器(Pxx)

4.3.3 上拉电阻选择寄存器(PUxx)

4.3.4 端口输入模式寄存器(PIM1)

4.3.5 端口输出模式寄存器(POM1)

4.3.6 端口模式控制寄存器(PMCxx)

4.3.7 A/D端口配置寄存器(ADPC)

4.3.8 外围I/O重定向寄存器(PIOR)

4.3.9 LCD端口功能寄存器0~4(PFSEG0~PFSEG4)

4.3.10 LCD输入切换控制寄存器(ISCLCD)

4.4 端口功能的运行

4.4.1 输入/输出端口的写操作

4.4.2 输入/输出端口的读操作

4.4.3 输入/输出端口的运算

4.4.4 和不同电位(1.8V、2.5V、3V)外部设备的连接方法

4.4.5 通过输入/输出缓冲器进行的不同电位(1.8V、2.5V、3V)的对应

4.5 使用复用引脚时的寄存器设定

4.5.1 使用复用功能时的基本思想

4.5.2 不使用输出功能的复用功能的寄存器设定

4.5.3 使用的端口功能和复用功能的寄存器设定例子

4.6 使用端口功能时的注意事项

4.6.1 有关对端口寄存器n(Pn)的位存储器操作指令的注意事项

4.6.2 有关引脚设定的注意事项

第5章 时钟发生电路

5.1 时钟发生电路的功能

5.2 时钟发生电路的结构

5.3 控制时钟发生电路的寄存器

5.3.1 时钟运行模式控制寄存器(CMC)

5.3.2 系统时钟控制寄存器(CKC)

5.3.3 时钟运行状态控制寄存器(CSC)

5.3.4 振荡稳定时间计数器的状态寄存器(OSTC)

5.3.5 振荡稳定时间选择寄存器(OSTS)

5.3.6 外围允许寄存器0(PER0)

5.3.7 副系统时钟提供模式控制寄存器(OSMC)

5.3.8 高速内部振荡器的频率选择寄存器(HOCODIV)

5.3.9 高速内部振荡器的微调寄存器(HIOTRM)

5.4 系统时钟振荡电路

5.4.1 X1振荡电路

5.4.2 XT1振荡电路

5.4.3 高速内部振荡器

5.4.4 低速内部振荡器

5.5 时钟发生电路的运行

5.6 时钟控制

5.6.1 高速内部振荡器的设定例子

5.6.2 X1振荡电路的设定例子

5.6.3 XT1振荡电路的设定例子

5.6.4 CPU时钟的状态转移图

5.6.5 CPU时钟转移前的条件和转移后的处理

5.6.6 切换CPU时钟和系统时钟所需要的时间

5.6.7 时钟振荡停止前的条件

5.7 谐振器和振荡电路常数

第6章 定时器阵列单元

6.1 定时器阵列单元的功能

6.1.1 独立通道运行功能

6.1.2 多通道联动运行功能

6.1.3 8位定时器运行功能(只限于通道1和通道3)

6.1.4 LIN-bus支持功能(只限于通道5)

6.2 定时器阵列单元的结构

6.2.1 定时器计数寄存器mn(TCRmn)

6.2.2 定时器数据寄存器mn(TDRmn)

6.3 控制定时器阵列单元的寄存器

6.3.1 外围允许寄存器0(PER0)

6.3.2 定时器时钟选择寄存器m(TPSm)

6.3.3 定时器模式寄存器mn(TMRmn)

6.3.4 定时器状态寄存器mn(TSRmn)

6.3.5 定时器通道允许状态寄存器m(TEm)

6.3.6 定时器通道开始寄存器m(TSm)

6.3.7 定时器通道停止寄存器m(TTm)

6.3.8 定时器输入选择寄存器0(TIS0)

6.3.9 定时器输出选择寄存器(TOS)

6.3.10 定时器输出允许寄存器m(TOEm)

6.3.11 定时器输出寄存器m(TOm)

6.3.12 定时器输出电平寄存器m(TOLm)

6.3.13 定时器输出模式寄存器m(TOMm)

6.3.14 输入切换控制寄存器(ISC)

6.3.15 噪声滤波器允许寄存器1(NFEN1)

6.3.16 端口模式寄存器1、3~5、14(PM1、PM3~PM5、PM14)

6.4 定时器阵列单元的基本规则

6.4.1 多通道联动运行功能的基本规则

6.4.2 8位定时器运行功能的基本规则(只限于通道1和通道3)

6.5 计数器的运行

6.5.1 计数时钟(fTCLK)

6.5.2 计数器的开始时序

6.5.3 计数器的运行

6.6 通道输出(TOmn引脚)的控制

6.6.1 TOmn引脚输出电路的结构

6.6.2 TOmn引脚的输出设定

6.6.3 通道输出运行的注意事项

6.6.4 TOmn位的一次性操作

6.6.5 有关开始计数时的定时器中断和TOmn引脚输出

6.7 定时器输入(TImn)的控制

6.7.1 TImn引脚输入电路的结构

6.7.2 噪声滤波器

6.7.3 操作通道输入时的注意事项

6.8 定时器阵列单元的独立通道运行功能

6.8.1 作为间隔定时器/方波输出的运行

6.8.2 作为外部事件计数器的运行

6.8.3 作为分频器的运行(只限于通道0)

6.8.4 作为输入脉冲间隔测量的运行

6.8.5 作为输入信号高低电平宽度测量的运行

6.8.6 作为延迟计数器的运行

6.9 定时器阵列单元的多通道联动运行功能

6.9.1 作为单触发脉冲输出功能的运行

6.9.2 作为PWM功能的运行

6.9.3 作为多重PWM输出功能的运行

6.9.4 遥控输出功能

第7章 实时时钟

7.1 实时时钟的功能

7.2 实时时钟的结构

7.3 控制实时时钟的寄存器

7.3.1 外围允许寄存器0(PER0)

7.3.2 副系统时钟提供模式控制寄存器(OSMC)

7.3.3 实时时钟控制寄存器0(RTCC0)

7.3.4 实时时钟控制寄存器1(RTCC1)

7.3.5 秒计数寄存器(SEC)

7.3.6 分钟计数寄存器(MIN)

7.3.7 小时计数寄存器(HOUR)

7.3.8 日计数寄存器(DAY)

7.3.9 星期计数寄存器(WEEK)

7.3.10 月计数寄存器(MONTH)

7.3.11 年计数寄存器(YEAR)

7.3.12 时钟误差校正寄存器(SUBCUD)

7.3.13 闹钟分钟寄存器(ALARMWM)

7.3.14 闹钟小时寄存器(ALARMWH)

7.3.15 闹钟星期寄存器(ALARMWW)

7.3.16 端口模式寄存器3(PM3)

7.3.17 端口寄存器3(P3)

7.4 实时时钟的运行

7.4.1 实时时钟的运行开始

7.4.2 开始运行后HALT/STOP模式的转移

7.4.3 实时时钟计数器的读写

7.4.4 实时时钟的闹钟设定

7.4.5 实时时钟的1Hz输出

7.4.6 实时时钟的时钟误差校正例子

第8章 12位间隔定时器

8.1 12位间隔定时器的功能

8.2 12位间隔定时器的结构

8.3 控制12位间隔定时器的寄存器

8.3.1 外围允许寄存器0(PER0)

8.3.2 副系统时钟提供模式控制寄存器(OSMC)

8.3.3 间隔定时器的控制寄存器(ITMC)

8.4 12位间隔定时器的运行

8.4.1 12位间隔定时器的运行时序

8.4.2 从HALT/STOP模式返回后开始计数器的运行并且再次向HALT/STOP模式的转移

第9章 时钟输出/蜂鸣器输出控制电路

9.1 时钟输出/蜂鸣器输出控制电路的功能

9.2 时钟输出/蜂鸣器输出控制电路的结构

9.3 控制时钟输出/蜂鸣器输出控制电路的寄存器

9.3.1 外围允许寄存器0(PER0)

9.3.2 时钟输出选择寄存器n(CKSn)

9.3.3 端口模式寄存器5、14(PM5、PM14)

9.4 时钟输出/蜂鸣器输出控制电路的运行

9.4.1 输出引脚的运行

9.5 时钟输出/蜂鸣器输出控制电路的注意事项

第10章 看门狗定时器

10.1 看门狗定时器的功能

10.2 看门狗定时器的结构

10.3 控制看门狗定时器的寄存器

10.3.1 看门狗定时器的允许寄存器(WDTE)

10.4 看门狗定时器的运行

10.4.1 看门狗定时器的运行控制

10.4.2 看门狗定时器上溢时间的设定

10.4.3 看门狗定时器窗口打开期间的设定

10.4.4 看门狗定时器间隔中断的设定

第11章 A/D转换器

11.1 A/D转换器的功能

11.2 A/D转换器的结构

11.3 A/D转换器使用的寄存器

11.3.1 外围允许寄存器0(PER0)

11.3.2 A/D转换器的模式寄存器0(ADM0)

11.3.3 A/D转换器的模式寄存器1(ADM1)

11.3.4 A/D转换器的模式寄存器2(ADM2)

11.3.5 10位A/D转换结果寄存器(ADCR)

11.3.6 8位A/D转换结果寄存器(ADCRH)

11.3.7 模拟输入通道指定寄存器(ADS)

11.3.8 转换结果比较上限值设定寄存器(ADUL)

11.3.9 转换结果比较下限值设定寄存器(ADLL)

11.3.10 A/D测试寄存器(ADTES)

11.3.11 控制模拟输入引脚端口功能的寄存器

11.4 A/D转换器的转换运行

11.5 输入电压和转换结果

11.6 A/D转换器的运行模式

11.6.1 软件触发模式(连续转换模式)

11.6.2 软件触发模式(单次转换模式)

11.6.3 硬件触发无等待模式(连续转换模式)

11.6.4 硬件触发无等待模式(单次转换模式)

11.6.5 硬件触发等待模式(连续转换模式)

11.6.6 硬件触发等待模式(单次转换模式)

11.7 A/D转换器的设定流程图

11.7.1 软件触发模式的设定

11.7.2 硬件触发无等待模式的设定

11.7.3 硬件触发等待模式的设定

11.7.4 选择温度传感器输出/内部基准电压输出时的设定 (以软件触发模式、单次转换模式为例)

11.7.5 测试模式的设定

11.8 SNOOZE模式功能

11.9 A/D转换器特性表的阅读方法

11.10 A/D转换器的注意事项

第12章 串行阵列单元

12.1 串行阵列单元的功能

12.1.1 3线串行I/O(CSI00、CSI01)

12.1.2 UART(UART0)

12.2 串行阵列单元的结构

12.2.1 移位寄存器

12.2.2 串行数据寄存器mn(SDRmn)的低9位

12.3 控制串行阵列单元的寄存器

12.3.1 外围允许寄存器0(PER0)

12.3.2 串行时钟选择寄存器m(SPSm)

12.3.3 串行模式寄存器mn(SMRmn)

12.3.4 串行通信运行设定寄存器mn(SCRmn)

12.3.5 串行数据寄存器mn(SDRmn)的高7位

12.3.6 串行标志清除触发寄存器mn(SIRmn)

12.3.7 串行状态寄存器mn(SSRmn)

12.3.8 串行通道开始寄存器m(SSm)

12.3.9 串行通道停止寄存器m(STm)

12.3.10 串行通道允许状态寄存器m(SEm)

12.3.11 串行输出允许寄存器m(SOEm)

12.3.12 串行输出寄存器m(SOm)

12.3.13 串行输出电平寄存器m(SOLm)

12.3.14 串行待机控制寄存器m(SSCm)

12.3.15 输入切换控制寄存器(ISC)

12.3.16 噪声滤波器允许寄存器0(NFEN0)

12.3.17 控制串行输入/输出引脚端口功能的寄存器

12.4 运行停止模式

12.4.1 以单元为单位停止运行的情况

12.4.2 按通道停止运行的情况

12.5 3线串行I/O(CSI00、CSI01)通信的运行

12.5.1 主控发送

12.5.2 主控接收

12.5.3 主控的发送和接收

12.5.4 从属发送

12.5.5 从属接收

12.5.6 从属发送和接收

12.5.7 SNOOZE模式功能

12.5.8 传送时钟频率的计算

12.5.9 在3线串行I/O(CSI00、CSI01)通信过程中发生错误时的处理步骤

12.6 UART(UART0)通信的运行

12.6.1 UART发送

12.6.2 UART接收

12.6.3 SNOOZE模式功能

12.6.4 波特率的计算

12.6.5 UART(UART0)通信过程中发生错误时的处理步骤

12.7 LIN通信的运行

12.7.1 LIN发送

12.7.2 LIN接收

第13章 串行接口IICA

13.1 串行接口IICA的功能

13.2 串行接口IICA的结构

13.3 控制串行接口IICA的寄存器

13.3.1 外围允许寄存器0(PER0)

13.3.2 IICA控制寄存器00(IICCTL00)

13.3.3 IICA状态寄存器0(IICS0)

13.3.4 IICA标志寄存器0(IICF0)

13.3.5 IICA控制寄存器01(IICCTL01)

13.3.6 IICA低电平宽度设定寄存器0(IICWL0)

13.3.7 IICA高电平宽度设定寄存器0(IICWH0)

13.3.8 端口模式寄存器6(PM6)

13.4 I2C总线模式的功能

13.4.1 引脚结构

13.4.2 通过IICWL0寄存器和IICWH0寄存器设定传送时钟的方法

13.5 I2C总线的定义和控制方法

13.5.1 开始条件

13.5.2 地址

13.5.3 传送方向的指定

13.5.4 应答(ACK)

13.5.5 停止条件

13.5.6 等待

13.5.7 等待的解除方法

13.5.8 中断请求(INTIICA0)的产生时序和等待控制

13.5.9 地址匹配的检测方法

13.5.10 错误的检测

13.5.11 扩展码

13.5.12 仲裁

13.5.13 唤醒功能

13.5.14 通信预约

13.5.15 其他注意事项

13.5.16 通信运行

13.5.17 I2C中断请求(INTIICA0)的产生时序

13.6 时序图

第14章 LCD控制器/驱动器

14.1 LCD控制器/驱动器的功能

14.2 LCD控制器/驱动器的结构

14.3 控制LCD控制器/驱动器的寄存器

14.3.1 外围允许寄存器0(PER0)

14.3.2 LCD模式寄存器0(LCDM0)

14.3.3 LCD模式寄存器1(LCDM1)

14.3.4 副系统时钟提供模式控制寄存器(OSMC)

14.3.5 LCD时钟控制寄存器0(LCDC0)

14.3.6 LCD升压电平控制寄存器(VLCD)

14.3.7 LCD输入切换控制寄存器(ISCLCD)

14.3.8 LCD端口功能寄存器0~4(PFSEG0~PFSEG4)

14.3.9 端口模式寄存器1、3~7、12、14(PM1、PM3~PM7、PM12、PM14)

14.4 LCD显示数据寄存器

14.5 LCD显示寄存器的选择

14.5.1 A图形区和B图形区的数据显示

14.5.2 闪烁显示(A图形区和B图形区的数据的交替显示)

14.6 LCD控制器/驱动器的设定

14.7 运行停止步骤

14.8 LCD驱动电压VL1、VL2、VL3、VL4的提供

14.8.1 外部电阻分割方式

14.8.2 内部升压方式

14.8.3 电容分割方式

14.9 公共信号和段信号

14.9.1 通常液晶波形的情况

14.10 显示模式

14.10.1 静态显示例子

14.10.2 2个时间片的显示例子

14.10.3 3个时间片的显示例子

14.10.4 4个时间片的显示例子

14.10.5 8个时间片的显示例子

第15章 乘除器和乘加器

15.1 乘除器和乘加器的功能

15.2 乘除器和乘加器的结构

15.2.1 乘除数据寄存器A(MDAH、MDAL)

15.2.2 乘除数据寄存器B(MDBL、MDBH)

15.2.3 乘除数据寄存器C(MDCL、MDCH)

15.3 控制乘除器和乘加器的寄存器

15.3.1 乘除控制寄存器(MDUC)

15.4 乘除器和乘加器的运算

15.4.1 乘法运算(无符号)

15.4.2 乘法运算(带符号)

15.4.3 乘加运算(无符号)

15.4.4 乘加运算(带符号)

15.4.5 除法运算

第16章 DMA控制器

16.1 DMA控制器的功能

16.2 DMA控制器的结构

16.2.1 DMA SFR地址寄存器n(DSAn)

16.2.2 DMA RAM地址寄存器n(DRAn)

16.2.3 DMA字节计数寄存器n(DBCn)

16.3 控制DMA控制器的寄存器

16.3.1 DMA模式控制寄存器n(DMCn)

16.3.2 DMA运行控制寄存器n(DRCn)

16.4 DMA控制器的运行

16.4.1 运行步骤

16.4.2 传送模式

16.4.3 DMA传送的结束

16.5 DMA控制器的设定例子

16.5.1 CSI连续发送

16.5.2 A/D转换结果的连续读取

16.5.3 UART连续接收+ACK发送

16.5.4 通过DWAITn位保留DMA传送

16.5.5 通过软件强制结束

16.6 DMA控制器的注意事项

第17章 中断功能

17.1 中断功能的种类

17.2 中断源和结构

17.3 控制中断功能的寄存器

17.3.1 中断请求标志寄存器(IF0L、IF0H、IF1L、IF1H、IF2L)

17.3.2 中断屏蔽标志寄存器(MK0L、MK0H、MK1L、MK1H、MK2L)

17.3.3 优先级指定标志寄存器(PR00L、PR00H、PR01L、PR01H、PR02L、PR10L、 PR10H、PR11L、PR11H、PR12L)

17.3.4 外部中断上升沿允许寄存器(EGP0)和外部中断下降沿允许寄存器(EGN0)

17.3.5 程序状态字(PSW)

17.4 中断处理的操作

17.4.1 可屏蔽中断请求的接受

17.4.2 软件中断请求的接受

17.4.3 多重中断处理

17.4.4 中断请求的保留

第18章 键中断功能

18.1 键中断的功能

18.2 键中断的结构

18.3 控制键中断的寄存器

18.3.1 键返回控制寄存器(KRCTL)

18.3.2 键返回模式寄存器0(KRM0)

18.3.3 键返回标志寄存器(KRF)

18.3.4 端口模式寄存器1、3、7、14(PM1、PM3、PM7、PM14)

18.4 键中断功能的运行

18.4.1 不使用键中断标志的情况(KRMD=0)

18.4.2 使用键中断标志的情况(KRMD=1)

第19章 待机功能

19.1 待机功能和结构

19.1.1 待机功能

19.2 控制待机功能的寄存器

19.3 待机功能的运行

19.3.1 HALT模式

19.3.2 STOP模式

19.3.3 SNOOZE模式

第20章 复位功能

20.1 复位时序

20.2 复位期间的运行状态

20.3 确认复位源的寄存器

20.3.1 复位控制标志寄存器(RESF)

第21章 上电复位电路

21.1 上电复位电路的功能

21.2 上电复位电路的结构

21.3 上电复位电路的运行

第22章 电压检测电路

22.1 电压检测电路的功能

22.2 电压检测电路的结构

22.3 控制电压检测电路的寄存器

22.3.1 电压检测寄存器(LVIM)

22.3.2 电压检测电平寄存器(LVIS)

22.4 电压检测电路的运行

22.4.1 用作复位模式时的设定

22.4.2 用作中断模式时的设定

22.4.3 用作中断&复位模式时的设定

22.5 电压检测电路的注意事项

第23章 安全功能

23.1 安全功能的概要

23.2 安全功能使用的寄存器

23.3 安全功能的运行

23.3.1 闪存CRC运算功能(高速CRC)

23.3.2 CRC运算功能(通用CRC)

23.3.3 RAM奇偶校验错误检测功能

23.3.4 RAM保护功能

23.3.5 SFR保护功能

23.3.6 非法存储器存取检测功能

23.3.7 频率检测功能

23.3.8 A/D测试功能

第24章 稳压器

24.1 稳压器的概要

第25章 选项字节

25.1 选项字节的功能

25.1.1 用户选项字节(000C0H~000C2H)

25.1.2 片上调试选项字节(000C3H)

25.2 用户选项字节的格式

25.3 片上调试选项字节的格式

25.4 选项字节的设定

第26章 闪存

26.1 使用闪存编程器的编程方法

26.1.1 编程环境

26.1.2 通信方式

26.2 使用外部器件(内置UART)的编程方法

26.2.1 编程环境

26.2.2 通信方式

26.3 电路板上的引脚处理

26.3.1 P40/TOOL0引脚

26.3.2 RESET引脚

26.3.3 端口引脚

26.3.4 REGC引脚

26.3.5 X1引脚和X2引脚

26.3.6 电源

26.4 串行编程方法

26.4.1 串行编程的步骤

26.4.2 闪存编程模式

26.4.3 通信方式

26.4.4 通信命令

26.5 使用PG-FP5时的各命令处理时间(参考值)

26.6 自编程

26.6.1 自编程的步骤

26.6.2 闪存屏蔽窗口功能

26.7 安全设定

26.8 数据闪存

26.8.1 数据闪存的概要

26.8.2 控制数据闪存的寄存器

26.8.3 数据闪存的存取步骤

第27章 片上调试功能

27.1 和E1片上调试仿真器的连接

27.2 片上调试安全ID

27.3 用户资源的确保

第28章 十进制校正(BCD)电路

28.1 十进制校正电路的功能

28.2 十进制校正电路使用的寄存器

28.2.1 BCD校正结果寄存器(BCDADJ)

28.3 十进制校正电路的运行

第29章 指令集的概要

29.1 凡例

29.1.1 操作数的表现形式和记述方法

29.1.2 操作栏的说明

29.1.3 标志栏的说明

29.1.4 PREFIX指令

29.2 操作一览表

第30章 电特性(A、G:TA=–40~+85°C)

30.1 绝对最大额定值

30.2 振荡电路特性

30.2.1 X1、XT1振荡电路特性

30.2.2 内部振荡器特性

30.3 DC特性

30.3.1 引脚特性

30.3.2 电源电流特性

30.4 AC特性

30.4.1 基本运行

30.5 外围功能特性

30.5.1 串行阵列单元

30.5.2 串行接口IICA

30.6 模拟特性

30.6.1 A/D转换器特性

30.6.2 温度传感器/内部基准电压特性

30.6.3 POR电路特性

30.6.4 LVD电路特性

30.6.5 电源电压的上升时间

30.7 LCD特性

30.7.1 外部电阻分割方式

30.7.2 内部升压方式

30.7.3 电容分割方式

30.8 STOP模式中的数据存储器的低电源电压数据保持特性

30.9 闪存编程特性

30.10 专用闪存编程器通信(UART)

30.11 闪存编程模式的进入时序

第31章 电特性(G:TA=–40~+105°C)

31.1 绝对最大额定值

31.2 振荡电路特性

31.2.1 X1、XT1振荡电路特性

31.2.2 内部振荡器特性

31.3 DC特性

31.3.1 引脚特性

31.3.2 电源电流特性

31.4 AC特性

31.4.1 基本运行

31.5 外围功能特性

31.5.1 串行阵列单元

31.5.2 串行接口IICA

31.6 模拟特性

31.6.1 A/D转换器特性

31.6.2 温度传感器/内部基准电压特性

31.6.3 POR电路特性

31.6.4 LVD电路特性

31.6.5 电源电压的上升时间

31.7 LCD特性

31.7.1 外部电阻分割方式

31.7.2 内部升压方式

31.7.3 电容分割方式

31.8 STOP模式中的数据存储器的低电源电压数据保持特性

31.9 闪存编程特性

31.10 专用闪存编程器通信(UART)

31.11 闪存编程模式的进入时序

第32章 封装尺寸图

32.1 32引脚产品

32.2 44引脚产品

32.3 48引脚产品

32.4 52引脚产品

32.5 64引脚产品

附录A 修订记录

底页

地址栏

封底

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc