4

3

2

1

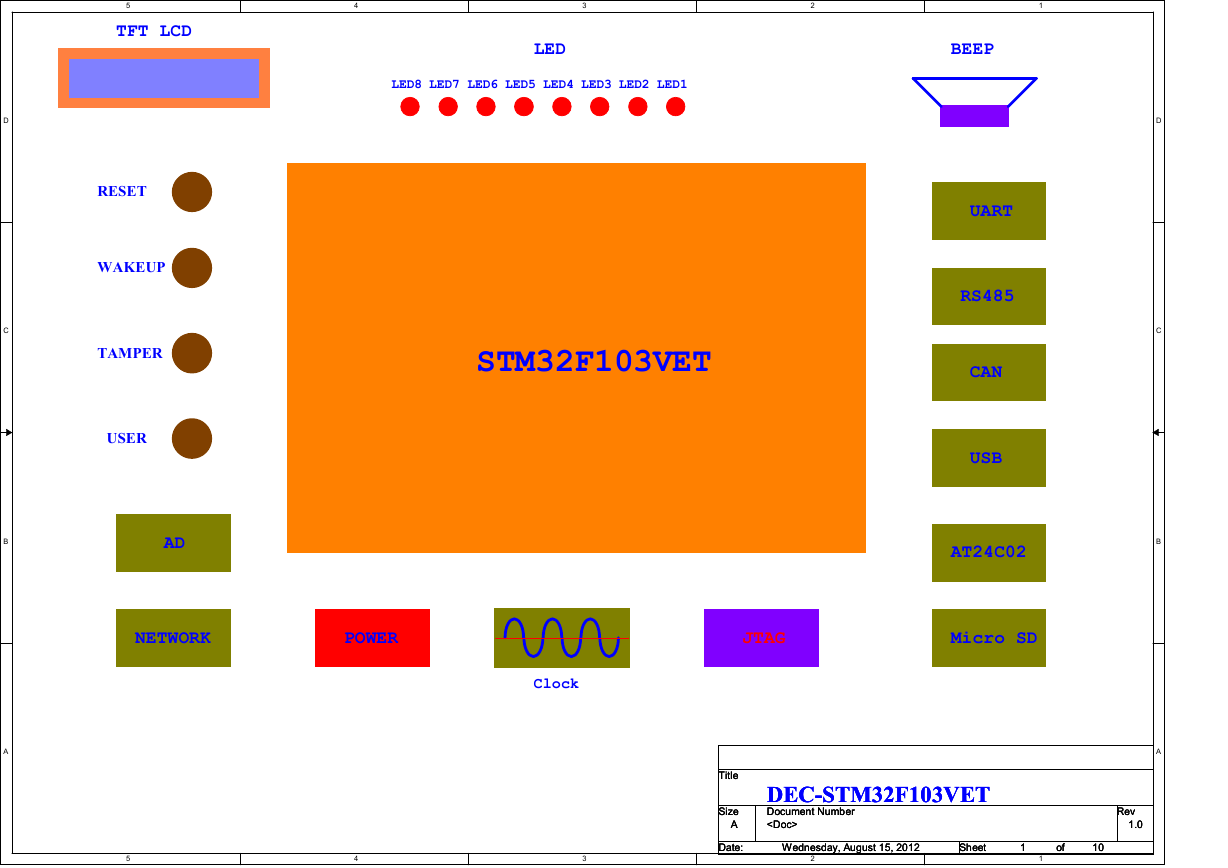

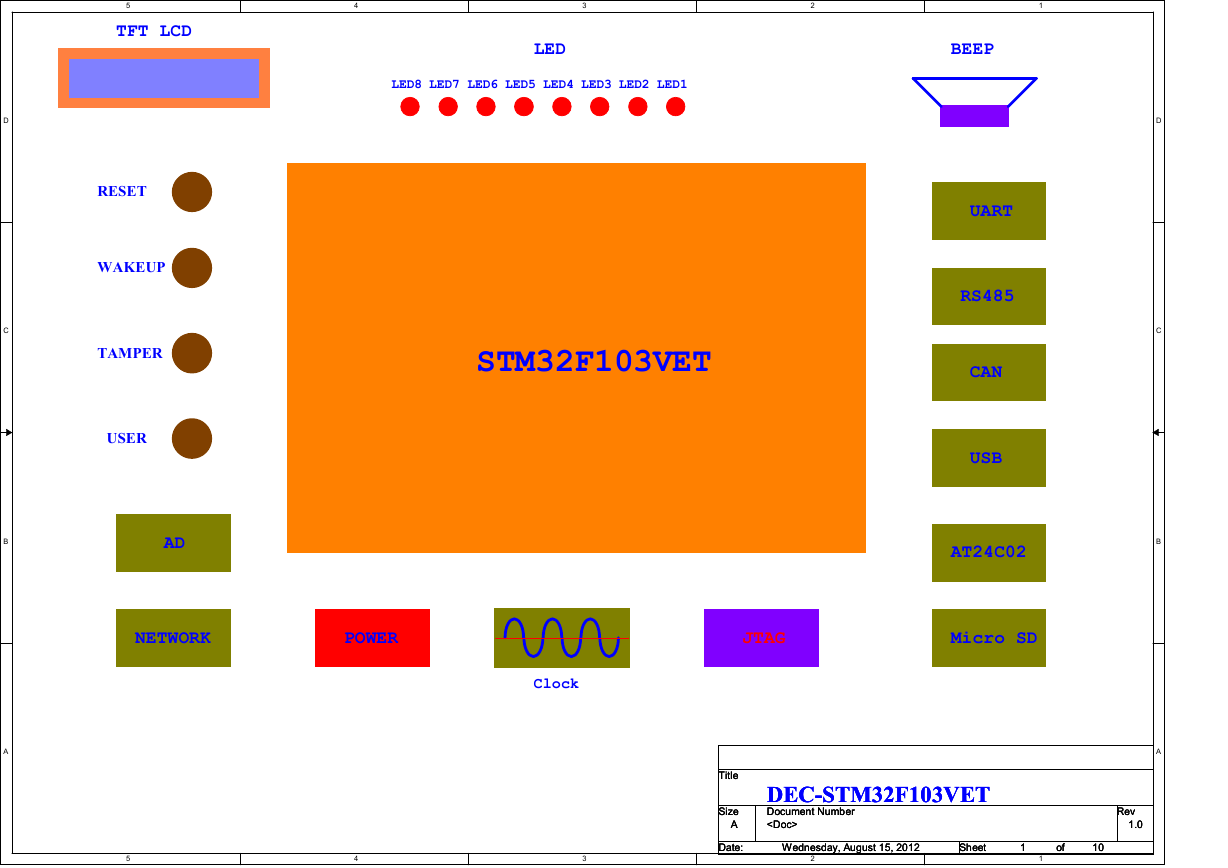

LED

LED4

LED5

LED8

LED7

LED6

LED3 LED2 LED1

STM32F103VET

5

TFT LCD

RESET

WAKEUP

TAMPER

USER

AD

D

C

B

A

BEEP

UART

RS485

CAN

USB

AT24C02

Micro SD

D

C

B

A

NETWORK

POWER

JTAG

Clock

5

4

3

Title

Title

Title

Size

Size

Size

A

A

A

Date:

Date:

Date:

DEC-STM32F103VET

DEC-STM32F103VET

DEC-STM32F103VET

Document Number

Document Number

Document Number

Rev

Rev

Rev

1.0

1.0

1.0

Wednesday, August 15, 2012

Wednesday, August 15, 2012

Wednesday, August 15, 2012

2

Sheet

Sheet

Sheet

1

1

1

1

of

of

of

10

10

10

�

D

C

B

A

4

3

2

1

5

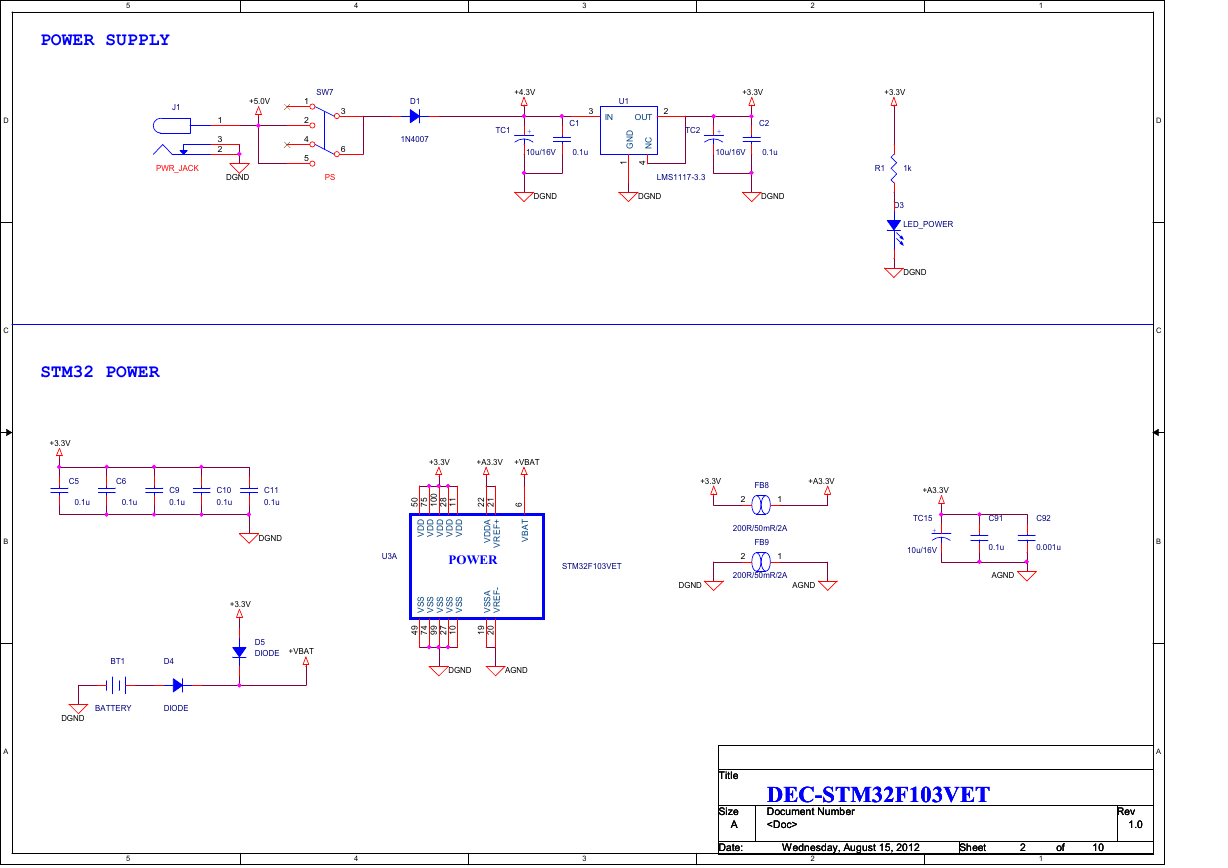

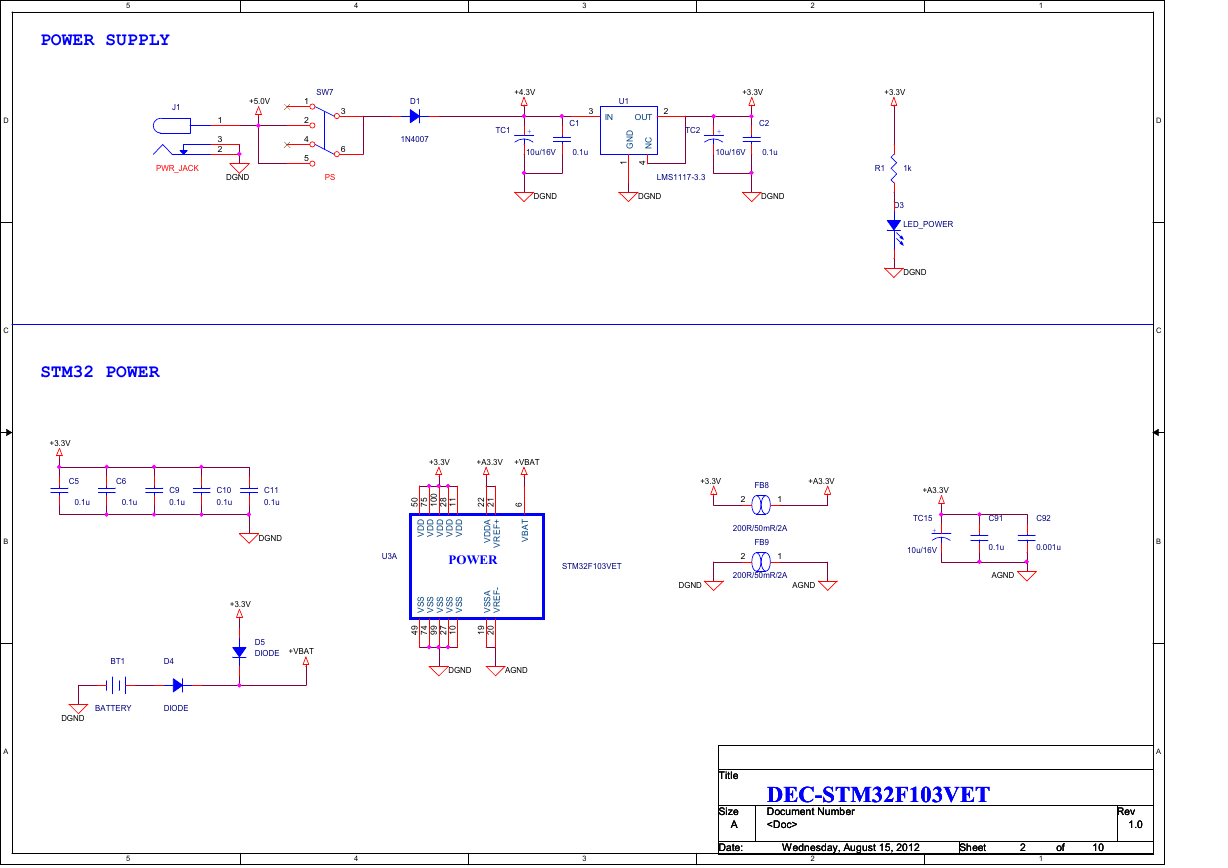

POWER SUPPLY

J1

+5.0V

1

3

2

PWR_JACK

SW7

3

6

1

2

4

5

D1

1N4007

+4.3V

TC1

+

10u/16V

0.1u

U1

IN

OUT

2

3

C1

D

N

G

C

N

1

4

+3.3V

C2

TC2

+

10u/16V

0.1u

DGND

PS

LMS1117-3.3

DGND

DGND

DGND

+3.3V

R1

1k

D3

LED_POWER

DGND

STM32 POWER

+3.3V

C5

C6

0.1u

0.1u

C9

0.1u

C10

0.1u

C11

0.1u

DGND

+3.3V

D5

DIODE

+VBAT

BT1

D4

BATTERY

DIODE

DGND

+3.3V

+A3.3V

+VBAT

0

5

5

7

0

0

1

8

2

1

1

D

D

V

D

D

V

D

D

V

D

D

V

D

D

V

2

2

1

2

6

A

D

D

V

+

F

E

R

V

T

A

B

V

U3A

POWER

STM32F103VET

S

S

V

S

S

V

S

S

V

S

S

V

S

S

V

9

4

4

7

9

9

7

2

0

1

A

S

S

V

-

F

E

R

V

9

1

0

2

DGND

AGND

+3.3V

FB8

2

1

+A3.3V

200R/50mR/2A

FB9

2

1

200R/50mR/2A

AGND

DGND

+A3.3V

TC15

+

10u/16V

C92

0.001u

C91

0.1u

AGND

5

4

3

Title

Title

Title

Size

Size

Size

A

A

A

Date:

Date:

Date:

DEC-STM32F103VET

DEC-STM32F103VET

DEC-STM32F103VET

Document Number

Document Number

Document Number

Rev

Rev

Rev

1.0

1.0

1.0

Wednesday, August 15, 2012

Wednesday, August 15, 2012

Wednesday, August 15, 2012

2

Sheet

Sheet

Sheet

2

2

2

1

of

of

of

10

10

10

D

C

B

A

�

5

4

3

2

1

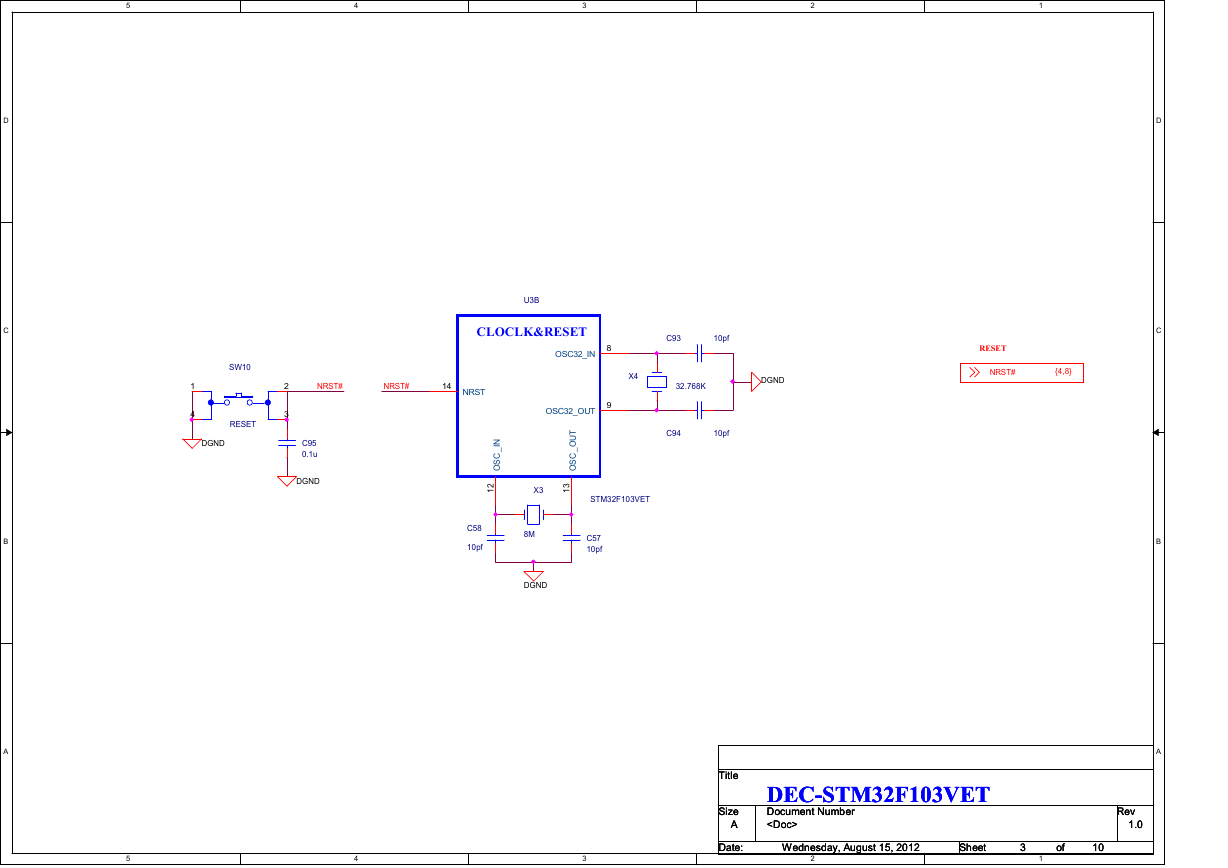

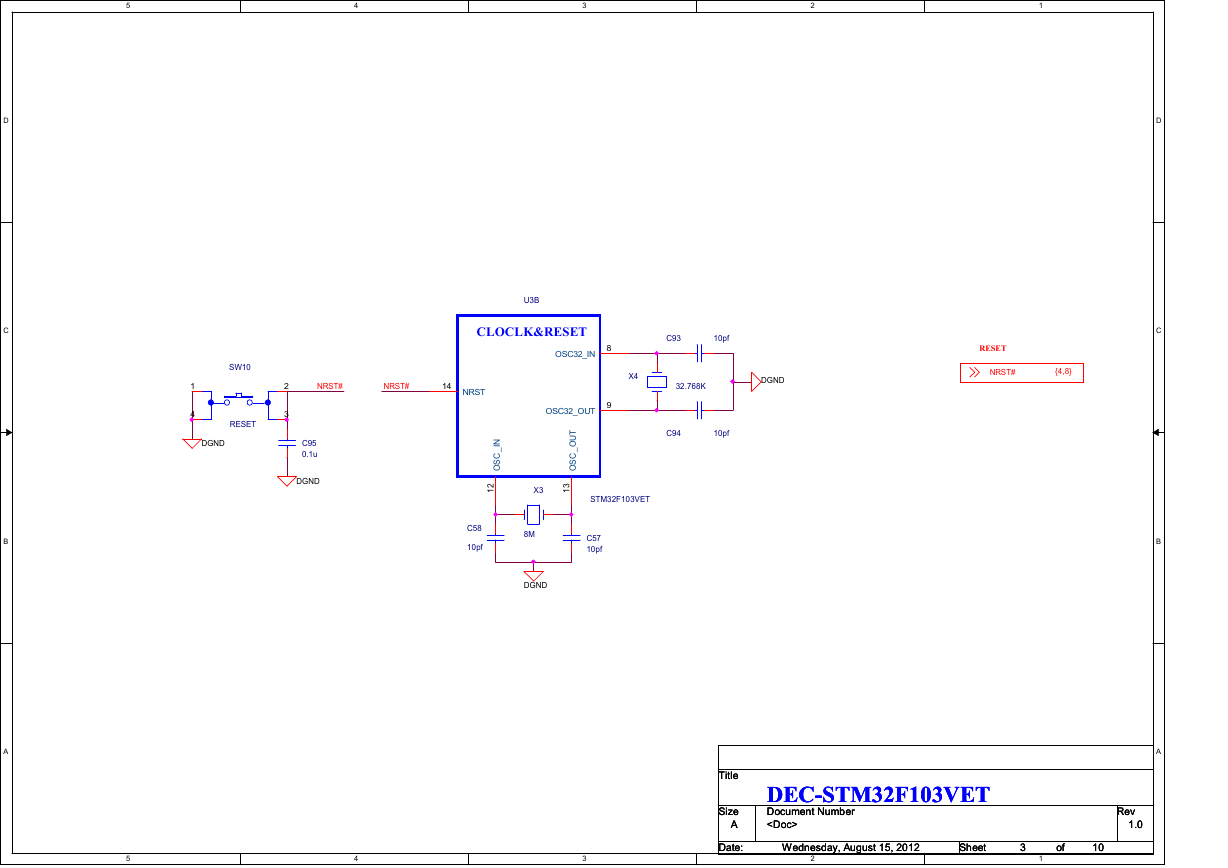

U3B

CLOCLK&RESET

OSC32_IN

NRST#

NRST#

14

NRST

C93

10pf

X4

32.768K

DGND

8

9

C94

10pf

RESET

NRST#

{4,8}

SW10

1

4

RESET

DGND

2

3

D

C

B

A

C95

0.1u

DGND

OSC32_OUT

T

U

O

_

C

S

O

I

N

_

C

S

O

2

1

X3

3

1

STM32F103VET

C58

10pf

C57

10pf

8M

DGND

D

C

B

A

5

4

3

Title

Title

Title

Size

Size

Size

A

A

A

Date:

Date:

Date:

DEC-STM32F103VET

DEC-STM32F103VET

DEC-STM32F103VET

Document Number

Document Number

Document Number

Rev

Rev

Rev

1.0

1.0

1.0

Wednesday, August 15, 2012

Wednesday, August 15, 2012

Wednesday, August 15, 2012

2

Sheet

Sheet

Sheet

3

3

3

1

of

of

of

10

10

10

�

D

C

B

A

5

4

3

2

1

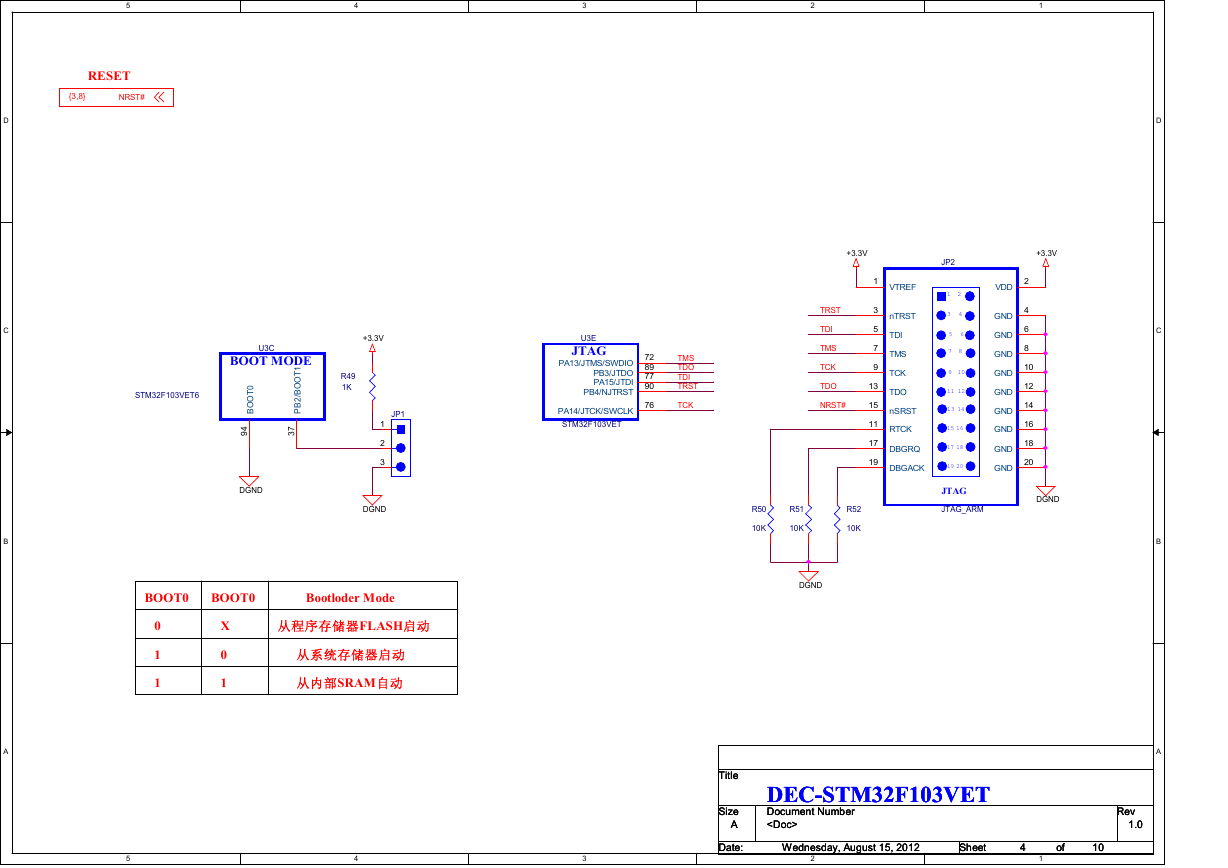

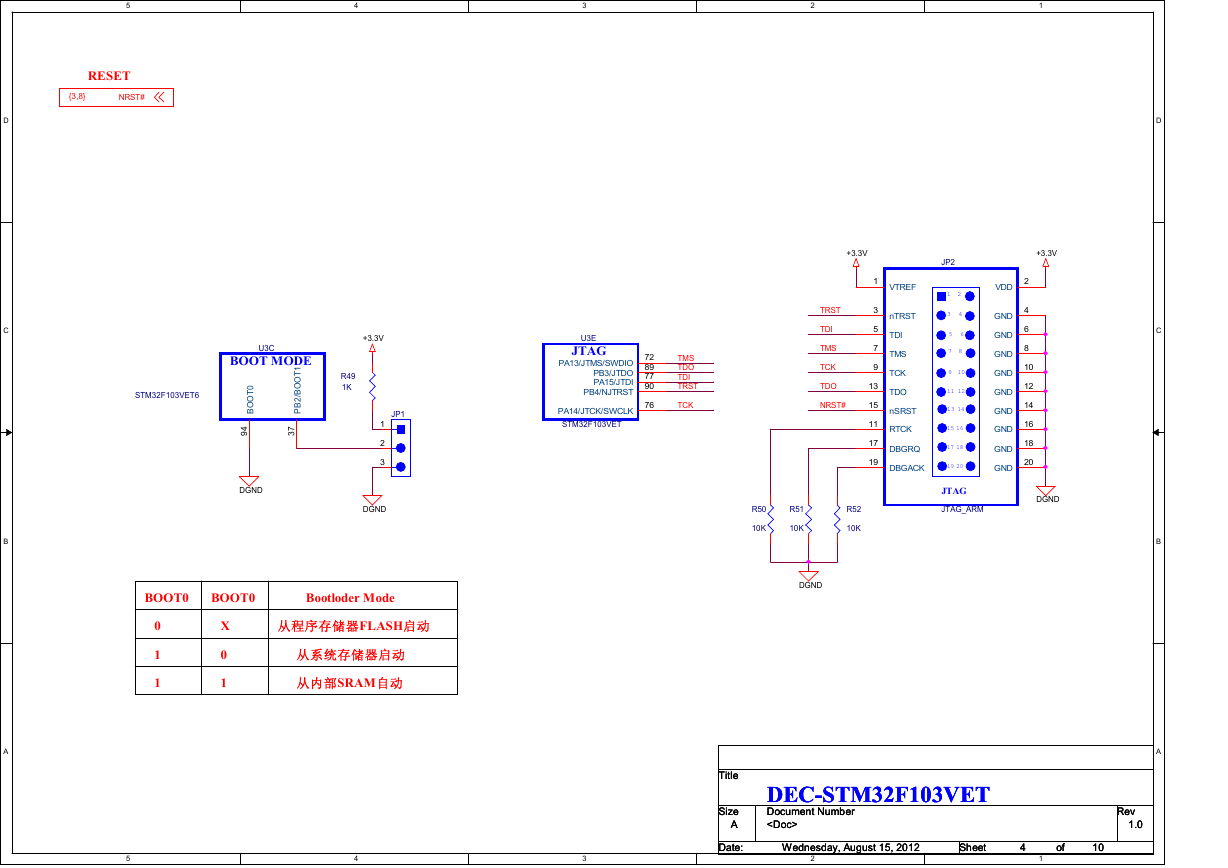

RESET

{3,8}

NRST#

U3C

BOOT MODE

STM32F103VET6

0

T

O

O

B

1

T

O

O

B

2

B

P

/

4

9

7

3

DGND

U3E

JTAG

PA13/JTMS/SWDIO

PB3/JTDO

PA15/JTDI

PB4/NJTRST

PA14/JTCK/SWCLK

STM32F103VET

+3.3V

R49

1K

JP1

1

2

3

DGND

BOOT0

BOOT0

Bootloder Mode

0

1

1

X

0

1

从程序存储器FLASH启动

从系统存储器启动

从内部SRAM自动

72

89

77

90

76

TMS

TDO

TDI

TRST

TCK

+3.3V

TRST

TDI

TMS

TCK

TDO

NRST#

1

3

5

7

9

13

15

11

17

19

VTREF

nTRST

TDI

TMS

TCK

TDO

nSRST

RTCK

DBGRQ

DBGACK

JP2

1 2

3

5

4

6

7 8

9 10

11 12

13

14

15

16

17

18

19

20

+3.3V

2

4

6

8

10

12

14

16

18

20

VDD

GND

GND

GND

GND

GND

GND

GND

GND

GND

JTAG

JTAG_ARM

DGND

R50

10K

R51

10K

R52

10K

DGND

D

C

B

A

5

4

3

Title

Title

Title

Size

Size

Size

A

A

A

Date:

Date:

Date:

DEC-STM32F103VET

DEC-STM32F103VET

DEC-STM32F103VET

Document Number

Document Number

Document Number

Rev

Rev

Rev

1.0

1.0

1.0

Wednesday, August 15, 2012

Wednesday, August 15, 2012

Wednesday, August 15, 2012

2

Sheet

Sheet

Sheet

4

4

4

1

of

of

of

10

10

10

�

5

4

3

2

1

{8}

{9}

{8}

{8}

{8}

{8}

{8}

{8}

{8}

{8}

{8}

{8}

{8}

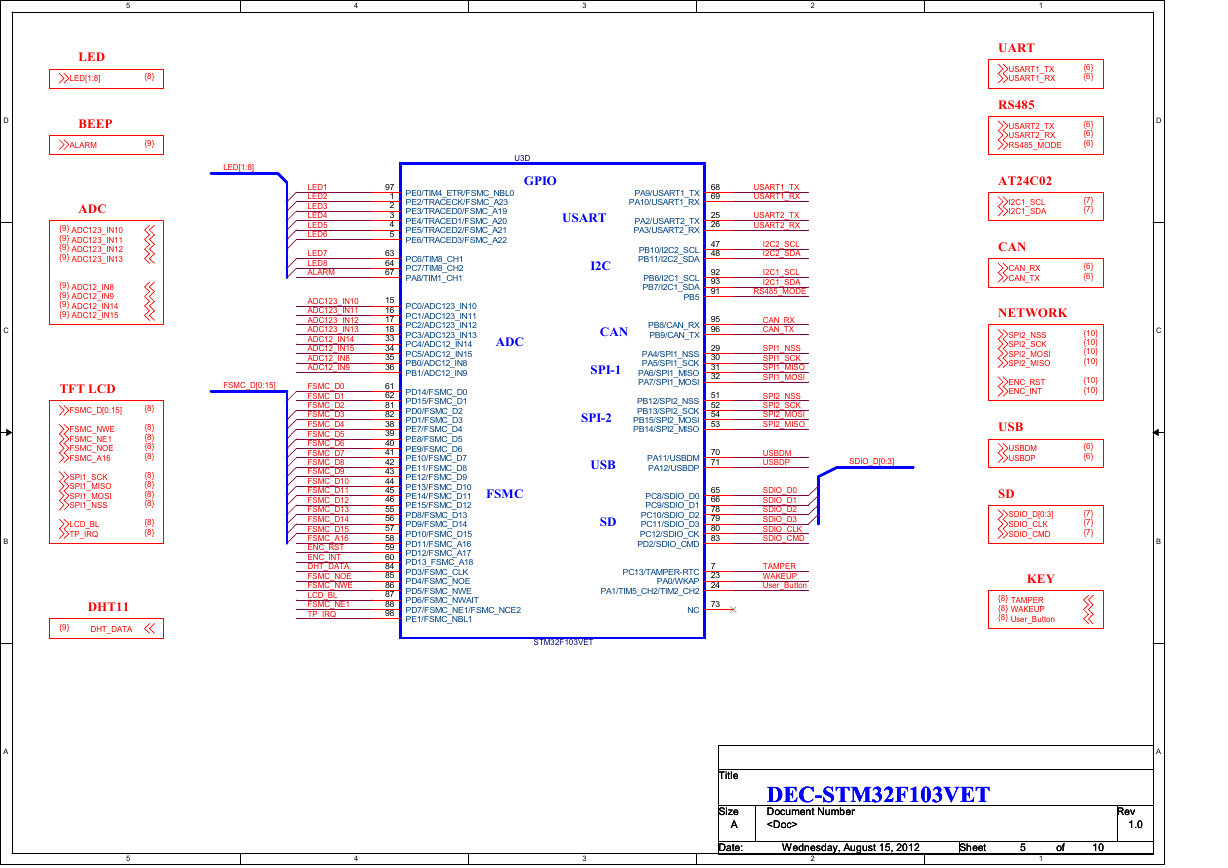

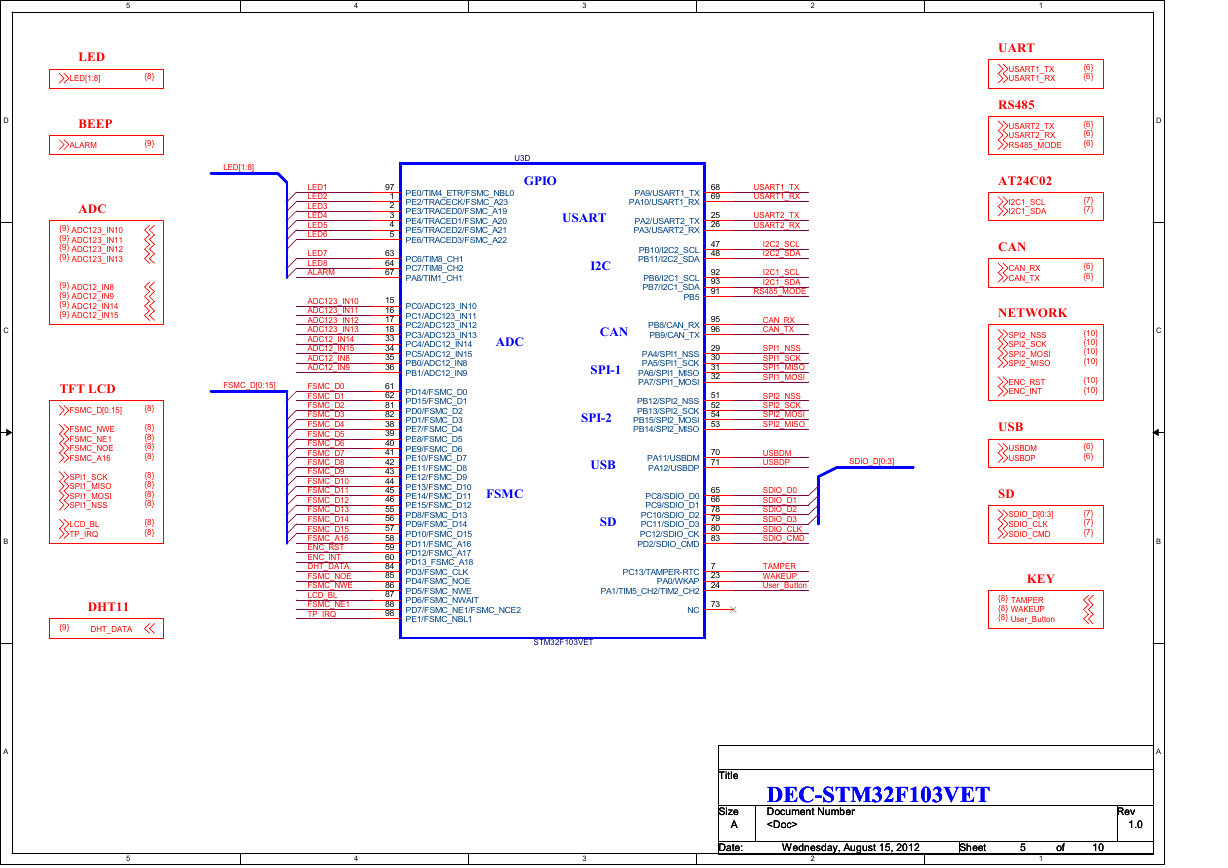

LED

LED[1:8]

BEEP

ALARM

ADC

ADC123_IN10

ADC123_IN11

ADC123_IN12

ADC123_IN13

ADC12_IN8

ADC12_IN9

ADC12_IN14

ADC12_IN15

{9}

{9}

{9}

{9}

{9}

{9}

{9}

{9}

TFT LCD

FSMC_D[0:15]

FSMC_NWE

FSMC_NE1

FSMC_NOE

FSMC_A16

SPI1_SCK

SPI1_MISO

SPI1_MOSI

SPI1_NSS

LCD_BL

TP_IRQ

DHT11

DHT_DATA

{9}

D

C

B

A

LED[1:8]

FSMC_D[0:15]

LED1

LED2

LED3

LED4

LED5

LED6

LED7

LED8

ALARM

ADC123_IN10

ADC123_IN11

ADC123_IN12

ADC123_IN13

ADC12_IN14

ADC12_IN15

ADC12_IN8

ADC12_IN9

FSMC_D0

FSMC_D1

FSMC_D2

FSMC_D3

FSMC_D4

FSMC_D5

FSMC_D6

FSMC_D7

FSMC_D8

FSMC_D9

FSMC_D10

FSMC_D11

FSMC_D12

FSMC_D13

FSMC_D14

FSMC_D15

FSMC_A16

ENC_RST

ENC_INT

DHT_DATA

FSMC_NOE

FSMC_NWE

LCD_BL

FSMC_NE1

TP_IRQ

97

1

2

3

4

5

63

64

67

15

16

17

18

33

34

35

36

61

62

81

82

38

39

40

41

42

43

44

45

46

55

56

57

58

59

60

84

85

86

87

88

98

U3D

GPIO

PE0/TIM4_ETR/FSMC_NBL0

PE2/TRACECK/FSMC_A23

PE3/TRACED0/FSMC_A19

PE4/TRACED1/FSMC_A20

PE5/TRACED2/FSMC_A21

PE6/TRACED3/FSMC_A22

PC6/TIM8_CH1

PC7/TIM8_CH2

PA8/TIM1_CH1

PC0/ADC123_IN10

PC1/ADC123_IN11

PC2/ADC123_IN12

PC3/ADC123_IN13

PC4/ADC12_IN14

PC5/ADC12_IN15

PB0/ADC12_IN8

PB1/ADC12_IN9

ADC

PD14/FSMC_D0

PD15/FSMC_D1

PD0/FSMC_D2

PD1/FSMC_D3

PE7/FSMC_D4

PE8/FSMC_D5

PE9/FSMC_D6

PE10/FSMC_D7

PE11/FSMC_D8

PE12/FSMC_D9

PE13/FSMC_D10

PE14/FSMC_D11

PE15/FSMC_D12

PD8/FSMC_D13

PD9/FSMC_D14

PD10/FSMC_D15

PD11/FSMC_A16

PD12/FSMC_A17

PD13_FSMC_A18

PD3/FSMC_CLK

PD4/FSMC_NOE

PD5/FSMC_NWE

PD6/FSMC_NWAIT

PD7/FSMC_NE1/FSMC_NCE2

PE1/FSMC_NBL1

FSMC

USART

I2C

PA9/USART1_TX

PA10/USART1_RX

PA2/USART2_TX

PA3/USART2_RX

PB10/I2C2_SCL

PB11/I2C2_SDA

PB6/I2C1_SCL

PB7/I2C1_SDA

PB5

CAN

PB8/CAN_RX

PB9/CAN_TX

SPI-1

SPI-2

PA4/SPI1_NSS

PA5/SPI1_SCK

PA6/SPI1_MISO

PA7/SPI1_MOSI

PB12/SPI2_NSS

PB13/SPI2_SCK

PB15/SPI2_MOSI

PB14/SPI2_MISO

USB

PA11/USBDM

PA12/USBDP

SD

PC8/SDIO_D0

PC9/SDIO_D1

PC10/SDIO_D2

PC11/SDIO_D3

PC12/SDIO_CK

PD2/SDIO_CMD

PC13/TAMPER-RTC

PA0/WKAP

PA1/TIM5_CH2/TIM2_CH2

NC

68

69

25

26

47

48

92

93

91

95

96

29

30

31

32

51

52

54

53

70

71

65

66

78

79

80

83

7

23

24

73

STM32F103VET

USART1_TX

USART1_RX

USART2_TX

USART2_RX

I2C2_SCL

I2C2_SDA

I2C1_SCL

I2C1_SDA

RS485_MODE

CAN_RX

CAN_TX

SPI1_NSS

SPI1_SCK

SPI1_MISO

SPI1_MOSI

SPI2_NSS

SPI2_SCK

SPI2_MOSI

SPI2_MISO

USBDM

USBDP

SDIO_D0

SDIO_D1

SDIO_D2

SDIO_D3

SDIO_CLK

SDIO_CMD

TAMPER

WAKEUP

User_Button

SDIO_D[0:3]

{6}

{6}

{6}

{6}

{6}

{7}

{7}

{6}

{6}

{10}

{10}

{10}

{10}

{10}

{10}

{6}

{6}

{7}

{7}

{7}

UART

USART1_TX

USART1_RX

RS485

USART2_TX

USART2_RX

RS485_MODE

AT24C02

I2C1_SCL

I2C1_SDA

CAN

CAN_RX

CAN_TX

NETWORK

SPI2_NSS

SPI2_SCK

SPI2_MOSI

SPI2_MISO

ENC_RST

ENC_INT

USB

USBDM

USBDP

SD

SDIO_D[0:3]

SDIO_CLK

SDIO_CMD

KEY

{8}

{8}

{8}

TAMPER

WAKEUP

User_Button

D

C

B

A

5

4

3

Title

Title

Title

Size

Size

Size

A

A

A

Date:

Date:

Date:

DEC-STM32F103VET

DEC-STM32F103VET

DEC-STM32F103VET

Document Number

Document Number

Document Number

Rev

Rev

Rev

1.0

1.0

1.0

Wednesday, August 15, 2012

Wednesday, August 15, 2012

Wednesday, August 15, 2012

2

Sheet

Sheet

Sheet

5

5

5

1

of

of

of

10

10

10

�

D

C

B

A

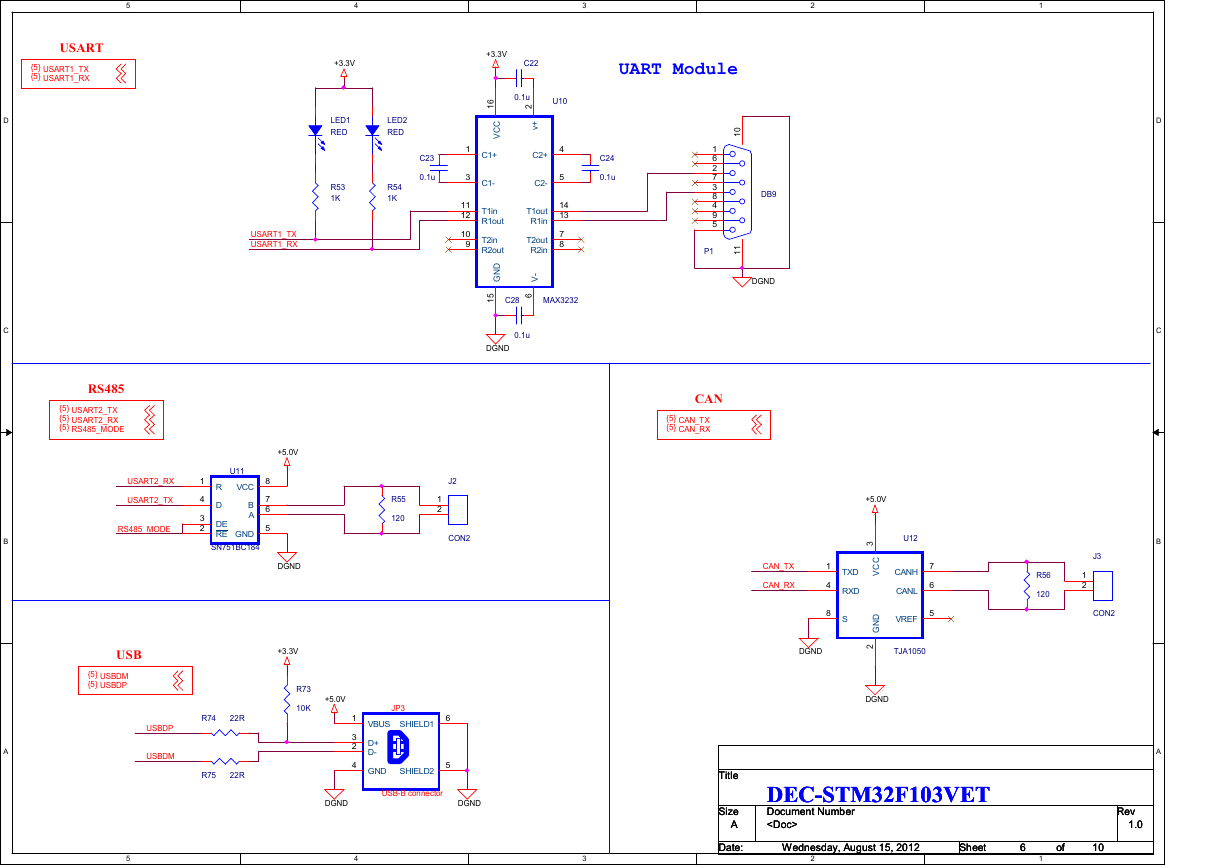

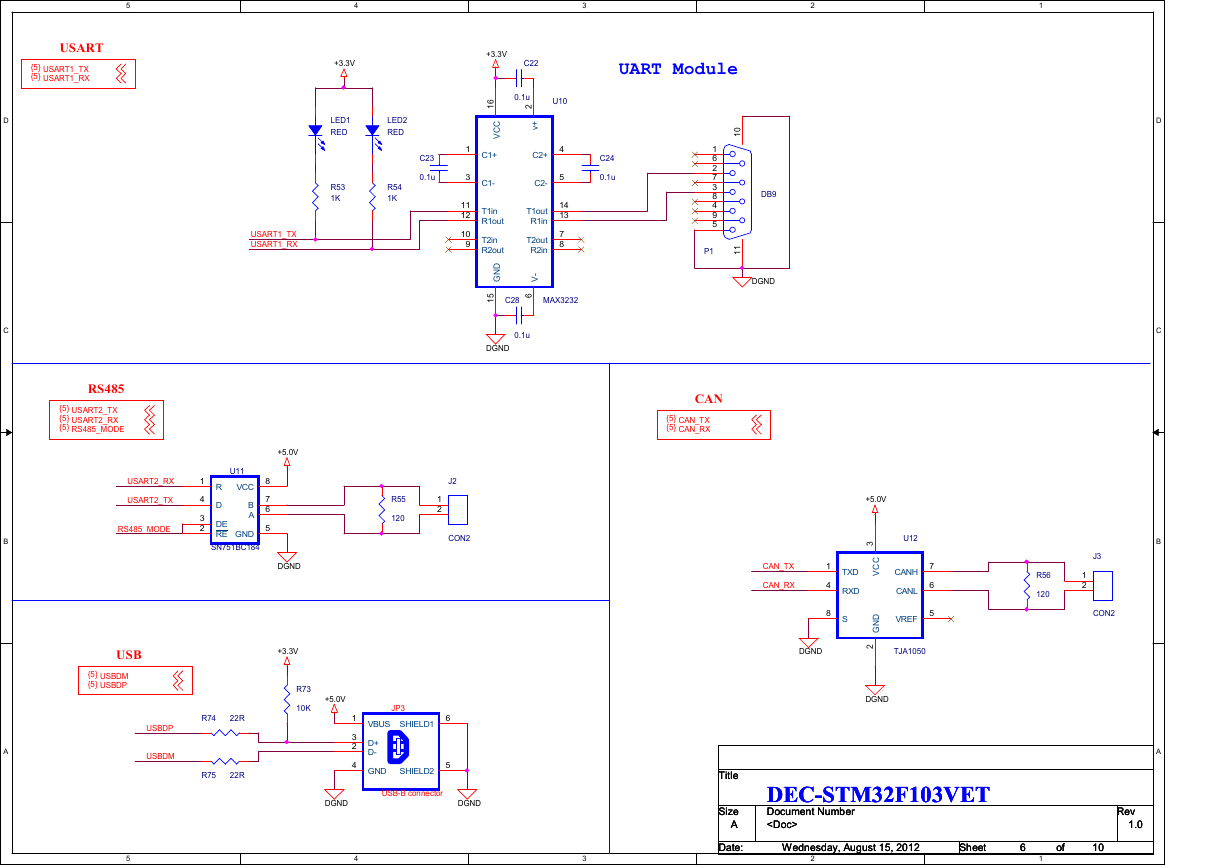

RS485

USART2_TX

USART2_RX

RS485_MODE

{5}

{5}

{5}

USART2_RX

USART2_TX

1

4

R

D

RS485_MODE

3

2 DE

RE

SN751BC184

GND

R55

120

J2

1

2

CON2

USART1_TX

USART1_RX

+5.0V

U11

VCC

8

7

6B

A

5

DGND

+3.3V

5

USART

{5}

{5}

USART1_TX

USART1_RX

4

+3.3V

LED1

RED

LED2

RED

C23

0.1u

R53

1K

R54

1K

3

2

1

C24

0.1u

1

3

11

12

10

9

+3.3V

C22

6

1

C

C

V

C1+

C1-

T1in

R1out

T2in

R2out

D

N

G

0.1u

2

U10

4

5

14

13

7

8

+

v

C2+

C2-

T1out

R1in

T2out

R2in

-

V

5

1

6

C28

MAX3232

0.1u

DGND

UART Module

0

1

1

6

2

7

3

8

4

9

5

P1

1

1

DB9

DGND

CAN

{5}

{5}

CAN_TX

CAN_RX

USB

{5}

{5}

USBDM

USBDP

5

USBDP

USBDM

R74

22R

R75

22R

R73

10K

+5.0V

1

JP3

VBUS

SHIELD1

3

2 D+

D-

GND

SHIELD2

USB-B connector

DGND

4

4

6

5

DGND

CAN_TX

CAN_RX

+5.0V

1

4

8

TXD

RXD

S

3

C

C

V

D

N

G

U12

CANH

CANL

VREF

7

6

5

DGND

2

TJA1050

DGND

R56

120

J3

1

2

CON2

Title

Title

Title

Size

Size

Size

A

A

A

Date:

Date:

Date:

DEC-STM32F103VET

DEC-STM32F103VET

DEC-STM32F103VET

Document Number

Document Number

Document Number

Rev

Rev

Rev

1.0

1.0

1.0

Wednesday, August 15, 2012

Wednesday, August 15, 2012

Wednesday, August 15, 2012

2

Sheet

Sheet

Sheet

6

6

6

1

of

of

of

10

10

10

3

D

C

B

A

�

5

4

3

2

1

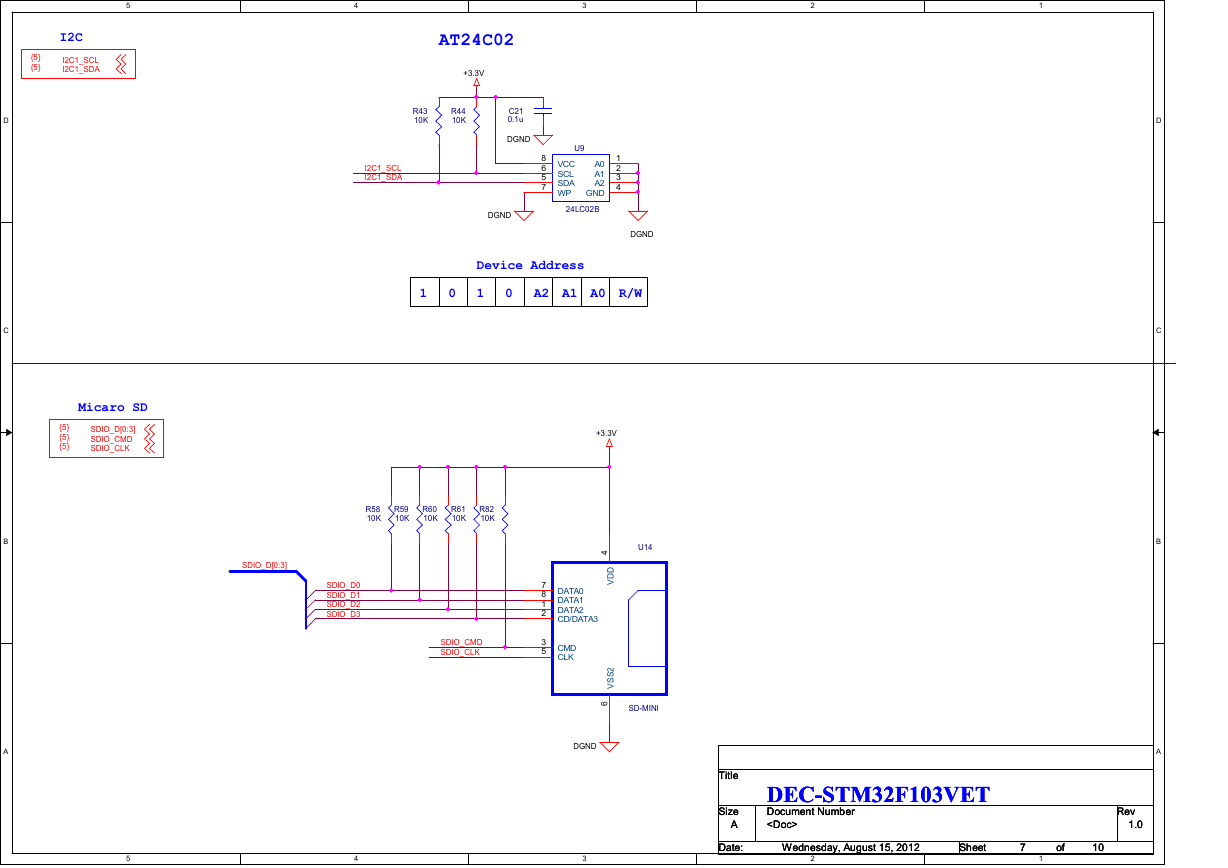

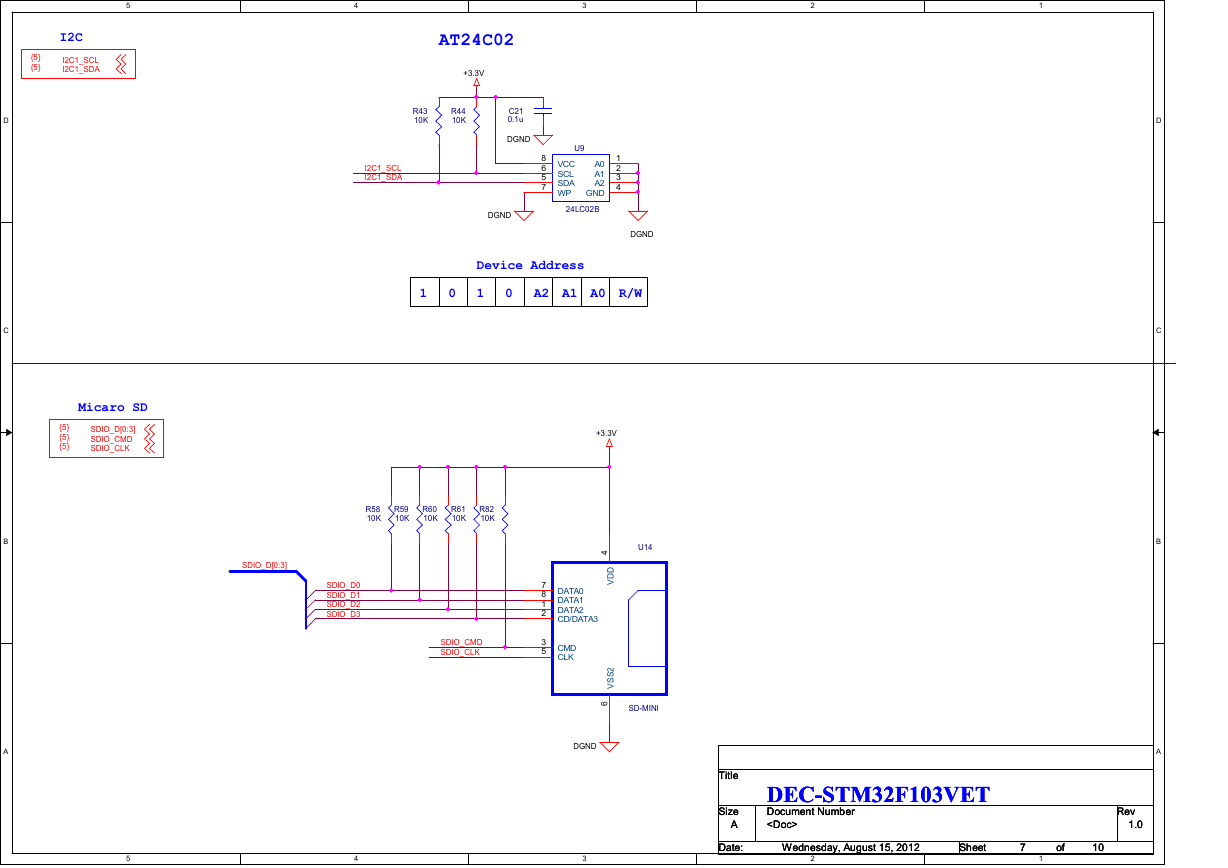

I2C

{5}

{5}

I2C1_SCL

I2C1_SDA

Micaro SD

{5}

{5}

{5}

SDIO_D[0:3]

SDIO_CMD

SDIO_CLK

D

C

B

A

AT24C02

+3.3V

R43

10K

R44

10K

C21

0.1u

DGND

I2C1_SCL

I2C1_SDA

DGND

U9

8

VCC

6

5 SCL

SDA

7

WP

1

2

3

4

A0

A1

A2

GND

24LC02B

DGND

Device Address

1

0

A2 A1 A0 R/W

1

0

R58

10K

R59

10K

R60

10K

R61

10K

R82

10K

SDIO_D[0:3]

SDIO_D0

SDIO_D1

SDIO_D2

SDIO_D3

SDIO_CMD

SDIO_CLK

+3.3V

4

U14

7

8

1

2

3

5

DATA0

DATA1

DATA2

CD/DATA3

CMD

CLK

D

D

V

2

S

S

V

6

SD-MINI

DGND

D

C

B

A

5

4

3

Title

Title

Title

Size

Size

Size

A

A

A

Date:

Date:

Date:

DEC-STM32F103VET

DEC-STM32F103VET

DEC-STM32F103VET

Document Number

Document Number

Document Number

Rev

Rev

Rev

1.0

1.0

1.0

Wednesday, August 15, 2012

Wednesday, August 15, 2012

Wednesday, August 15, 2012

2

Sheet

Sheet

Sheet

7

7

7

1

of

of

of

10

10

10

�

4

+3.3V

LED1

LED2

LED3

LED4

LED5

LED5

LED7

LED8

LED3

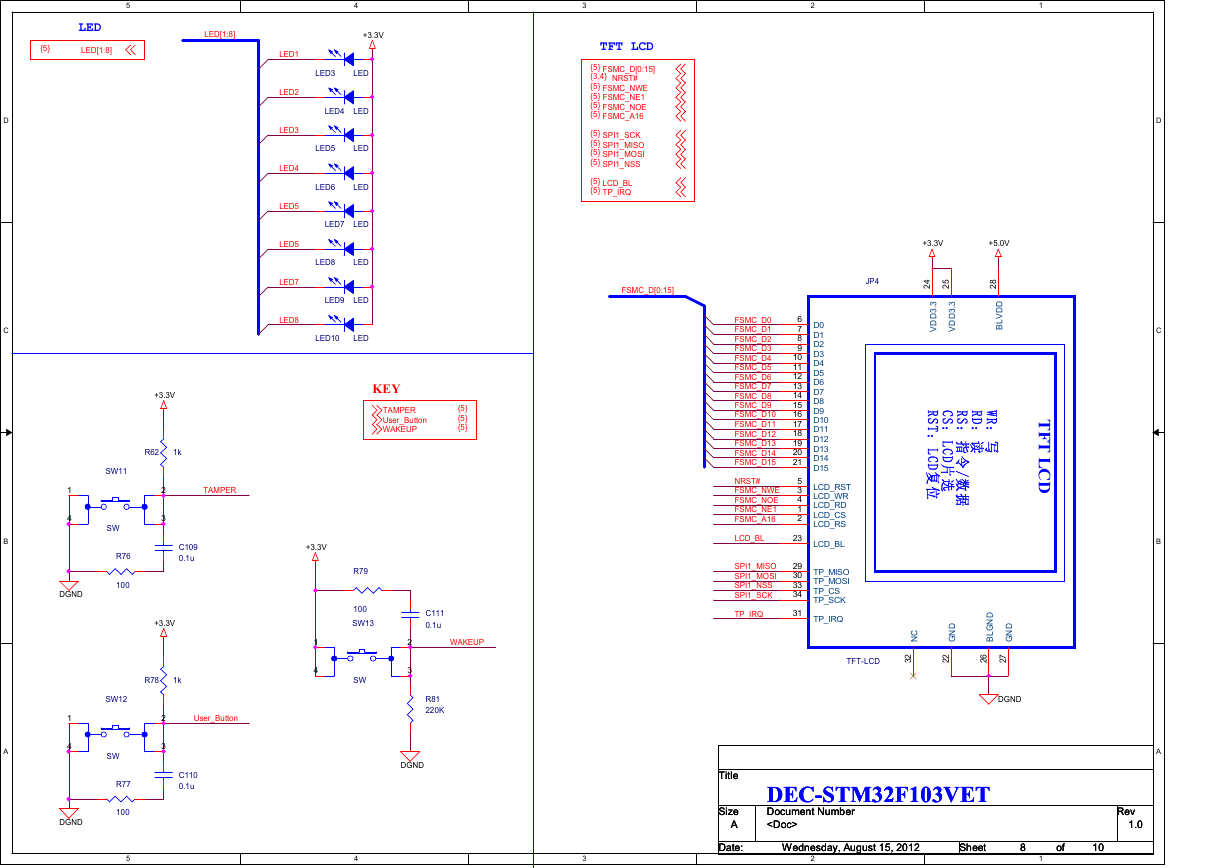

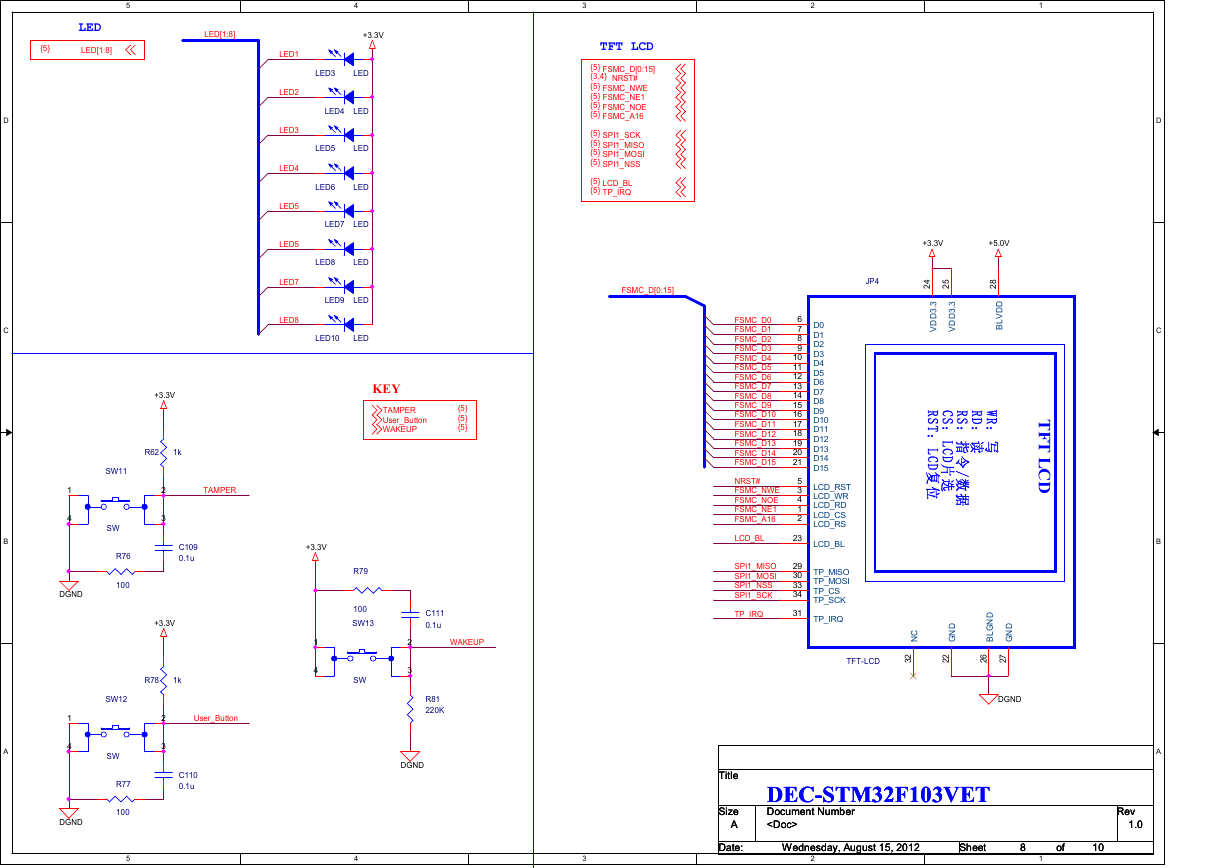

LED

LED4

LED

LED5

LED

LED6

LED

LED7

LED

LED8

LED

LED9

LED

LED10

LED

KEY

TAMPER

User_Button

WAKEUP

{5}

{5}

{5}

+3.3V

1

4

R79

100

SW13

SW

WAKEUP

2

3

C111

0.1u

R81

220K

DGND

D

C

B

A

5

LED

{5}

LED[1:8]

LED[1:8]

+3.3V

R62

1k

2

3

C109

0.1u

TAMPER

+3.3V

R78

1k

2

3

User_Button

C110

0.1u

1

4

DGND

1

4

DGND

SW11

SW

R76

100

SW12

SW

R77

100

5

4

3

3

2

1

TFT LCD

FSMC_D[0:15]

{5}

{3,4}

{5}

{5}

{5}

{5}

NRST#

FSMC_NWE

FSMC_NE1

FSMC_NOE

FSMC_A16

{5}

{5}

{5}

{5}

{5}

{5}

SPI1_SCK

SPI1_MISO

SPI1_MOSI

SPI1_NSS

LCD_BL

TP_IRQ

FSMC_D[0:15]

D

C

B

A

+3.3V

+5.0V

JP4

4

2

5

2

8

2

3

.

3

D

D

V

3

.

3

D

D

V

D

D

V

L

B

R

S

T

:

L

C

D

复

位

C

S

R

S

R

D

W

R

:

读

:

写

:

L

C

D

片

选

:

指

令

/

数

据

T

F

T

L

C

D

C

N

D

N

G

D

N

G

L

B

D

N

G

FSMC_D0

FSMC_D1

FSMC_D2

FSMC_D3

FSMC_D4

FSMC_D5

FSMC_D6

FSMC_D7

FSMC_D8

FSMC_D9

FSMC_D10

FSMC_D11

FSMC_D12

FSMC_D13

FSMC_D14

FSMC_D15

NRST#

FSMC_NWE

FSMC_NOE

FSMC_NE1

FSMC_A16

LCD_BL

SPI1_MISO

SPI1_MOSI

SPI1_NSS

SPI1_SCK

TP_IRQ

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

5

3

4

1

2

23

29

30

33

34

31

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

LCD_RST

LCD_WR

LCD_RD

LCD_CS

LCD_RS

LCD_BL

TP_MISO

TP_MOSI

TP_CS

TP_SCK

TP_IRQ

TFT-LCD

2

3

2

2

6

2

7

2

DGND

Title

Title

Title

Size

Size

Size

A

A

A

Date:

Date:

Date:

DEC-STM32F103VET

DEC-STM32F103VET

DEC-STM32F103VET

Document Number

Document Number

Document Number

Rev

Rev

Rev

1.0

1.0

1.0

Wednesday, August 15, 2012

Wednesday, August 15, 2012

Wednesday, August 15, 2012

2

Sheet

Sheet

Sheet

8

8

8

1

of

of

of

10

10

10

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc