单片机课程设计报告

题目:

设计者 1:

负责任务:

专业班级/学号:

设计者 2:

负责任务:

专业班级/学号:

指导教师 1:

指导教师 2:

答辩时间:

�

目录

一、设计题目、设计目的 ································································································································2

1.1、说明选题的来源、意义和目的 ································································· 2

1.2、课题承担人员及分工说明 ·········································································2

二、课题总体设计说明 ······································································································································2

2.1、说明总体开发计划和课题所达到的功能目标和技术指标 ························ 2

2.2、课题总体设计方案,比较几个备选方案,确定最终方案 ························ 3

三、硬件设计说明 ·················································································································································4

3.1、硬件总体设计方案 ···················································································· 4

3.2、硬件设计的总电路原理图、PCB 图及原件清单 ········································ 7

四、软件设计说明 ·················································································································································9

4.1、软件总体设计方案 ···················································································· 9

4.2、软件功能模块划分 ···················································································· 9

五、硬件调试说明 ·············································································································································· 12

5.1、硬件性能测试 ·························································································· 12

5.2、实验测得的数据 ······················································································ 12

5.3、软件性能测试 ·························································································· 13

六、附件 ·····································································································································································13

附件 1、波形回放信号图 ··················································································13

附件 2、硬件外观图 ························································································· 15

附件 3、PROTUES 仿真效果图 ·······································································17

1

�

一、设计题目、设计目的

1.1、说明选题的来源、意义和目的

选题来源:本次课题设计根据 2011 全国大学生电子大赛—H 题波形采集、存储

与回放系统基本要求设计的,

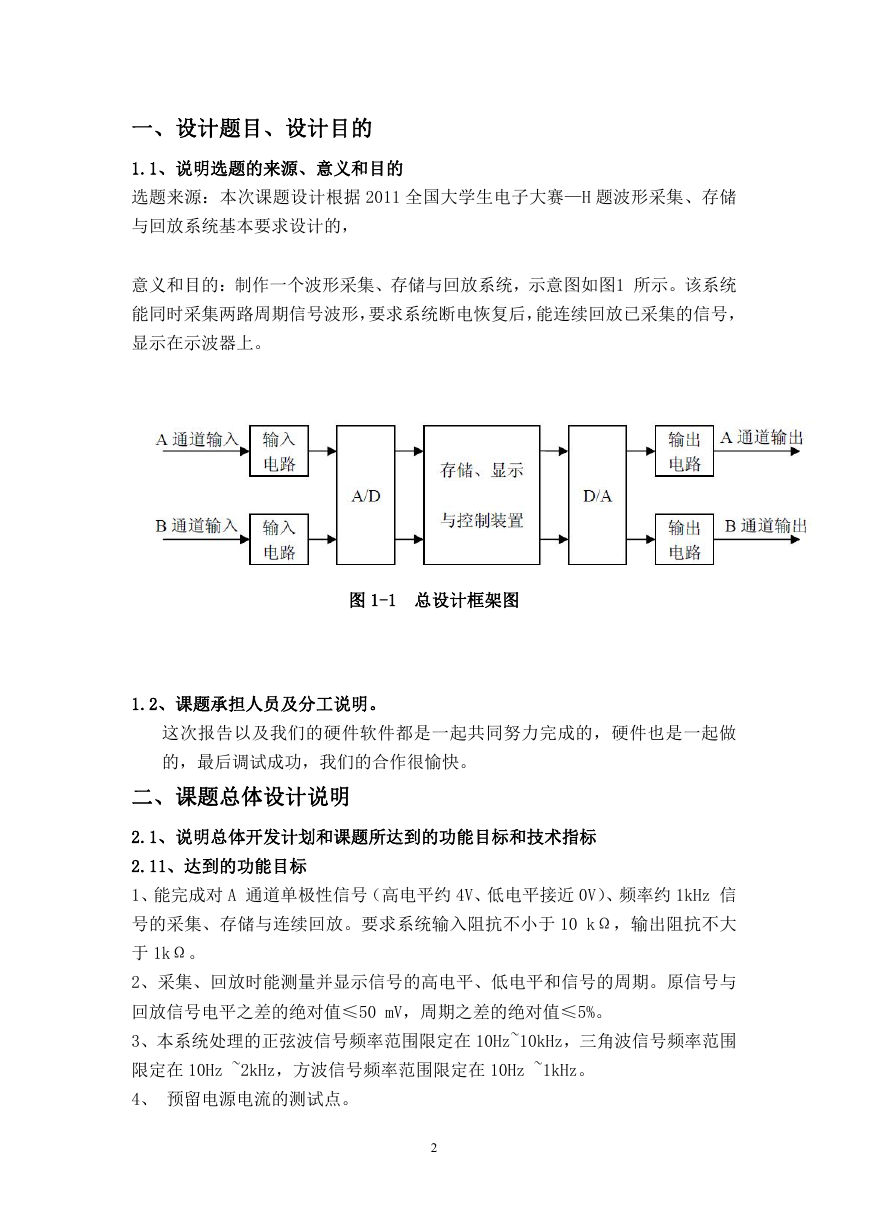

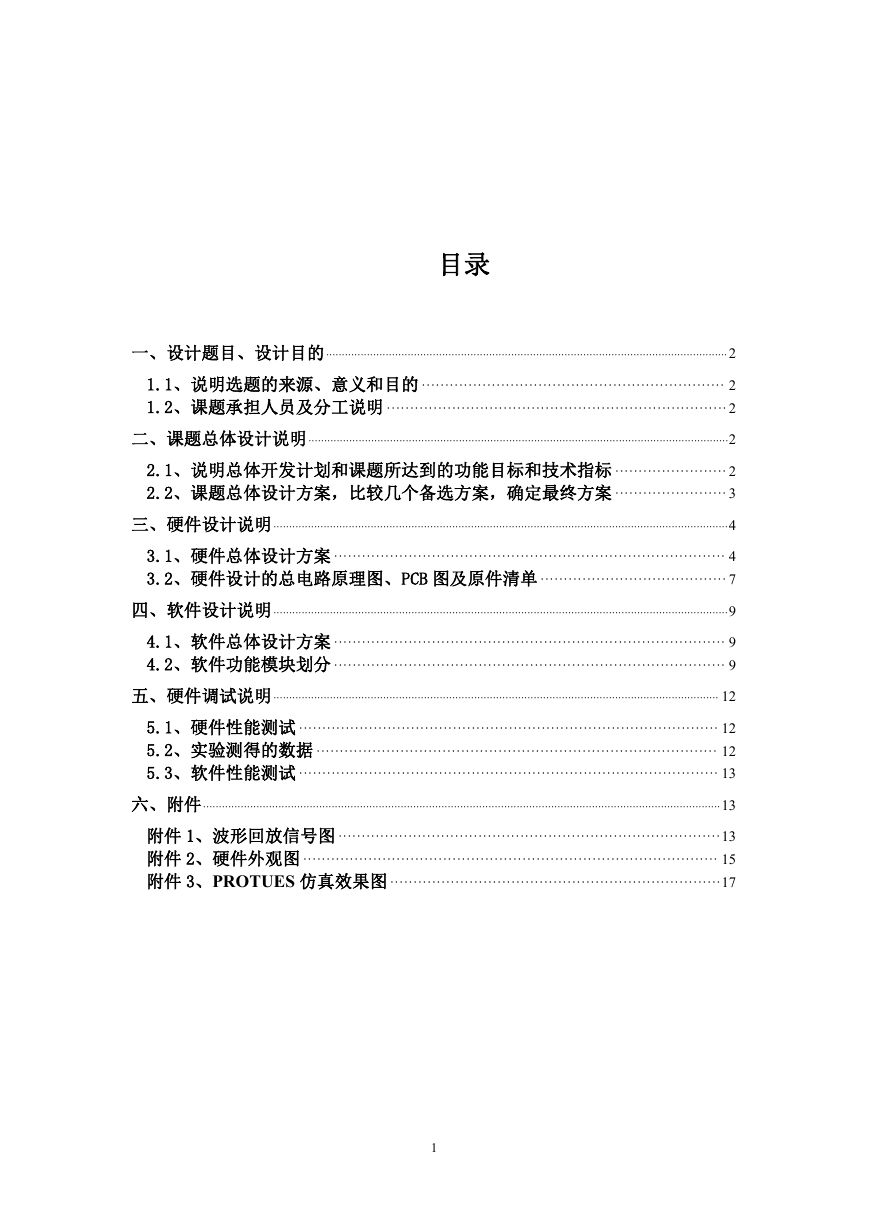

意义和目的:制作一个波形采集、存储与回放系统,示意图如图1 所示。该系统

能同时采集两路周期信号波形,要求系统断电恢复后,能连续回放已采集的信号,

显示在示波器上。

图 1-1 总设计框架图

1.2、课题承担人员及分工说明。

这次报告以及我们的硬件软件都是一起共同努力完成的,硬件也是一起做

的,最后调试成功,我们的合作很愉快。

二、课题总体设计说明

2.1、说明总体开发计划和课题所达到的功能目标和技术指标

2.11、达到的功能目标

1、能完成对 A 通道单极性信号(高电平约 4V、低电平接近 0V)、频率约 1kHz 信

号的采集、存储与连续回放。要求系统输入阻抗不小于 10 kΩ,输出阻抗不大

于 1kΩ。

2、采集、回放时能测量并显示信号的高电平、低电平和信号的周期。原信号与

回放信号电平之差的绝对值≤50 mV,周期之差的绝对值≤5%。

3、本系统处理的正弦波信号频率范围限定在 10Hz~10kHz,三角波信号频率范围

限定在 10Hz ~2kHz,方波信号频率范围限定在 10Hz ~1kHz。

4、 预留电源电流的测试点。

2

�

5、 采集与回放时采用示波器监视。

6、 采集、回放时显示的周期和幅度应是信号的实际测量值,规定采用十进制数

字显示,周期以“ms”为单位,幅度以“V”为单位。

2.12、技术指标

1、A/D 位数选择依据

通用示波器垂直方向共 8 格,要求每格 32 级,共有 32 8=256 级。

n

log 2

256

8

因此采用 8 位 A/D 以上的即可。

2、采用频率选择依据

假设扫描速度为 t s/div,每格点数为 n,采样频率为 sf ,则:

f s

n

t

,当 n=20

时,针对不同的扫描速度,可得到不同的采样频率。在一定的情况下,扫描速度

的改变是通过改变采样频率实现的。对于 10KHz 的正弦波,采样频率为 1MHz 时,

每周期可采样 100 个点,由采样值可以很好地恢复采样前的信号。因而,选用采

样频率为 1MHz 以上的 A/D 即可满足单路输入时对频率范围的要求。若考虑到双

路输入的情况,所需 A/D 最高采样频率应为 2MHz。因而,应选择采样频率为 2MHz

以下的 A/D。

3、波形回放频率选择依据

显示屏上显示的信号是从存储器中读出的信号,只要使观察到的波形不闪烁即

可。本设计中,单通道时刷新频率为 200Hz;双踪示波时,每通道刷新频率为

100HZ。通过计算,每秒读出的点数为 200*200=40K。即 RAM 读出频率为 40KHz,

要求 D/A 转换速率高于 40KHz。

2.2、课题总体设计方案,比较几个备选方案,确定最终方案

题目要求及相关指标分析 题目的要求是制作一个波形采集、 存储与回放系

统。 由于被测信号为模拟信号, 存储过程为数字量,故应该通过 A/D 转化将

模拟信号进行量化处理,然后送到单片机中存储,当需要显示的时候,从单片机

读出数据并通过 D/A 转化为模拟信号,然后送往示波器观察信号的波形。因此,

设计的重点是模拟信号的处理与采样、数字信号的存储、数字信号转化为模拟信

号送出及系统的控制 4 个方面。

有以下几种设计方案:

方案一:

方案一采用 PCF8591 作为信号输入输出转换主控芯片,根据 PCF 的特点,信

号输入采用四个模拟量输入,一个模拟量输出,因为没有设计输入电路对输入信

号进行相应的降压,所以输入限制在 0~5V 之间,频率为几百赫兹左右,所以输

3

�

出也没有必要做输出电路,经过芯片内部 DA 处理输出即可。电路信号储存依然

采用 AT24c02 进行储存,LCD1602 显示。

方案二:

使用具有高速 A/D 转换 STC12C5A60S2 芯片、外部存储芯片和液晶显示 1602,

方案三:

升级成高极端单片机芯片 STM32103RC(低功耗),内置 A/D,D/A 转换,LCD1602

显示。

方案二和方案三编程等实际操作要求高,芯片也没接触高,方案一的芯片

STC89C51RC 比较熟悉,操作也比较方便,电路设计简单易懂,程序编写方便,

且元器件少,,故选择第一个方案。

三、硬件设计说明

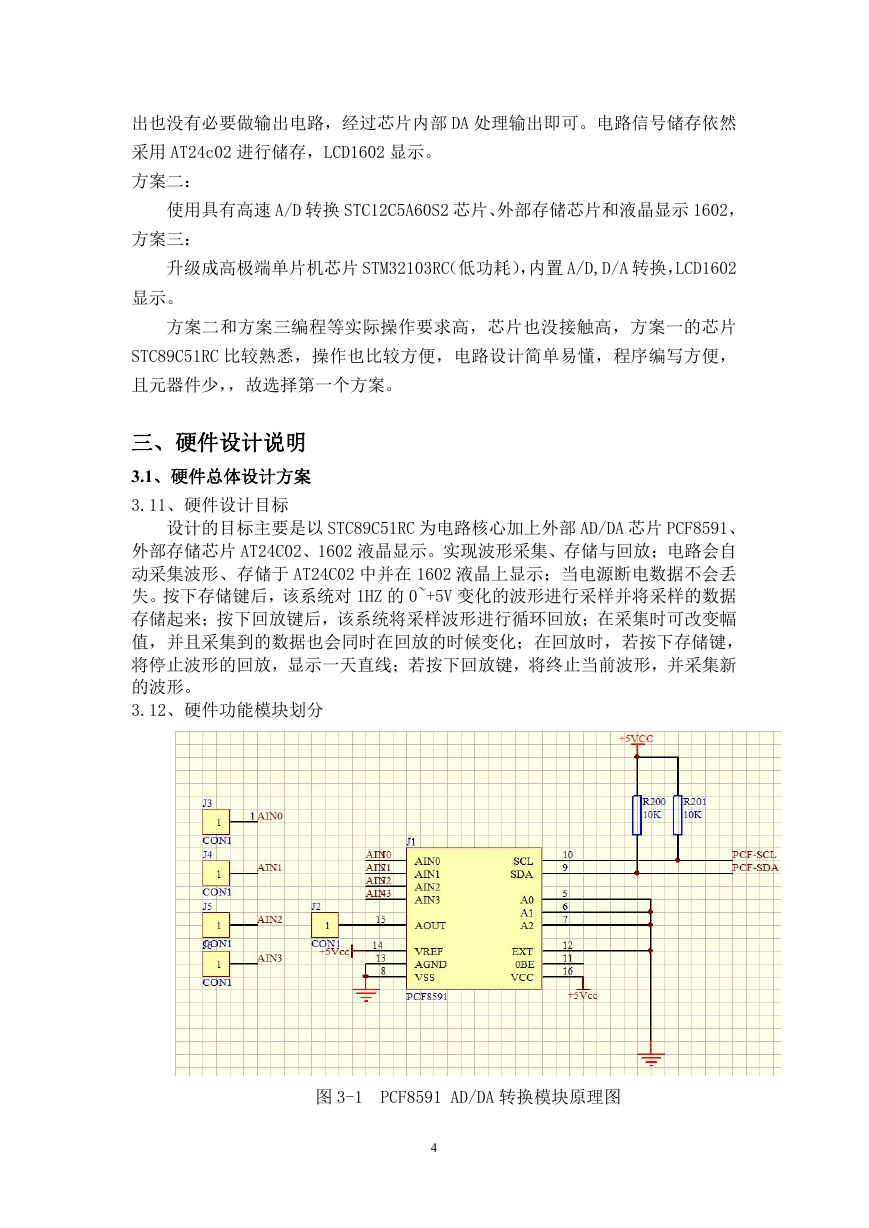

3.1、硬件总体设计方案

3.11、硬件设计目标

设计的目标主要是以 STC89C51RC 为电路核心加上外部 AD/DA 芯片 PCF8591、

外部存储芯片 AT24C02、1602 液晶显示。实现波形采集、存储与回放;电路会自

动采集波形、存储于 AT24C02 中并在 1602 液晶上显示;当电源断电数据不会丢

失。按下存储键后,该系统对 1HZ 的 0~+5V 变化的波形进行采样并将采样的数据

存储起来;按下回放键后,该系统将采样波形进行循环回放;在采集时可改变幅

值,并且采集到的数据也会同时在回放的时候变化;在回放时,若按下存储键,

将停止波形的回放,显示一天直线;若按下回放键,将终止当前波形,并采集新

的波形。

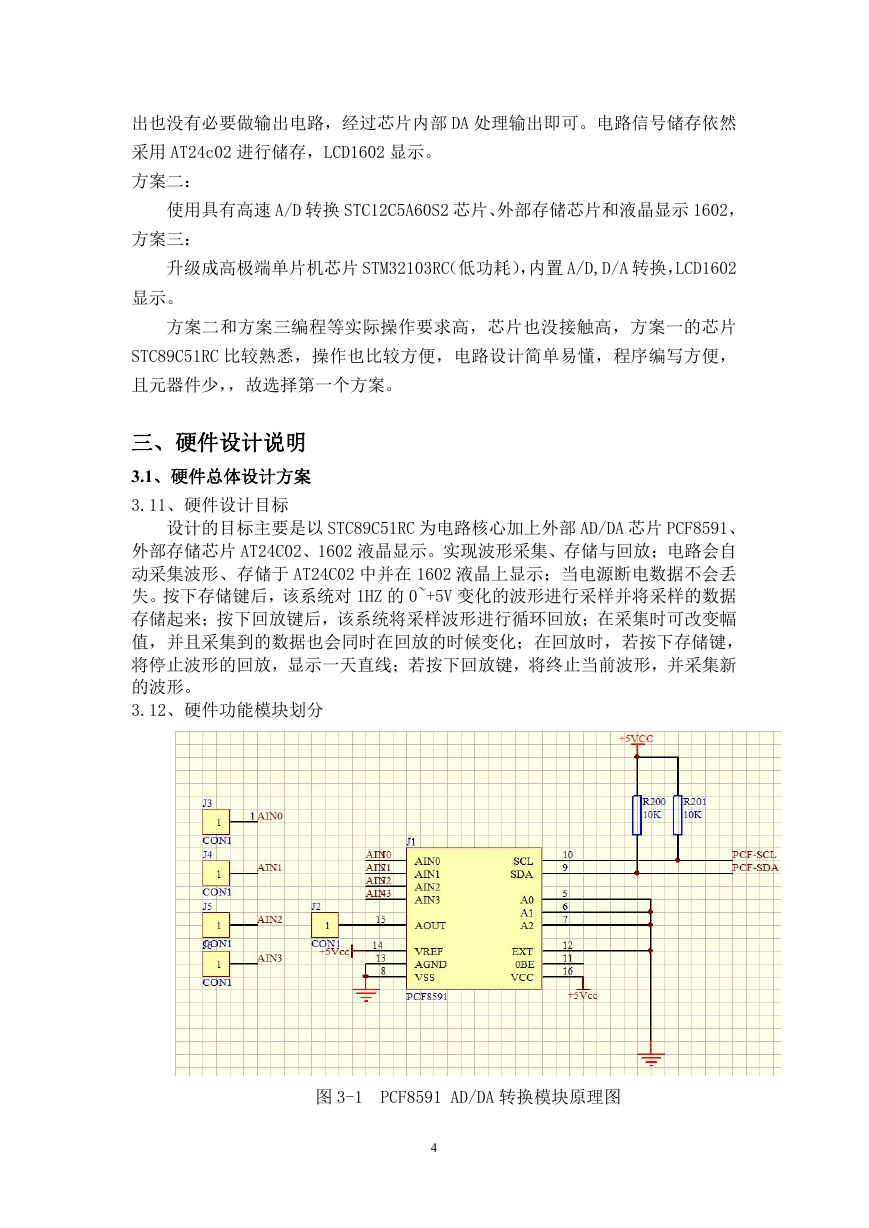

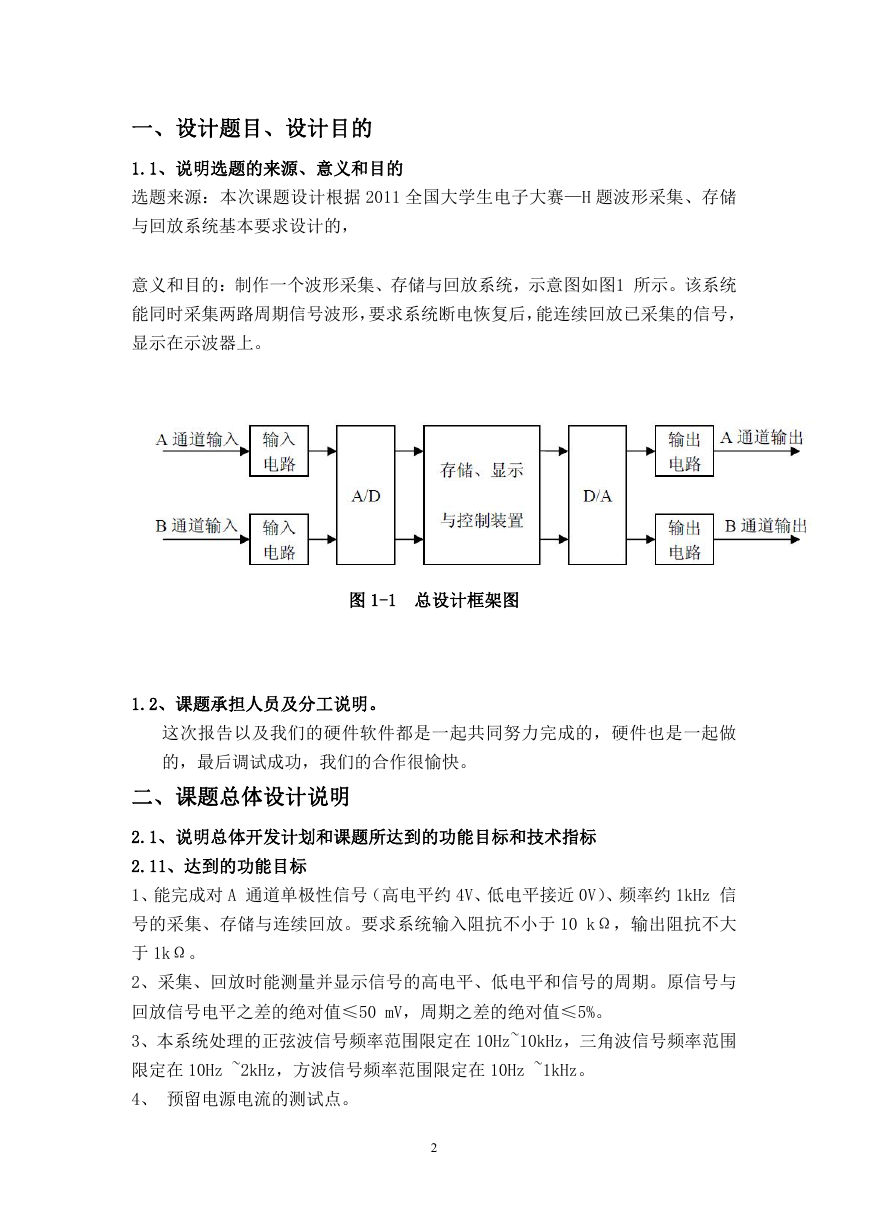

3.12、硬件功能模块划分

图 3-1

PCF8591 AD/DA 转换模块原理图

4

�

图 3-1 PCF8591 是具有 I2C 总线接口的 A/D 转换芯片。和 CPU 的信息传输过

程中仅靠时钟线 SCL 和数据线 SDA 就可以实现 8 位 A/D 及 D/A 转换器,有 4 路

A/D 转换输入,1 路 D/A 模拟输出。AIN0~AIN3:模拟信号输入端。本次实验的

输入信号接到 AIN0。A0~A3:引脚地址端。VDD、VSS 是电源端,SDA、SCL 是 I2C

总线的数据线、时钟线;OSC 为外部时钟输入端,内部时钟输出端;EXT:内部、

外部时钟选择线,使用内部时钟时 EXT 接地 AGND:模拟信号地; AOUT 为 D/A

转换输出端; VREF:基准电源端。

AOUT 为 D/A 转换输出端,AIN0~AIN3 为 A/D 的模拟信号输入端,输入

输出的地址、控制和数据信号都是通过双线双向 I2C 总线以串行的方式进行传

输。

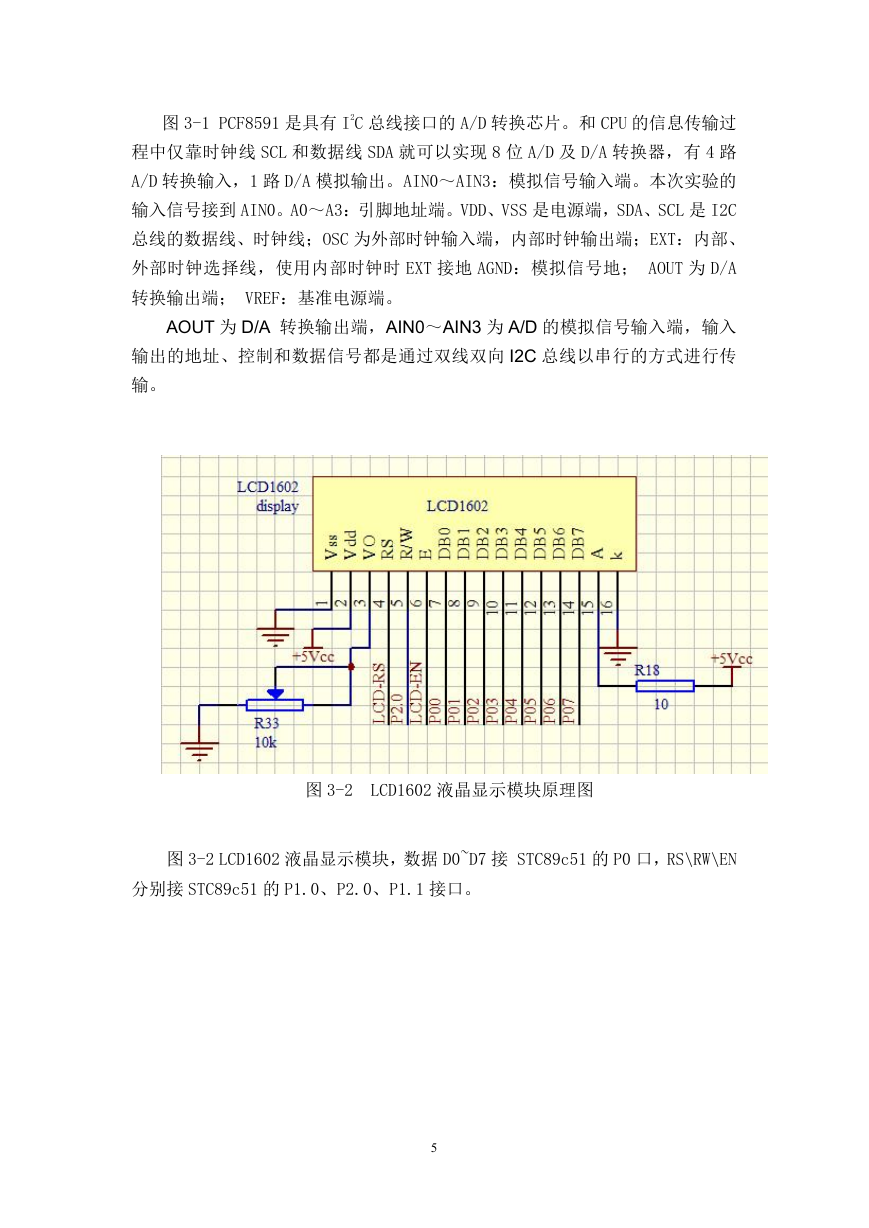

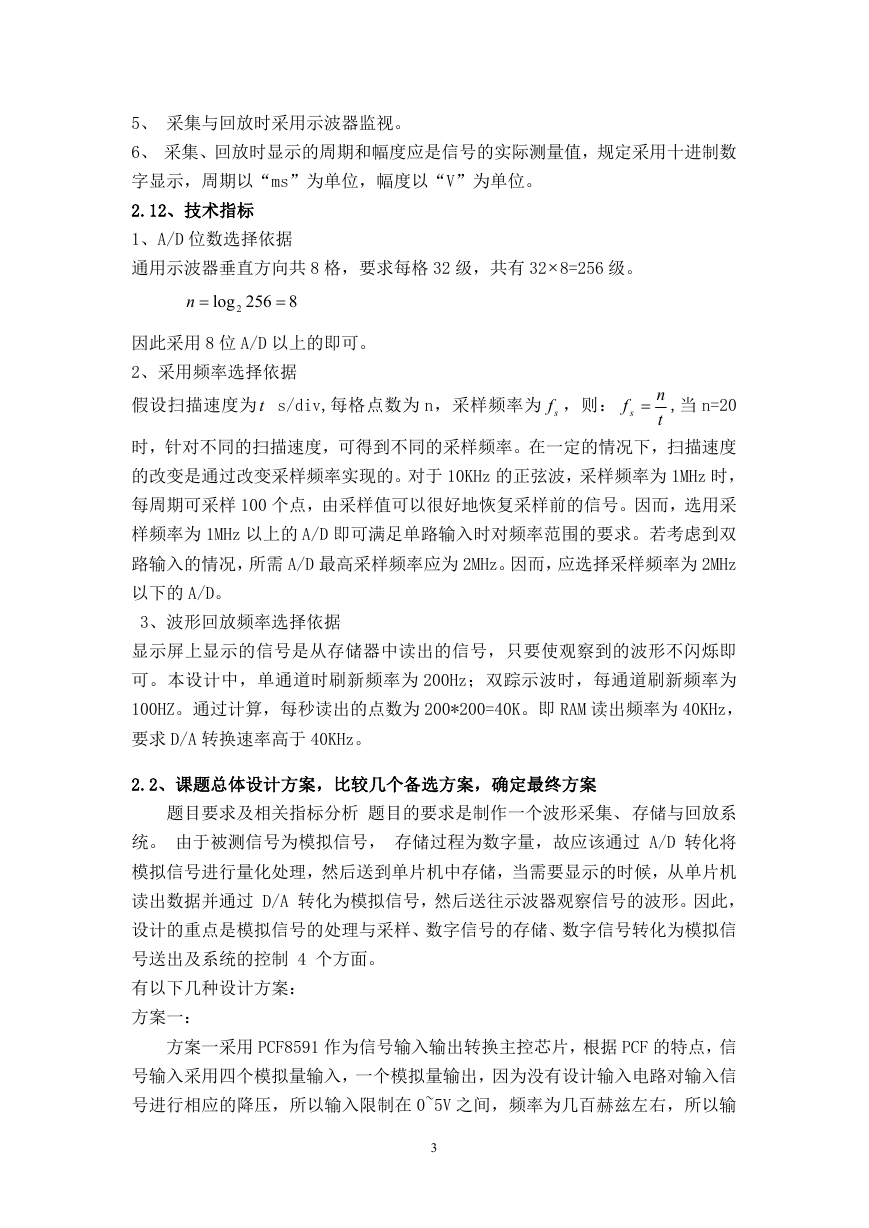

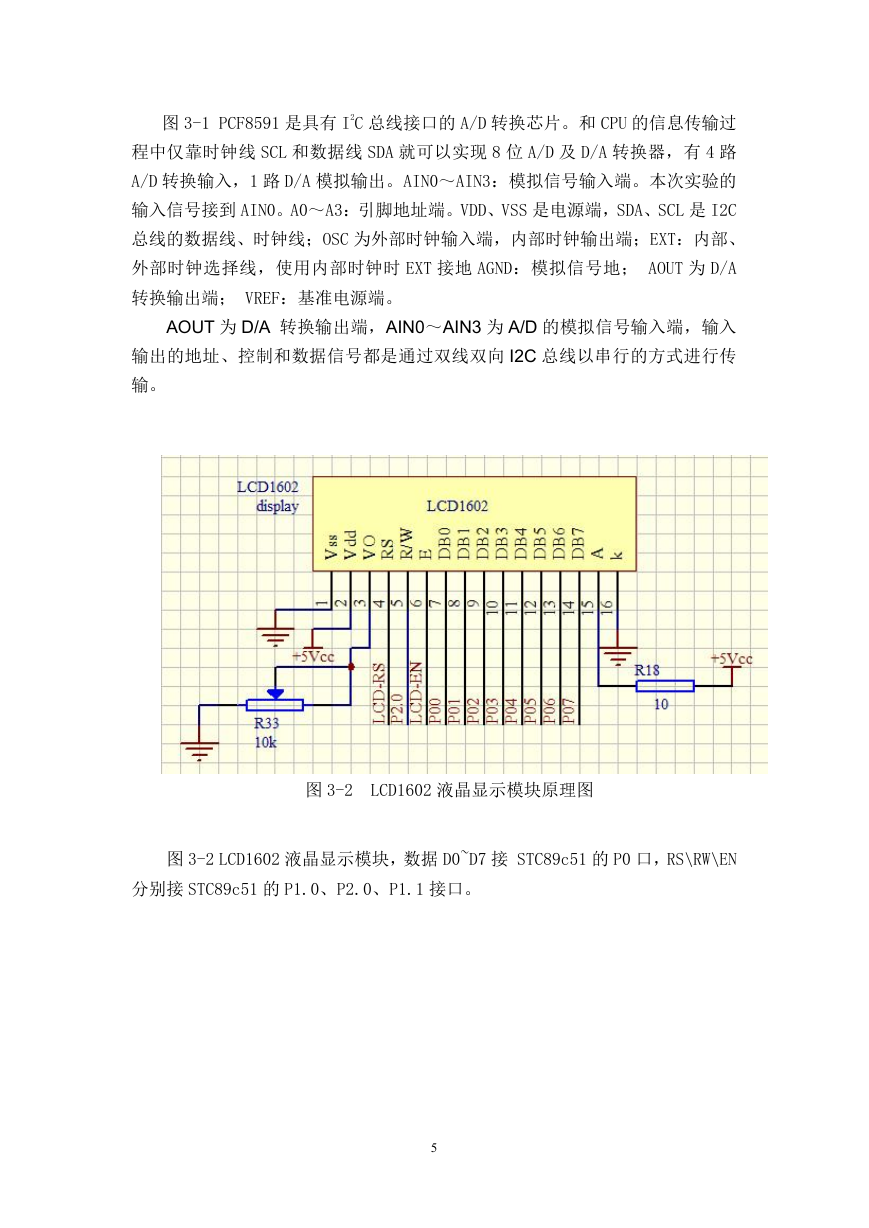

图 3-2

LCD1602 液晶显示模块原理图

图 3-2 LCD1602 液晶显示模块,数据 D0~D7 接 STC89c51 的 P0 口,RS\RW\EN

分别接 STC89c51 的 P1.0、P2.0、P1.1 接口。

5

�

图 3-3 AT24C02 储存模块原理图

如图 3-3 所示为本题的存储模块电路图,采集的外部信号经单片机处理后存

到 AT24C02。引脚 A0、A1、A2、GND 都接地,SCL 和 SDA 接 P1.2 、P1.3。

图 3-4 按键模块

图 3-4 是按键模块,按键 S1、S2、S3、S4 分别接 P3 口的 P3.2、P3.3、P3.4、

P3.5,本次实验的存储与回放的两个按键分别由 S4 和 S2 完成的。

6

�

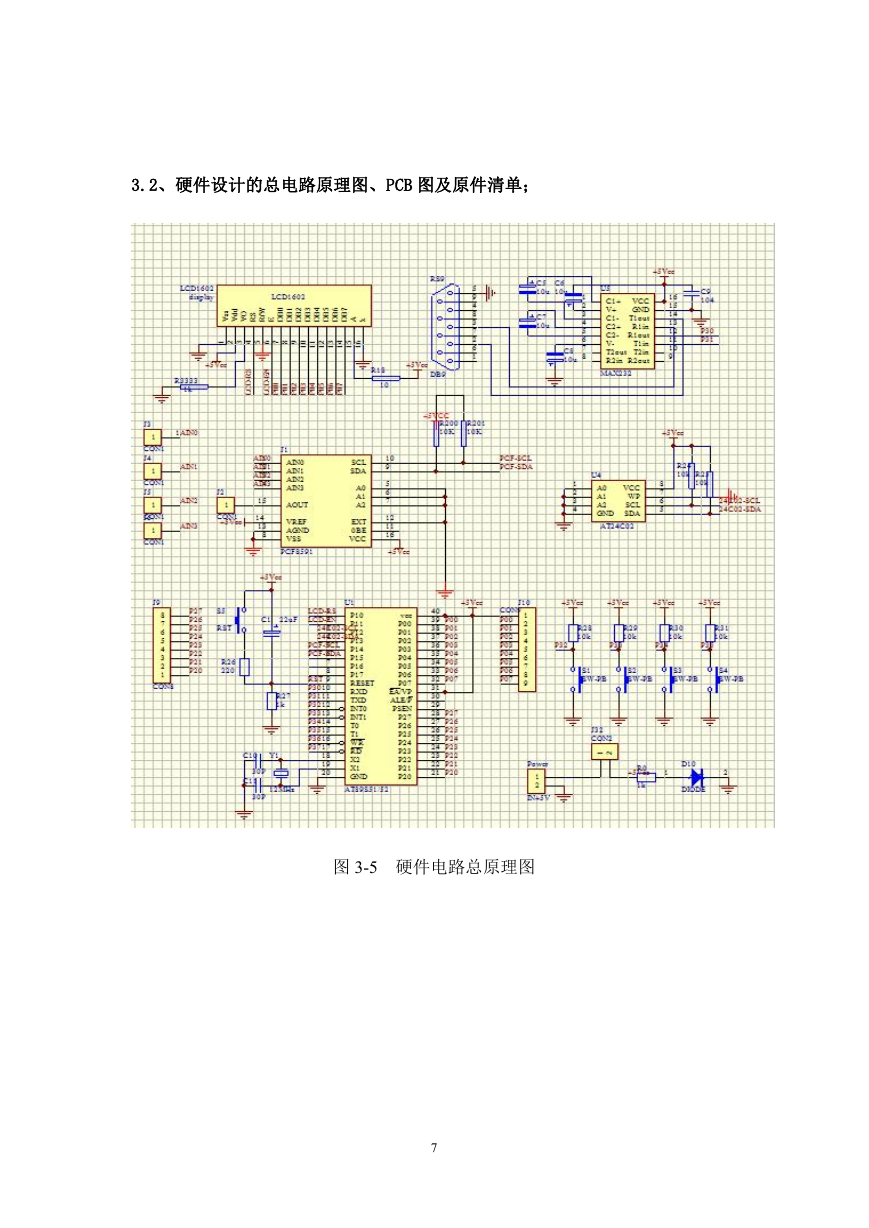

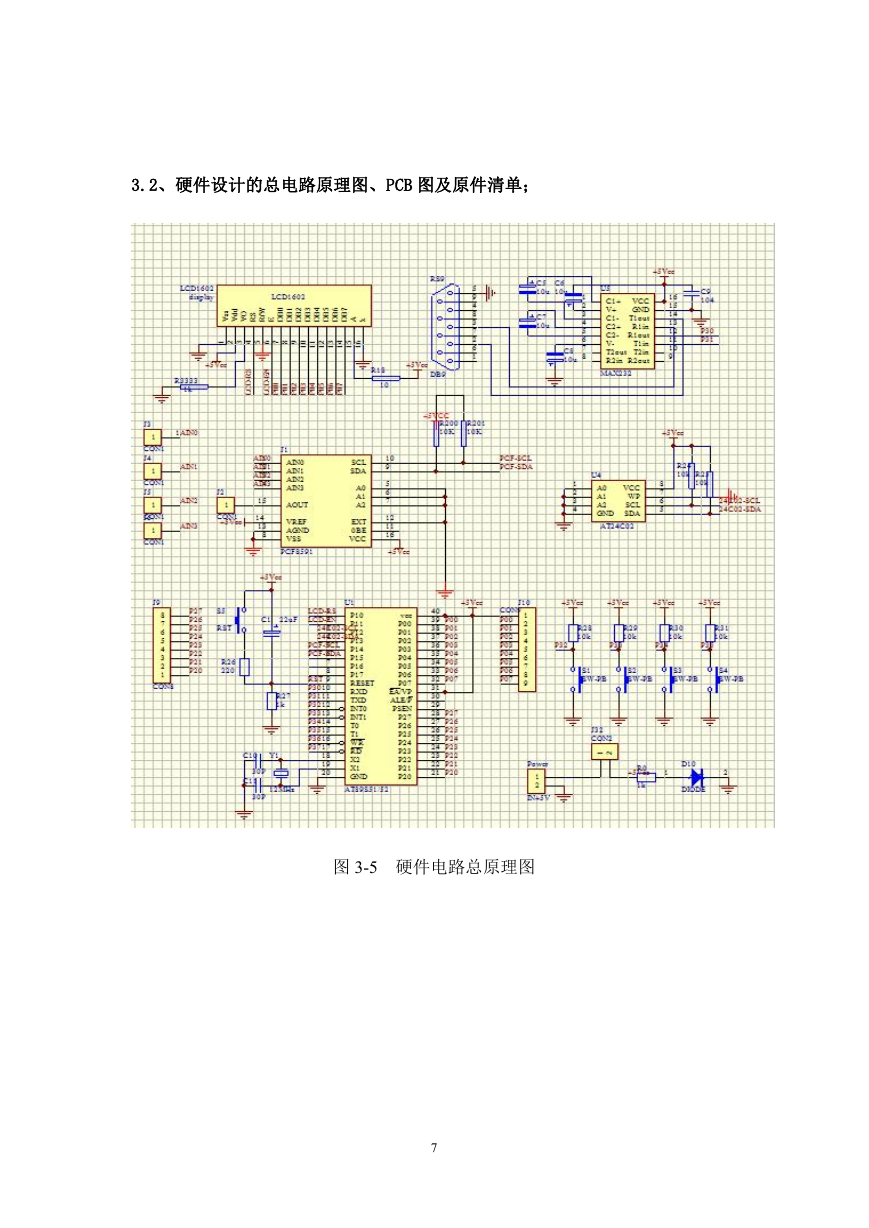

3.2、硬件设计的总电路原理图、PCB 图及原件清单;

图 3-5 硬件电路总原理图

7

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc