1 TMS320C6678 Features and Description

1.1 Features

1.2 Applications

1.3 KeyStone Architecture

1.4 Device Description

1.5 Functional Block Diagram

1.6 Release History

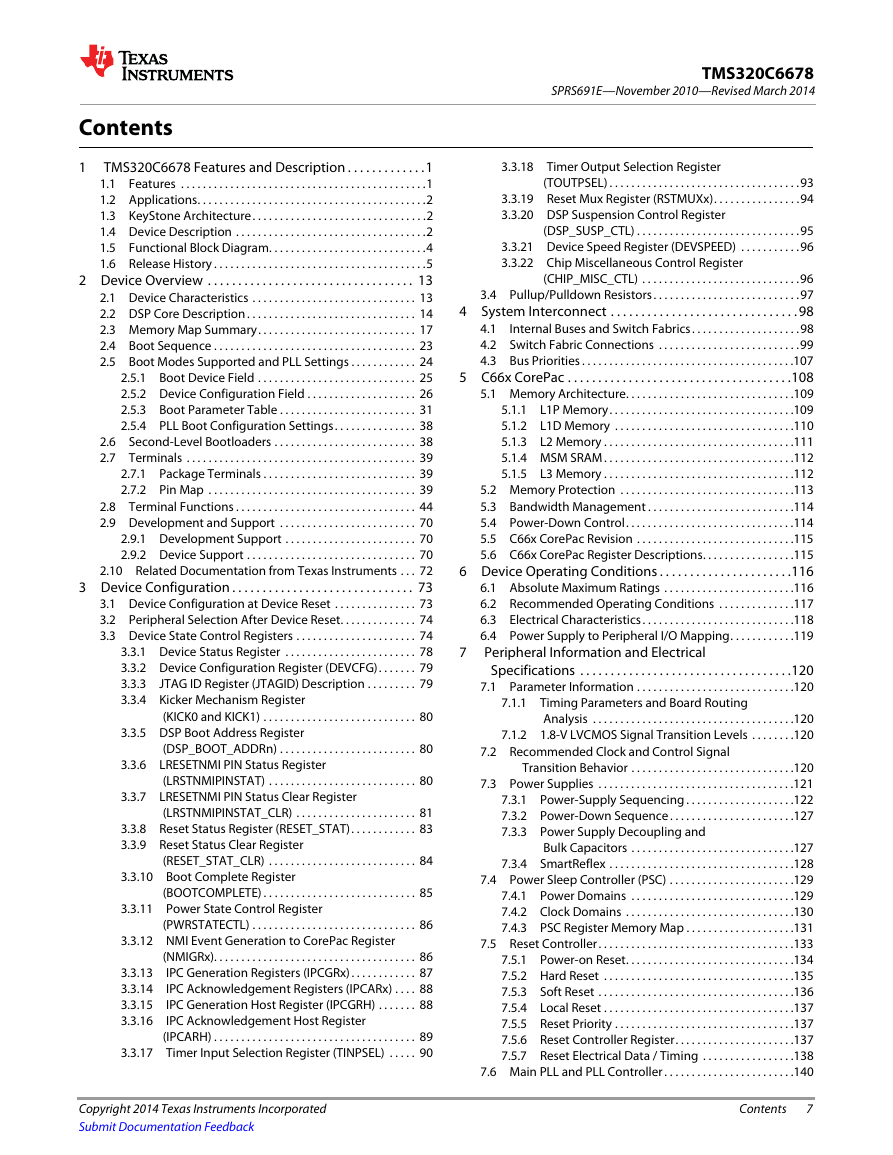

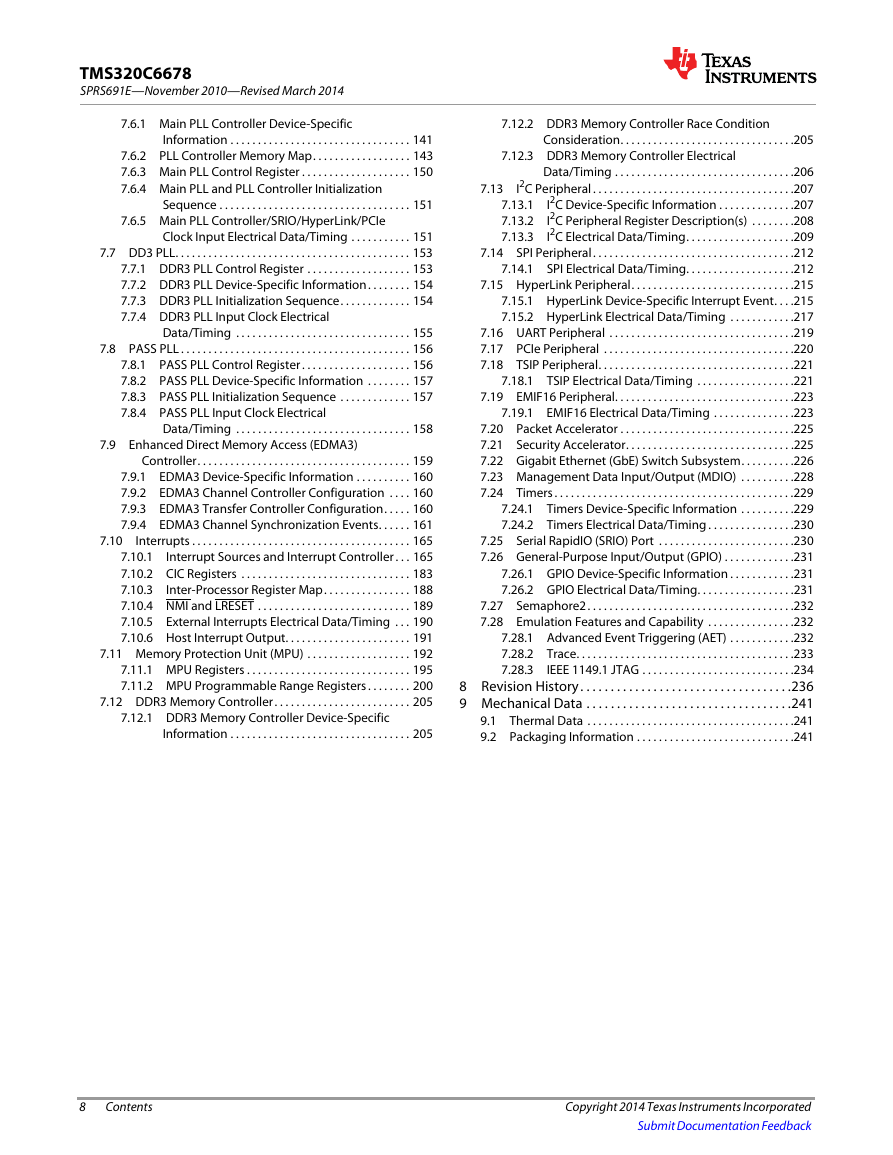

Contents

List of Figures

List of Tables

2 Device Overview

2.1 Device Characteristics

2.2 DSP Core Description

2.3 Memory Map Summary

2.4 Boot Sequence

2.5 Boot Modes Supported and PLL Settings

2.5.1 Boot Device Field

2.5.2 Device Configuration Field

2.5.2.1 No Boot/ EMIF16 Boot Device Configuration

2.5.2.2 Serial Rapid I/O Boot Device Configuration

2.5.2.3 Ethernet (SGMII) Boot Device Configuration

2.5.2.4 PCI Boot Device Configuration

2.5.2.5 I2C Boot Device Configuration

2.5.2.6 SPI Boot Device Configuration

2.5.2.7 HyperLink Boot Device Configuration

2.5.3 Boot Parameter Table

2.5.3.1 EMIF16 Boot Parameter Table

2.5.3.2 SRIO Boot Parameter Table

2.5.3.3 Ethernet Boot Parameter Table

2.5.3.4 PCIe Boot Parameter Table

2.5.3.5 I2C Boot Parameter Table

2.5.3.6 SPI Boot Parameter Table

2.5.3.7 HyperLink Boot Parameter Table

2.5.3.8 DDR3 Configuration Table

2.5.4 PLL Boot Configuration Settings

2.6 Second-Level Bootloaders

2.7 Terminals

2.7.1 Package Terminals

2.7.2 Pin Map

2.8 Terminal Functions

2.9 Development and Support

2.9.1 Development Support

2.9.2 Device Support

2.9.2.1 Device and Development-Support Tool Nomenclature

2.10 Related Documentation from Texas Instruments

3 Device Configuration

3.1 Device Configuration at Device Reset

3.2 Peripheral Selection After Device Reset

3.3 Device State Control Registers

3.3.1 Device Status Register

3.3.2 Device Configuration Register (DEVCFG)

3.3.3 JTAG ID Register (JTAGID) Description

3.3.4 Kicker Mechanism Register (KICK0 and KICK1)

3.3.5 DSP Boot Address Register (DSP_BOOT_ADDRn)

3.3.6 LRESETNMI PIN Status Register (LRSTNMIPINSTAT)

3.3.7 LRESETNMI PIN Status Clear Register (LRSTNMIPINSTAT_CLR)

3.3.8 Reset Status Register (RESET_STAT)

3.3.9 Reset Status Clear Register (RESET_STAT_CLR)

3.3.10 Boot Complete Register (BOOTCOMPLETE)

3.3.11 Power State Control Register (PWRSTATECTL)

3.3.12 NMI Event Generation to CorePac Register (NMIGRx)

3.3.13 IPC Generation Registers (IPCGRx)

3.3.14 IPC Acknowledgement Registers (IPCARx)

3.3.15 IPC Generation Host Register (IPCGRH)

3.3.16 IPC Acknowledgement Host Register (IPCARH)

3.3.17 Timer Input Selection Register (TINPSEL)

3.3.18 Timer Output Selection Register (TOUTPSEL)

3.3.19 Reset Mux Register (RSTMUXx)

3.3.20 DSP Suspension Control Register (DSP_SUSP_CTL)

3.3.21 Device Speed Register (DEVSPEED)

3.3.22 Chip Miscellaneous Control Register (CHIP_MISC_CTL)

3.4 Pullup/Pulldown Resistors

4 System Interconnect

4.1 Internal Buses and Switch Fabrics

4.2 Switch Fabric Connections

4.3 Bus Priorities

5 C66x CorePac

5.1 Memory Architecture

5.1.1 L1P Memory

5.1.2 L1D Memory

5.1.3 L2 Memory

5.1.4 MSM SRAM

5.1.5 L3 Memory

5.2 Memory Protection

5.3 Bandwidth Management

5.4 Power-Down Control

5.5 C66x CorePac Revision

5.6 C66x CorePac Register Descriptions

6 Device Operating Conditions

6.1 Absolute Maximum Ratings

6.2 Recommended Operating Conditions

6.3 Electrical Characteristics

6.4 Power Supply to Peripheral I/O Mapping

7 Peripheral Information and Electrical Specifications

7.1 Parameter Information

7.1.1 Timing Parameters and Board Routing Analysis

7.1.2 1.8-V LVCMOS Signal Transition Levels

7.2 Recommended Clock and Control Signal Transition Behavior

7.3 Power Supplies

7.3.1 Power-Supply Sequencing

7.3.1.1 Core-Before-IO Power Sequencing

7.3.1.2 IO-Before-Core Power Sequencing

7.3.1.3 Prolonged Resets

7.3.1.4 Clocking During Power Sequencing

7.3.2 Power-Down Sequence

7.3.3 Power Supply Decoupling and Bulk Capacitors

7.3.4 SmartReflex

7.4 Power Sleep Controller (PSC)

7.4.1 Power Domains

7.4.2 Clock Domains

7.4.3 PSC Register Memory Map

7.5 Reset Controller

7.5.1 Power-on Reset

7.5.2 Hard Reset

7.5.3 Soft Reset

7.5.4 Local Reset

7.5.5 Reset Priority

7.5.6 Reset Controller Register

7.5.7 Reset Electrical Data / Timing

7.6 Main PLL and PLL Controller

7.6.1 Main PLL Controller Device-Specific Information

7.6.1.1 Internal Clocks and Maximum Operating Frequencies

7.6.1.2 Main PLL Controller Operating Modes

7.6.1.3 Main PLL Stabilization, Lock, and Reset Times

7.6.2 PLL Controller Memory Map

7.6.2.1 PLL Secondary Control Register (SECCTL)

7.6.2.2 PLL Controller Divider Register (PLLDIV2, PLLDIV5, PLLDIV8)

7.6.2.3 PLL Controller Clock Align Control Register (ALNCTL)

7.6.2.4 PLLDIV Divider Ratio Change Status Register (DCHANGE)

7.6.2.5 SYSCLK Status Register (SYSTAT)

7.6.2.6 Reset Type Status Register (RSTYPE)

7.6.2.7 Reset Control Register (RSTCTRL)

7.6.2.8 Reset Configuration Register (RSTCFG)

7.6.2.9 Reset Isolation Register (RSISO)

7.6.3 Main PLL Control Register

7.6.4 Main PLL and PLL Controller Initialization Sequence

7.6.5 Main PLL Controller/SRIO/HyperLink/PCIe Clock Input Electrical Data/Timing

7.7 DD3 PLL

7.7.1 DDR3 PLL Control Register

7.7.2 DDR3 PLL Device-Specific Information

7.7.3 DDR3 PLL Initialization Sequence

7.7.4 DDR3 PLL Input Clock Electrical Data/Timing

7.8 PASS PLL

7.8.1 PASS PLL Control Register

7.8.2 PASS PLL Device-Specific Information

7.8.3 PASS PLL Initialization Sequence

7.8.4 PASS PLL Input Clock Electrical Data/Timing

7.9 Enhanced Direct Memory Access (EDMA3) Controller

7.9.1 EDMA3 Device-Specific Information

7.9.2 EDMA3 Channel Controller Configuration

7.9.3 EDMA3 Transfer Controller Configuration

7.9.4 EDMA3 Channel Synchronization Events

7.10 Interrupts

7.10.1 Interrupt Sources and Interrupt Controller

7.10.2 CIC Registers

7.10.2.1 CIC0/CIC1 Register Map

7.10.2.2 CIC2 Register Map

7.10.2.3 CIC3 Register Map

7.10.3 Inter-Processor Register Map

7.10.4 NMI and LRESET

7.10.5 External Interrupts Electrical Data/Timing

7.10.6 Host Interrupt Output

7.11 Memory Protection Unit (MPU)

7.11.1 MPU Registers

7.11.1.1 MPU Register Map

7.11.1.2 Device-Specific MPU Registers

7.11.2 MPU Programmable Range Registers

7.11.2.1 Programmable Range n Start Address Register (PROGn_MPSAR)

7.11.2.2 Programmable Range n End Address Register (PROGn_MPEAR)

7.11.2.3 Programmable Range n Memory Protection Page Attribute Register (PROGn_MPPA)

7.11.2.4 MPU Registers Reset Values

7.12 DDR3 Memory Controller

7.12.1 DDR3 Memory Controller Device-Specific Information

7.12.2 DDR3 Memory Controller Race Condition Consideration

7.12.3 DDR3 Memory Controller Electrical Data/Timing

7.13 I2C Peripheral

7.13.1 I2C Device-Specific Information

7.13.2 I2C Peripheral Register Description(s)

7.13.3 I2C Electrical Data/Timing

7.13.3.1 Inter-Integrated Circuits (I2C) Timing

7.14 SPI Peripheral

7.14.1 SPI Electrical Data/Timing

7.14.1.1 SPI Timing

7.15 HyperLink Peripheral

7.15.1 HyperLink Device-Specific Interrupt Event

7.15.2 HyperLink Electrical Data/Timing

7.16 UART Peripheral

7.17 PCIe Peripheral

7.18 TSIP Peripheral

7.18.1 TSIP Electrical Data/Timing

7.19 EMIF16 Peripheral

7.19.1 EMIF16 Electrical Data/Timing

7.20 Packet Accelerator

7.21 Security Accelerator

7.22 Gigabit Ethernet (GbE) Switch Subsystem

7.23 Management Data Input/Output (MDIO)

7.24 Timers

7.24.1 Timers Device-Specific Information

7.24.2 Timers Electrical Data/Timing

7.25 Serial RapidIO (SRIO) Port

7.26 General-Purpose Input/Output (GPIO)

7.26.1 GPIO Device-Specific Information

7.26.2 GPIO Electrical Data/Timing

7.27 Semaphore2

7.28 Emulation Features and Capability

7.28.1 Advanced Event Triggering (AET)

7.28.2 Trace

7.28.2.1 Trace Electrical Data/Timing

7.28.3 IEEE 1149.1 JTAG

7.28.3.1 IEEE 1149.1 JTAG Compatibility Statement

7.28.3.2 JTAG Electrical Data/Timing

8 Revision History

9 Mechanical Data

9.1 Thermal Data

9.2 Packaging Information

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc