CPU6502 Instruction Manual v1.1

Preliminary

11/10/1999

SUNPLUS TECHNOLOGY CO., LTD.

�

CPU6502 Instruction Manual v1.1, Preliminary

CPU6502 Instruction Manual v1.1

ª 1999 Sunplus Technology, Co., Ltd.

ALL RIGHTS RESERVED

Documentation Notice: Sunplus Technology reserves the right to change this documentation without

prior notice.

Information provided by Sunplus Technology is believed to be accurate and reliable. However, no

responsibility is assumed by Sunplus Technology for errors, omissions or any loss of profit resulting

from the use of information contained in this documentation.

If you have suggestions on this documentation which can better serve your needs, please contact:

Sunplus Technology

Division of System Application

Department of System Application II

No. 19, Innovation Road 1, Science-Based Industrial Park,

Hsin-Chu, Taiwan, R.O.C.

FAX: 886-3-578-6006

e-mail: service@sunplus.com.tw

Printed in Taiwan, R.O.C.

Printing History

v1.0

v1.1

04/16/1999

11/10/1999

by Michael Lin

by Michael Lin

Sunplus reserves the rights to change this documentation without prior notice. 11/10/1999

2

�

CPU6502 Instruction Manual v1.1, Preliminary

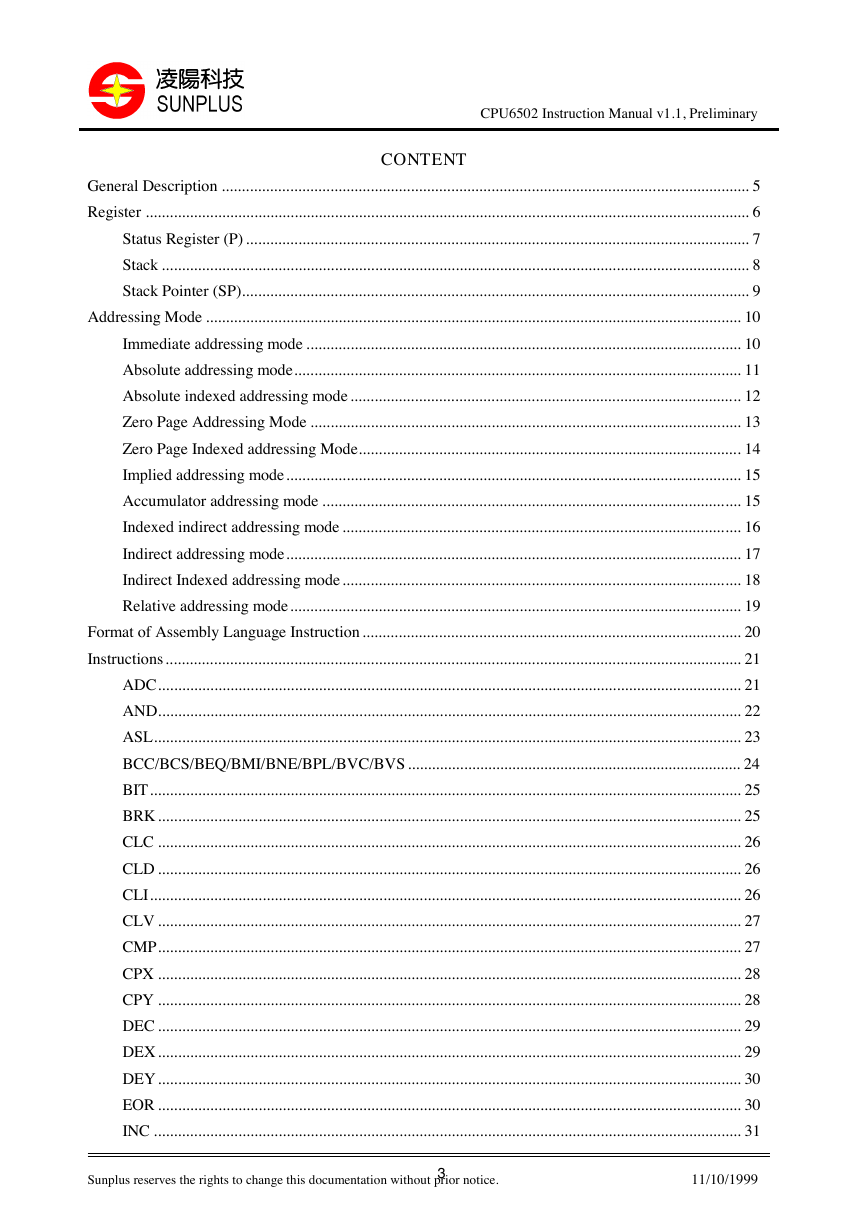

CONTENT

General Description ................................................................................................................................... 5

Register ...................................................................................................................................................... 6

Status Register (P) ............................................................................................................................. 7

Stack .................................................................................................................................................. 8

Stack Pointer (SP).............................................................................................................................. 9

Addressing Mode ..................................................................................................................................... 10

Immediate addressing mode ............................................................................................................ 10

Absolute addressing mode............................................................................................................... 11

Absolute indexed addressing mode ................................................................................................. 12

Zero Page Addressing Mode ........................................................................................................... 13

Zero Page Indexed addressing Mode............................................................................................... 14

Implied addressing mode................................................................................................................. 15

Accumulator addressing mode ........................................................................................................ 15

Indexed indirect addressing mode ................................................................................................... 16

Indirect addressing mode................................................................................................................. 17

Indirect Indexed addressing mode................................................................................................... 18

Relative addressing mode................................................................................................................ 19

Format of Assembly Language Instruction .............................................................................................. 20

Instructions............................................................................................................................................... 21

ADC................................................................................................................................................. 21

AND................................................................................................................................................. 22

ASL.................................................................................................................................................. 23

BCC/BCS/BEQ/BMI/BNE/BPL/BVC/BVS ................................................................................... 24

BIT................................................................................................................................................... 25

BRK................................................................................................................................................. 25

CLC ................................................................................................................................................. 26

CLD ................................................................................................................................................. 26

CLI................................................................................................................................................... 26

CLV ................................................................................................................................................. 27

CMP................................................................................................................................................. 27

CPX ................................................................................................................................................. 28

CPY ................................................................................................................................................. 28

DEC ................................................................................................................................................. 29

DEX................................................................................................................................................. 29

DEY................................................................................................................................................. 30

EOR ................................................................................................................................................. 30

INC .................................................................................................................................................. 31

Sunplus reserves the rights to change this documentation without prior notice. 11/10/1999

3

�

CPU6502 Instruction Manual v1.1, Preliminary

INX .................................................................................................................................................. 31

INY .................................................................................................................................................. 32

JMP.................................................................................................................................................. 32

JSR................................................................................................................................................... 33

LDA................................................................................................................................................. 33

LDX................................................................................................................................................. 34

LDY................................................................................................................................................. 34

LSR.................................................................................................................................................. 35

NOP ................................................................................................................................................. 35

ORA................................................................................................................................................. 36

PHA ................................................................................................................................................. 36

PHP.................................................................................................................................................. 37

PLA.................................................................................................................................................. 37

PLP .................................................................................................................................................. 37

ROL ................................................................................................................................................. 38

ROR................................................................................................................................................. 39

RTI................................................................................................................................................... 39

RTS.................................................................................................................................................. 40

SBC.................................................................................................................................................. 40

SEC.................................................................................................................................................. 41

SED.................................................................................................................................................. 41

SEI ................................................................................................................................................... 41

STA.................................................................................................................................................. 42

STX.................................................................................................................................................. 42

STY.................................................................................................................................................. 43

TAX................................................................................................................................................. 43

TAY................................................................................................................................................. 44

TSX.................................................................................................................................................. 44

TXA................................................................................................................................................. 44

TXS.................................................................................................................................................. 45

TYA................................................................................................................................................. 45

Summary of Available Instruction set for each CPU Type...................................................................... 46

Sunplus reserves the rights to change this documentation without prior notice. 11/10/1999

4

�

CPU6502 Instruction Manual v1.1, Preliminary

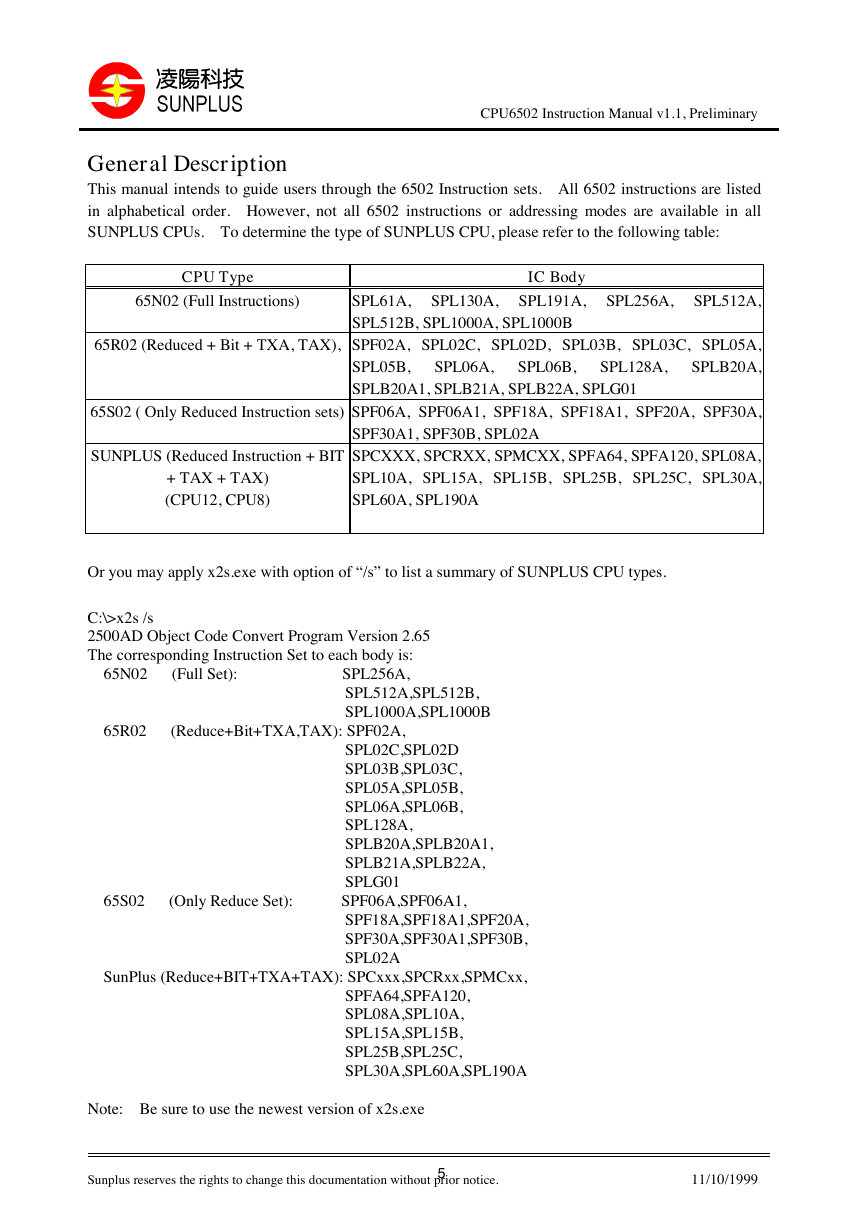

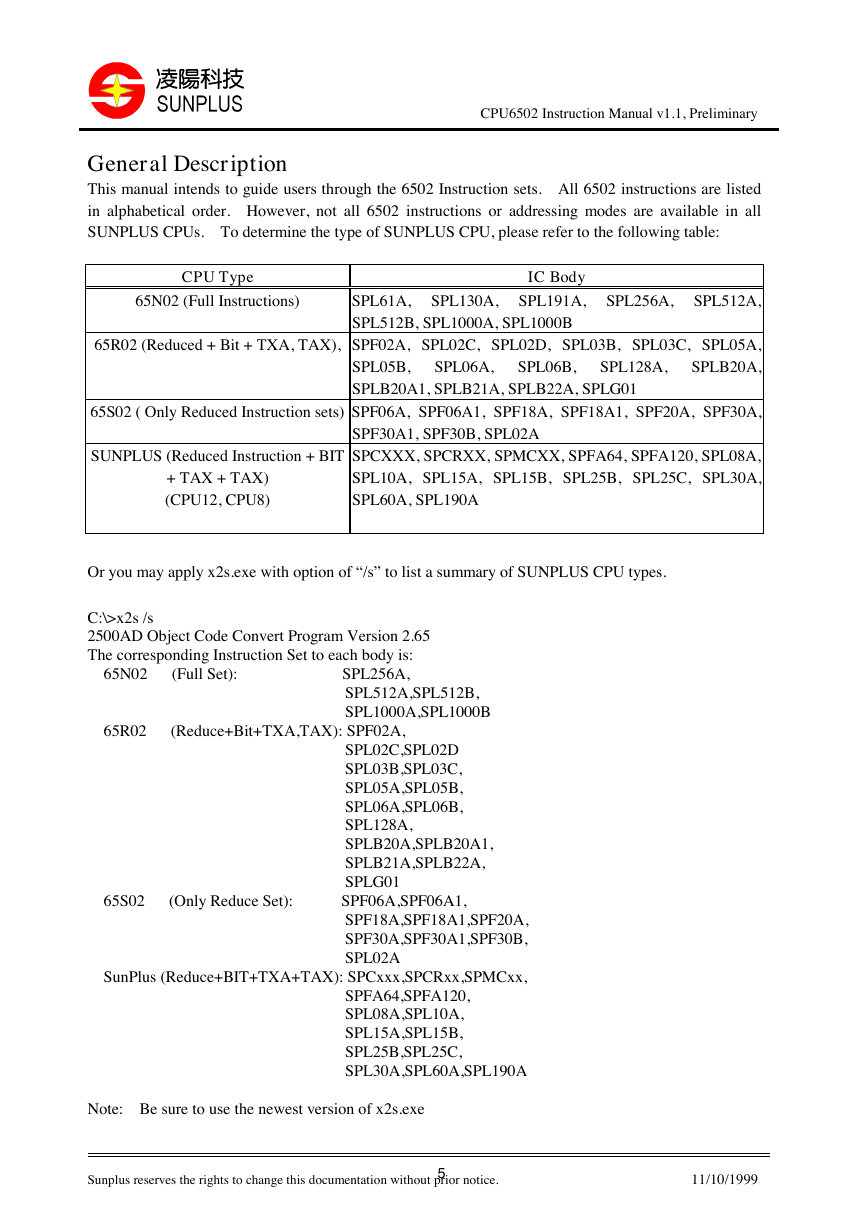

General Description

This manual intends to guide users through the 6502 Instruction sets. All 6502 instructions are listed

in alphabetical order. However, not all 6502 instructions or addressing modes are available in all

SUNPLUS CPUs. To determine the type of SUNPLUS CPU, please refer to the following table:

CPU Type

65N02 (Full Instructions)

IC Body

SPL61A, SPL130A, SPL191A, SPL256A, SPL512A,

SPL512B, SPL1000A, SPL1000B

65R02 (Reduced + Bit + TXA, TAX), SPF02A, SPL02C, SPL02D, SPL03B, SPL03C, SPL05A,

SPLB20A,

SPL128A,

SPL06B,

SPL05B,

SPLB20A1, SPLB21A, SPLB22A, SPLG01

SPL06A,

65S02 ( Only Reduced Instruction sets) SPF06A, SPF06A1, SPF18A, SPF18A1, SPF20A, SPF30A,

SUNPLUS (Reduced Instruction + BIT

+ TAX + TAX)

(CPU12, CPU8)

SPF30A1, SPF30B, SPL02A

SPCXXX, SPCRXX, SPMCXX, SPFA64, SPFA120, SPL08A,

SPL10A, SPL15A, SPL15B, SPL25B, SPL25C, SPL30A,

SPL60A, SPL190A

Or you may apply x2s.exe with option of “/s” to list a summary of SUNPLUS CPU types.

C:\>x2s /s

2500AD Object Code Convert Program Version 2.65

The corresponding Instruction Set to each body is:

65N02 (Full Set): SPL256A,

SPL512A,SPL512B,

SPL1000A,SPL1000B

65R02 (Reduce+Bit+TXA,TAX): SPF02A,

SPL02C,SPL02D

SPL03B,SPL03C,

SPL05A,SPL05B,

SPL06A,SPL06B,

SPL128A,

SPLB20A,SPLB20A1,

SPLB21A,SPLB22A,

SPLG01

65S02 (Only Reduce Set): SPF06A,SPF06A1,

SPF18A,SPF18A1,SPF20A,

SPF30A,SPF30A1,SPF30B,

SPL02A

SunPlus (Reduce+BIT+TXA+TAX): SPCxxx,SPCRxx,SPMCxx,

SPFA64,SPFA120,

SPL08A,SPL10A,

SPL15A,SPL15B,

SPL25B,SPL25C,

SPL30A,SPL60A,SPL190A

Note: Be sure to use the newest version of x2s.exe

Sunplus reserves the rights to change this documentation without prior notice. 11/10/1999

5

�

CPU6502 Instruction Manual v1.1, Preliminary

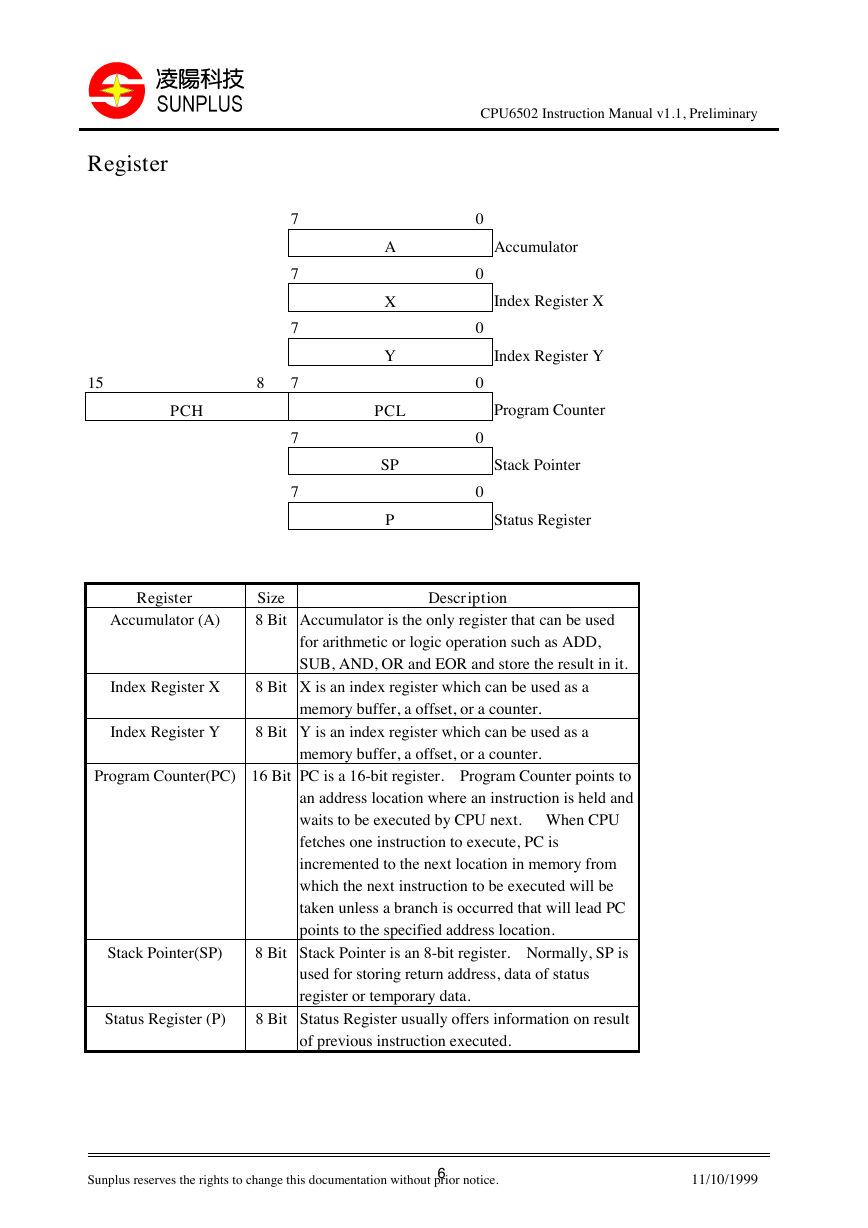

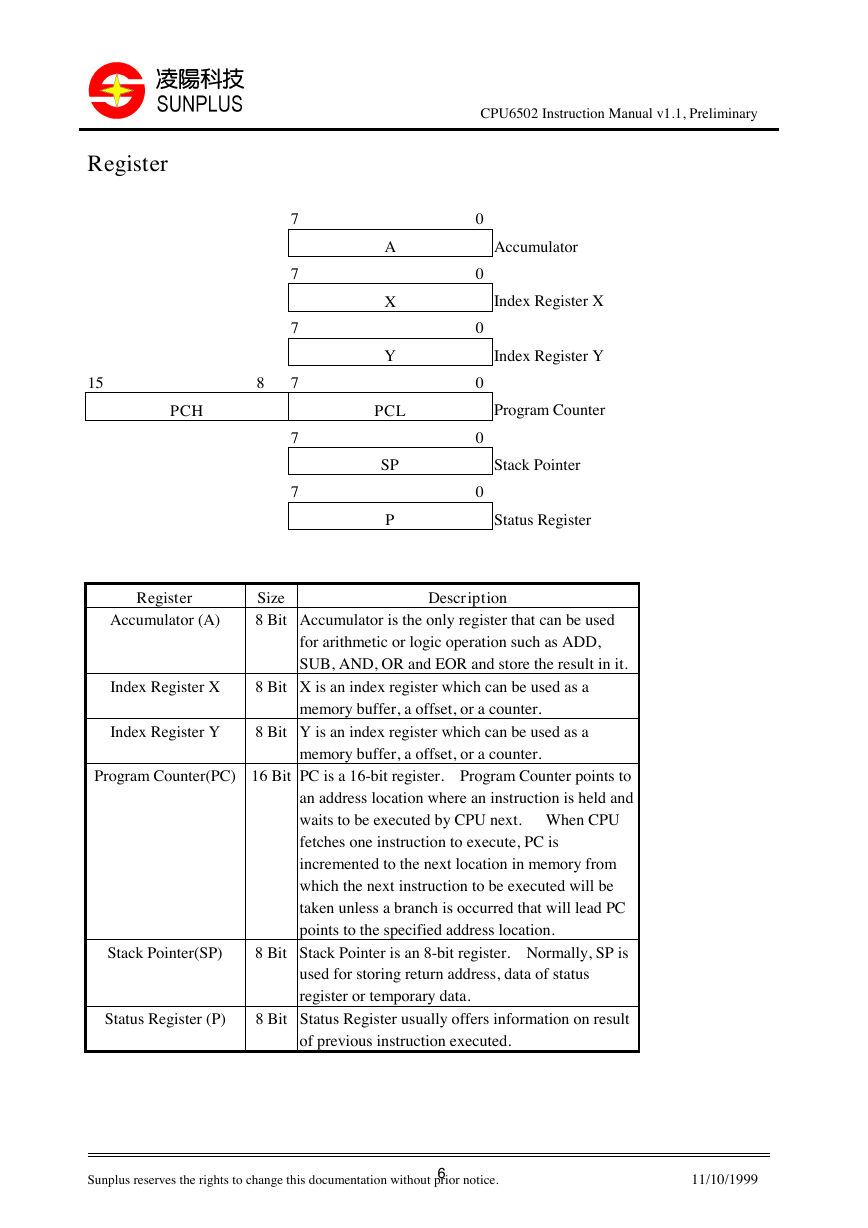

Register

7 0

A

Accumulator

7 0

X

Index Register X

7 0

Y

Index Register Y

15 8

7 0

PCH

PCL

Program Counter

7 0

SP

Stack Pointer

7 0

P

Status Register

Register

Accumulator (A)

Size

8 Bit Accumulator is the only register that can be used

Description

for arithmetic or logic operation such as ADD,

SUB, AND, OR and EOR and store the result in it.

Index Register X

8 Bit X is an index register which can be used as a

memory buffer, a offset, or a counter.

Index Register Y

8 Bit Y is an index register which can be used as a

memory buffer, a offset, or a counter.

Program Counter(PC) 16 Bit PC is a 16-bit register. Program Counter points to

an address location where an instruction is held and

waits to be executed by CPU next. When CPU

fetches one instruction to execute, PC is

incremented to the next location in memory from

which the next instruction to be executed will be

taken unless a branch is occurred that will lead PC

points to the specified address location.

Stack Pointer(SP)

8 Bit Stack Pointer is an 8-bit register. Normally, SP is

used for storing return address, data of status

register or temporary data.

Status Register (P)

8 Bit Status Register usually offers information on result

of previous instruction executed.

Sunplus reserves the rights to change this documentation without prior notice. 11/10/1999

6

�

CPU6502 Instruction Manual v1.1, Preliminary

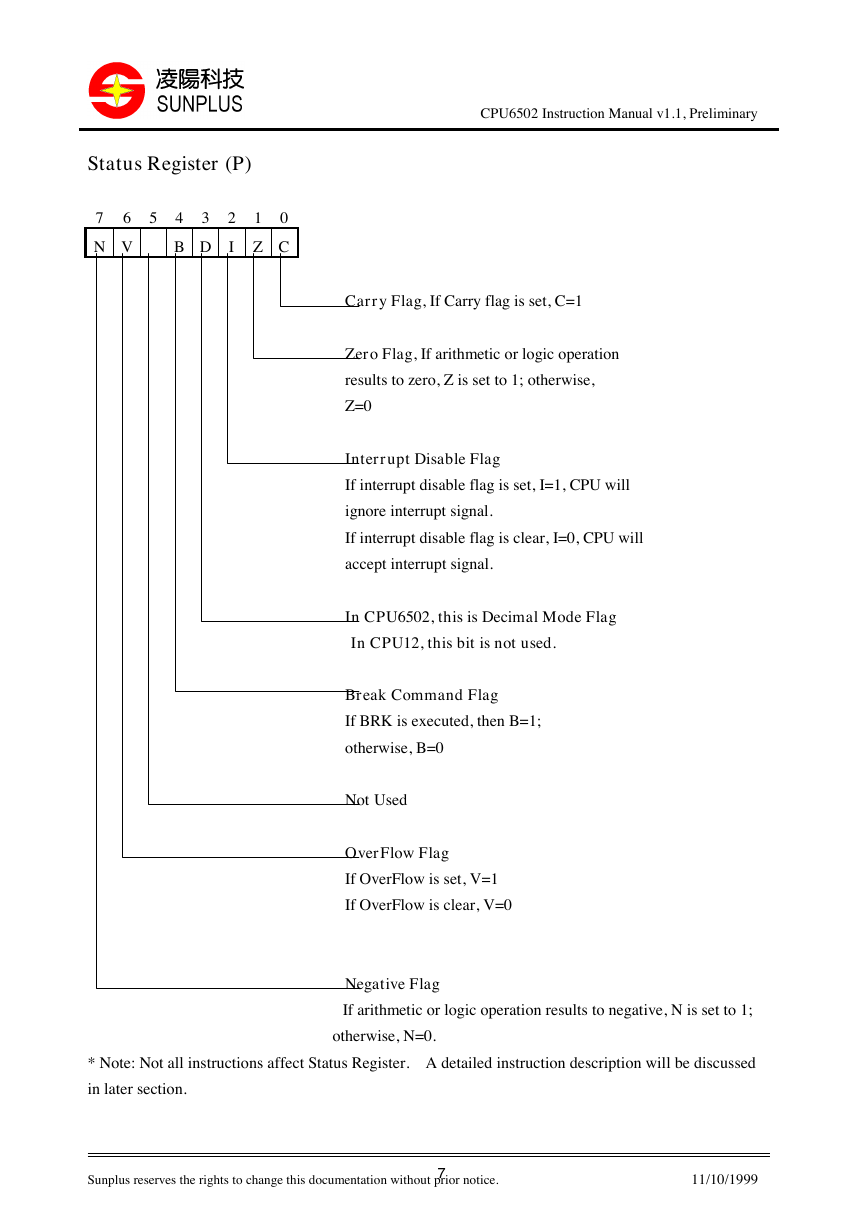

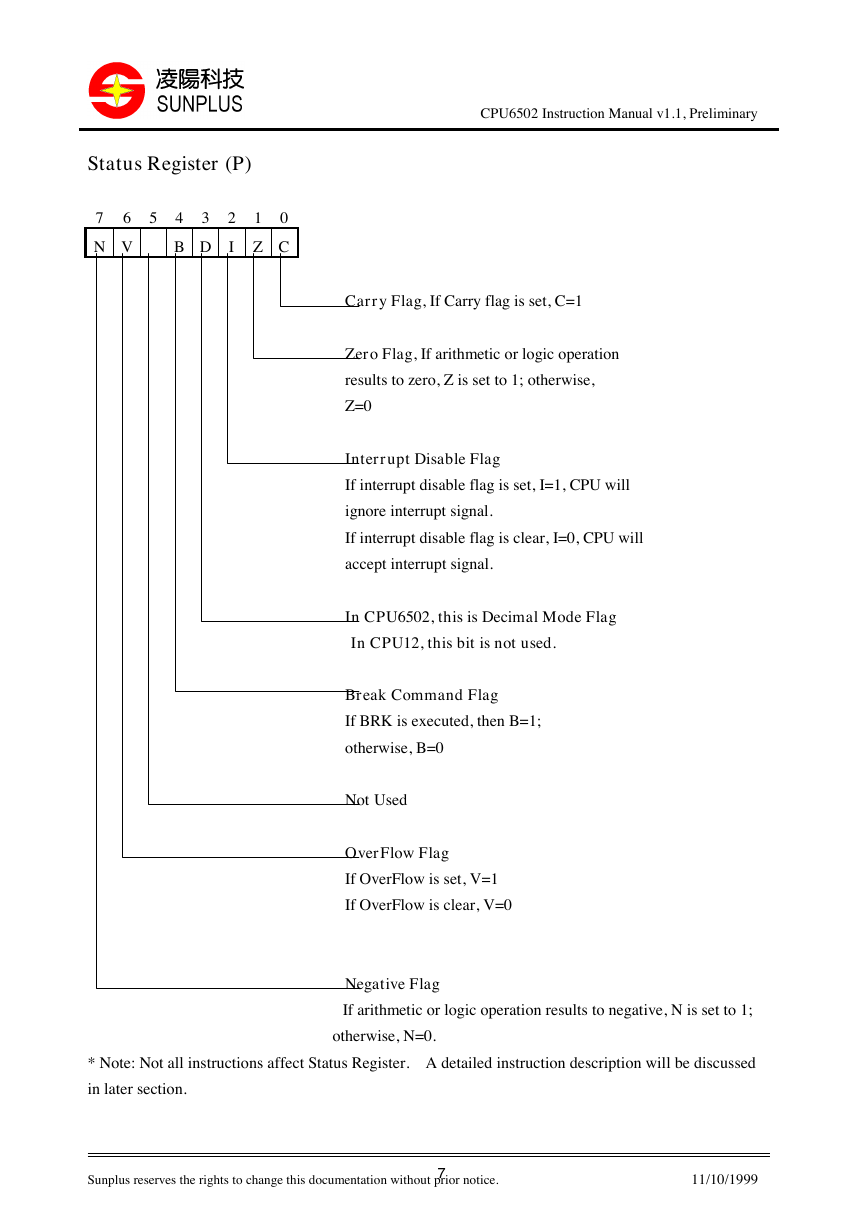

Status Register (P)

7

6

5

4

3

2

1

0

N V

B D I Z C

Carry Flag, If Carry flag is set, C=1

Zero Flag, If arithmetic or logic operation

results to zero, Z is set to 1; otherwise,

Z=0

Interrupt Disable Flag

If interrupt disable flag is set, I=1, CPU will

ignore interrupt signal.

If interrupt disable flag is clear, I=0, CPU will

accept interrupt signal.

In CPU6502, this is Decimal Mode Flag

In CPU12, this bit is not used.

Break Command Flag

If BRK is executed, then B=1;

otherwise, B=0

Not Used

OverFlow Flag

If OverFlow is set, V=1

If OverFlow is clear, V=0

Negative Flag

If arithmetic or logic operation results to negative, N is set to 1;

otherwise, N=0.

* Note: Not all instructions affect Status Register. A detailed instruction description will be discussed

in later section.

Sunplus reserves the rights to change this documentation without prior notice. 11/10/1999

7

�

CPU6502 Instruction Manual v1.1, Preliminary

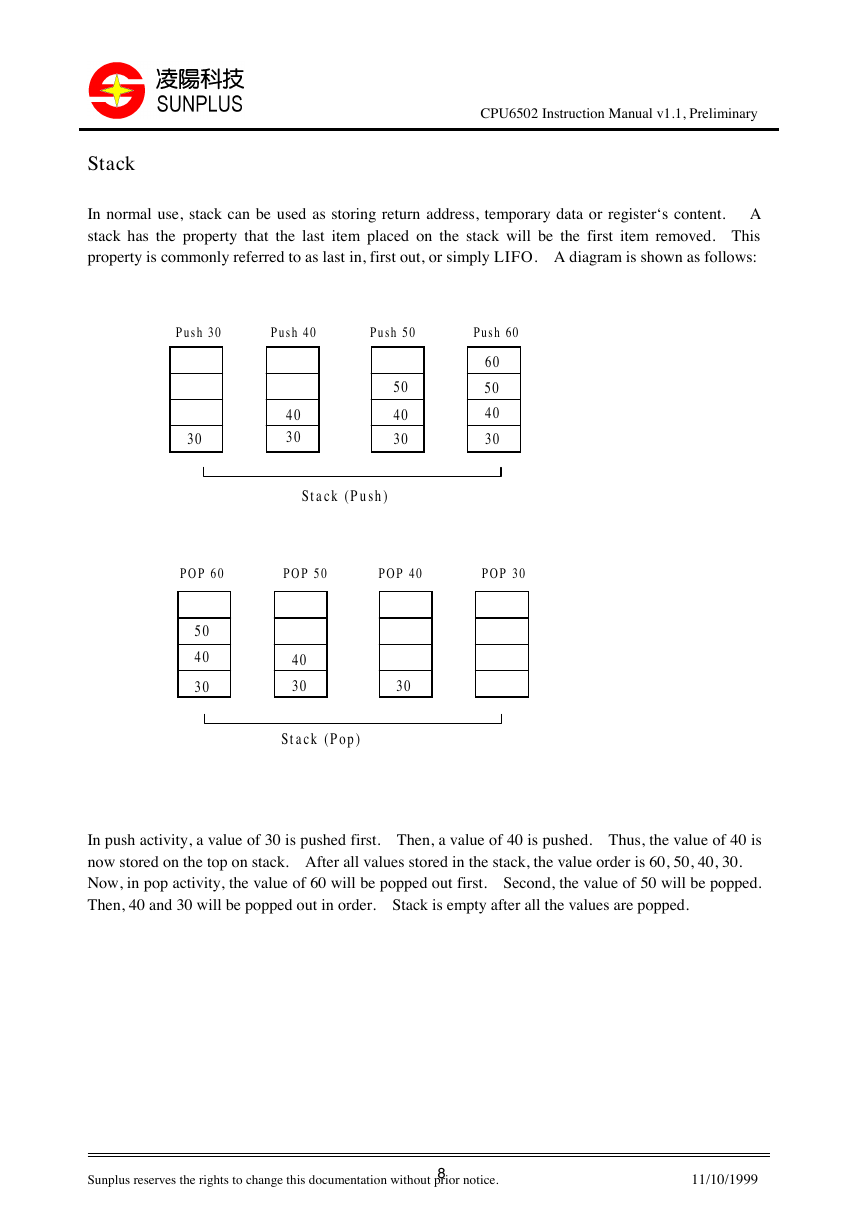

Stack

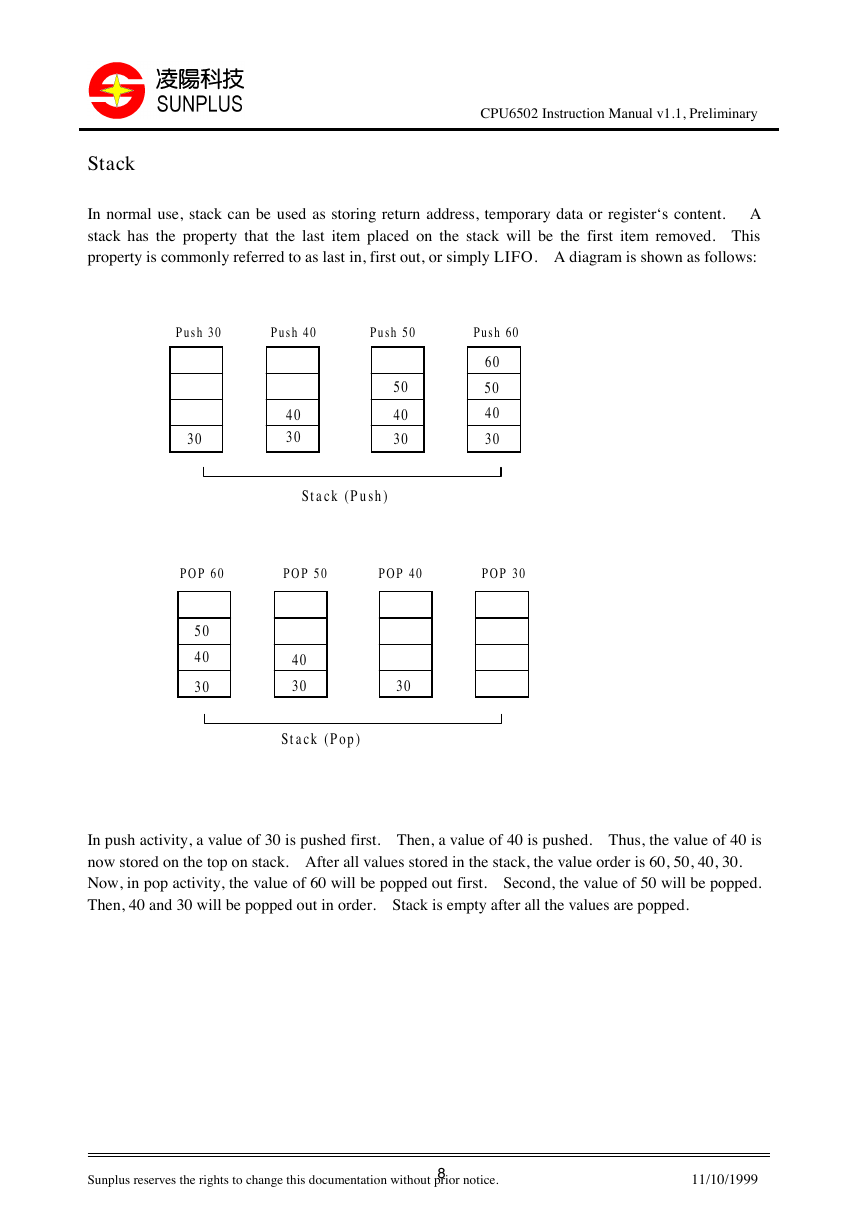

In normal use, stack can be used as storing return address, temporary data or register‘s content. A

stack has the property that the last item placed on the stack will be the first item removed. This

property is commonly referred to as last in, first out, or simply LIFO. A diagram is shown as follows:

Push 30

Push 40

Push 50

Push 60

50

40

30

60

50

40

30

30

40

30

Stack (Push)

P O P 6 0

P O P 5 0

P O P 4 0

P O P 3 0

50

40

30

40

30

30

Stack (Pop)

In push activity, a value of 30 is pushed first. Then, a value of 40 is pushed. Thus, the value of 40 is

now stored on the top on stack. After all values stored in the stack, the value order is 60, 50, 40, 30.

Now, in pop activity, the value of 60 will be popped out first. Second, the value of 50 will be popped.

Then, 40 and 30 will be popped out in order. Stack is empty after all the values are popped.

Sunplus reserves the rights to change this documentation without prior notice. 11/10/1999

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc