第 34 卷 第 5 期

2011 年 10 月

电 子 器 件

Chinese Journal of Electron Devices

Vol. 34 No. 5

Oct. 2011

The Design of Signal Generator Based on Verilog HDL

,

CHEN Longdao*

CHEN Yajun

,

Zhejiang University

,

Hangzhou 310027

College of Electrical Engineering

(

,

China

)

Abstract

In order to design the signal generator which can generate four kinds of signals—the sine wave

,

the triangle wave and the sawtooth wave

,

and whose amplitudes and frequencies are adaptively changeable

wave

,

the square

,

a

research about works was developed. The design is realized with Verilog HDL in the environment of Altera’s Quartus

Ⅱ. When the program was downloaded to the chip of FPGA

With Verilog HDL

,

the design efficiency is improved and the design has the advantages of facility design

,

convenient

,

the results of the experiments met the scheme design.

operation

,

high reliability.

:

Key words

embedded system

:

EEACC

1230

doi

10. 3969 / j. issn. 1005-9490. 2011. 05. 011

;

signal generator

;

Verilog Hardware Description Language

;

Quartus Ⅱ

:

:

基于 Verilog HDL 的信号发生器的设计

陈亚军,陈隆道*

( 浙江大学电气工程学院,杭州

310027

)

方波

、

三角波和锯齿波等四种波形,且输出波形的幅值

、

工具软件环境下,应用

频率可调的信号发生

、

器

语言编程来完成整个设计,不但提高了设计效率,而且使系统具

语言完成了系统的设计,建立的程序工程下载至

Verilog HDL

采用

FPGA

。

在

Altera

公司的

Quartus Ⅱ

摘 要: 旨在研究设计一种可以产生正弦波

器

件后,系统实验测试结果达到了预想效果

性能稳定的特点

有设计灵活

、

关键词: 嵌入式系统; 信号发生器;

中图分类号: TP312

实现简单

、

。

。

Verilog HDL

文献标识码: A

Verilog HDL

;

Quartus Ⅱ

DDS

检测

、

FPGA、

1-9

来直接合成正弦波[

信号发生器已广泛应用于工业

教学

医学

、

、

等领域,目前使用较多的设计方案是利用

单片

],这

机等处理器芯片控制

种方案相比传统采用模拟分立元件来设计信号发生

器的方法,信号频率更稳定

信号参数也易

精度更高

、

、

于调节,但电路复杂,成本也增加了

是

器件在嵌入

编程的工具软件,支持各种硬

、

等多种硬件

器件进行信号发生器系

Altera

式系统中的设计

件描述语言,功能齐全; 在

描述语言中,以往使用

FPGA

统设计 的 方 案 大 部 分 采 用

公司开发的一种针对

VHDL、AHDL

语 言,但

相比其他语言更易于用户编程和应用[

工具软件环境下,用

HDL

设计便是一种在

Verilog

该

]

。Quartus Ⅱ

CPLD \ FPGA

仿真

、

VHDL

。

7-9

QuartusⅡ

语言编程实现正弦波

方波

、

HDL

种波形的产生的信号发生器

。

三角波

、

Verilog

锯齿波四

、

收稿日期: 2011-06-15

修改日期: 2011-06-28

文章编号: 1005-9490( 2011) 05-0525-04

1 系统功能与实现原理

1. 1 系统功能简介

方波

、

该设计是一种能够产生正弦波

三角波

、

、

锯齿波等常用波形的信号发生器,并能根据要求对

输出波形的幅值和频率进行调节

根据选择开关的

。

控制信号,信号发生器可产生幅值在

范围内

可调

范围内可调的四种常

频率在

、

用波形

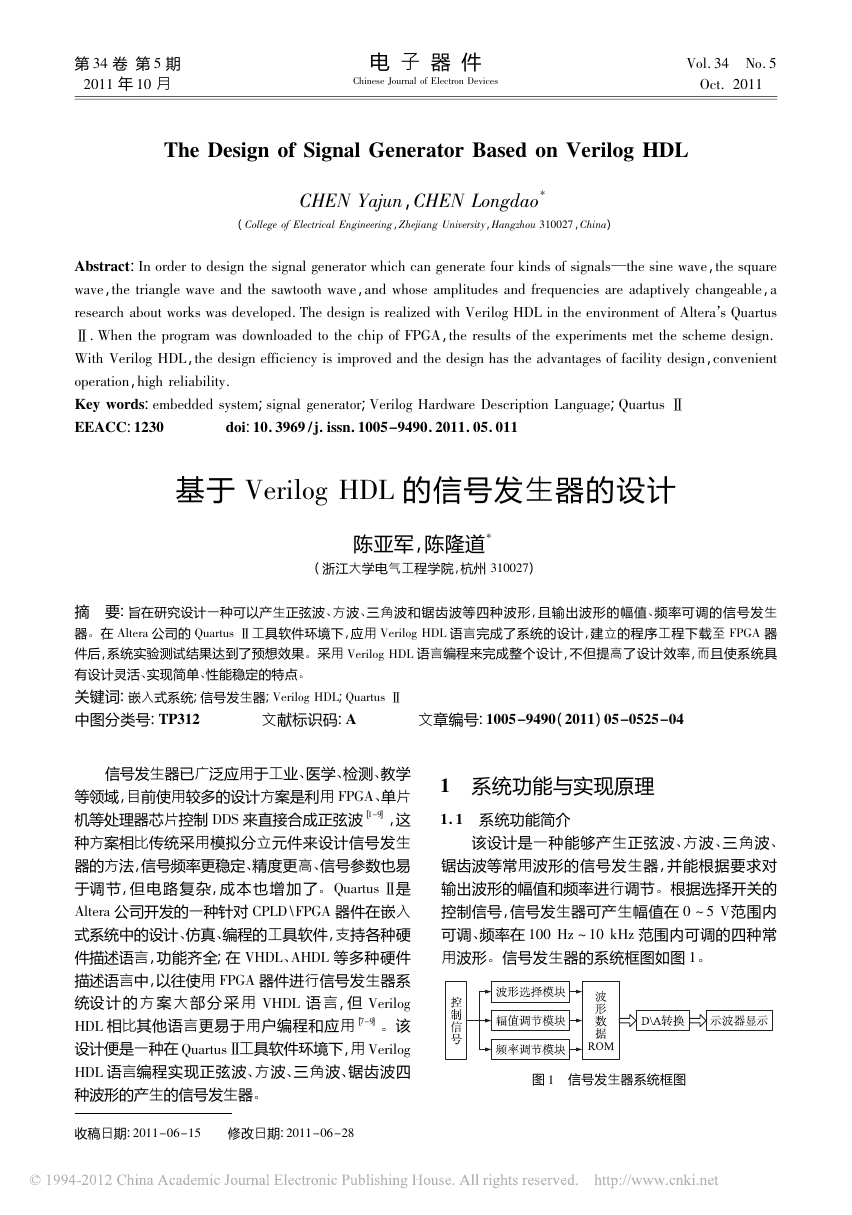

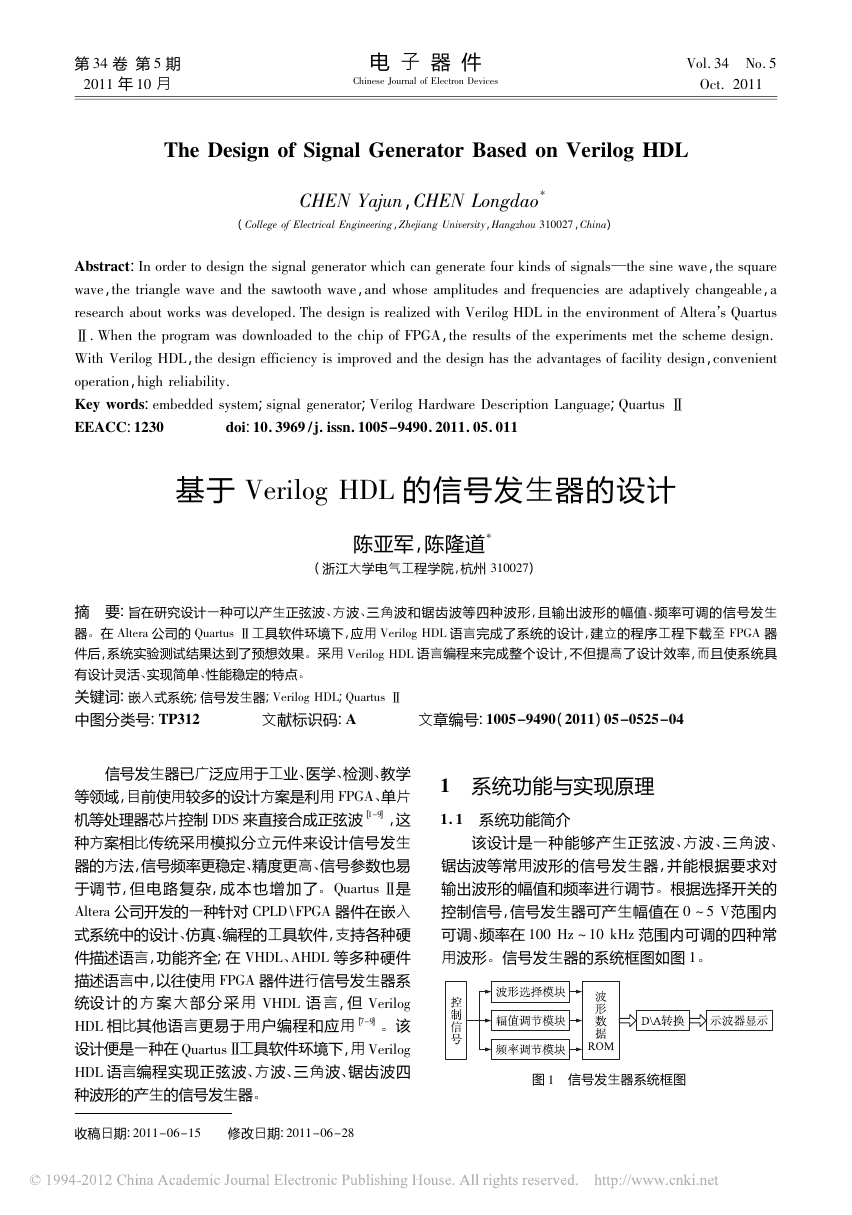

信号发生器的系统框图如图

100 Hz ~ 10 kHz

0 ~ 5 V

1。

。

图 1 信号发生器系统框图

�

625

电 子 器 件

第 34 卷

1. 2 实现原理概述

8

即

256

. mif

个点的

Quartus Ⅱ

号离散量化为

据,利 用

“Memory Initialization File”

的波形数据,再用

产生四种波形的原理: 将每种波形一周期的信

位二进制数作为波形数

软 件 内 部 自 带 的 初 始 化 文 件

文件来存储得到

文件定制波形数据存储器的

系

datarom. v

统按照选择开关的控制信号选择波形种类,然后根

据

中不同波形不同的地址读取相应的波形数

据,再根据控制信号对数据进行调幅操作,之后按照

由控制信号调制出的正确频率输送波形数据,经

文件,并将其例化为电路

D /

数模转换滤波后,便可送至示波器显示,从而实现

模块

ROM

ROM

. mif

。

A

了信号发生器波形发生的功能

2 波形数据存储 ROM 定制

。

8

。

个

256

256

ROM

定制波形数据存储

首先需要获取每种信

号的波形数据,要求每种波形数据均由

位

的二进制数构成

正弦波一周期波形数据的获取原

理是将正弦波一周期的信号幅值量化,离散采样,将

个点,并将每个点的

一个周期的正弦波分解成

位二进制数,从而完成正弦波的波形数

值转存为

据获取

锯齿波的波形数据获取方法

、

相仿

(

8

波的波形数据; 三角波: 前半周期从

0

递减到最小值

255

0

角波的波形数据; 锯齿波: 整个周期从

,从而获得锯齿波的波形数据[

值

255

的方

累加到最大值

,以此获取三

累加到最大

。

方波: 前半周期,即

,从而得到占空比为

位) ,后半周期取

个点,取最大值

,后半周期从

三角波

、

8

方波

50%

255

128

0

]

。

0

10

255

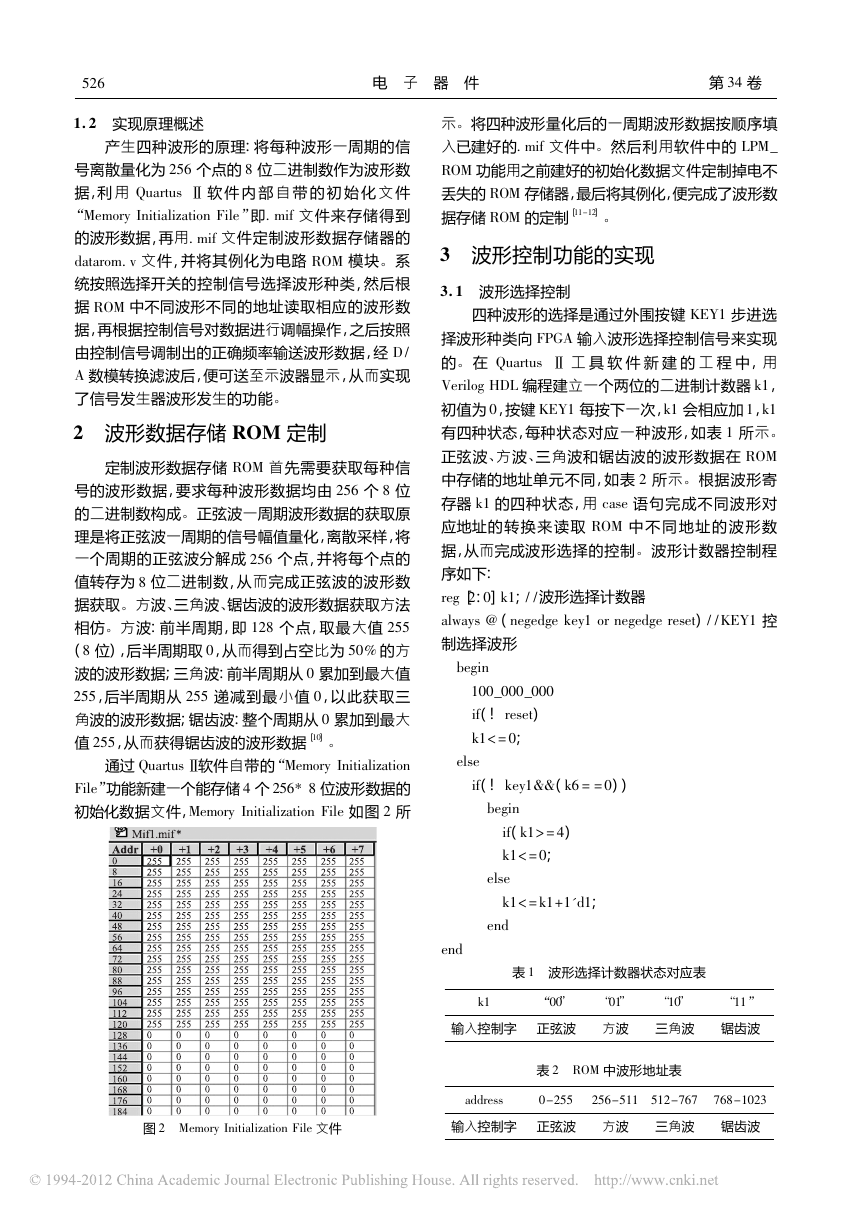

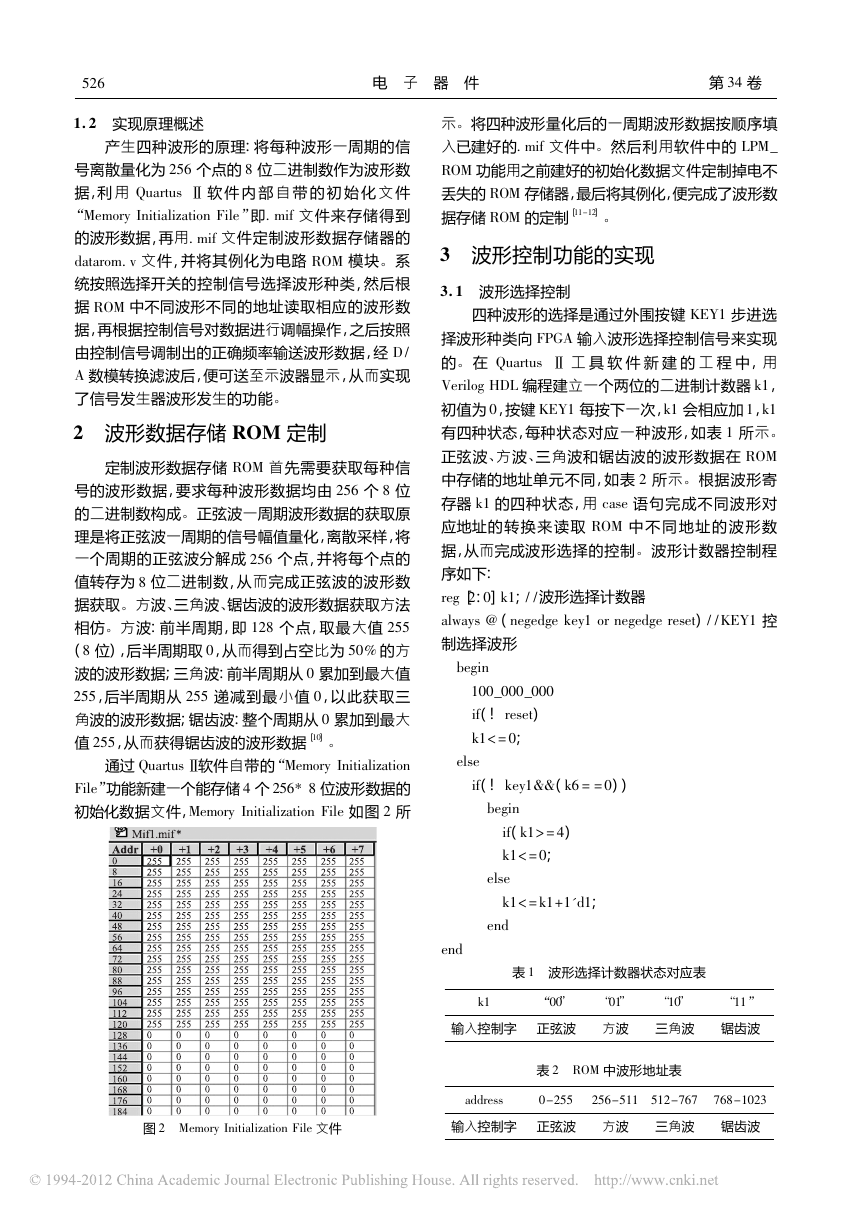

通过

功能新建一个能存储

软件自带的

个

Quartus Ⅱ

4

File”

初始化数据文件,

“Memory Initialization

位波形数据的

所

256* 8

如图

Memory Initialization File

2

。

。

示

入已建好的

将四种波形量化后的一周期波形数据按顺序填

文件中

然后利用软件中的

。

. mif

LPM_

功能用之前建好的初始化数据文件定制掉电不

存储器,最后将其例化,便完成了波形数

的定制[

ROM

11-12

]

ROM

丢失的

据存储

ROM

。

3 波形控制功能的实现

3. 1 波形选择控制

四种波形的选择是通过外围按键

择波形种类向

的

在

。

Quartus Ⅱ

FPGA

KEY1

步进选

输入波形选择控制信号来实现

工 具 软 件 新 建 的 工 程 中,用

,

0

KEY1

,按键

方波

、

k1

,

1

k1

所示

每按下一次,

k1

编程建立一个两位的二进制计数器

会相应加

1

三角波和锯齿波的波形数据在

、

Verilog HDL

初值为

有四种状态,每种状态对应一种波形,如表

正弦波

中存储的地址单元不同,如表

存器

应地址的转换来读取

据,从而完成波形选择的控制

序如下:

ROM

根据波形寄

2

语句完成不同波形对

中不同地址的波形数

波形计数器控制程

的四种状态,用

所示

ROM

case

。

。

k1

。

[

2

reg

:

]

k1

0

(

always @

制选择波形

;

/ /

波形选择计数器

negedge key1 or negedge reset

)

/ / KEY1

控

begin

100_000_000

( !

if

)

reset

;

k1< = 0

else

if

( !

(

key1&&

k6 = = 0

) )

begin

(

if

)

k1> = 4

;

k1< = 0

else

k1< = k1+1'd1

end

end

;

表 1 波形选择计数器状态对应表

k1

“00”

输入控制字 正弦波

“01” “10”

方波

三角波

“11”

锯齿波

表 2 ROM 中波形地址表

address

0-255

输入控制字 正弦波

256-511 512-767

三角波

方波

768-1023

锯齿波

图 2 Memory Initialization File 文件

�

第 5 期

陈亚军,陈隆道: 基于 Verilog HDL 的信号发生器的设计

725

3. 2 幅值调节控制

对输出波形幅值的调节是通过外围按键

FPGA

步减向

在程序工程中,用

二进制计数器

次,

相应减

k2

1。

k2

KEY2

输入波形幅值的控制信号来实现的

。

编程建立一个六位的

每按下一

,按键

KEY2

Verilog HDL

,初值为

50

根据公式:

(

)

1

data = data0* k2 /50

是直接从波形数据

其中,

data0

ROM

中送出的值,

转换的数据

该

数模转换芯片,

,所以

。

是幅值调节后最终送去

5 V

D / A

D / A

DAC0832

,根据式(

5 V

) ,按键

转换采用的是

,即输出参考电压为

data

设计

其电源电压最大为

5 V

输出波形最大幅值为

KEY2

每次步减是减少波形输出最大幅值的五十分之一,

因此,输出波形的幅值可调范围为

即步减

位二进制数构成,每次

,故幅值调节的精

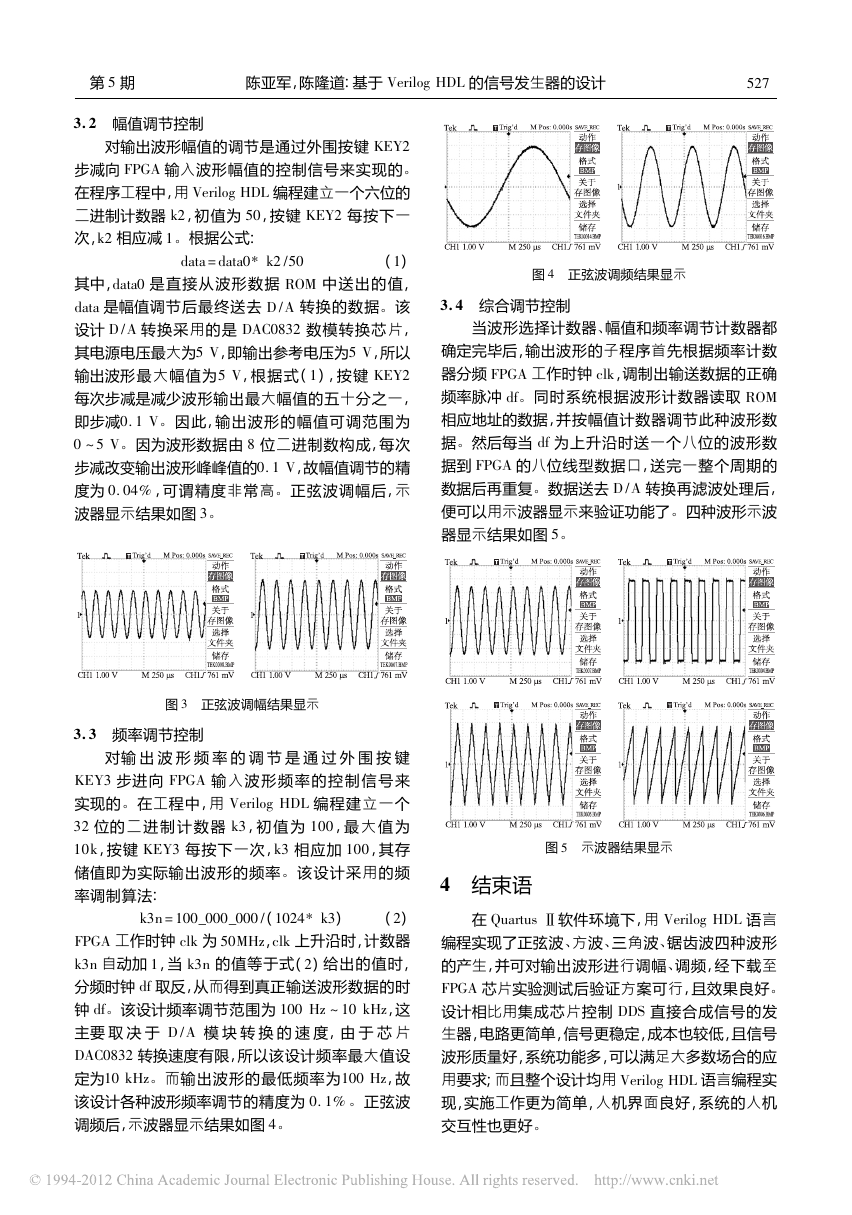

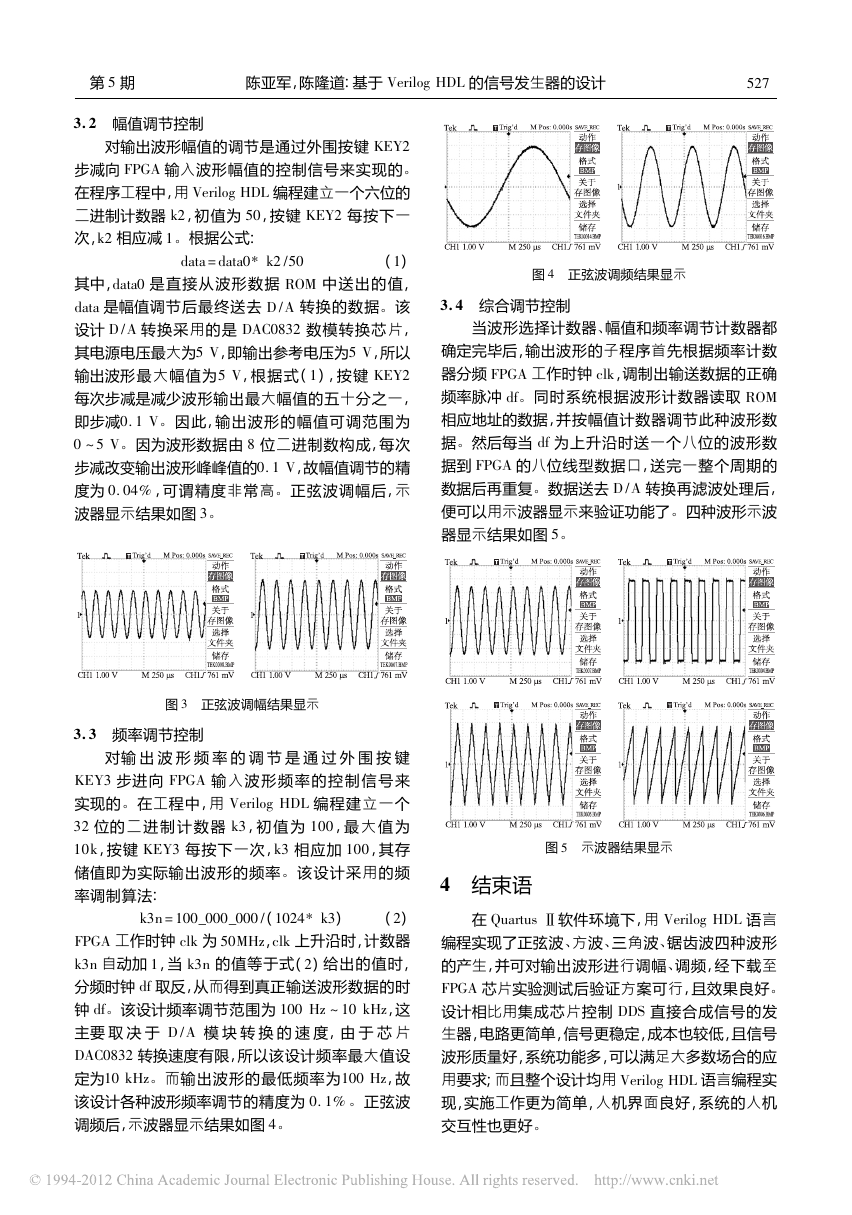

正弦波调幅后,示

0 ~ 5 V。

8

步减改变输出波形峰峰值的

度为

波器显示结果如图

,可谓精度非常高

因为波形数据由

0. 1 V。

0. 04%

0. 1 V

。

1

3。

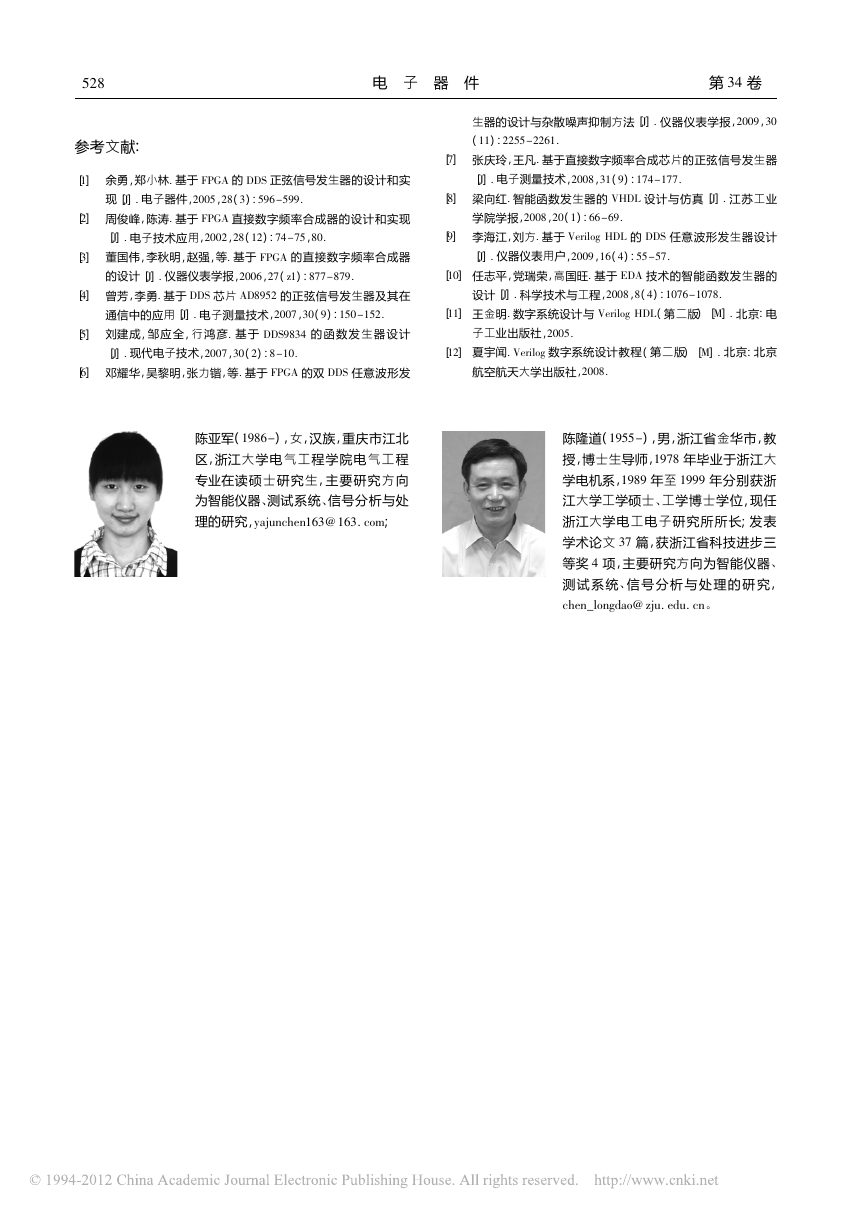

图 4 正弦波调频结果显示

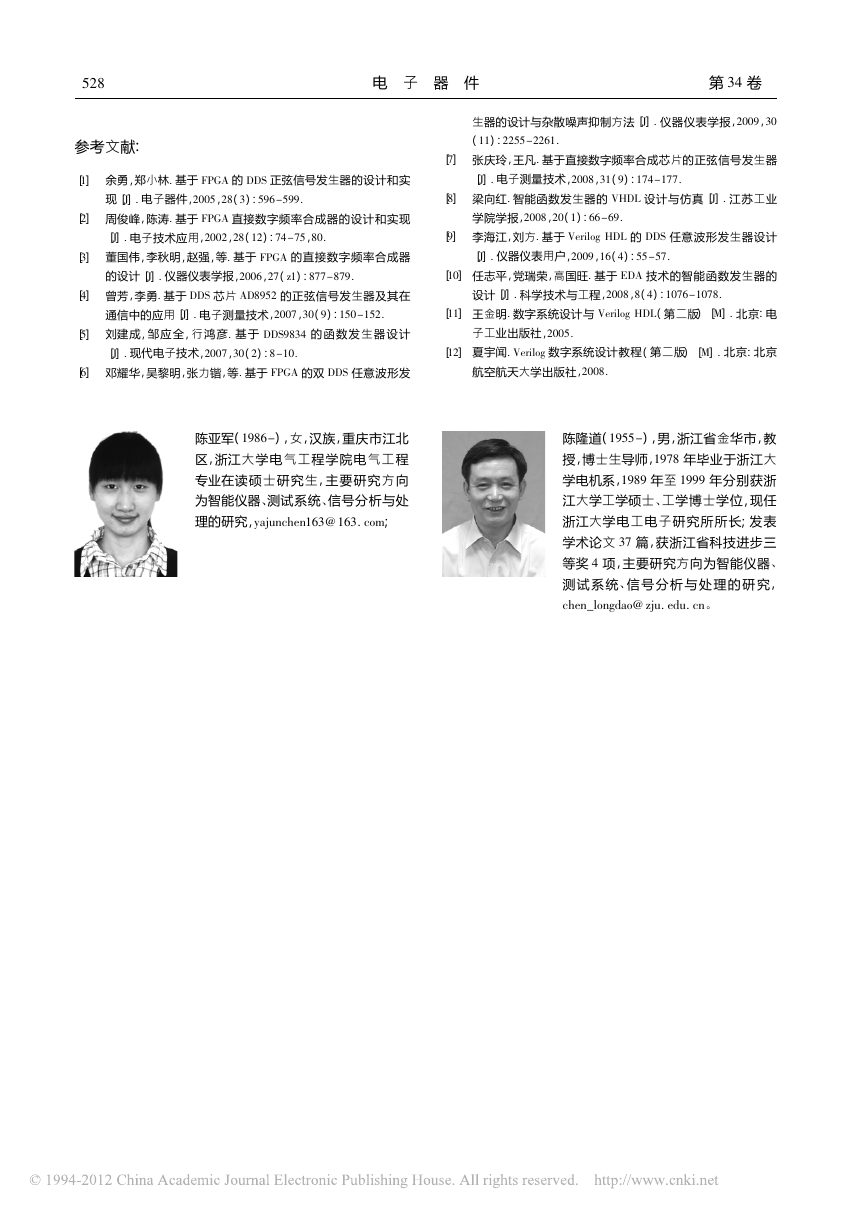

3. 4 综合调节控制

clk

df。

FPGA

当波形选择计数器

工作时钟

同时系统根据波形计数器读取

幅值和频率调节计数器都

、

确定完毕后,输出波形的子程序首先根据频率计数

,调制出输送数据的正确

器分频

频率脉冲

ROM

相应地址的数据,并按幅值计数器调节此种波形数

据

为上升沿时送一个八位的波形数

。

的八位线型数据口,送完一整个周期的

据到

转换再滤波处理后,

数据后再重复

便可以用示波器显示来验证功能了

四种波形示波

器显示结果如图

然后每当

数据送去

FPGA

D / A

。

。

df

5。

图 3 正弦波调幅结果显示

3. 3 频率调节控制

。

FPGA

步进向

KEY3

实现的

对输 出 波 形 频 率 的 调 节 是 通 过 外 围按 键

输入波形频率的控制信号来

编程建立一个

,最 大 值 为

100

,其存

相应加

该设计采用的频

在工程中,用

位的二 进 制 计 数 器

,按键

每按下一次,

10k

k3

储值即为实际输出波形的频率

率调制算法:

Verilog HDL

,初 值 为

KEY3

100

32

。

k3

(

)

2

2

df

为

clk

k3n

FPGA

自动加

1024* k3

k3n

分频时钟

钟

主要 取 决 于

k3n = 100_000_000 /

(

,

50MHz

clk

的值等于式(

)

上升沿时,计数器

工作时钟

) 给出的值时,

,当

1

取反,从而得到真正输送波形数据的时

,这

模 块 转 换 的 速 度,由 于 芯 片

转换速度有限,所以该设计频率最大值设

,故

正弦波

而输出波形的最低频率为

该设计频率调节范围为

100 Hz ~ 10 kHz

DAC0832

定为

该设计各种波形频率调节的精度为

调频后,示波器显示结果如图

10 kHz。

0. 1% 。

100 Hz

D / A

df。

4。

图 5 示波器结果显示

4 结束语

在

方波

、

软件环境下,用

语言

Quartus Ⅱ

Verilog HDL

编程实现了正弦波

锯齿波四种波形

三角波

、

、

的产生,并可对输出波形进行调幅

调频,经下载至

、

芯片实验测试后验证方案可行,且效果良好

FPGA

。

设计相比用集成芯片控制

直接合成信号的发

生器,电路更简单,信号更稳定,成本也较低,且信号

波形质量好,系统功能多,可以满足大多数场合的应

用要求; 而且整个设计均用

语言编程实

现,实施工作更为简单,人机界面良好,系统的人机

交互性也更好

Verilog HDL

DDS

。

�

825

参考文献:

电 子 器 件

生器的设计与杂散噪声抑制方法[

]

J

.

(

) :

11

2255-2261.

第 34 卷

仪器仪表学报,

2009

,

30

[

] 张庆玲,王凡

7

.

基于直接数字频率合成芯片的正弦信号发生器

正弦信号发生器的设计和实

]

[

J

.

电子测量技术,

,

31

智能函数发生器的

2008

(

) :

9

174-177.

VHDL

]

设计与仿真[

J

.

江苏工业

[

] 梁向红

8

.

学院学报,

[

] 李海江,刘方

9

.

2008

(

,

20

基于

) :

1

66-69.

Verilog HDL

(

]

[

J

.

仪器仪表用户,

2009

] 任志平,党瑞荣,高国旺

,

16

基于

科学技术与工程,

设计[

]

.

J

] 王金明

数字系统设计与

.

EDA

,

(

8

2008

[

10

[

11

Verilog HDL

.

子工业出版社,

任意波形发生器设计

DDS

的

) :

4

55-57.

技术的智能函数发生器的

4

) :

1076-1078.

( 第二版) [

M

]

.

北京: 电

[

] 夏宇闻

12

. Verilog

2005.

数字系统设计教程( 第二版) [

]

.

M

北京: 北京

航空航天大学出版社,

2008.

1999

1989

1955-

1978

年至

) ,男,浙江省金华市,教

陈隆道(

授,博士生导师,

年毕业于浙江大

学电机系,

年分别获浙

工学博士学位,现任

江大学工学硕士

、

浙江大学电工电子研究所所长; 发表

篇,获浙江省科技进步三

学术论文

项,主要研究方向为智能仪器

等奖

测试 系 统

、

信 号 分 析 与 处 理的 研 究 ,

37

4

、

chen_longdao@ zju. edu. cn。

[

] 余勇,郑小林

1

]

现[

J

.

.

基于

电子器件,

基于

FPGA

,

28

2005

的

(

3

DDS

) :

FPGA

[

] 周俊峰,陈涛

2

.

]

[

J

.

电子技术应用,

2002

[

] 董国伟,李秋明,赵强,等

3

]

的设计[

J

.

[

] 曾芳,李勇

4

仪器仪表学报,

基于

DDS

]

通信中的应用[

J

.

芯片

.

AD8952

电子测量技术,

2006

596-599.

(

) :

直接数字频率合成器的设计和实现

,

28

12

基于

,

80.

的直接数字频率合成器

) :

74-75

.

FPGA

(

,

27

z1

877-879.

的正弦信号发生器及其在

(

,

30

9

) :

150-152.

2007

的函数发生器设计

[

] 刘建成,邹应全,行鸿彦

5

.

,

30

[

] 邓耀华,吴黎明,张力锴,等

6

现代电子技术,

]

[

J

.

2007

.

基于

DDS9834

) :

8-10.

(

2

基于

FPGA

的双

DDS

任意波形发

1986-

陈亚军(

) ,女,汉族,重庆市江北

区,浙江大学电气工程学院电气工程

专业在读硕士研究生,主要研究方向

为智能仪器

信号分析与处

、

理的研究,

测试系统

、

yajunchen163@ 163. com

;

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc