007+2004821074(149259898)

015+zhengjunfe

031_yangyansky(287817962)

050+ywnwa(109264732)

067+chaosming(276907343)

084_suary(122757250)

115 dandan112

由衷感谢以上几位抽出宝贵的时间整理各模块的相关寄存器!

限于水平,整理过程中难免存在错误或不当之处,恳请大家批评指正。

在奋斗中前行!

事件管理器寄存器.................................................................................................2

GPIO MUX 寄存器 ...............................................................................................14

eCAN部分 .............................................................................................................18

WDRST 时钟、锁相环、看门狗和低功耗模式寄存器 ...................................33

片内外设的中断扩展(PIE)寄存器 .................................................................38

串行通信接口.......................................................................................................42

ADC模块相关寄存器............................................................................................46

SPI模块寄存器......................................................................................................54

1

�

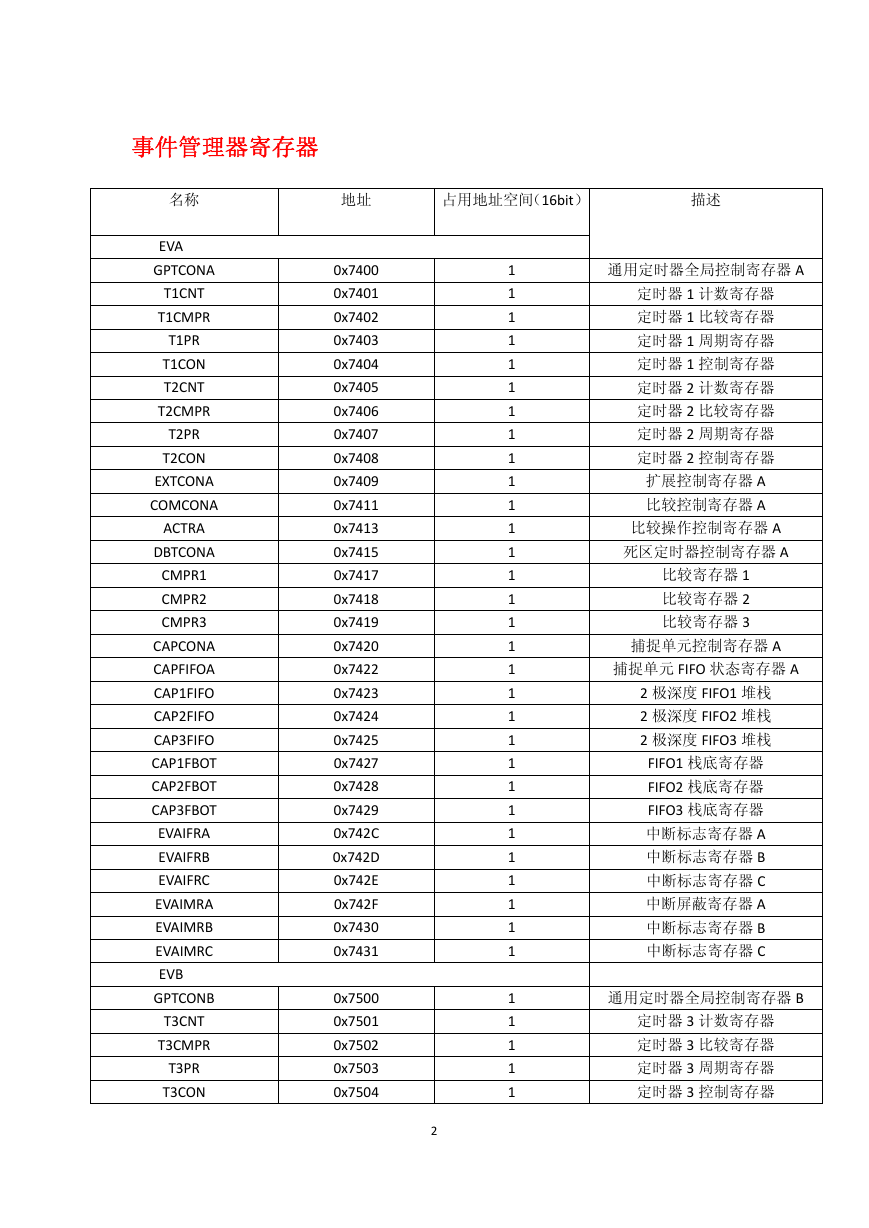

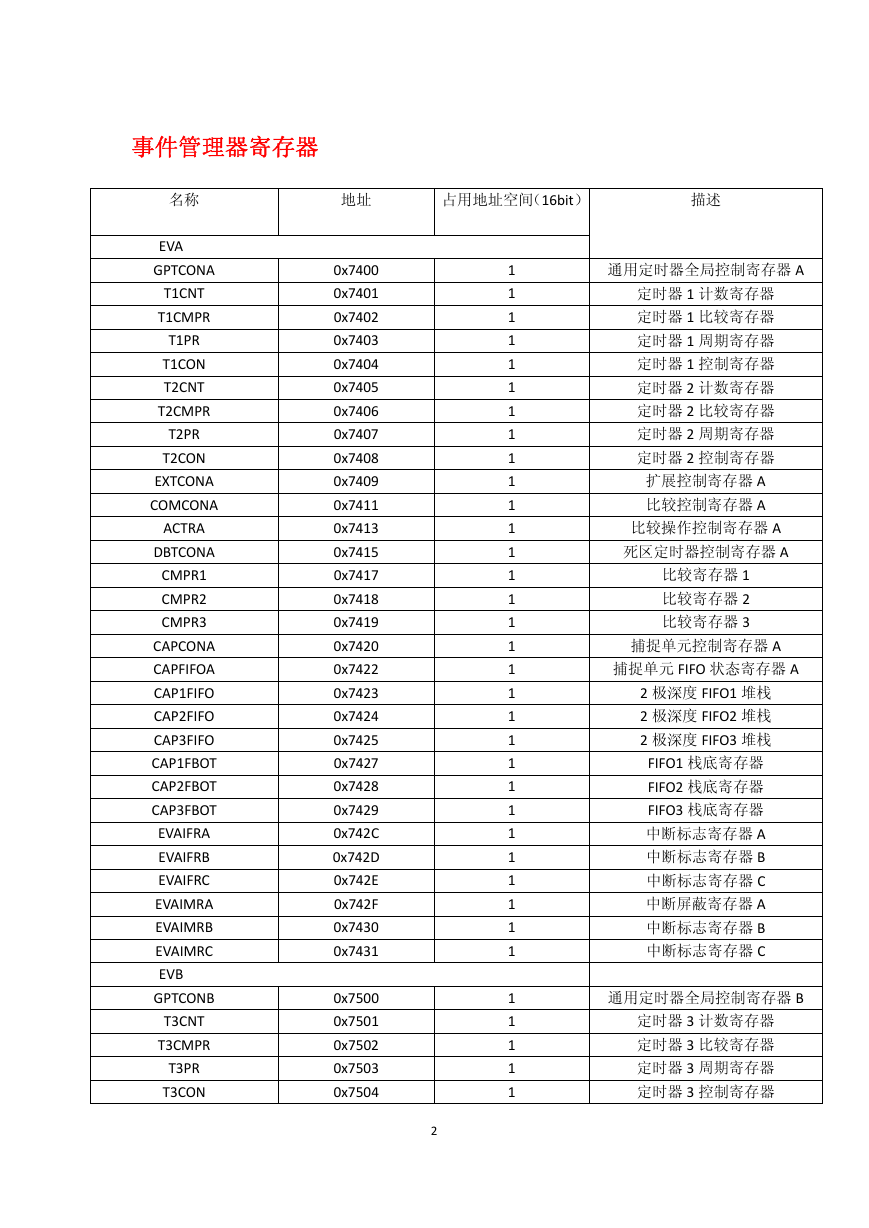

事件管理器寄存器

名称

EVA

地址

占用地址空间(16bit)

描述

GPTCONA

T1CNT

T1CMPR

T1PR

T1CON

T2CNT

T2CMPR

T2PR

T2CON

EXTCONA

COMCONA

ACTRA

DBTCONA

CMPR1

CMPR2

CMPR3

CAPCONA

CAPFIFOA

CAP1FIFO

CAP2FIFO

CAP3FIFO

CAP1FBOT

CAP2FBOT

CAP3FBOT

EVAIFRA

EVAIFRB

EVAIFRC

EVAIMRA

EVAIMRB

EVAIMRC

EVB

GPTCONB

T3CNT

T3CMPR

T3PR

T3CON

0x7400

0x7401

0x7402

0x7403

0x7404

0x7405

0x7406

0x7407

0x7408

0x7409

0x7411

0x7413

0x7415

0x7417

0x7418

0x7419

0x7420

0x7422

0x7423

0x7424

0x7425

0x7427

0x7428

0x7429

0x742C

0x742D

0x742E

0x742F

0x7430

0x7431

0x7500

0x7501

0x7502

0x7503

0x7504

2

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

通用定时器全局控制寄存器 A

定时器 1 计数寄存器

定时器 1 比较寄存器

定时器 1 周期寄存器

定时器 1 控制寄存器

定时器 2 计数寄存器

定时器 2 比较寄存器

定时器 2 周期寄存器

定时器 2 控制寄存器

扩展控制寄存器 A

比较控制寄存器 A

比较操作控制寄存器 A

死区定时器控制寄存器 A

比较寄存器 1

比较寄存器 2

比较寄存器 3

捕捉单元控制寄存器 A

捕捉单元 FIFO 状态寄存器 A

2 极深度 FIFO1 堆栈

2 极深度 FIFO2 堆栈

2 极深度 FIFO3 堆栈

FIFO1 栈底寄存器

FIFO2 栈底寄存器

FIFO3 栈底寄存器

中断标志寄存器 A

中断标志寄存器 B

中断标志寄存器 C

中断屏蔽寄存器 A

中断标志寄存器 B

中断标志寄存器 C

通用定时器全局控制寄存器 B

定时器 3 计数寄存器

定时器 3 比较寄存器

定时器 3 周期寄存器

定时器 3 控制寄存器

�

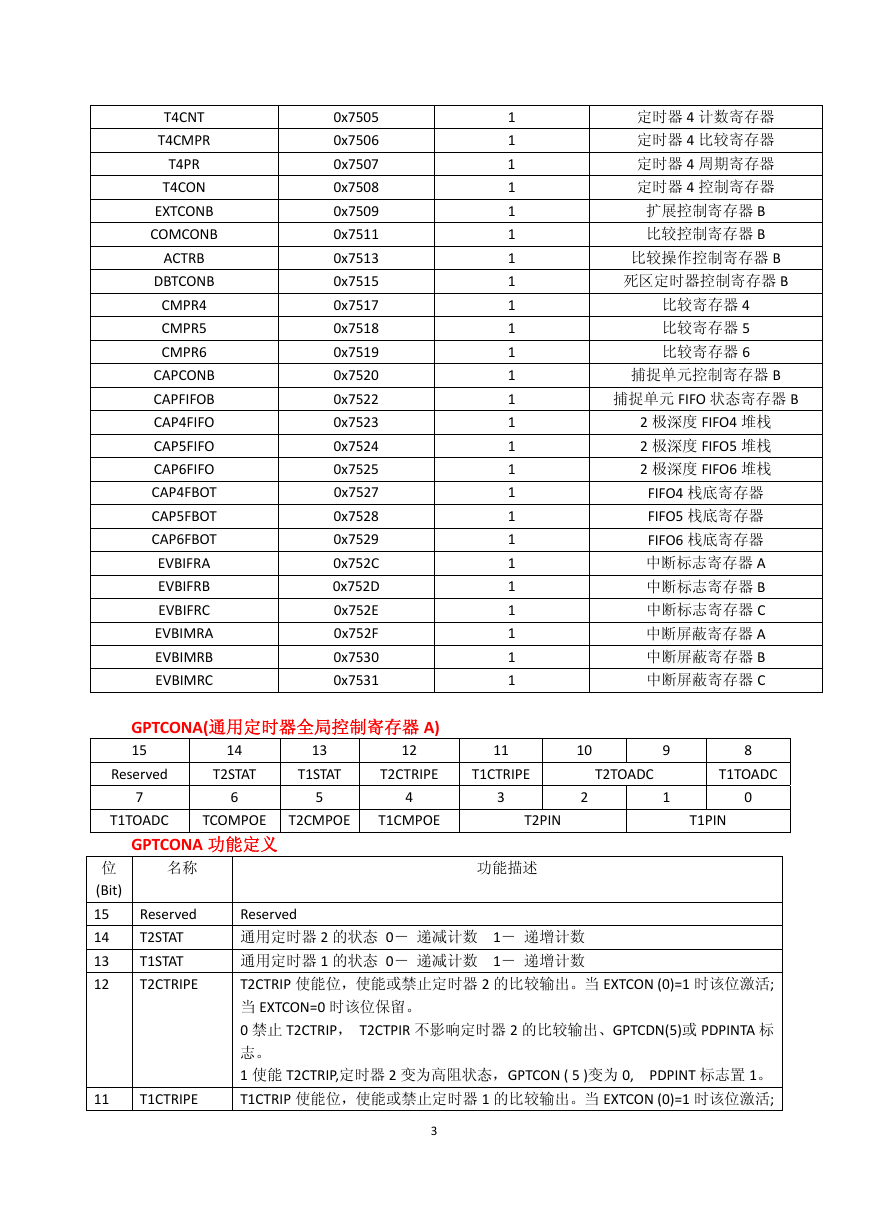

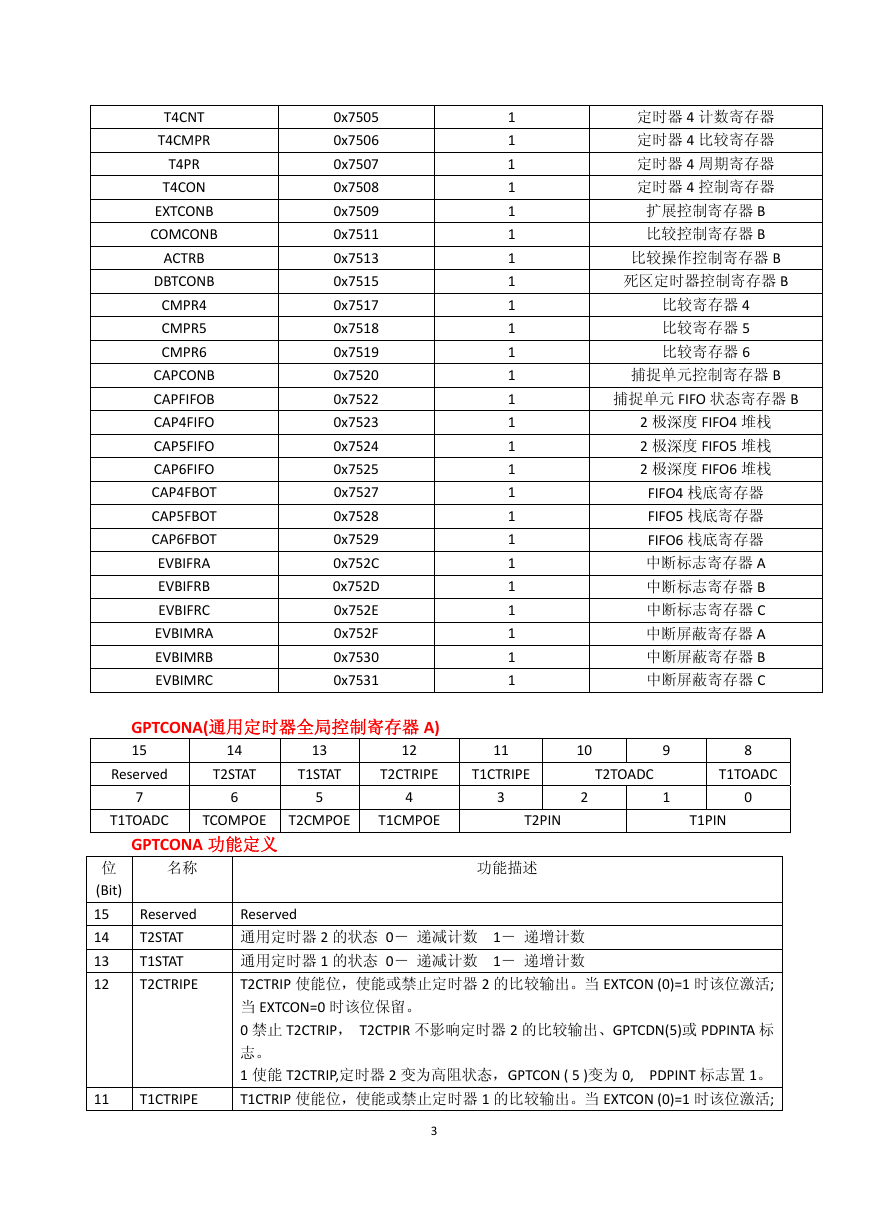

T4CNT

T4CMPR

T4PR

T4CON

EXTCONB

COMCONB

ACTRB

DBTCONB

CMPR4

CMPR5

CMPR6

CAPCONB

CAPFIFOB

CAP4FIFO

CAP5FIFO

CAP6FIFO

CAP4FBOT

CAP5FBOT

CAP6FBOT

EVBIFRA

EVBIFRB

EVBIFRC

EVBIMRA

EVBIMRB

EVBIMRC

0x7505

0x7506

0x7507

0x7508

0x7509

0x7511

0x7513

0x7515

0x7517

0x7518

0x7519

0x7520

0x7522

0x7523

0x7524

0x7525

0x7527

0x7528

0x7529

0x752C

0x752D

0x752E

0x752F

0x7530

0x7531

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

定时器 4 计数寄存器

定时器 4 比较寄存器

定时器 4 周期寄存器

定时器 4 控制寄存器

扩展控制寄存器 B

比较控制寄存器 B

比较操作控制寄存器 B

死区定时器控制寄存器 B

比较寄存器 4

比较寄存器 5

比较寄存器 6

捕捉单元控制寄存器 B

捕捉单元 FIFO 状态寄存器 B

2 极深度 FIFO4 堆栈

2 极深度 FIFO5 堆栈

2 极深度 FIFO6 堆栈

FIFO4 栈底寄存器

FIFO5 栈底寄存器

FIFO6 栈底寄存器

中断标志寄存器 A

中断标志寄存器 B

中断标志寄存器 C

中断屏蔽寄存器 A

中断屏蔽寄存器 B

中断屏蔽寄存器 C

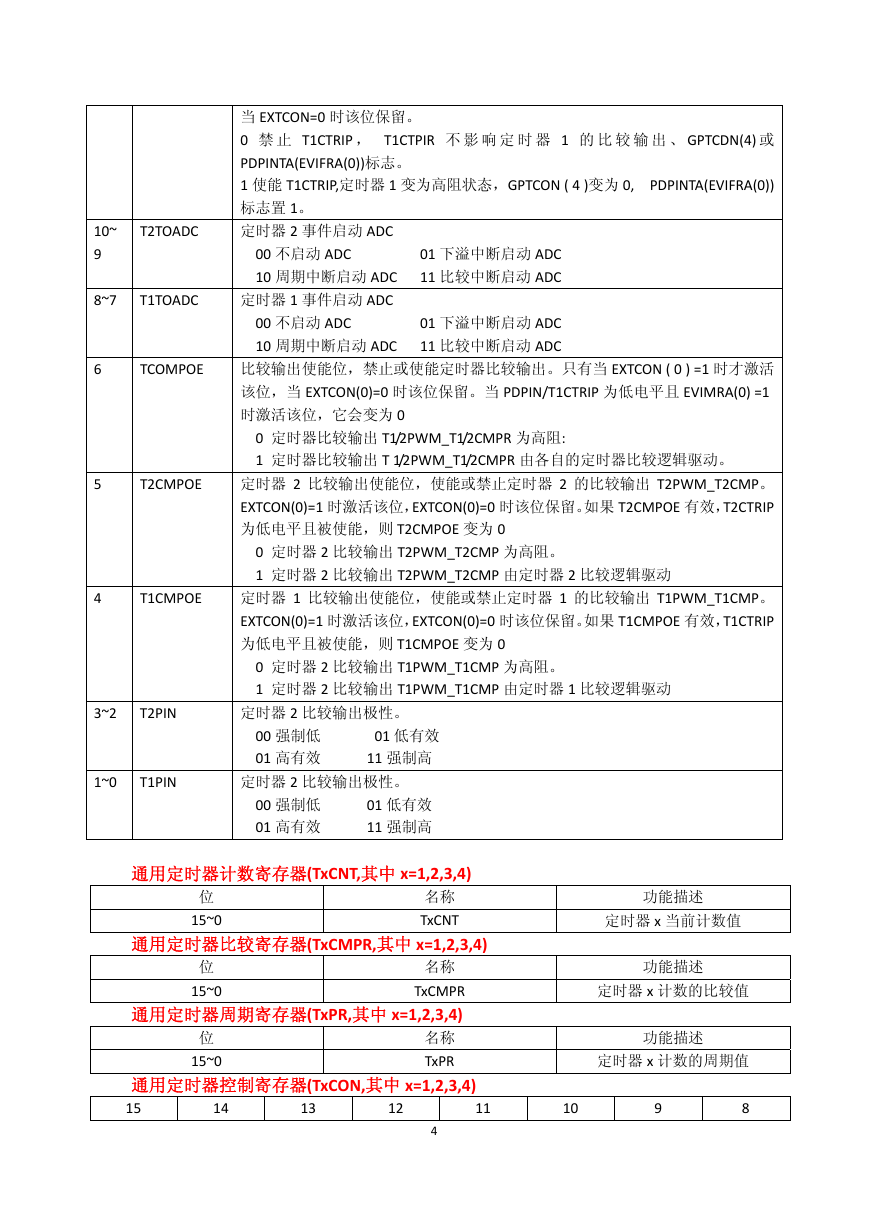

GPTCONA(通用定时器全局控制寄存器 A)

15

14

13

12

11

10

Reserved

T2STAT

T1STAT

T2CTRIPE

T1CTRIPE

T2TOADC

7

6

5

4

3

2

9

1

8

T1TOADC

0

T1TOADC

TCOMPOE

T2CMPOE

T1CMPOE

T2PIN

T1PIN

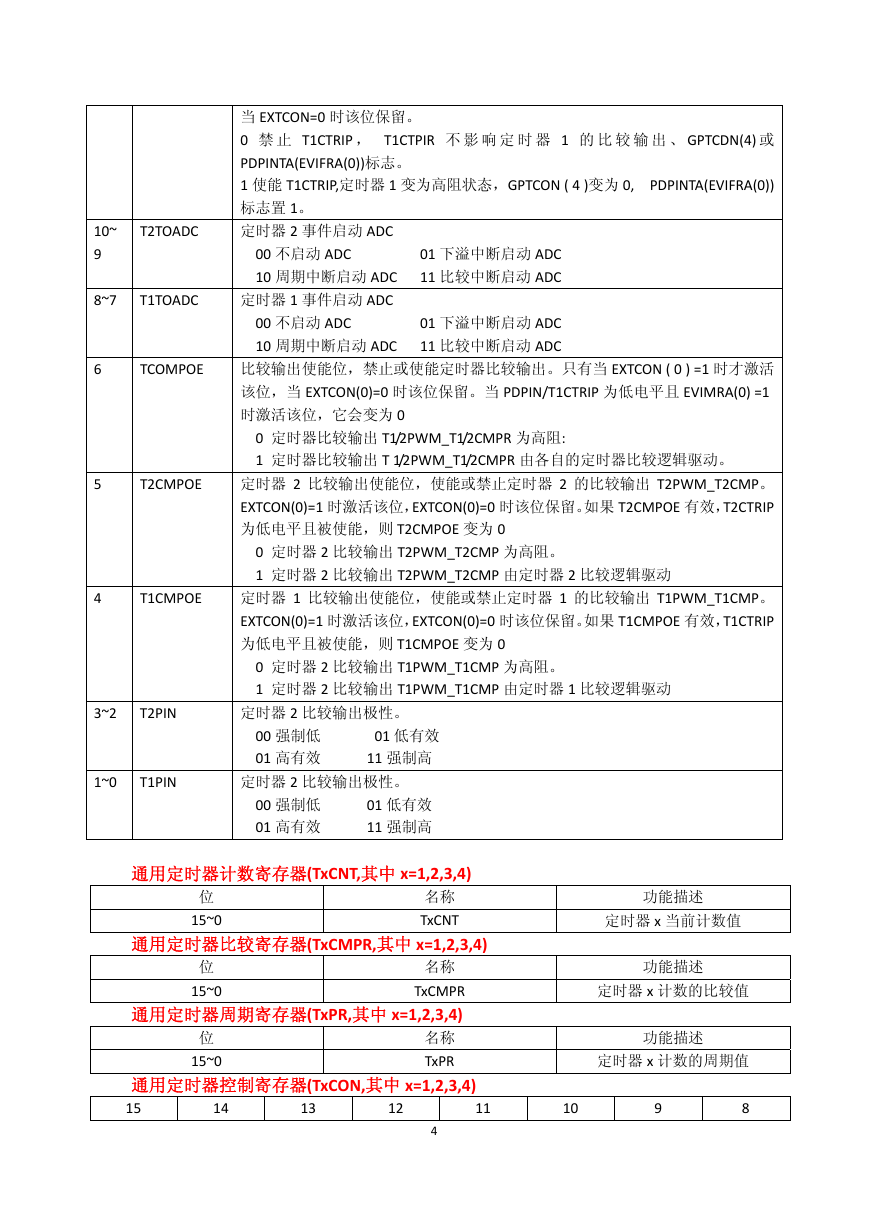

GPTCONA 功能定义

位

(Bit)

15

14

13

12

名称

Reserved

T2STAT

T1STAT

T2CTRIPE

11

T1CTRIPE

功能描述

Reserved

通用定时器 2 的状态 0- 递减计数 1- 递增计数

通用定时器 1 的状态 0- 递减计数 1- 递增计数

T2CTRIP 使能位,使能或禁止定时器 2 的比较输出。当 EXTCON (0)=1 时该位激活;

当 EXTCON=0 时该位保留。

0 禁止 T2CTRIP, T2CTPIR 不影响定时器 2 的比较输出、GPTCDN(5)或 PDPINTA 标

志。

1 使能 T2CTRIP,定时器 2 变为高阻状态,GPTCON ( 5 )变为 0, PDPINT 标志置 1。

T1CTRIP 使能位,使能或禁止定时器 1 的比较输出。当 EXTCON (0)=1 时该位激活;

3

�

当 EXTCON=0 时该位保留。

0 禁 止 T1CTRIP , T1CTPIR 不 影 响 定 时 器 1 的 比 较 输 出 、 GPTCDN(4) 或

PDPINTA(EVIFRA(0))标志。

1 使能 T1CTRIP,定时器 1 变为高阻状态,GPTCON ( 4 )变为 0, PDPINTA(EVIFRA(0))

标志置 1。

定时器 2 事件启动 ADC

00 不启动 ADC 01 下溢中断启动 ADC

10 周期中断启动 ADC 11 比较中断启动 ADC

定时器 1 事件启动 ADC

00 不启动 ADC 01 下溢中断启动 ADC

10 周期中断启动 ADC 11 比较中断启动 ADC

比较输出使能位,禁止或使能定时器比较输出。只有当 EXTCON ( 0 ) =1 时才激活

该位,当 EXTCON(0)=0 时该位保留。当 PDPIN/T1CTRIP 为低电平且 EVIMRA(0) =1

时激活该位,它会变为 0

0 定时器比较输出 T1/2PWM_T1/2CMPR 为高阻:

1 定时器比较输出 T 1/2PWM_T1/2CMPR 由各自的定时器比较逻辑驱动。

定时器 2 比较输出使能位,使能或禁止定时器 2 的比较输出 T2PWM_T2CMP。

EXTCON(0)=1 时激活该位,EXTCON(0)=0 时该位保留。如果 T2CMPOE 有效,T2CTRIP

为低电平且被使能,则 T2CMPOE 变为 0

0 定时器 2 比较输出 T2PWM_T2CMP 为高阻。

1 定时器 2 比较输出 T2PWM_T2CMP 由定时器 2 比较逻辑驱动

定时器 1 比较输出使能位,使能或禁止定时器 1 的比较输出 T1PWM_T1CMP。

EXTCON(0)=1 时激活该位,EXTCON(0)=0 时该位保留。如果 T1CMPOE 有效,T1CTRIP

为低电平且被使能,则 T1CMPOE 变为 0

0 定时器 2 比较输出 T1PWM_T1CMP 为高阻。

1 定时器 2 比较输出 T1PWM_T1CMP 由定时器 1 比较逻辑驱动

定时器 2 比较输出极性。

00 强制低 01 低有效

01 高有效 11 强制高

定时器 2 比较输出极性。

00 强制低 01 低有效

01 高有效 11 强制高

T2TOADC

10~

9

8~7

T1TOADC

6

TCOMPOE

5

T2CMPOE

4

T1CMPOE

3~2

T2PIN

1~0

T1PIN

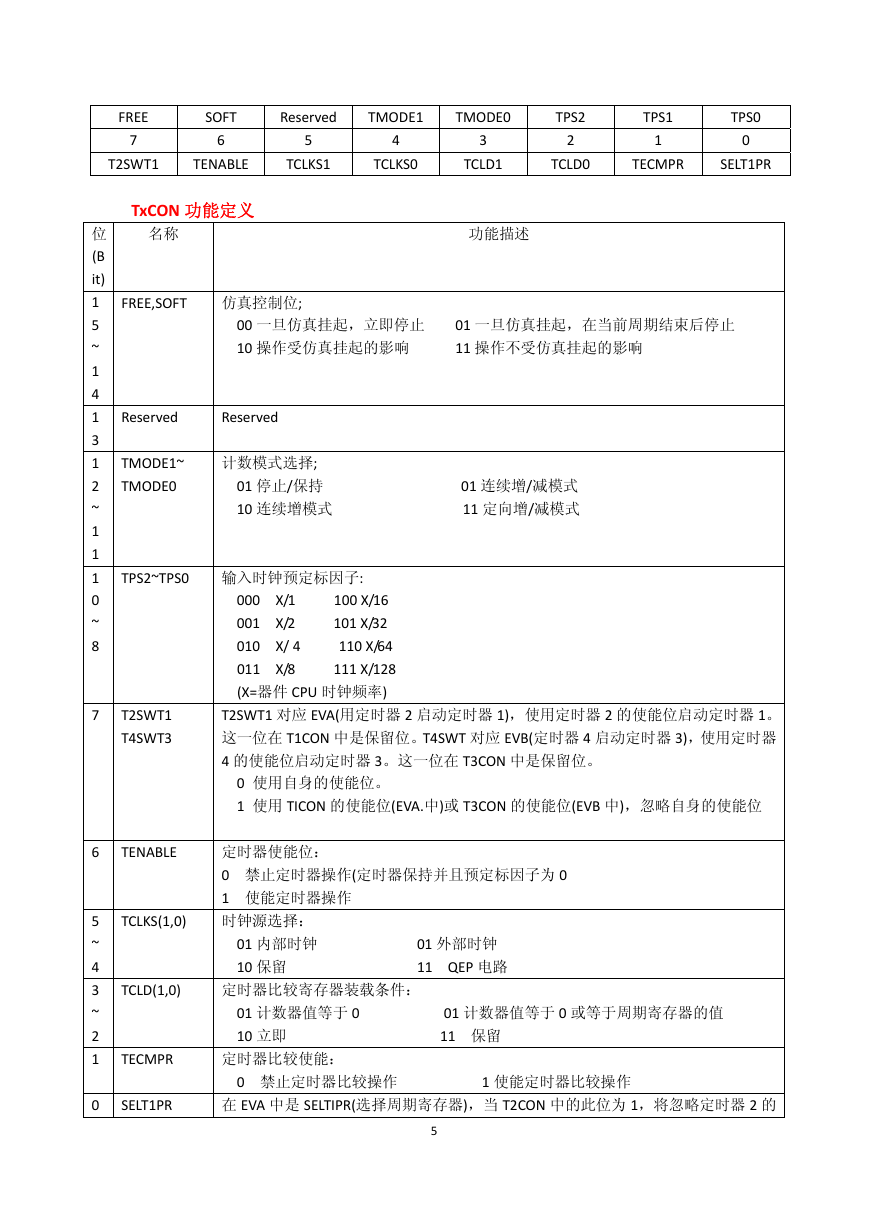

通用定时器计数寄存器(TxCNT,其中 x=1,2,3,4)

位

15~0

名称

TxCNT

通用定时器比较寄存器(TxCMPR,其中 x=1,2,3,4)

位

15~0

TxCMPR

通用定时器周期寄存器(TxPR,其中 x=1,2,3,4)

名称

TxPR

位

15~0

名称

通用定时器控制寄存器(TxCON,其中 x=1,2,3,4)

15

14

11

13

12

4

功能描述

定时器 x 当前计数值

功能描述

定时器 x 计数的比较值

功能描述

定时器 x 计数的周期值

10

9

8

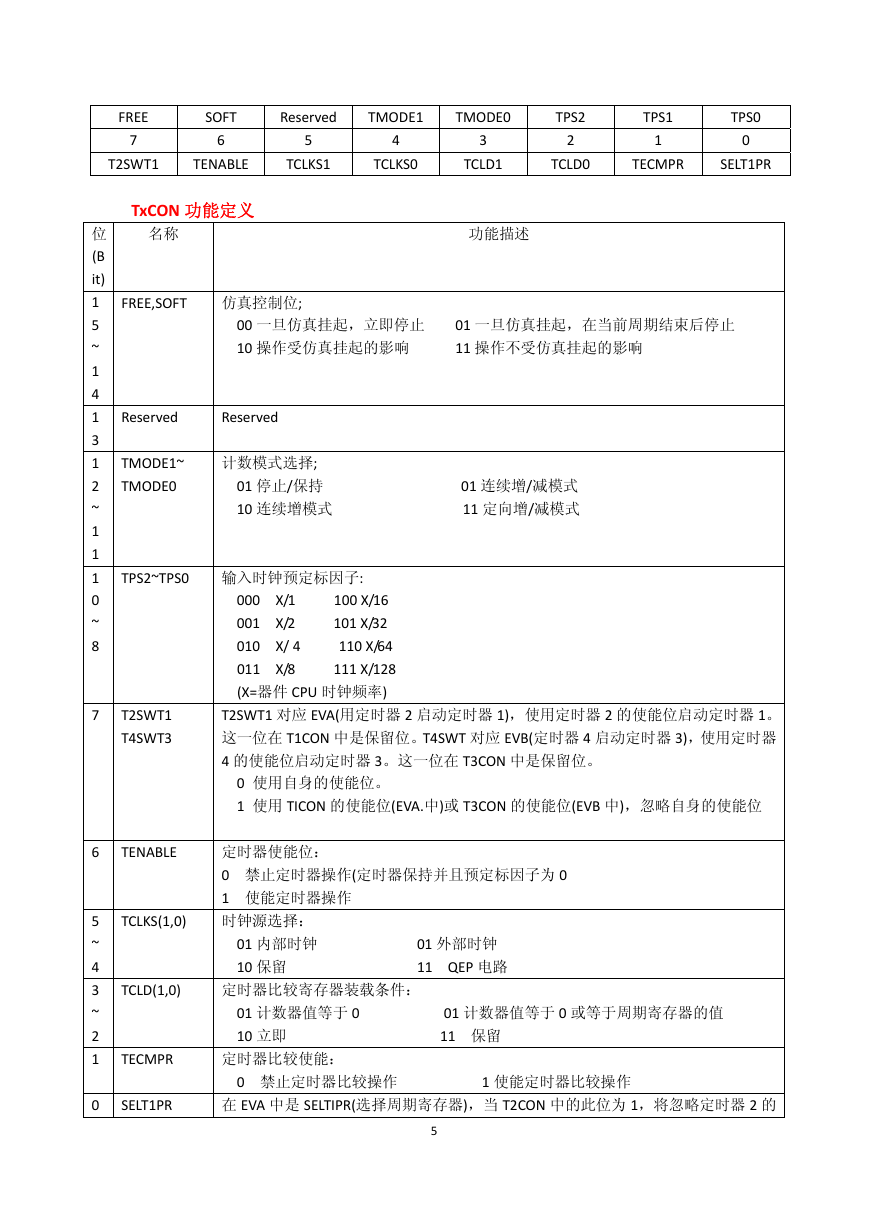

�

FREE

7

SOFT

6

Reserved

TMODE1

TMODE0

5

4

3

T2SWT1

TENABLE

TCLKS1

TCLKS0

TCLD1

TPS2

2

TCLD0

TPS1

1

TPS0

0

TECMPR

SELT1PR

TxCON 功能定义

名称

功能描述

FREE,SOFT

仿真控制位;

00 一旦仿真挂起,立即停止 01 一旦仿真挂起,在当前周期结束后停止

10 操作受仿真挂起的影响 11 操作不受仿真挂起的影响

Reserved

Reserved

TMODE1~

TMODE0

计数模式选择;

01 停止/保持 01 连续增/减模式

10 连续增模式 11 定向增/减模式

TPS2~TPS0 输入时钟预定标因子:

位

(B

it)

1

5

~

1

4

1

3

1

2

~

1

1

1

0

~

8

7

000 X/1 100 X/16

001 X/2 101 X/32

010 X/ 4 110 X/64

011 X/8 111 X/128

(X=器件 CPU 时钟频率)

T2SWT1 对应 EVA(用定时器 2 启动定时器 1),使用定时器 2 的使能位启动定时器 1。

这一位在 T1CON 中是保留位。T4SWT 对应 EVB(定时器 4 启动定时器 3),使用定时器

4 的使能位启动定时器 3。这一位在 T3CON 中是保留位。

0 使用自身的使能位。

1 使用 TICON 的使能位(EVA.中)或 T3CON 的使能位(EVB 中),忽略自身的使能位

定时器使能位:

0 禁止定时器操作(定时器保持并且预定标因子为 0

1 使能定时器操作

时钟源选择:

01 内部时钟 01 外部时钟

10 保留 11 QEP 电路

定时器比较寄存器装载条件:

01 计数器值等于 0 01 计数器值等于 0 或等于周期寄存器的值

10 立即 11 保留

定时器比较使能:

0 禁止定时器比较操作 1 使能定时器比较操作

在 EVA 中是 SELTIPR(选择周期寄存器),当 T2CON 中的此位为 1,将忽略定时器 2 的

5

T2SWT1

T4SWT3

6

TENABLE

5

~

4

3

~

2

1

0

TCLKS(1,0)

TCLD(1,0)

TECMPR

SELT1PR

�

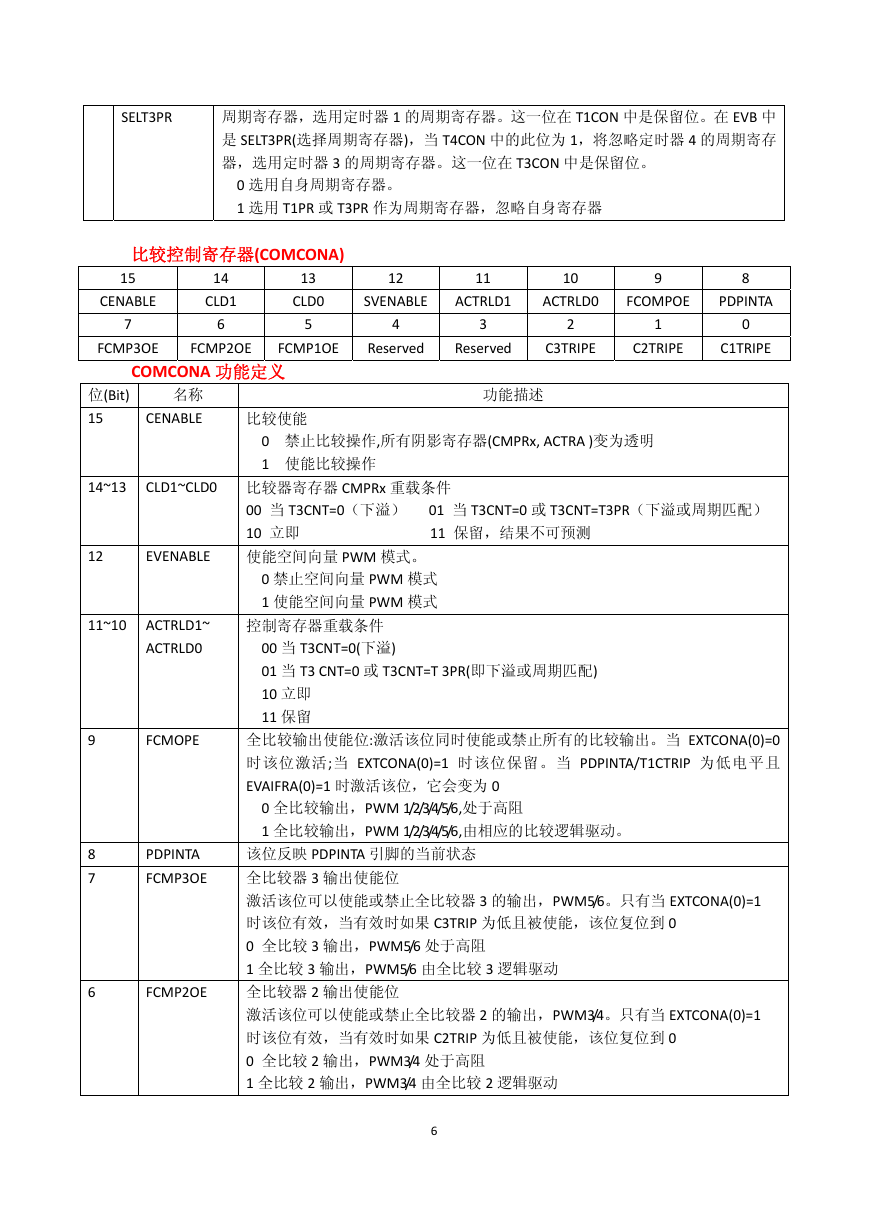

SELT3PR

周期寄存器,选用定时器 1 的周期寄存器。这一位在 T1CON 中是保留位。在 EVB 中

是 SELT3PR(选择周期寄存器),当 T4CON 中的此位为 1,将忽略定时器 4 的周期寄存

器,选用定时器 3 的周期寄存器。这一位在 T3CON 中是保留位。

0 选用自身周期寄存器。

1 选用 T1PR 或 T3PR 作为周期寄存器,忽略自身寄存器

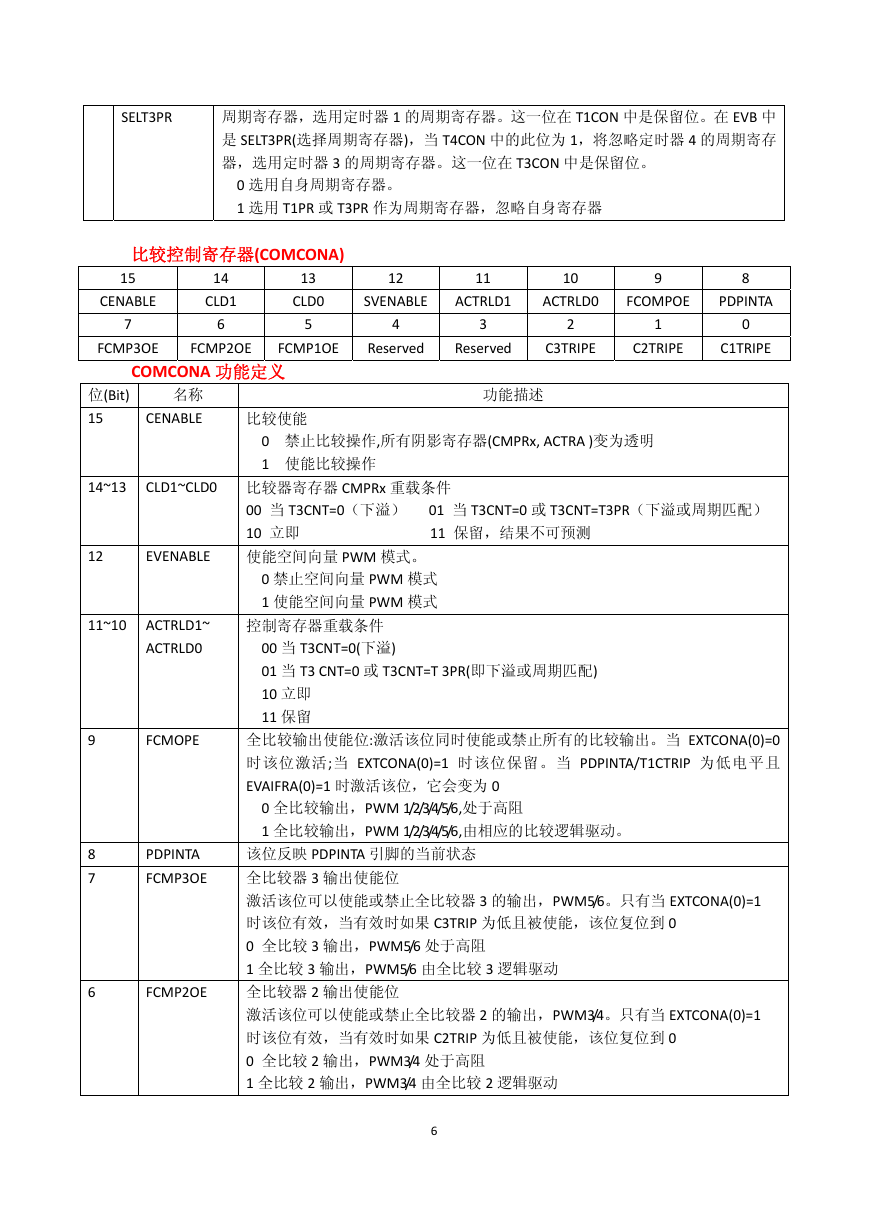

比较控制寄存器(COMCONA)

15

CENABLE

7

14

CLD1

6

13

CLD0

5

12

11

10

9

8

SVENABLE

ACTRLD1

ACTRLD0

FCOMPOE

PDPINTA

4

3

2

1

0

FCMP3OE

FCMP2OE

FCMP1OE

Reserved

Reserved

C3TRIPE

C2TRIPE

C1TRIPE

COMCONA 功能定义

位(Bit)

15

名称

CENABLE

功能描述

比较使能

0 禁止比较操作,所有阴影寄存器(CMPRx, ACTRA )变为透明

1 使能比较操作

14~13 CLD1~CLD0 比较器寄存器 CMPRx 重载条件

12

EVENABLE

11~10 ACTRLD1~

ACTRLD0

9

FCMOPE

8

7

PDPINTA

FCMP3OE

6

FCMP2OE

00 当 T3CNT=0(下溢) 01 当 T3CNT=0 或 T3CNT=T3PR(下溢或周期匹配)

10 立即 11 保留,结果不可预测

使能空间向量 PWM 模式。

0 禁止空间向量 PWM 模式

1 使能空间向量 PWM 模式

控制寄存器重载条件

00 当 T3CNT=0(下溢)

01 当 T3 CNT=0 或 T3CNT=T 3PR(即下溢或周期匹配)

10 立即

11 保留

全比较输出使能位:激活该位同时使能或禁止所有的比较输出。当 EXTCONA(0)=0

时该位激活;当 EXTCONA(0)=1 时该位保留。当 PDPINTA/T1CTRIP 为低电平且

EVAIFRA(0)=1 时激活该位,它会变为 0

0 全比较输出,PWM 1/2/3/4/5/6,处于高阻

1 全比较输出,PWM 1/2/3/4/5/6,由相应的比较逻辑驱动。

该位反映 PDPINTA 引脚的当前状态

全比较器 3 输出使能位

激活该位可以使能或禁止全比较器 3 的输出,PWM5/6。只有当 EXTCONA(0)=1

时该位有效,当有效时如果 C3TRIP 为低且被使能,该位复位到 0

0 全比较 3 输出,PWM5/6 处于高阻

1 全比较 3 输出,PWM5/6 由全比较 3 逻辑驱动

全比较器 2 输出使能位

激活该位可以使能或禁止全比较器 2 的输出,PWM3/4。只有当 EXTCONA(0)=1

时该位有效,当有效时如果 C2TRIP 为低且被使能,该位复位到 0

0 全比较 2 输出,PWM3/4 处于高阻

1 全比较 2 输出,PWM3/4 由全比较 2 逻辑驱动

6

�

5

FCMP1OE

4~3

2

Reserved

C3TRIPE

1

C2TRIPE

0

C1TRIPE

全比较器 1 输出使能位

激活该位可以使能或禁止全比较器 1 的输出,PWM1/2。只有当 EXTCONA(0)=1

时该位有效,当有效时如果 C1TRIP 为低且被使能,该位复位到 0

0 全比较 1 输出,PWM1/2 处于高阻

1 全比较 1 输出,PWM1/2 由全比较 1 逻辑驱动

Reserved

全比较器 3 输出切换使能位

激活该位可以使能或禁止全比较器 3 的输出关闭功能。只有当 EXTCONA(0)=0

时该位有效,当 EXTCONA(0)=1 时该位保留

0 完全比较器 3 的输出关闭功能被禁止,C3TRIP 状态不影响比较器 3 的输出、

COMCONA(8)以及 PDPINTA 标志(EVAIFRA(0))

1 完全比较器 3 的输出关闭功能被使能,当 T3TRIP 是低时,完全比较器 3 的两

个输出引脚输出高阻状态,COMCONA(8)复位为 0,并且 PDPINTA 的标志置 1

全比较器 2 输出切换使能位

激活该位可以使能或禁止全比较器 3 的输出关闭功能。只有当 EXTCONA(0)=0

时该位有效,当 EXTCONA(0)=1 时该位保留

0 完全比较器 2 的输出关闭功能被禁止,C2TRIP 状态不影响比较器 2 的输出、

COMCONA(7)以及 PDPINTA 标志(EVAIFRA(0))

1 完全比较器 2 的输出关闭功能被使能,当 T2TRIP 是低时,完全比较器 2 的两

个输出引脚输出高阻状态,COMCONA(7)复位为 0,并且 PDPINTA 的标志置 1

全比较器 1 输出切换使能位

激活该位可以使能或禁止全比较器 1 的输出关闭功能。只有当 EXTCONA(0)=0

时该位有效,当 EXTCONA(0)=1 时该位保留

0 完全比较器 1 的输出关闭功能被禁止,C1TRIP 状态不影响比较器 1 的输出、

COMCONA(6)以及 PDPINTA 标志(EVAIFRA(0))

1 完全比较器 1 的输出关闭功能被使能,当 T1TRIP 是低时,完全比较器 1 的两

个输出引脚输出高阻状态,COMCONA(6)复位为 0,并且 PDPINTA 的标志置 1

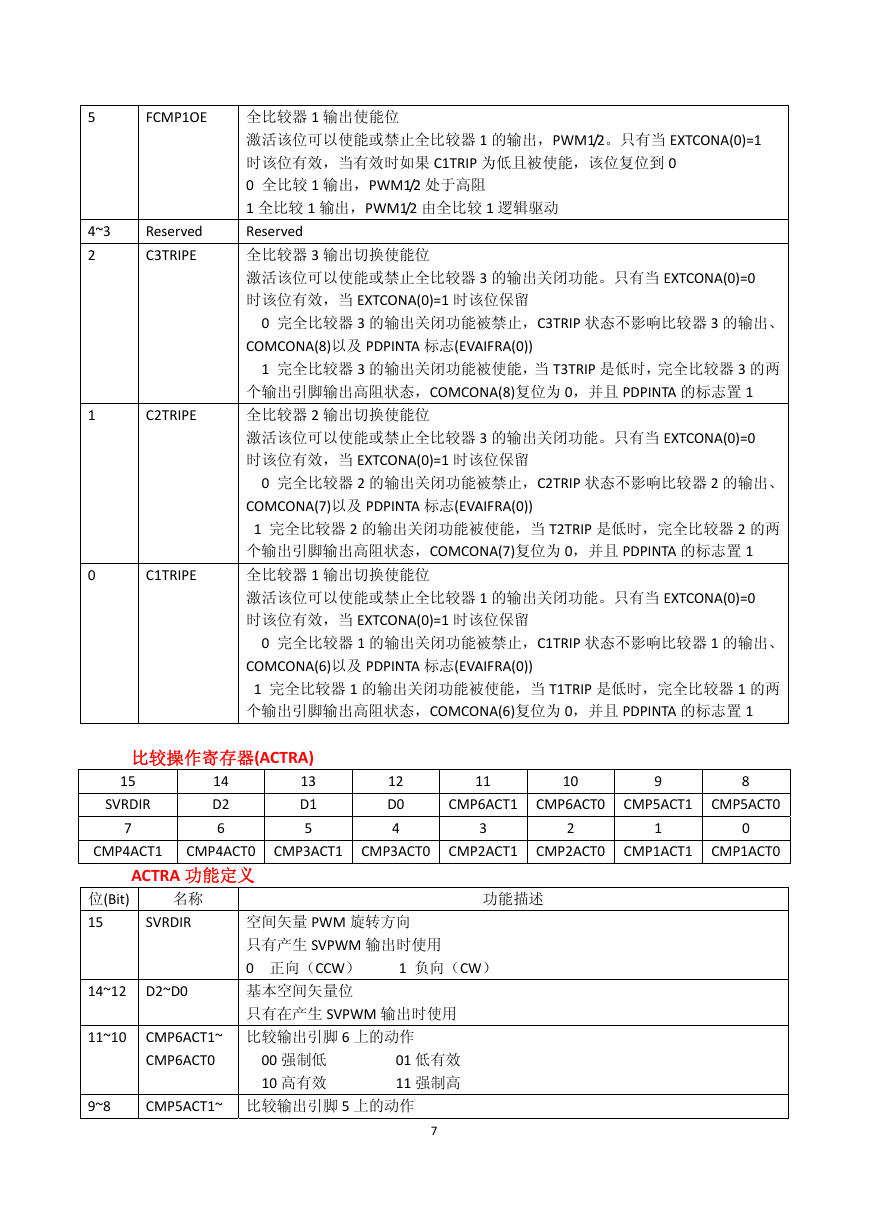

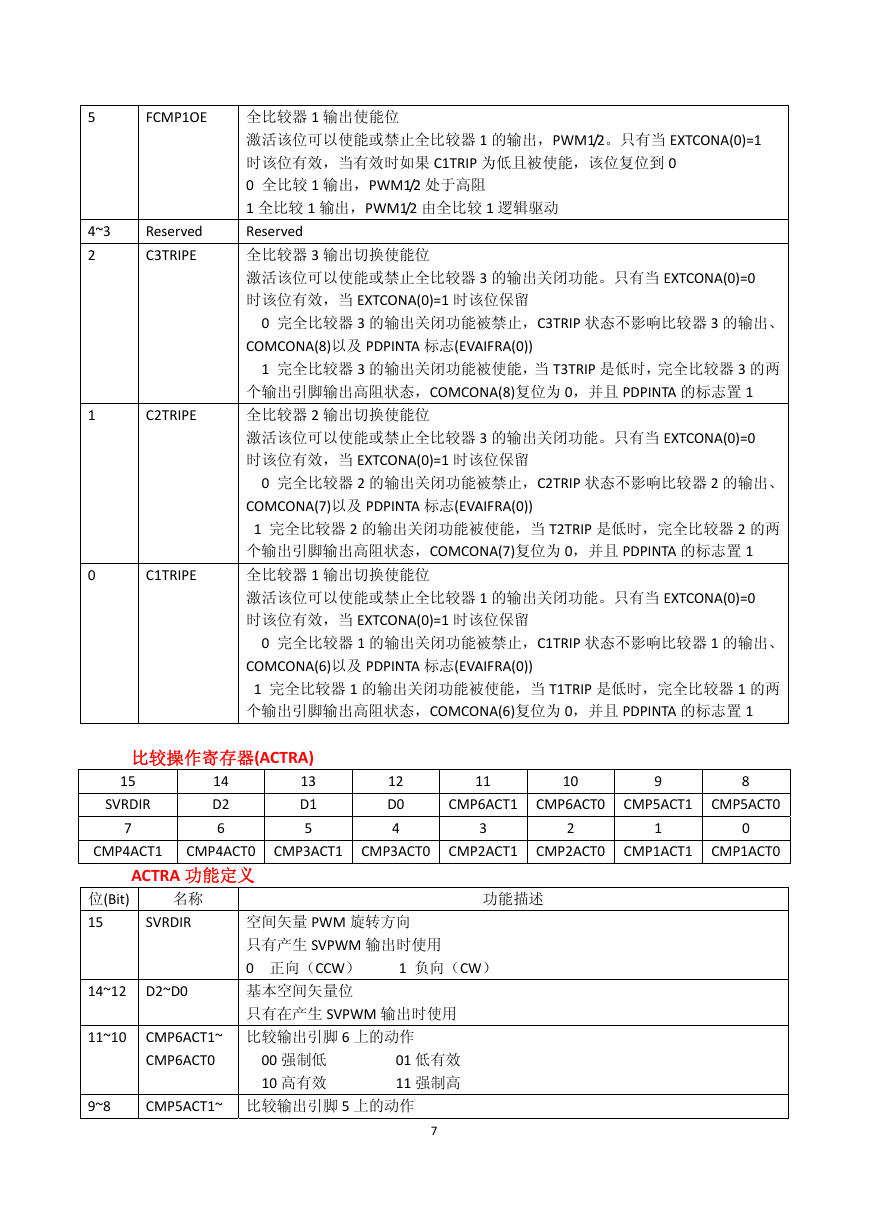

比较操作寄存器(ACTRA)

13

D1

5

14

D2

6

SVRDIR

15

7

12

D0

4

11

10

9

8

CMP6ACT1

CMP6ACT0

CMP5ACT1 CMP5ACT0

3

2

1

0

CMP4ACT1

CMP4ACT0

ACTRA 功能定义

CMP3ACT1 CMP3ACT0

CMP2ACT1

CMP2ACT0

CMP1ACT1 CMP1ACT0

位(Bit)

15

名称

SVRDIR

14~12 D2~D0

11~10 CMP6ACT1~

CMP6ACT0

功能描述

空间矢量 PWM 旋转方向

只有产生 SVPWM 输出时使用

0 正向(CCW) 1 负向(CW)

基本空间矢量位

只有在产生 SVPWM 输出时使用

比较输出引脚 6 上的动作

00 强制低 01 低有效

10 高有效 11 强制高

9~8

CMP5ACT1~ 比较输出引脚 5 上的动作

7

�

CMP5ACT0

CMP4ACT1~

CMP4ACT0

CMP3ACT1~

CMP3ACT0

CMP2ACT1~

CMP2ACT0

7~6

5~4

3~2

1~0

CMP1ACT1~

CMP1ACT0

00 强制低 01 低有效

10 高有效 11 强制高

比较输出引脚 4 上的动作

00 强制低 01 低有效

10 高有效 11 强制高

比较输出引脚 3 上的动作

00 强制低 01 低有效

10 高有效 11 强制高

比较输出引脚 2 上的动作

00 强制低 01 低有效

10 高有效 11 强制高

比较输出引脚 1 上的动作

00 强制低 01 低有效

10 高有效 11 强制高

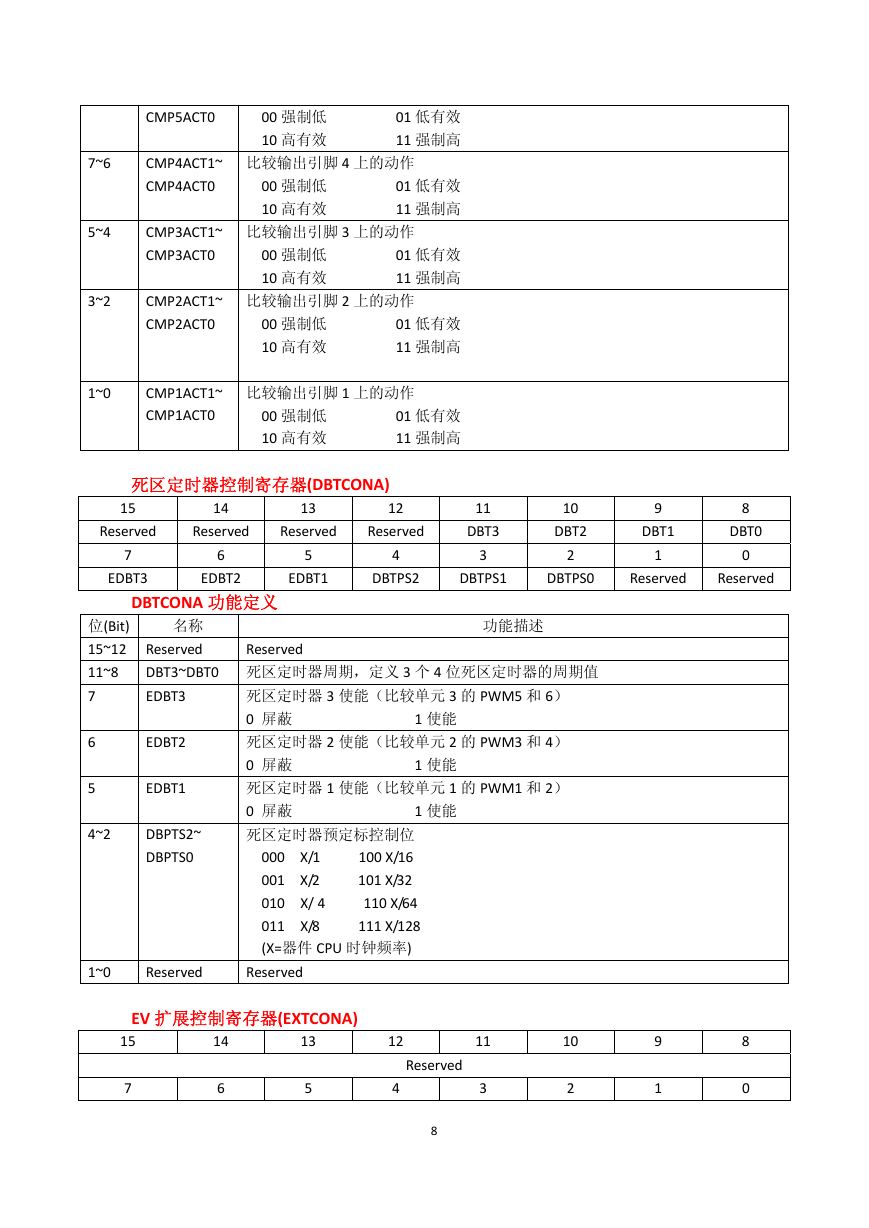

死区定时器控制寄存器(DBTCONA)

15

14

13

12

Reserved

Reserved

Reserved

Reserved

6

5

4

11

DBT3

3

10

DBT2

2

9

DBT1

1

8

DBT0

0

EDBT2

EDBT1

DBTPS2

DBTPS1

DBTPS0

Reserved

Reserved

DBTCONA 功能定义

7

EDBT3

名称

位(Bit)

15~12 Reserved

11~8

7

6

5

4~2

EDBT2

EDBT1

DBPTS2~

DBPTS0

1~0

Reserved

Reserved

功能描述

DBT3~DBT0 死区定时器周期,定义 3 个 4 位死区定时器的周期值

EDBT3

死区定时器 3 使能(比较单元 3 的 PWM5 和 6)

0 屏蔽 1 使能

死区定时器 2 使能(比较单元 2 的 PWM3 和 4)

0 屏蔽 1 使能

死区定时器 1 使能(比较单元 1 的 PWM1 和 2)

0 屏蔽 1 使能

死区定时器预定标控制位

000 X/1 100 X/16

001 X/2 101 X/32

010 X/ 4 110 X/64

011 X/8 111 X/128

(X=器件 CPU 时钟频率)

Reserved

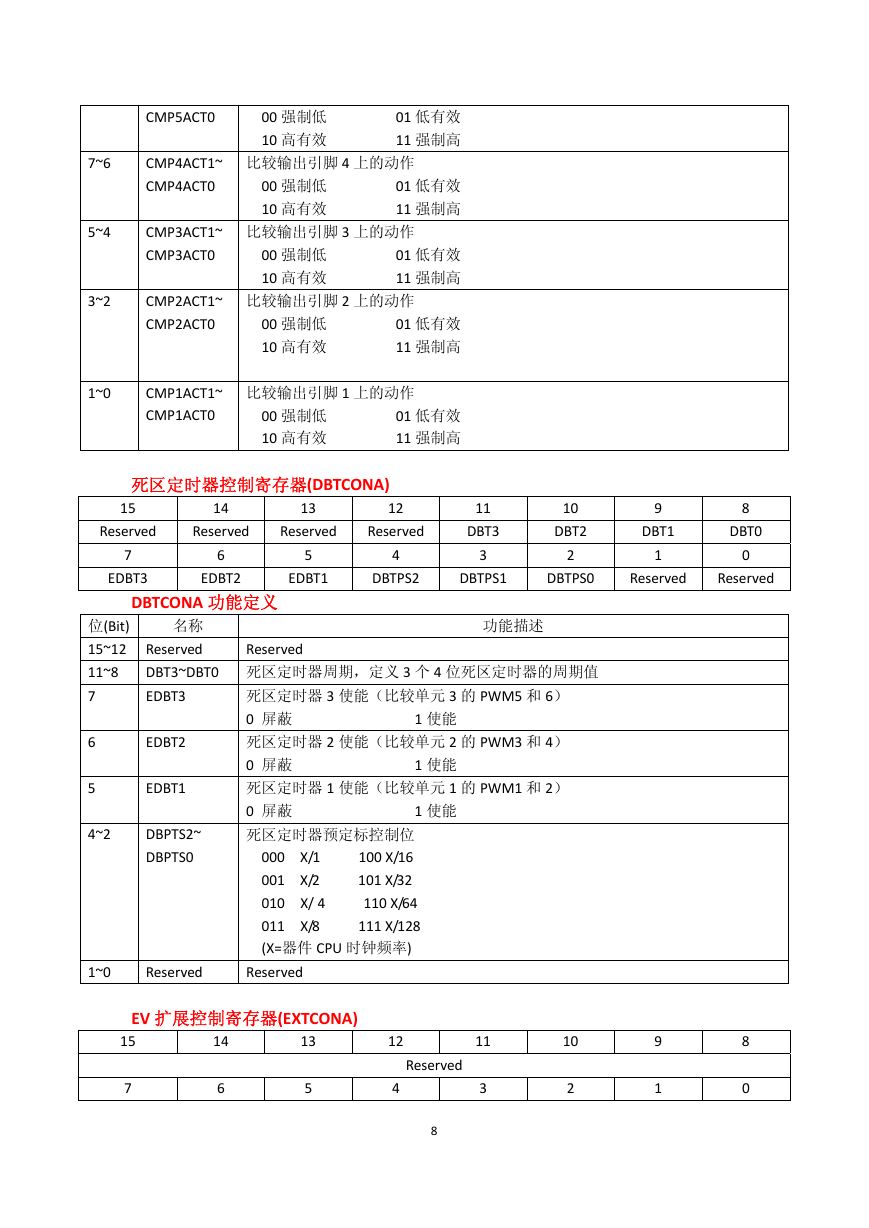

EV 扩展控制寄存器(EXTCONA)

15

7

14

6

13

5

12

Reserved

4

11

3

8

10

2

9

1

8

0

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc