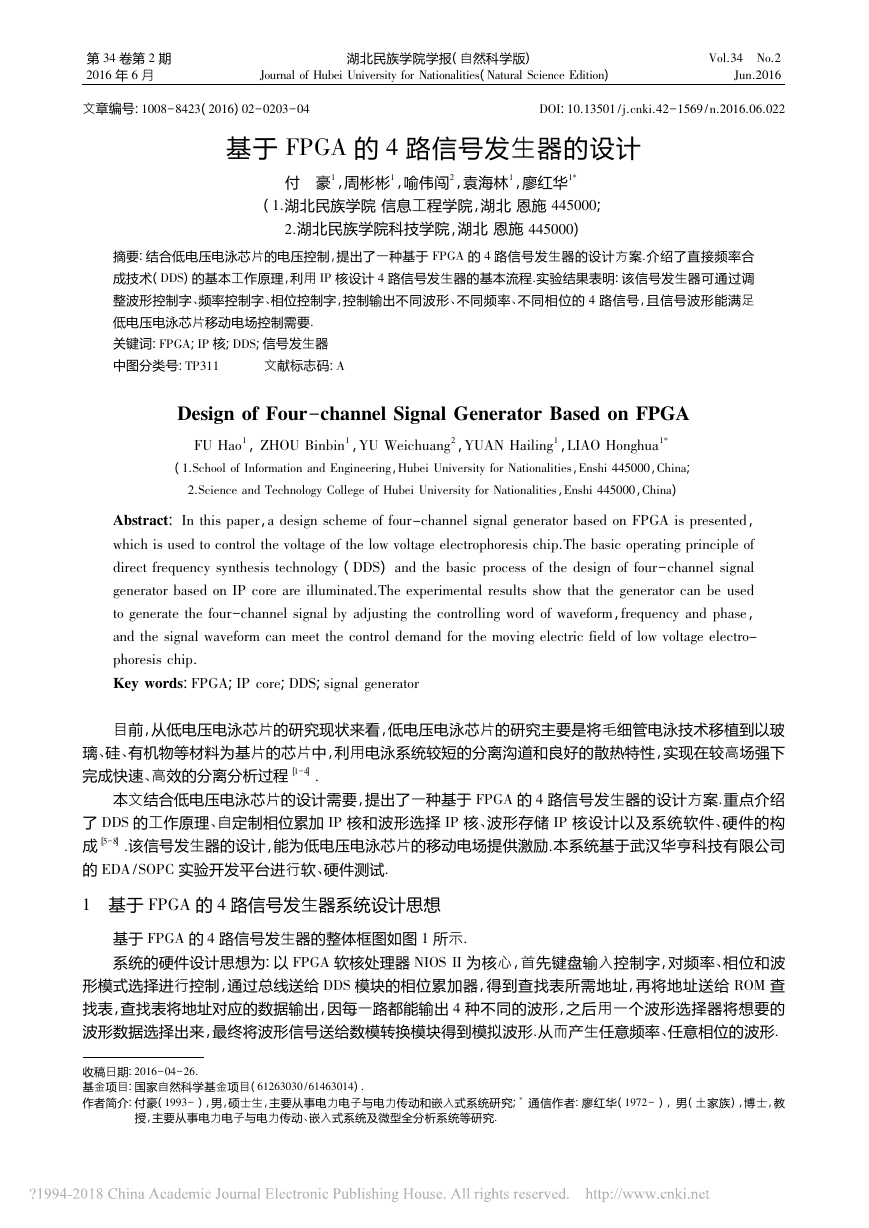

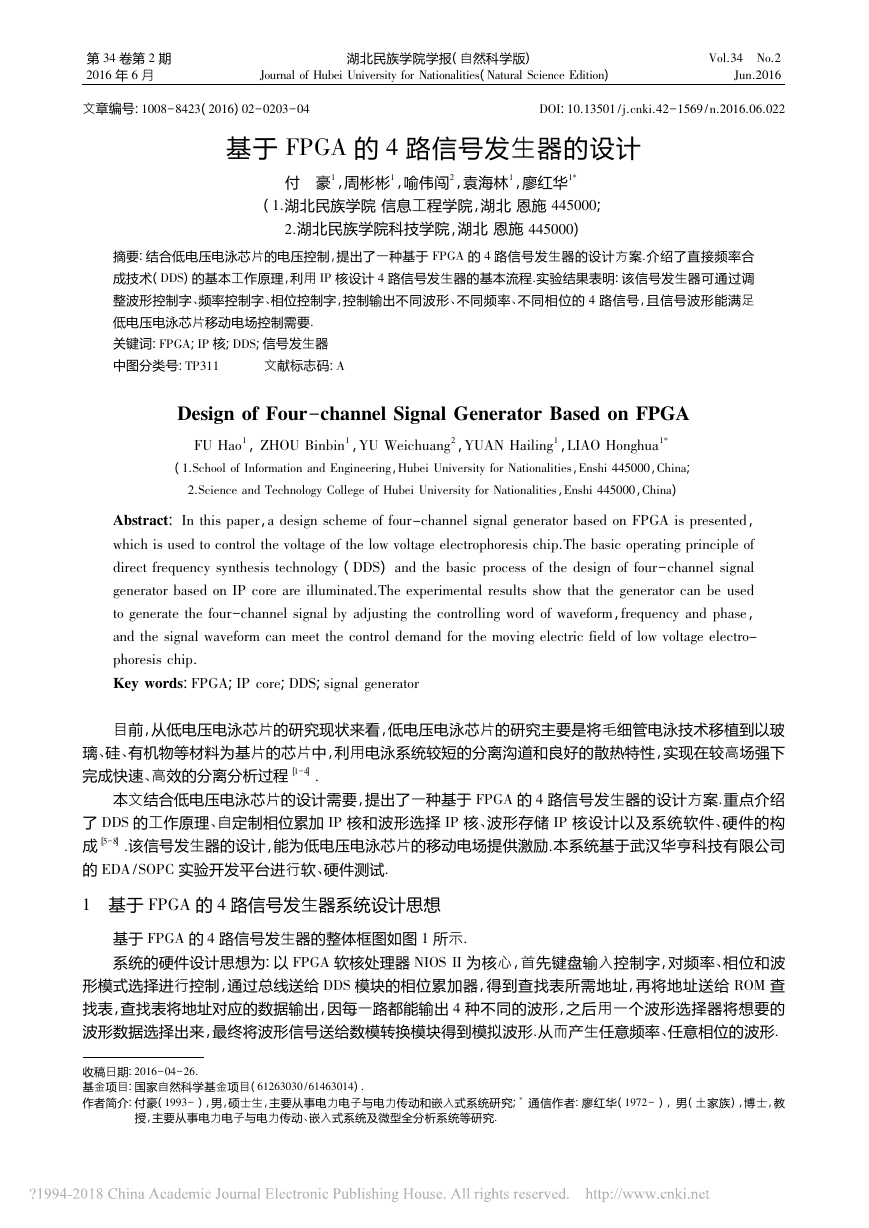

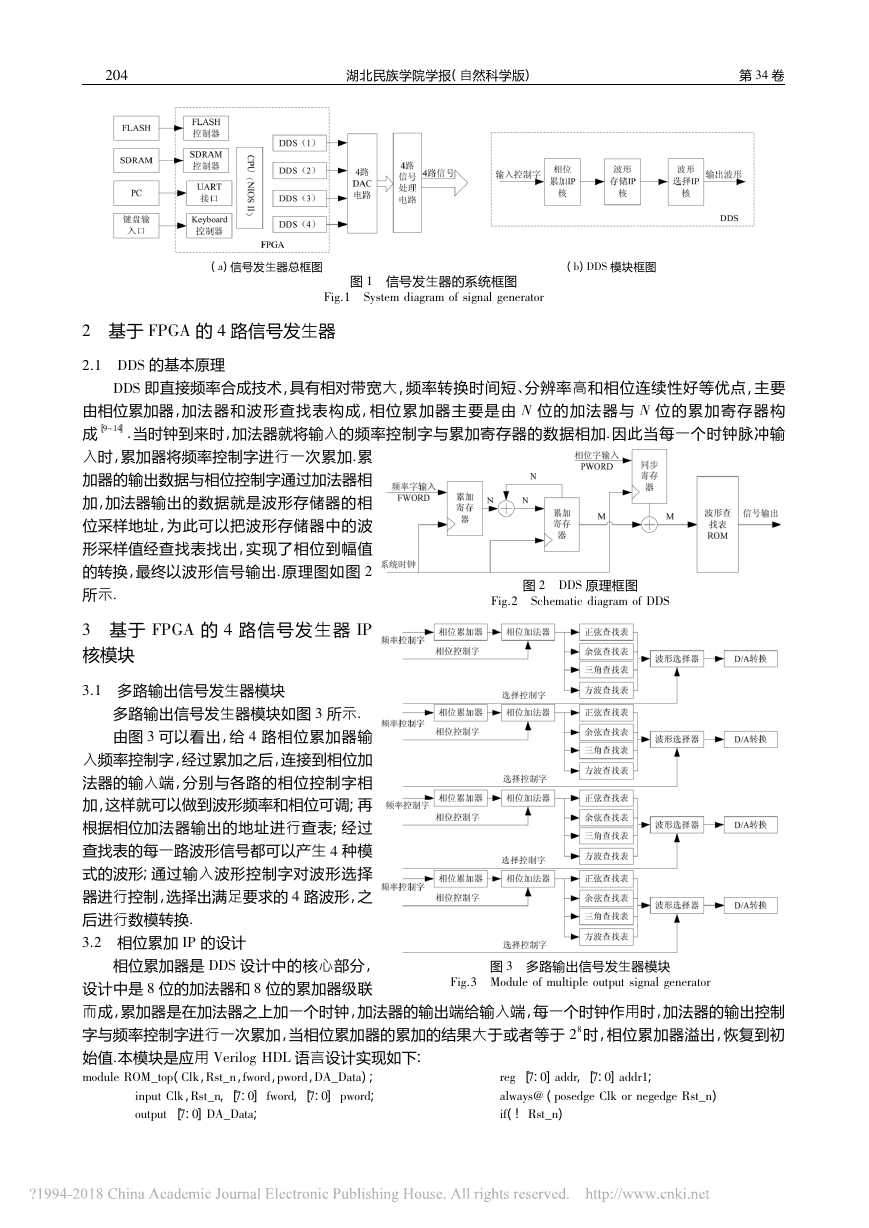

收稿日期:2016-04-26.基金项目:国家自然科学基金项目(61263030/61463014).作者简介:付豪(1993-),男,硕士生,主要从事电力电子与电力传动和嵌入式系统研究;*通信作者:廖红华(1972-),男(土家族),博士,教授,主要从事电力电子与电力传动、嵌入式系统及微型全分析系统等研究.文章编号:1008-8423(2016)02-0203-04DOI:10.13501/j.cnki.42-1569/n.2016.06.022基于FPGA的4路信号发生器的设计付豪1,周彬彬1,喻伟闯2,袁海林1,廖红华1*(1.湖北民族学院信息工程学院,湖北恩施445000;2.湖北民族学院科技学院,湖北恩施445000)摘要:结合低电压电泳芯片的电压控制,提出了一种基于FPGA的4路信号发生器的设计方案.介绍了直接频率合成技术(DDS)的基本工作原理,利用IP核设计4路信号发生器的基本流程.实验结果表明:该信号发生器可通过调整波形控制字、频率控制字、相位控制字,控制输出不同波形、不同频率、不同相位的4路信号,且信号波形能满足低电压电泳芯片移动电场控制需要.关键词:FPGA;IP核;DDS;信号发生器中图分类号:TP311文献标志码:ADesignofFour-channelSignalGeneratorBasedonFPGAFUHao1,ZHOUBinbin1,YUWeichuang2,YUANHailing1,LIAOHonghua1*(1.SchoolofInformationandEngineering,HubeiUniversityforNationalities,Enshi445000,China;2.ScienceandTechnologyCollegeofHubeiUniversityforNationalities,Enshi445000,China)Abstract:Inthispaper,adesignschemeoffour-channelsignalgeneratorbasedonFPGAispresented,whichisusedtocontrolthevoltageofthelowvoltageelectrophoresischip.Thebasicoperatingprincipleofdirectfrequencysynthesistechnology(DDS)andthebasicprocessofthedesignoffour-channelsignalgeneratorbasedonIPcoreareilluminated.Theexperimentalresultsshowthatthegeneratorcanbeusedtogeneratethefour-channelsignalbyadjustingthecontrollingwordofwaveform,frequencyandphase,andthesignalwaveformcanmeetthecontroldemandforthemovingelectricfieldoflowvoltageelectro-phoresischip.Keywords:FPGA;IPcore;DDS;signalgenerator目前,从低电压电泳芯片的研究现状来看,低电压电泳芯片的研究主要是将毛细管电泳技术移植到以玻璃、硅、有机物等材料为基片的芯片中,利用电泳系统较短的分离沟道和良好的散热特性,实现在较高场强下完成快速、高效的分离分析过程[1-4].本文结合低电压电泳芯片的设计需要,提出了一种基于FPGA的4路信号发生器的设计方案.重点介绍了DDS的工作原理、自定制相位累加IP核和波形选择IP核、波形存储IP核设计以及系统软件、硬件的构成[5-8].该信号发生器的设计,能为低电压电泳芯片的移动电场提供激励.本系统基于武汉华亨科技有限公司的EDA/SOPC实验开发平台进行软、硬件测试.1基于FPGA的4路信号发生器系统设计思想基于FPGA的4路信号发生器的整体框图如图1所示.系统的硬件设计思想为:以FPGA软核处理器NIOSII为核心,首先键盘输入控制字,对频率、相位和波形模式选择进行控制,通过总线送给DDS模块的相位累加器,得到查找表所需地址,再将地址送给ROM查找表,查找表将地址对应的数据输出,因每一路都能输出4种不同的波形,之后用一个波形选择器将想要的波形数据选择出来,最终将波形信号送给数模转换模块得到模拟波形.从而产生任意频率、任意相位的波形.第34卷第2期湖北民族学院学报(自然科学版)Vol.34No.22016年6月JournalofHubeiUniversityforNationalities(NaturalScienceEdition)Jun.2016�

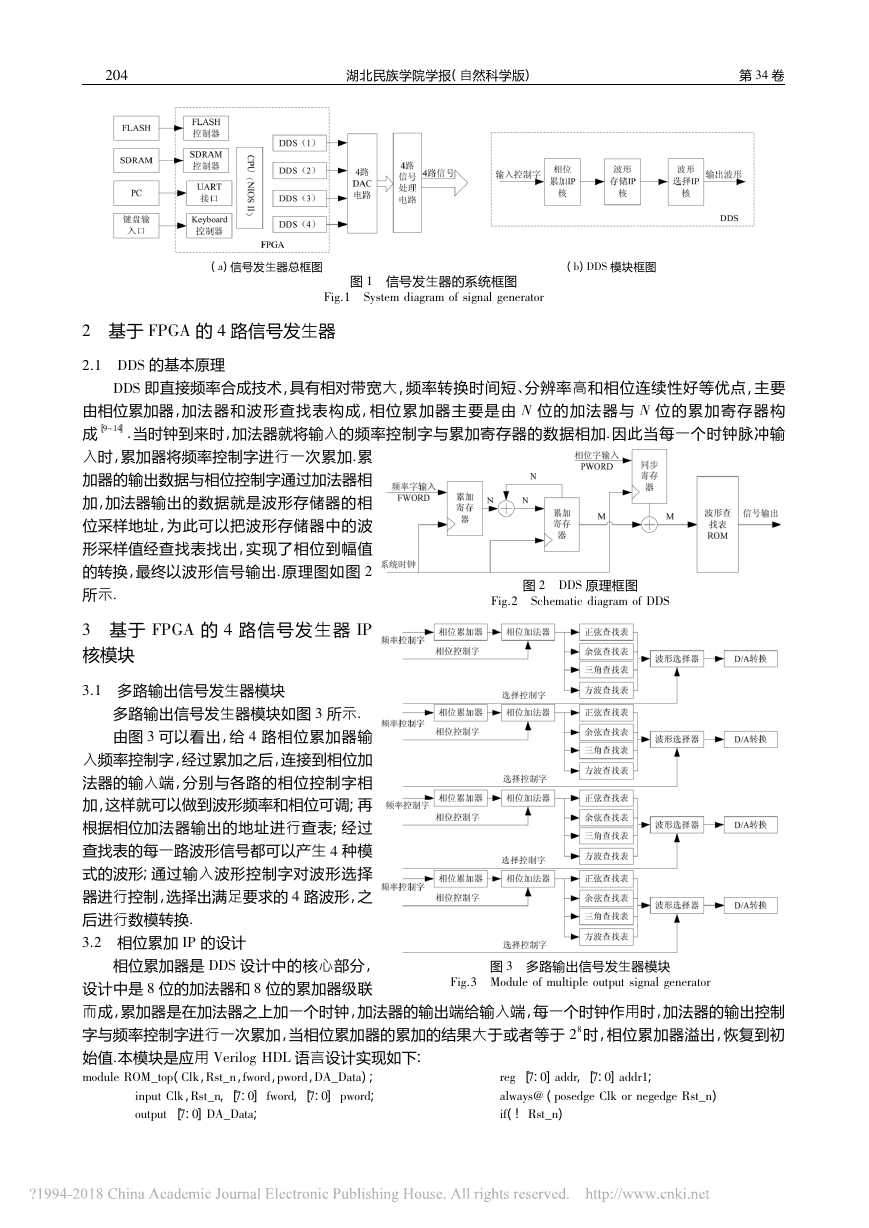

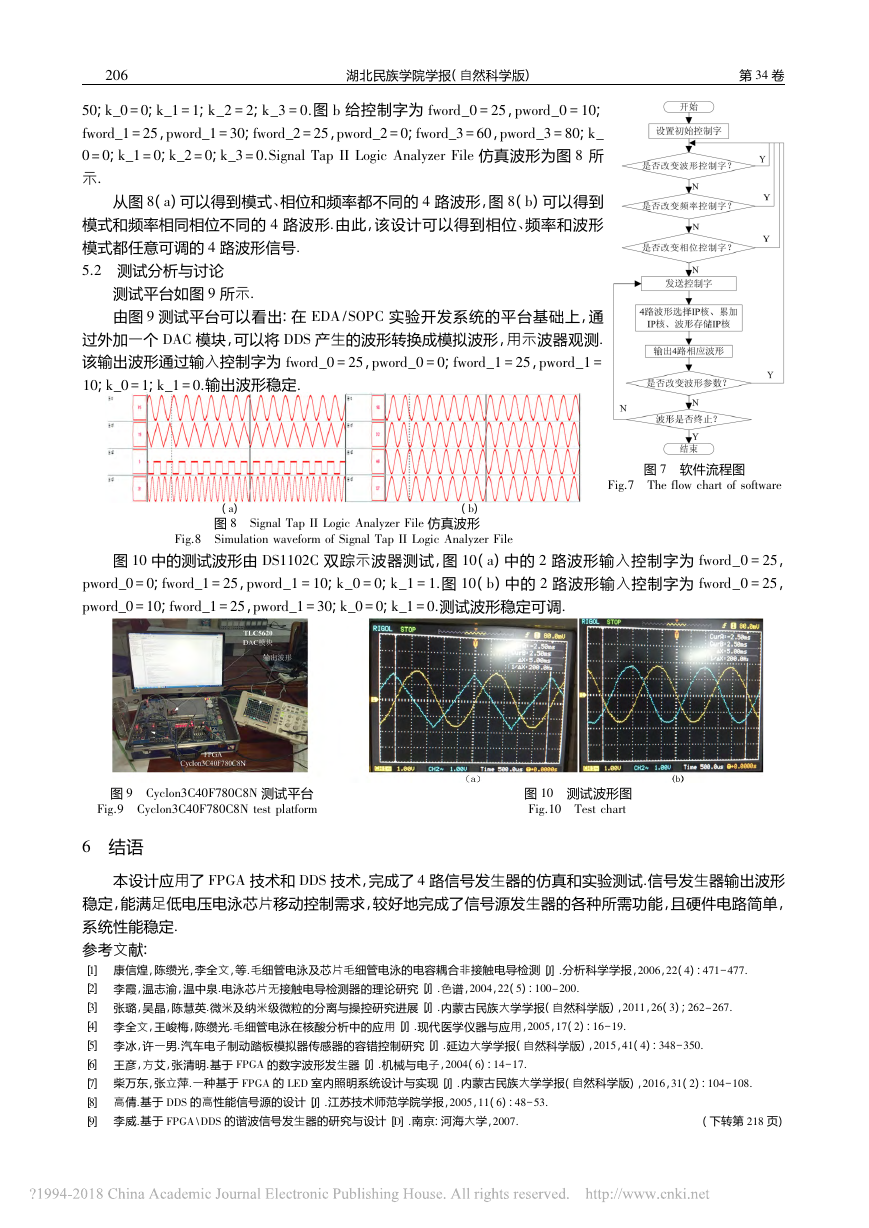

(a)信号发生器总框图(b)DDS模块框图图1信号发生器的系统框图Fig.1Systemdiagramofsignalgenerator2基于FPGA的4路信号发生器2.1DDS的基本原理图2DDS原理框图Fig.2SchematicdiagramofDDS图3多路输出信号发生器模块Fig.3ModuleofmultipleoutputsignalgeneratorDDS即直接频率合成技术,具有相对带宽大,频率转换时间短、分辨率高和相位连续性好等优点,主要由相位累加器,加法器和波形查找表构成,相位累加器主要是由N位的加法器与N位的累加寄存器构成[9-14].当时钟到来时,加法器就将输入的频率控制字与累加寄存器的数据相加.因此当每一个时钟脉冲输入时,累加器将频率控制字进行一次累加.累加器的输出数据与相位控制字通过加法器相加,加法器输出的数据就是波形存储器的相位采样地址,为此可以把波形存储器中的波形采样值经查找表找出,实现了相位到幅值的转换,最终以波形信号输出.原理图如图2所示.3基于FPGA的4路信号发生器IP核模块3.1多路输出信号发生器模块多路输出信号发生器模块如图3所示.由图3可以看出,给4路相位累加器输入频率控制字,经过累加之后,连接到相位加法器的输入端,分别与各路的相位控制字相加,这样就可以做到波形频率和相位可调;再根据相位加法器输出的地址进行查表;经过查找表的每一路波形信号都可以产生4种模式的波形;通过输入波形控制字对波形选择器进行控制,选择出满足要求的4路波形,之后进行数模转换.3.2相位累加IP的设计相位累加器是DDS设计中的核心部分,设计中是8位的加法器和8位的累加器级联而成,累加器是在加法器之上加一个时钟,加法器的输出端给输入端,每一个时钟作用时,加法器的输出控制字与频率控制字进行一次累加,当相位累加器的累加的结果大于或者等于28时,相位累加器溢出,恢复到初始值.本模块是应用VerilogHDL语言设计实现如下:moduleROM_top(Clk,Rst_n,fword,pword,DA_Data);inputClk,Rst_n,[7:0]fword,[7:0]pword;output[7:0]DA_Data;reg[7:0]addr,[7:0]addr1;always@(posedgeClkornegedgeRst_n)if(!Rst_n)402湖北民族学院学报(自然科学版)第34卷�

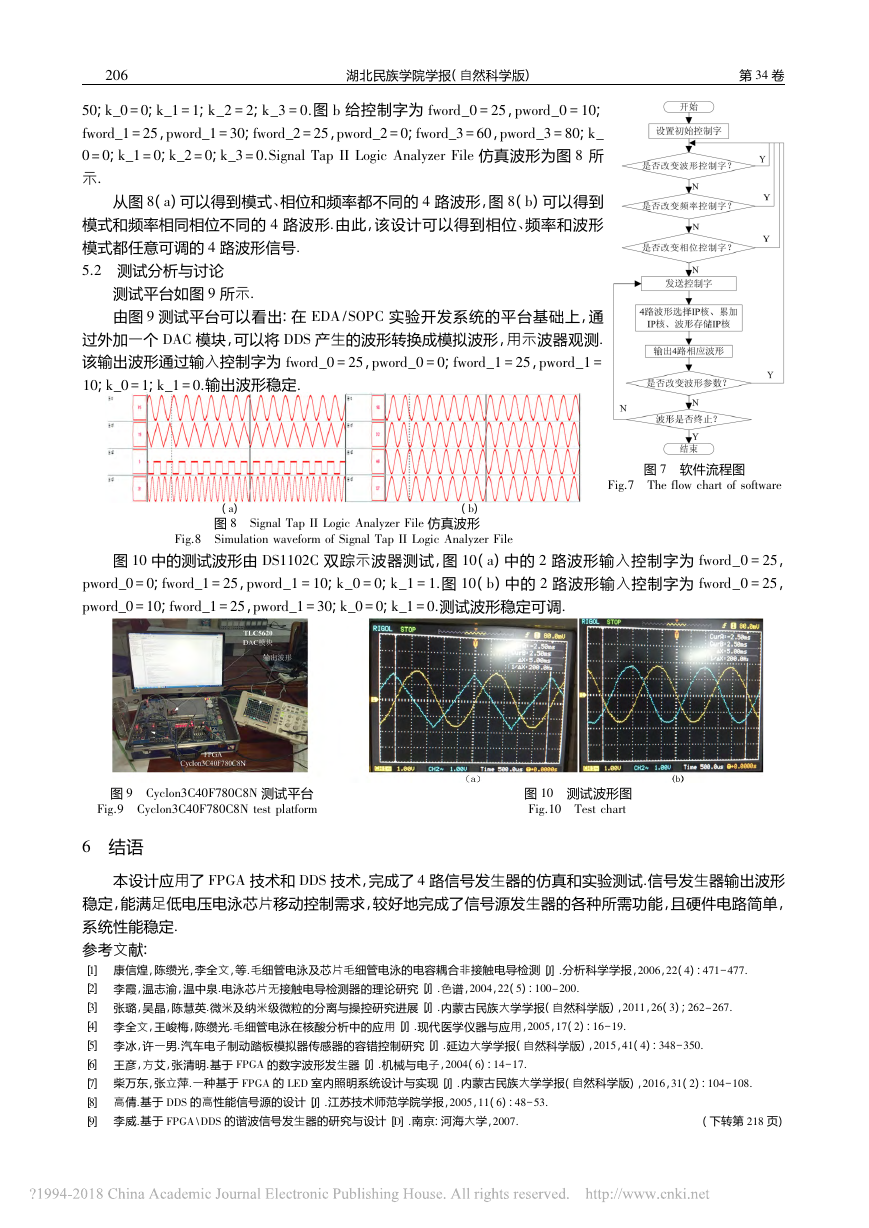

addr<=8'd0;elseaddr<=addr+fword;always@(posedgeClkornegedgeRst_n)if(!Rst_n)addr1<=8'd0;elseaddr1<=addr+pword;assignDA_Data=addr1;endmodule由以上代码生成IP核,如下图4所示.图4相位累加器IP核模块Fig.4IPcoremoduleofthephaseaccumulator图6波形选择器IP核模块Fig.6IPcoremoduleofwaveformselector3.3波形存储IP的设计波形存储器的输入与相位累加器的输出相连,实现相位地址到波形幅值的转换.设计中利用MATLAB进行波形仿真得出波形数据,该波形数据为10位,256个数据,因为余弦波和正弦波只是相位的不同,因此产生余弦波可以通过正弦波调相产生.首先用QuartusII中生成一个.mif文件,再将波形数据保存在.mif文件中,同时生成一个ROM的IP核,将文件加到该IP核中,得到波形存储器.下图为波形存储器的IP核模块.(a)(b)(c)图5波形存储器的IP核模块Fig.5IPcoremoduleofthewaveformmemory3.4波形选择IP的设计波形选择器的主要功能是:根据设计要求,从输入的4种波形中选择一种波形.通过波形选择控制字进行控制,当控制字为00时,选择第一种波形;控制字为01时,选择第二种波形;控制字为10时,选择第三种波形;控制字为11时,选择第四种波形.模块是应用VerilogHDL语言设计实现如下:modulexz(clk,Rst_n,k1,data1,data2,data3,data4,data);inputclk,[1:0]k1,Rst_n,[9:0]data1,[9:0]data2,[9:0]data3,[9:0]data4;output[9:0]data;reg[9:0]data_k;always@(posedgeclkornegedgeRst_n)if(!Rst_n)data_k<=10'b00_0000_0000;data_k<=10'b00_0000_0000;always@(posedgeclkornegedgeRst_n)begincase({k1})2'b00:data_k=data1;2'b01:data_k=data2;2'b10:data_k=data3;2'b11:data_k=data4;endcaseendassigndata=data_k;Endmodule由以上代码生成IP核,如下图6所示.4软件设计软件的设计如图7所示,工作流程为:当系统启动后,系统首先进入参数设定状态,通过判断键盘是否输入4路的波形选择和初始的信号频率和相位,设定好初始状态,根据设置值进行相应的处理,将频率和相位控制字送给相位累加IP核进行累加,累加的相位地址送给波形存储IP核,实现相位到幅值的转化,另外的波形选择控制字和波形存储IP核输出的波形信号同时送给波形选择IP核,输出到4路满足要求的波形信号.5仿真与测试分析与讨论5.1仿真与分析讨论设计通过SignalTapIILogicAnalyzerFile进行仿真,得到4路频率和相位可调的稳定波形.图a给的控制字为fword_0=25,pword_0=0;fword_1=25,pword_1=10;fword_2=25,pword_2=0;fword_3=30,pword_3=502第2期付豪等:基于FPGA的4路信号发生器的设计�

图7软件流程图Fig.7Theflowchartofsoftware50;k_0=0;k_1=1;k_2=2;k_3=0.图b给控制字为fword_0=25,pword_0=10;fword_1=25,pword_1=30;fword_2=25,pword_2=0;fword_3=60,pword_3=80;k_0=0;k_1=0;k_2=0;k_3=0.SignalTapIILogicAnalyzerFile仿真波形为图8所示.从图8(a)可以得到模式、相位和频率都不同的4路波形,图8(b)可以得到模式和频率相同相位不同的4路波形.由此,该设计可以得到相位、频率和波形模式都任意可调的4路波形信号.5.2测试分析与讨论测试平台如图9所示.由图9测试平台可以看出:在EDA/SOPC实验开发系统的平台基础上,通过外加一个DAC模块,可以将DDS产生的波形转换成模拟波形,用示波器观测.该输出波形通过输入控制字为fword_0=25,pword_0=0;fword_1=25,pword_1=10;k_0=1;k_1=0.输出波形稳定.(a)(b)图8SignalTapIILogicAnalyzerFile仿真波形Fig.8SimulationwaveformofSignalTapIILogicAnalyzerFile图10中的测试波形由DS1102C双踪示波器测试,图10(a)中的2路波形输入控制字为fword_0=25,pword_0=0;fword_1=25,pword_1=10;k_0=0;k_1=1.图10(b)中的2路波形输入控制字为fword_0=25,pword_0=10;fword_1=25,pword_1=30;k_0=0;k_1=0.测试波形稳定可调.图9Cyclon3C40F780C8N测试平台图10测试波形图Fig.9Cyclon3C40F780C8NtestplatformFig.10Testchart6结语本设计应用了FPGA技术和DDS技术,完成了4路信号发生器的仿真和实验测试.信号发生器输出波形稳定,能满足低电压电泳芯片移动控制需求,较好地完成了信号源发生器的各种所需功能,且硬件电路简单,系统性能稳定.参考文献:[1]康信煌,陈缵光,李全文,等.毛细管电泳及芯片毛细管电泳的电容耦合非接触电导检测[J].分析科学学报,2006,22(4):471-477.[2]李霞,温志渝,温中泉.电泳芯片无接触电导检测器的理论研究[J].色谱,2004,22(5):100-200.[3]张璐,吴晶,陈慧英.微米及纳米级微粒的分离与操控研究进展[J].内蒙古民族大学学报(自然科学版),2011,26(3);262-267.[4]李全文,王峻梅,陈缵光.毛细管电泳在核酸分析中的应用[J].现代医学仪器与应用,2005,17(2):16-19.[5]李冰,许一男.汽车电子制动踏板模拟器传感器的容错控制研究[J].延边大学学报(自然科学版),2015,41(4):348-350.[6]王彦,方艾,张清明.基于FPGA的数字波形发生器[J].机械与电子,2004(6):14-17.[7]柴万东,张立萍.一种基于FPGA的LED室内照明系统设计与实现[J].内蒙古民族大学学报(自然科学版),2016,31(2):104-108.[8]高倩.基于DDS的高性能信号源的设计[J].江苏技术师范学院学报,2005,11(6):48-53.[9]李威.基于FPGA\DDS的谐波信号发生器的研究与设计[D].南京:河海大学,2007.(下转第218页)602湖北民族学院学报(自然科学版)第34卷�

x12∨y12,x21·x11,x22·x12,x23·x13,y12,y22.该子句集存在矛盾,证明了结论的正确性.例2证明或反驳命题,从公式◇(x∨y)[μ≥1/3],□x[μ=1]和□y[μ≥2/3]推出公式◇y[μ≤1/3].同上可得:x≡(x1,x2,x3),y≡(y1,y2,y3),x≡(x1,x3,x2),y≡(y1,y3,y2).◇(x∨y)[μ≥1/3]=(◇x∨◇y)[μ≥1/3]=◇(x1∨y1,x2∨y2,x3∨y3)[μ≥1/3]=◇(010∨110∨111)=◇(x2∨y2),□x[μ=1]=□(x1x3x2)[μ=1]=□(111)=□(x1·x3·x2),□y[μ≥2/3]=□(y1y3y2)[μ≥2/3]=□(110∨111)=□(y1),◇y[μ≤1/3]=◇(010∨000)=◇(y1·y2).获得了等价公式:◇(x2∨y2),□(x1·x3·x2),□(y1),xi=0,1,yi=0,1.从以上公式中证明公式◇(y1·y2).对被证明的公式求反,得到以下的子句集:◇(x2∨y2),□(x1·x3·x2),□(y1),◇(y1·y2)=□(y1∨y2).最终形成以下的子句集:x12∨y12,x21·x11,x22·x12,x23·x13,y21,y11,y11∨y12,y21∨y22.该子句集不存在矛盾,证明了结论是不正确的.4结论本文的理论方法可以应用在各种智能系统中.显然,由于卢卡西维茨多值逻辑推理机的近似特性,还需要进一步研究多个真值和规定精度之间的关系.除此之外,如何将推理机应用于含有模糊谓词的模态推理中也是一个需要深入研究的课题.参考文献:[1]周娟,李超.基于卢卡西维茨多值演算的模态逻辑推理机[J].湖北民族学院学报(自然科学版),2015,33(3):285-289.[2]张家录,陈雪刚,赵晓东.经典命题逻辑的概率语义及其应用[J].计算机学报,2014,37(8):1775-1785.[3]GEMANOV,SAMKORA,GERMANYuO.Aninferencesystemforafuzzylogiconthebasisofmulti-valuedLukasiewiczcalculi[J].WorksoftheBelarusianUniversityofTechnology(Minsk,Belarus),NaturalSciencesandInformatics,VI,2010,(18):190-193(inRussian).[4]GERMANOV.Non-classicallogicalcalculi[M].TheRepublicofBelarus:BSUIR,2012:21-25(inRussian).[5]李骏,王国俊.基于支持度理论的广义ModusPonens问题的最优解[J].软件学报,2007,18(11):2712-2714.[6]NIVELLEDH,SCHMIDTRA,HUSTADTU.Resolution-basedmethodsformodallogics[J].LogicJournaloftheIGPL,2002,10(1):265-292.[7]陈晓平.自然演绎逻辑导论[M].广州:中山大学出版社,2006:102-103.[8]Jarmu-ekT.TableauMetatheoremforModalLogics[M].Germany:SpringerInternationalPublishing,2014:103-126.[9]王庆平,王国俊.多值Lukasiewicz逻辑公式的范式表示和计数问题[J].软件学报,2013,24(3):433-453.责任编辑:时凌(上接第206页)[10]周绍军.基于DDS技术的高精度双路可移相波形信号发生器设计[J].西南民族大学学报(自然科学版),2010,36(5):822-826.[11]徐建,刘晓妤.基于FPGA的信号发生器设计[J].湖北民族学院学报(自然科学版),2013,31(3):330-333.[12]VANKKAJ,LINDEBERGJ,HALONENK.Adirectdigitalsynthesizerwithtunabledeltasigmamodulator[J].AnalogIntegratedCircuitsandSig-nalProcessing,2004,38(1):7-15.[13]CHENTAIW,GUIP,XIULM,etal.Adigital-to-frequencysynthesizerwithclockdithering[J].AnalogIntegratedCircuits&SignalProcessing,2012,74(3):533-543.[14]CHENSG,CHIHJC,CHOUJY.Directdigitalfrequencysynthesisbasedonatwo-leveltable-lookupscheme[J].JournalofSignalProcessingSystems,2006,45(3):153-160.责任编辑:时凌812湖北民族学院学报(自然科学版)第34卷�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc