基于 Cypress 公司 USB2.0 芯片 CY7C68013A 的速传接口开发(供开发人员参考)

配置模式:SLAVE-FIFO

开发环境搭建:安装 cy3681_ez_usb_fx2_development_kit_15 开发包,

或者 cy3684_ez_usb_fx2lp_development_kit_15 开发包

cy3681_ez_usb_f

x2_development_kit_15.zip

cy3684_ez_usb_f

x2lp_development_kit_15开发包.zip

一、硬件电路

USB_CY7C68013

A.SchDoc

CY7C68013A 芯片的 PA0~PA7 这 8 个 IO 脚为开漏配置,最好在使用时接上 10K 电阻

关键注意点:

1.

上拉;

2.

CY7C68013A 芯片系统时钟为外接 24MHz 时钟,也可以由 FPGA 提供,片上 51 内核

内置 PLL 倍频,此时的系统内部工作时钟为 48MHz;

3. 芯片通信时钟 IFCLK 可选择由内部自身提供,也可外部提供,一般选择 48MHz,突

出 USB2.0 的高速通信速率,最好选择外部提供,保证与外部控制器 FPGA 的时序同步;

4. 芯片内部没有存储 RAM,需要外接一片 EPPROM 与芯片的 IIC 接口进行 Programme,

此时固件也必须生成 .iic 的文件;(具体见附件)

二、电脑 USB 驱动文件 .SYS \.INF 开发

Drivers.rar

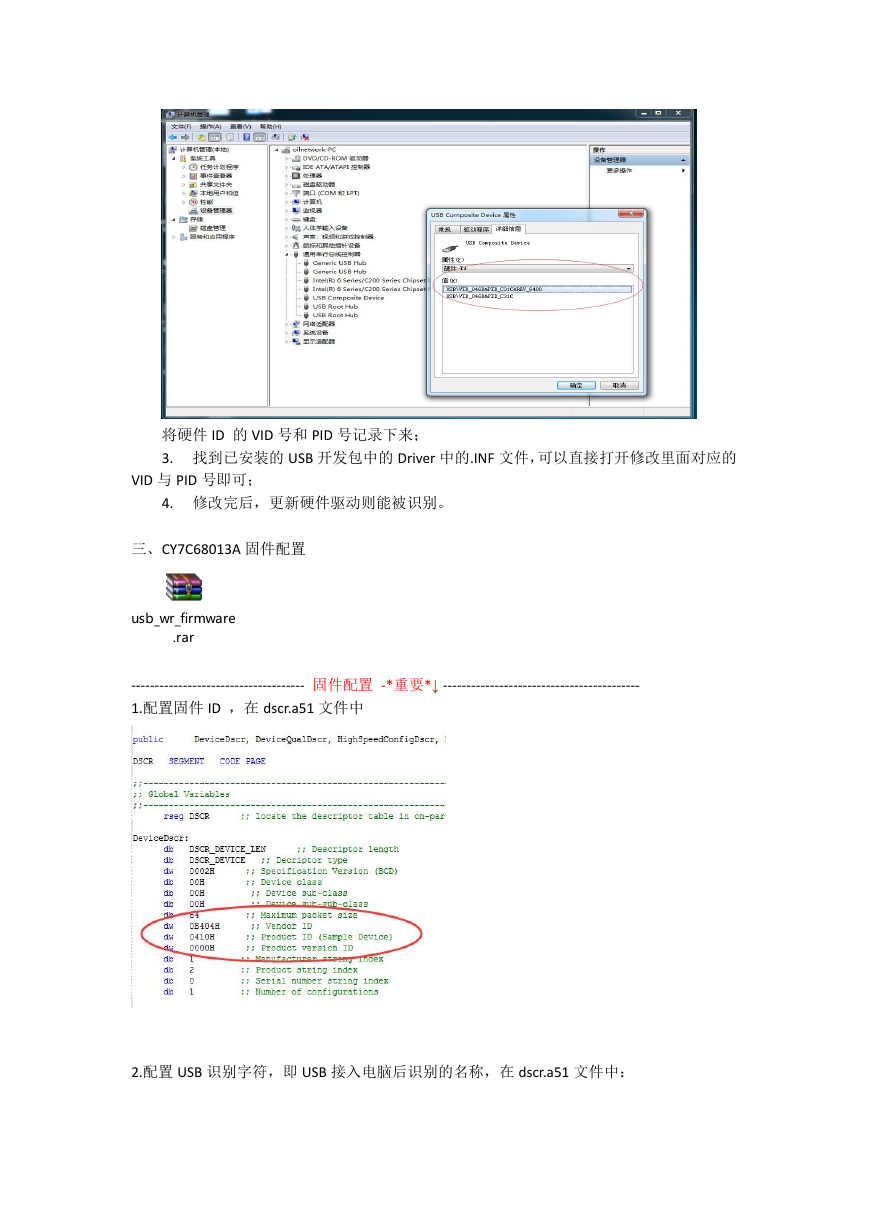

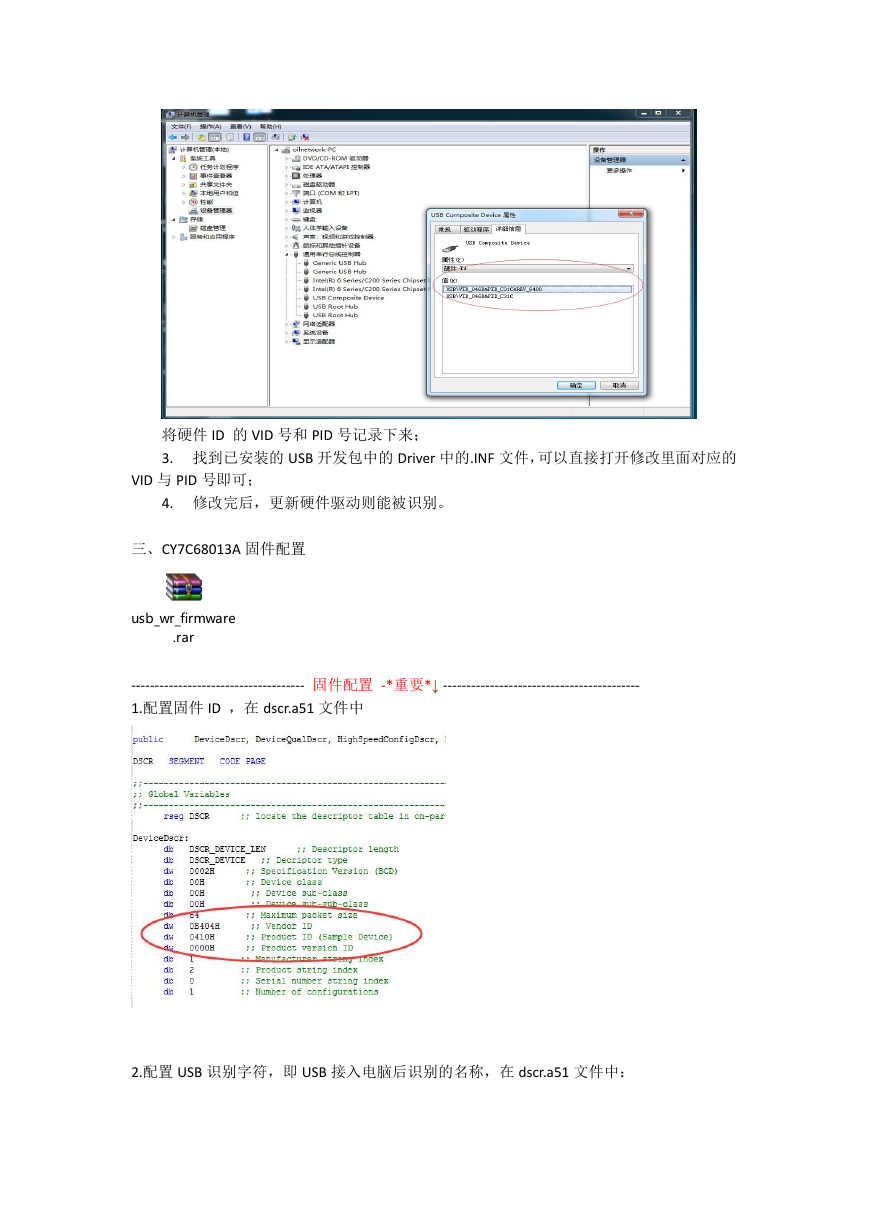

当连接好的硬件电路首次接入电脑,会出现未识别硬件的提示,解决识别问题操作步骤

如下:

1. 通过右键“我的电脑”进入设备管理器,查看通用串行总线控制器找到带有感叹号

的未识别硬件;

2. 右键未识别硬件,选择属性,再进入属性中的详细信息,在属性选择栏中选择“硬

件 ID”,则会弹出类似如下图:

�

将硬件 ID 的 VID 号和 PID 号记录下来;

3. 找到已安装的 USB 开发包中的 Driver 中的.INF 文件,可以直接打开修改里面对应的

VID 与 PID 号即可;

4. 修改完后,更新硬件驱动则能被识别。

三、CY7C68013A 固件配置

usb_wr_firmware

.rar

------------------------------------- 固件配置 -*重要*↓ ------------------------------------------

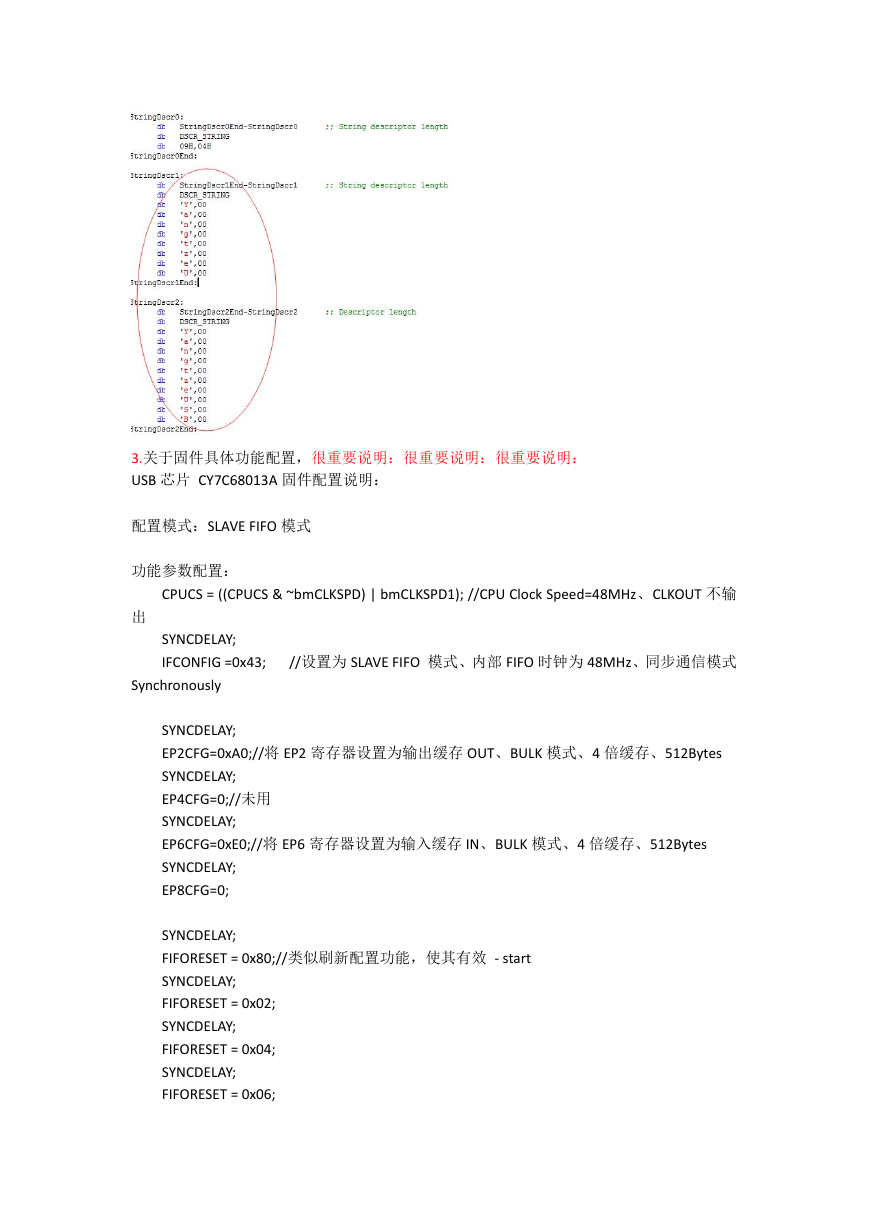

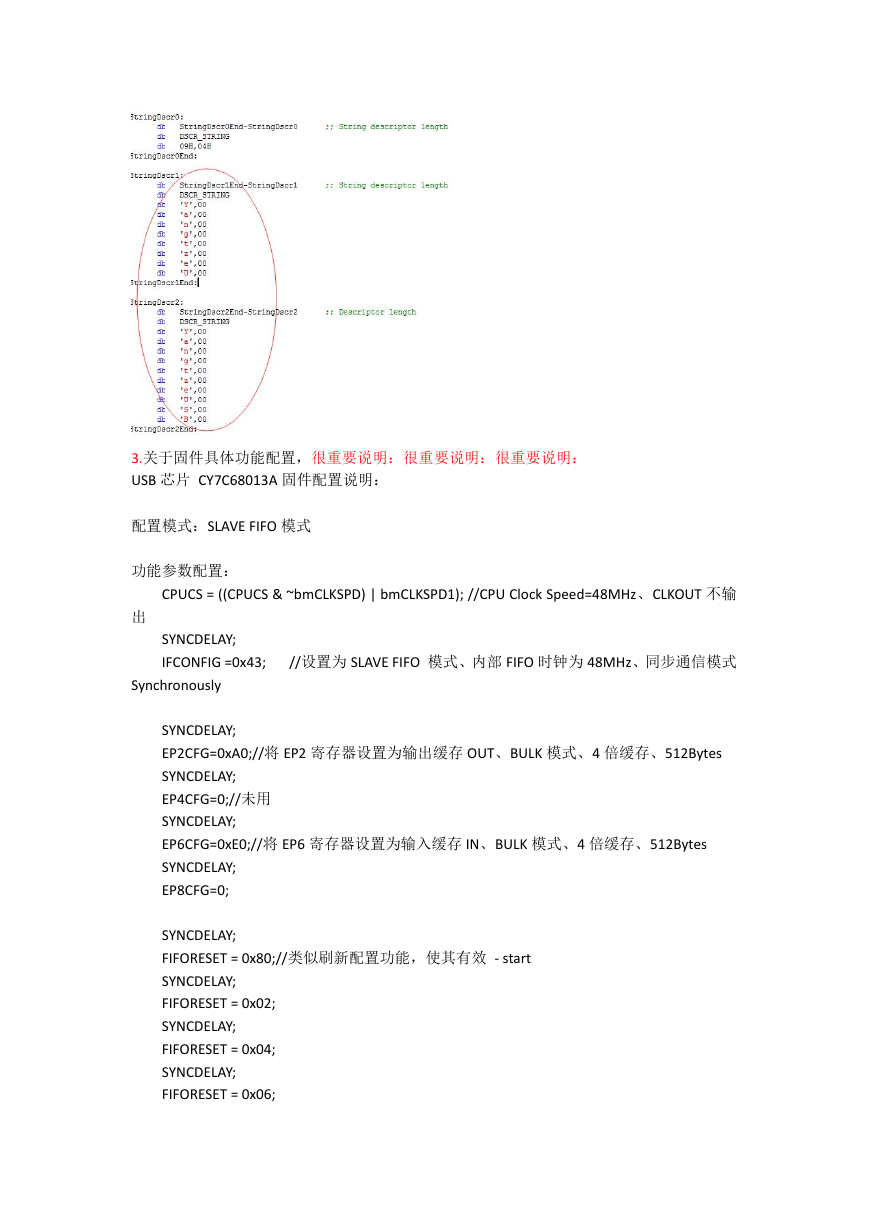

1.配置固件 ID ,在 dscr.a51 文件中

2.配置 USB 识别字符,即 USB 接入电脑后识别的名称,在 dscr.a51 文件中:

�

3.关于固件具体功能配置,很重要说明:很重要说明:很重要说明:

USB 芯片 CY7C68013A 固件配置说明:

配置模式:SLAVE FIFO 模式

功能参数配置:

CPUCS = ((CPUCS & ~bmCLKSPD) | bmCLKSPD1); //CPU Clock Speed=48MHz、CLKOUT 不输

出

SYNCDELAY;

IFCONFIG =0x43;

Synchronously

//设置为 SLAVE FIFO 模式、内部 FIFO 时钟为 48MHz、同步通信模式

SYNCDELAY;

EP2CFG=0xA0;//将 EP2 寄存器设置为输出缓存 OUT、BULK 模式、4 倍缓存、512Bytes

SYNCDELAY;

EP4CFG=0;//未用

SYNCDELAY;

EP6CFG=0xE0;//将 EP6 寄存器设置为输入缓存 IN、BULK 模式、4 倍缓存、512Bytes

SYNCDELAY;

EP8CFG=0;

SYNCDELAY;

FIFORESET = 0x80;//类似刷新配置功能,使其有效 - start

SYNCDELAY;

FIFORESET = 0x02;

SYNCDELAY;

FIFORESET = 0x04;

SYNCDELAY;

FIFORESET = 0x06;

�

SYNCDELAY;

FIFORESET = 0x08;

SYNCDELAY;

FIFORESET = 0x00;// - end

SYNCDELAY;

PINFLAGSAB = 0x8C;//将 FLAGB 脚设置为 EP2EF(EP2 寄存器空标志 - OUT -非空即读)、

FLAGA 为 EP2FF(EP2 满标志)

SYNCDELAY;

PINFLAGSCD = 0xFE;//将 FLAGD 脚设置为 EP8FF(EP8 满标志)、FLAGC 为 EP6FF(EP6 满

标志 - IN -非满即写)

= 0x0;//未使用 FLAGD(SLCS)引脚功能

SYNCDELAY;

PORTACFG

SYNCDELAY;

FIFOPINPOLAR = 0x00;//默认选定所有引脚为低电平有效

SYNCDELAY;

EP2FIFOCFG = 0x11;//设置为自动输出模式 AUTOOUT - 16 位数据接口

SYNCDELAY;

EP6FIFOCFG = 0x09;//设置为自动输入模式 AUTOIN - 16 位数据接口

SYNCDELAY;

:

FIFOADR0 - FIFOADR1

00

01

10

11

EP2

EP4

EP6

EP8

:

:

:

:

------------------------------------------------固件配置 ↑-------------------------------------------------------------

四、外部控制器设计 FPGA

EZ-USB-TRM2.p

df

时序参考文档:

USB_YJ_TestSucc

ess.rar

---------------------------------------------------------------------------------------------------------------------------------

在配置 FPGA 自带的 FIFO 时,注意:

�

!!!

否则在读出 FIFO 时在首位会出现两个空字节。

使用 show-ahead 模式,即读端的 rdreq 信号作为读取 FIFO 的确认信号(ACK),读取数据在 rdreq

置位后立即有效,不要额外的读取周期。

如果使用的是 Normal(Legacy),读端的 rdreq 信号作为读取 FIFO 的请求信号 REQ,读取数据在

rdreq 置位后的第二个时间周期有效,则会出现首两位空字节现象。

如果使用的是 ACTEL 的 FPGA 芯片:

但是在调用该 FIFO 的时候,需要

---------------------------------------------------------------------------------------------------------------------------------

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc