pg280-polar_June2018.pdf.html

极性编码器/解码器

v1.0

LogiCORE IP 产品指南

Vivado 设计套件

2019/12/8

1/72

�

2019/12/8

pg280-polar_June2018.pdf.html

支持的

设备系列(1)

支持的用户

介面

资源资源

设计文件

样例设计

测试平台

约束文件

模拟

模型

支持的

硬件驱动

设计输入

模拟

合成

介绍

在极地编码器/解码器的软 IP 核

支持 Polar 编码和解码。的极性

代码是可配置的,可以使用逐块

地进行。

注意:在本文档中,块是通用术语

用于编码器处理的数据的原子单位

或解码器。码字是编码块,用于讨

论,用于生成他的代码参数。

特征

• 支持 3GPP TS 38.212 V15.1.1 3rd

世代合作项目;技术

规范组无线接入网;

NR; 多路复用和信道编码

(版本 15)[参考文献 10]

解码器> 80 Mb / s(N = 1024,K = 200)

编码器> 700 Mb / s(N = 1024,K = 200)

• 极性编码或解码

• 吞吐量(1)最高:

• 高带宽 AXI4-Stream 接口

1. 请参阅性能。数字为时钟频率为 400MHz,

应针对实现的时钟进行缩放频率。吞吐量是

许多因素的函数包括代码大小,代码混合,

时钟频率和扩增参数。

支持

由 Xilinx 在 Xilinx 支持网页上提供

笔记:

1.有关支持的设备的完整列表,请参见 Vivado IP

2.有关工具的受支持版本,请参见 Xilinx 设计工具

目录。

箱:版本说明指南。

知识产权事实

LogiCORE™IP 事实表

核心细节

性能和资源利用网页

提供核心

UltraScale™,UltraScale +™

7 系列

AXI4-Lite,AXI4-Stream

不适用

IP 集成器框图

Verilog

Xilinx 设计约束(XDC)

系统 Verilog 安全模型

位精度 C 模型

用于 MATLAB 的 MEX 文件

单机版

(2)

Vivado®设计套件

经过测试的设计流程

对于支持模拟器,看到了

Xilinx 设计工具箱:版本说明指南。

维瓦多

Polar 编码器/解码器 v1.0 4

www.xilinx.com

产品规格书

2/72

�

pg280-polar_June2018.pdf.html

第 1 章

总览

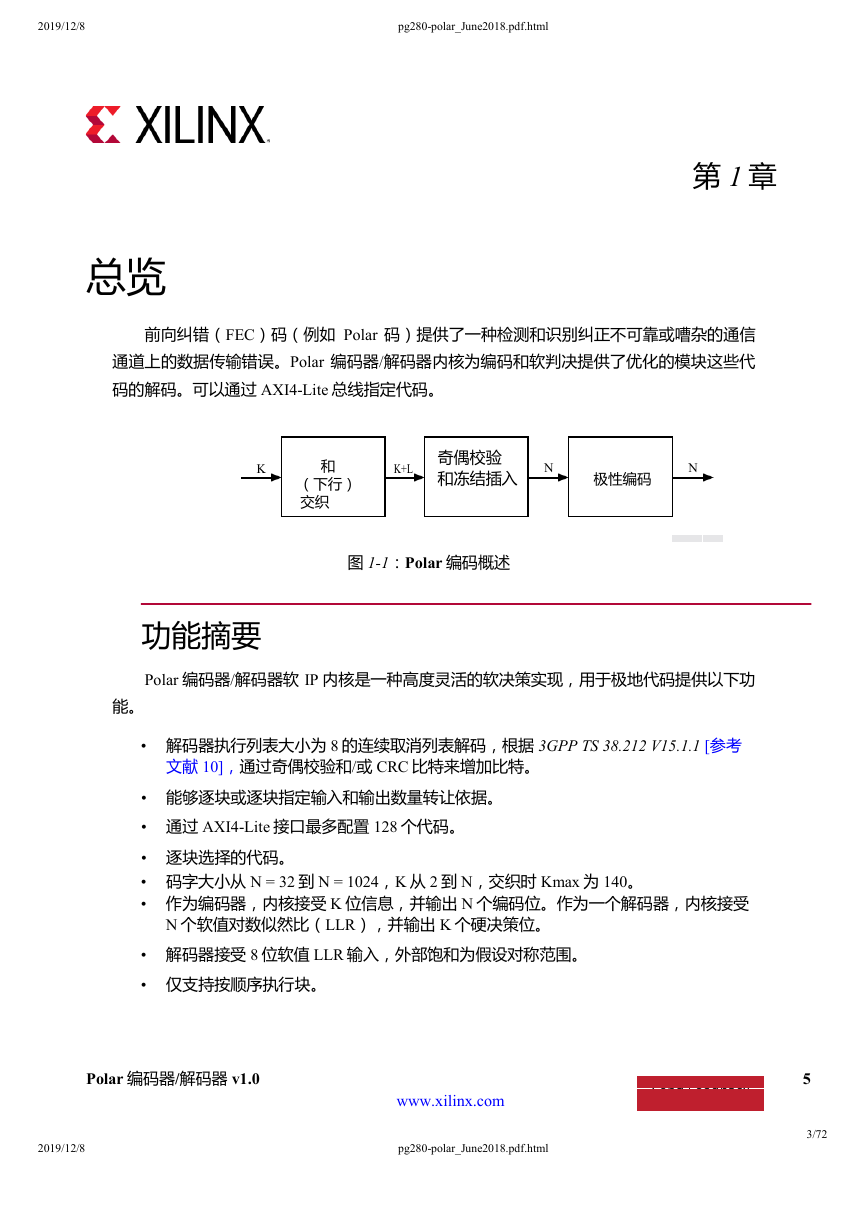

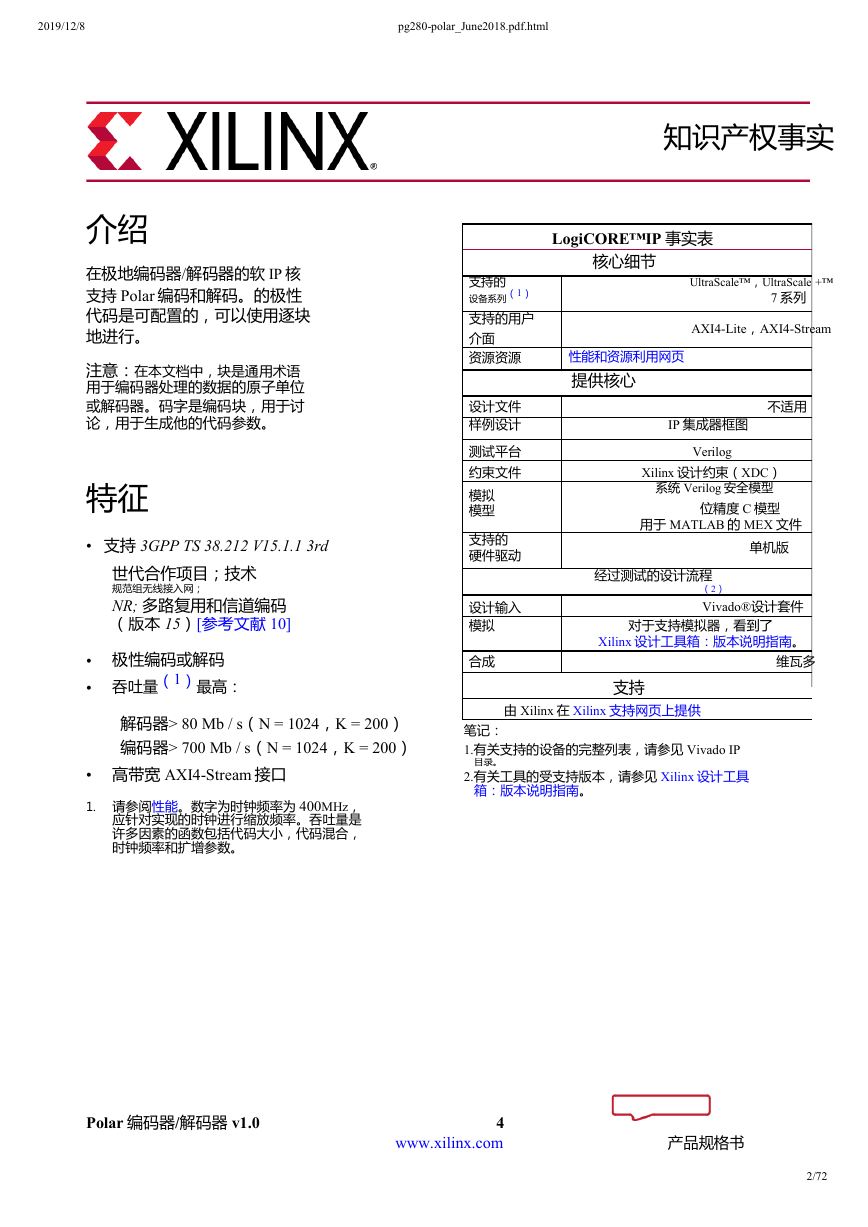

前向纠错(FEC)码(例如 Polar 码)提供了一种检测和识别纠正不可靠或嘈杂的通信

通道上的数据传输错误。Polar 编码器/解码器内核为编码和软判决提供了优化的模块这些代

码的解码。可以通过 AXI4-Lite 总线指定代码。

K

和

(下行)

交织

奇偶校验

K+L

和冻结插入

N

极性编码

N

图 1-1:Polar 编码概述

功能摘要

Polar 编码器/解码器软 IP 内核是一种高度灵活的软决策实现,用于极地代码提供以下功

能。

• 解码器执行列表大小为 8 的连续取消列表解码,根据 3GPP TS 38.212 V15.1.1 [参考

文献 10],通过奇偶校验和/或 CRC 比特来增加比特。

• 能够逐块或逐块指定输入和输出数量转让依据。

• 通过 AXI4-Lite 接口最多配置 128 个代码。

• 逐块选择的代码。

• 码字大小从 N = 32 到 N = 1024,K 从 2 到 N,交织时 Kmax 为 140。

• 作为编码器,内核接受 K 位信息,并输出 N 个编码位。作为一个解码器,内核接受

N 个软值对数似然比(LLR),并输出 K 个硬决策位。

• 解码器接受 8 位软值 LLR 输入,外部饱和为假设对称范围。

• 仅支持按顺序执行块。

2019/12/8

Polar 编码器/解码器 v1.0

2019/12/8

www.xilinx.com

pg280-polar_June2018.pdf.html

5

3/72

�

• 输入和输出上的宽数据接口。

• 单独的输入和输出流允许提供控制参数和状态逐块地进行。

第一章:概述

应用领域

Polar 编码器/解码器内核旨在但不限于在应用程序中使用需要 Polar 编码/解码,例如 5G

无线(3GPP TS 38.212 V15.1.1 复用和通道编码(第 15 版)[参考文献 10] )。表 1-1 描述了

用于每个所需的设置 在 3GPP TS 38.212 V15.1.1 [参考文献 10]中描述的 Polar 使用模式。

表 1-1:Polar 使用模式设置

使用方式

增加

两者或 CRC

联合会

生物安全信息交换所 CRC

DCI

CRC

笔记:

1.交错启用/禁用标志。

CRC_SEL

CRC6 或 CRC11

CRC24C

CRC24C

ITLV (1)

CRC_INIT

0

1 个

1 个

0

0

1 个

N,K

按要求

许可和订购

该 Xilinx LogiCORE™IP 模块是根据 Xilinx 核心许可条款提供的协议书。该模块是

Vivado®Design Suite 的一部分。完全访问仿真和硬件中的所有核心功能,您必须购买许可证

核心。完整许可证,请访问产品许可网页。评估许可证和 该内核或子系统可能会提供硬件

超时许可证。与您当地的人 联系 Xilinx 销售代表提供有关价格和可用性的信息。

有关更多信息,请访问 Polar 编码器/解码器产品网页。

有关其他 Xilinx LogiCORE IP 模块的信息,请参见 Xilinx Intelligent。属性页。有关其

他 Xil inx LogiCORE IP 的 价格和可用性的信息模块和工具,请与当地的 Xilinx 销售代表联

系。

Polar 编码器/解码器 v1.0

6

�

2019/12/8

pg280-polar_June2018.pdf.html

产品规格书

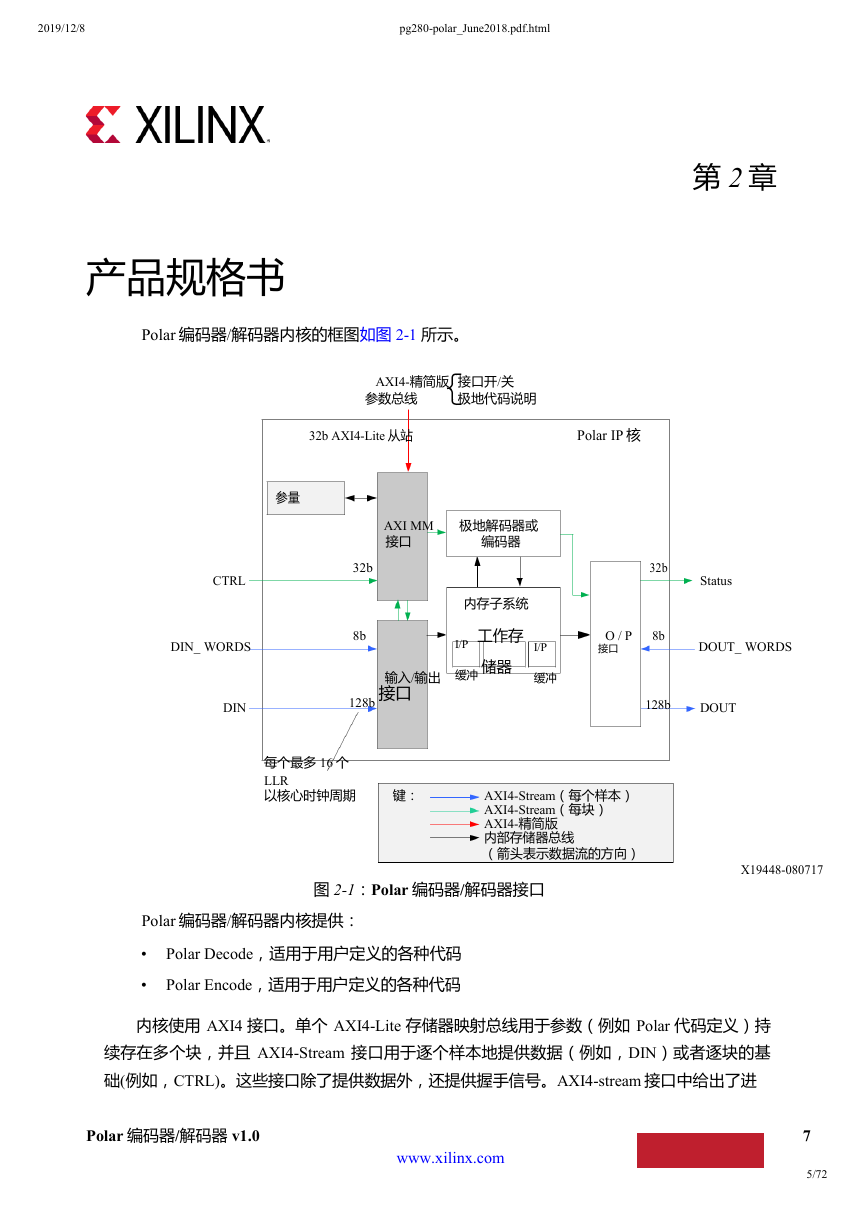

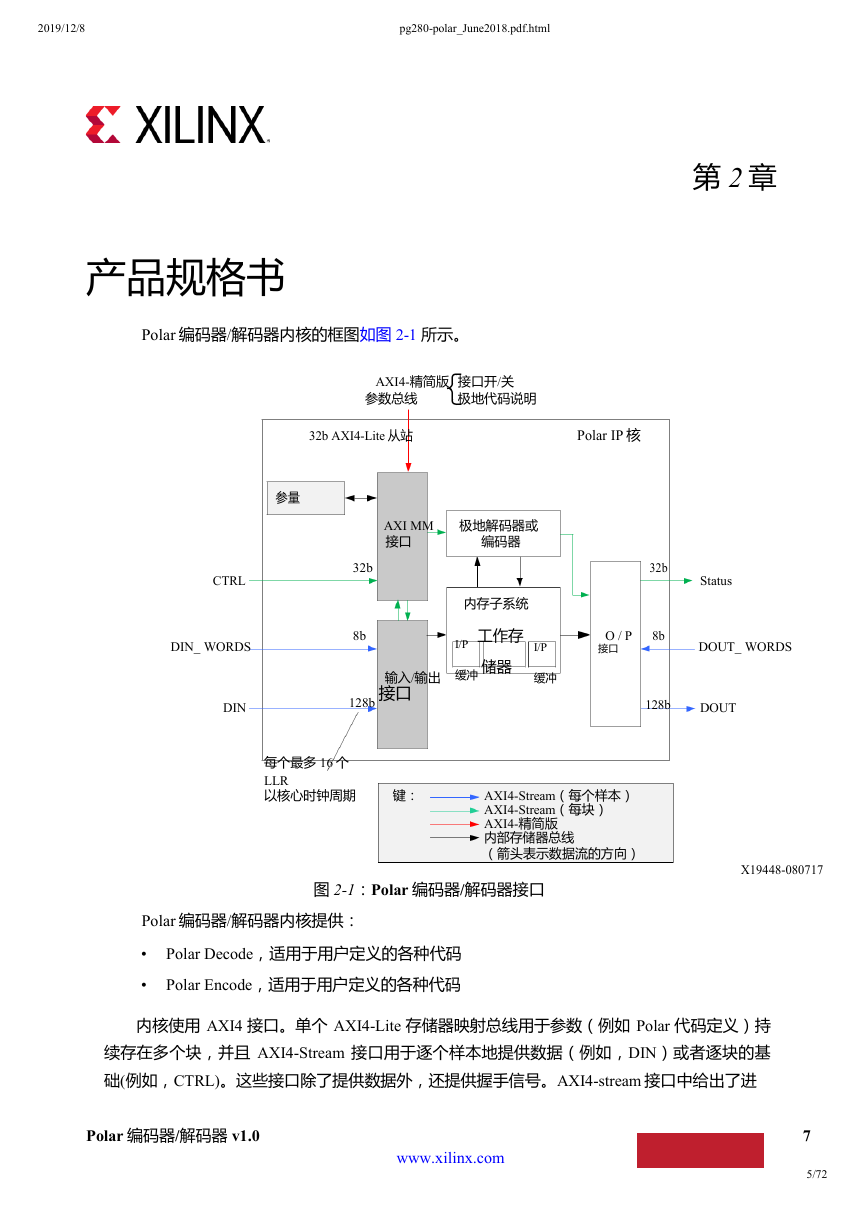

Polar 编码器/解码器内核的框图如图 2-1 所示。

参量

CTRL

DIN_ WORDS

DIN

第 2 章

AXI4-精简版 接口开/关

极地代码说明

参数总线

32b AXI4-Lite 从站

Polar IP 核

32b

8b

AXI MM 极地解码器或

接口

编码器

内存子系统

I/P 工作存

缓冲 储器

输入/输出

128b 接口

I/P

缓冲

32b

8b

128b

O / P

接口

Status

DOUT_ WORDS

DOUT

每个最多 16 个

LLR

以核心时钟周期

键:

AXI4-Stream(每个样本)

AXI4-Stream(每块)

AXI4-精简版

内部存储器总线

(箭头表示数据流的方向)

X19448-080717

图 2-1:Polar 编码器/解码器接口

Polar 编码器/解码器内核提供:

• Polar Decode,适用于用户定义的各种代码

• Polar Encode,适用于用户定义的各种代码

内核使用 AXI4 接口。单个 AXI4-Lite 存储器映射总线用于参数(例如 Polar 代码定义)持

续存在多个块,并且 AXI4-Stream 接口用于逐个样本地提供数据(例如,DIN)或者逐块的基

础(例如,CTRL)。这些接口除了提供数据外,还提供握手信号。AXI4-stream 接口中给出了进

Polar 编码器/解码器 v1.0

www.xilinx.com

7

5/72

�

2019/12/8

pg280-polar_June2018.pdf.html

第二章:产品规格

一步的细节。数据输入和输出缓冲器提供了与编码器/解码器操作重叠的输入和输出范围。

每个块通过数据输入接口(DIN)在多个周期内输入。在每个周期中传输的数据量由一个单

独的数据流(DIN_WORDS)设置,其中 DIN 上的每个事务都有一个值。输出是以类似的方式在

DOUT 输出流上生成的,类似地,在输入数据流 DOUT_WORDS 上指定了传输的数据量。

对于每个块,在控件(CTRL)输入流上需要一个输入,指定要使用的代码和用户提供的 id

字段。每个数据块需要一个控制字(事务),数据输入暂停,直到相关的控制字可用为止。当解

码(或编码)时,输出数据与状态(STATUS)输出接口上的状态字一起提供在 DOUT 上。

CTRL

DIN_WORDS

DIN

解码器/编码器 延迟

DOUT_WORDS

STATUS

DOUT

先进先出 延迟

DIN 输入取决于可用性

CTRL 和 DIN_WORDS

DOUT 输出取决于内部解码

器

输出和 DOUT_WORDS

状态取决于内部解码器输出

时间

图 2-2:Polar 编码器/解码器接口相关性概述

所有 AXI4-Stream 接口都包含用于流控制的有效和现成的握手。阻塞输出(通过去断言就绪)

最终停止解码,并在输入缓冲区满时阻止进一步的输入。图 2-2 总结了极地编码器/解码器核心

的数据依赖关系。这表明 DIN 上的数据输入依赖于 CTRL 和 DIN_WORDS,而对 DOUT 的输

出依赖于 DOUT_WORDS。然而,CTRL 的输入与 DIN_WORDS 的相关输入之间存在延迟,而

DIN 输入被接受,这是由每个信道上的 Trady 断言所指示的。同样,DIN_WORDS 和 DIN 之间

也有延迟。如果要最小化 DIN 上的延迟,则应预先提供 CTRL 和 DIN_WORDS 的输入。类似

地,对于输出,应该尽快驱动 DOUT_WORDS (如果需要的话),以避免在 DOUT 上出现任何延

迟。接口上有浅层缓冲区(如图 2-2 所示),在 CTRL 上提供关联的块控制之前,可以在 DIN 和

DOUT_WORDS 上输入少量数据。这些数据不被极地编解码核心处理,直到后者可用。这些缓

Polar 编码器/解码器 v1.0

www.xilinx.com

8

6/72

�

pg280-polar_June2018.pdf.html

第二章:产品规格

冲区的另一个含义是 DIN 输入可以从与应用 CTRL 和 DIN_WORDS 的 时间相同。

AXI 4-STREAM 数据接口的使用允许核心将数据吞吐量限制在它可以处理的速率上。要最

大限度地提高吞吐量,您只需确保数据始终在输入上可用,并且数据在可用时从输出中读取,

如 AXI 4-STREAM 握手信号所示。或者,如果要控制吞吐量,则只有 ctrl 输入可以调整到正确

的块吞吐量速率,而其他接口按前面描述的方式工作--也就是说,它们由极地编码器/解码器核

心本身调节。在所有 AXI 4-STREAM 从通道上,应该在块或码字的最后一个事务上断言 tlast。

核心断言用于块或代码字的最后输出事务。

注意:DIN_WORDS 和 DOUT_WORDS 具有更高级的操作模式,其中数字为 DIN 或

DOUT 上的每次传输指定元素的个数。

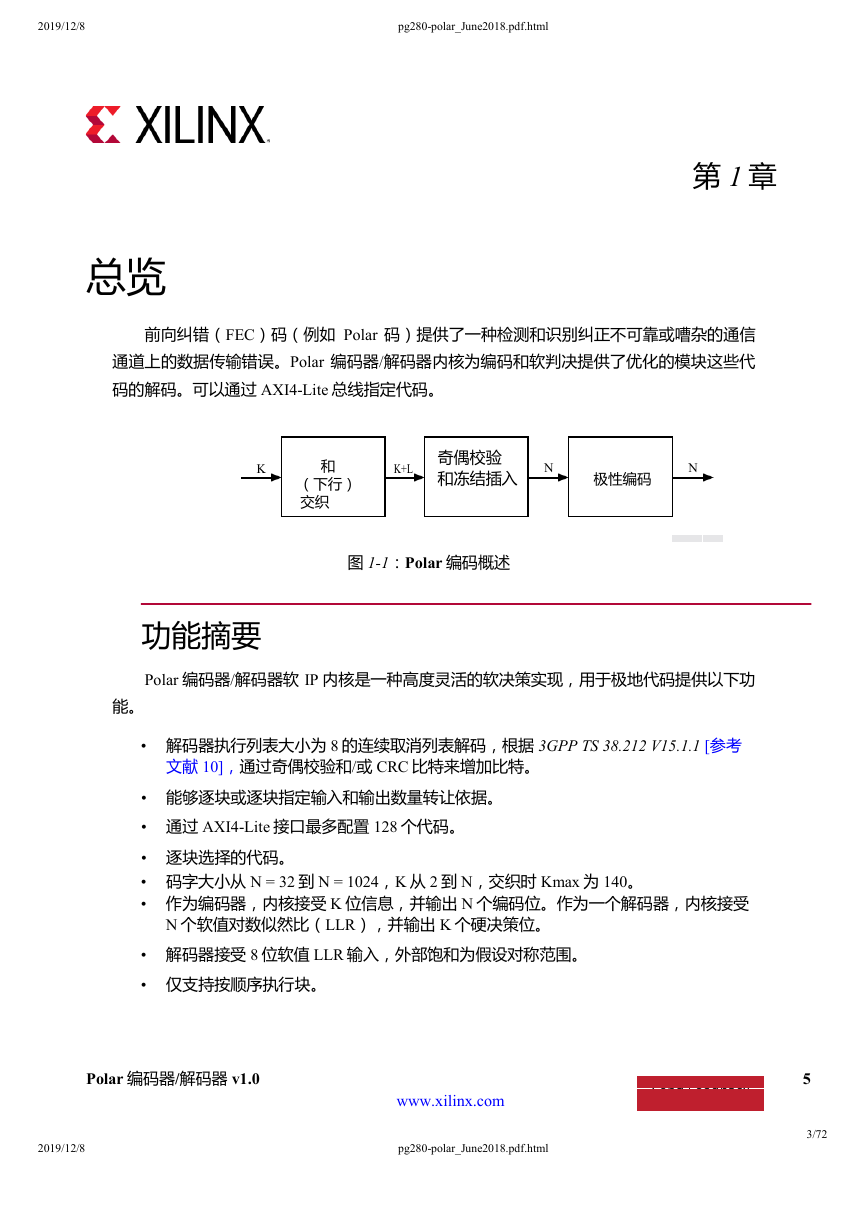

端口说明

表 2-1 显示核心的引脚。 表 2-1:核心引脚排列

信号

reset_n

core_clk

interrupt

s_axi_awaddr

s_axi_awvalid

s_axi_awready

s_axi_wdata

s_axi_wvalid

s_axi_wready

s_axi_bready

s_axi_bvalid

s_axi_araddr

s_axi_arvalid

s_axi_arready

s_axi_rready

s_axi_rdata

s_axi_rvalid

方向宽度

输入项

输入项

输出量

输入项

输入项

输出量

输入项

输入项

输出量

输入项

输出量

输入项

输入项

输出量

输入项

输出量

输出量

1

1

1

18

1

1

32

1

1

1

1

18

1

1

1

32

1

描述

同步复位,负极性

核心单时钟

指示错误情况。行为受控于中断控制寄存器。

参数总线:AXI4-Lite 内存映射从站接口

2019/12/8

Polar 编码器/解码器 v1.0

2019/12/8

pg280-polar_June2018.pdf.html

9

�

信号

表 2-1:核心引脚排列(续)

s_axis_din_words_tvalid

s_axis_din_words_tready

s_axis_din_words_tlast

s_axis_din_words_tdata

s_axis_ctrl_tvalid

s_axis_ctrl_tready

s_axis_ctrl_tdata

s_axis_din_tvalid

s_axis_din_tready

s_axis_din_tlast

s_axis_din_tdata

m_axis_status_tvalid

m_axis_status_tready

m_axis_status_tdata

s_axis_dout_words_tvalid

s_axis_dout_words_tready

s_axis_dout_words_tlast

s_axis_dout_words_tdata

m_axis_dout_tvalid

m_axis_dout_tready

m_axis_dout_tlast

m_axis_dout_tdata

方向

输入项

输出量

输入项

输入项

输入项

输出量

输入项

输入项

输出量

输入项

输入项

输出量

输入项

输出量

输入项

输出量

输入项

输入项

输出量

输入项

输出量

输出量

宽度

1

1

1

8

1

1

32

1

1

1

128

1

1

32

1

1

1

8

1

1

1

128

第二章:产品规格

描述

控制数据输入总线上的字节数:AXI4-Stream 从接口

控制输入总线:AXI4-Stream 从接口

数据输入总线:AXI4-Stream 从接口

状态输出总线:AXI4-Stream 主接口

控制数据输出总线上的字节数:AXI4-Stream 从接口

数据输出总线:AXI4-Stream 主接口

参数总线

AXI4-Lite 参数总线允许在写接口上进行两个未完成的事务,以及读取界面上的一项未完

成交易。较高数量的优秀写接口上的事务提高了写下载吞吐量,从而允许极地代码可以更快地

更新。

Polar 编码器/解码器 v1.0

www.xilinx.com

10

8/72

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc