IP 核复用的系统芯片 SoC 设计技术

http://www.paper.edu.cn

李茜

北京邮电大学,北京(100876)

E-mail:madder205@gmail.com

摘 要:本文介绍了系统芯片 SoC 的特点及 IP 核复用技术,着重从 IP 核复用技术方面探讨

了 SoC 设计中的关键技术问题,讨论了 IP 复用技术的优势。最后,对 IP 核复用在 SoC 设

计中的发展前景做出展望。

关键词:SoC,IP 核,IP 复用

1. 引 言

随着集成电路制造技术的快速发展,使 IC 设计进入了系统芯片 SoC(System on Chip)

的时代。SoC 极大地缩小系统体积、提高了系统的性能;采用基于 IP(Intellectual Property)

核的设计,允许在芯片设计过程中复用已经经过验证的高性能的 IP 核,从而提高了设计效

率,缩短设计周期。

2. SoC 的特点及 IP 核复用技术

自 1947 年晶体管诞生以来,微电子技术在迄今为止的六十年时间里得到了飞速的发展。

Moore 定律指出,特征尺寸平均每三年缩小 2 倍,集成度平均每三年增加四倍、芯片尺寸

每年提高 12%。集成电路芯片在规模上经历了小规模 SSI、中规模 MSI、大规模 LSI、超大

规模 VLSI 之后,进入了超大规模 GSI 阶段,集成电路工艺技术发展趋势如表 1 所示。这使

得将整个复杂系统集成到一个芯片,即 SoC 成为可能。

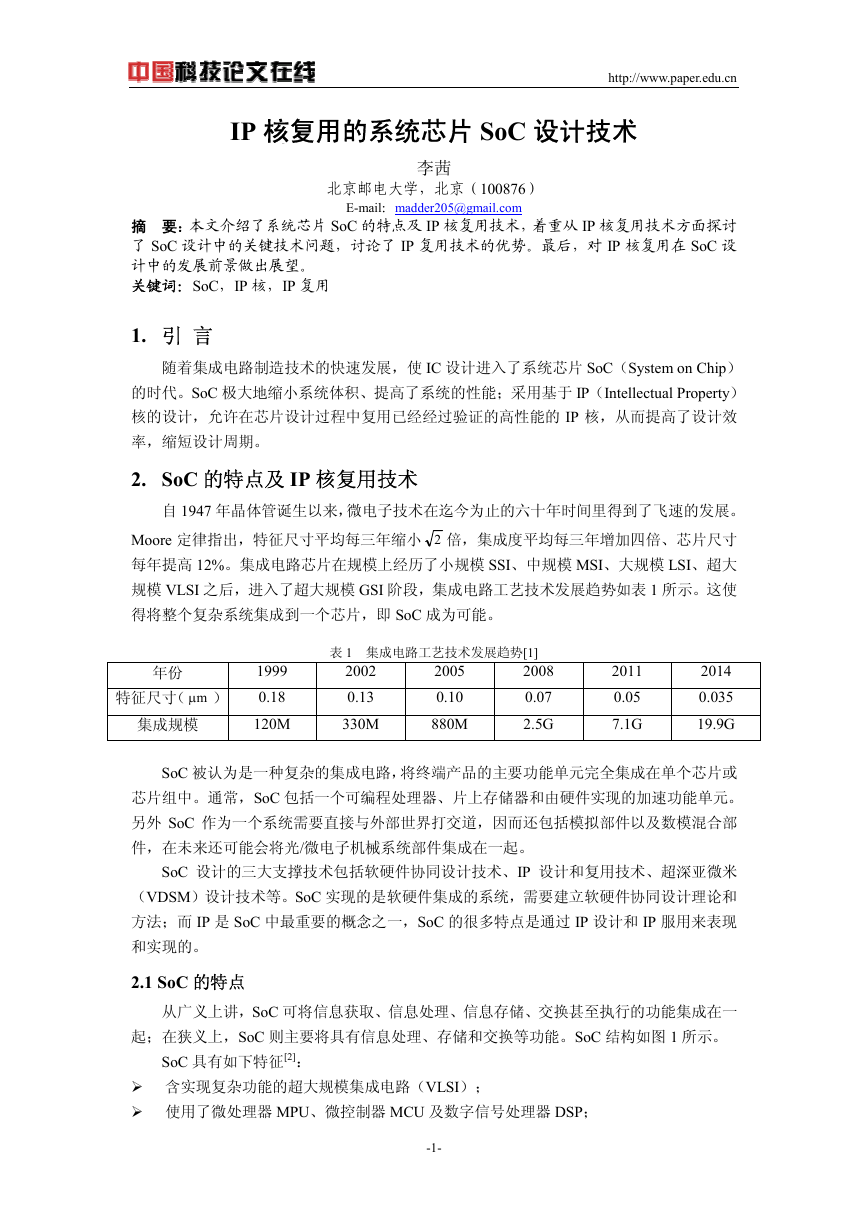

年份

特征尺寸( mµ )

集成规模

1999

0.18

120M

2002

0.13

330M

2008

0.07

2.5G

2011

0.05

7.1G

2014

0.035

19.9G

表 1 集成电路工艺技术发展趋势[1]

2005

0.10

880M

SoC 被认为是一种复杂的集成电路,将终端产品的主要功能单元完全集成在单个芯片或

芯片组中。通常,SoC 包括一个可编程处理器、片上存储器和由硬件实现的加速功能单元。

另外 SoC 作为一个系统需要直接与外部世界打交道,因而还包括模拟部件以及数模混合部

件,在未来还可能会将光/微电子机械系统部件集成在一起。

SoC 设计的三大支撑技术包括软硬件协同设计技术、IP 设计和复用技术、超深亚微米

(VDSM)设计技术等。SoC 实现的是软硬件集成的系统,需要建立软硬件协同设计理论和

方法;而 IP 是 SoC 中最重要的概念之一,SoC 的很多特点是通过 IP 设计和 IP 服用来表现

和实现的。

2.1 SoC 的特点

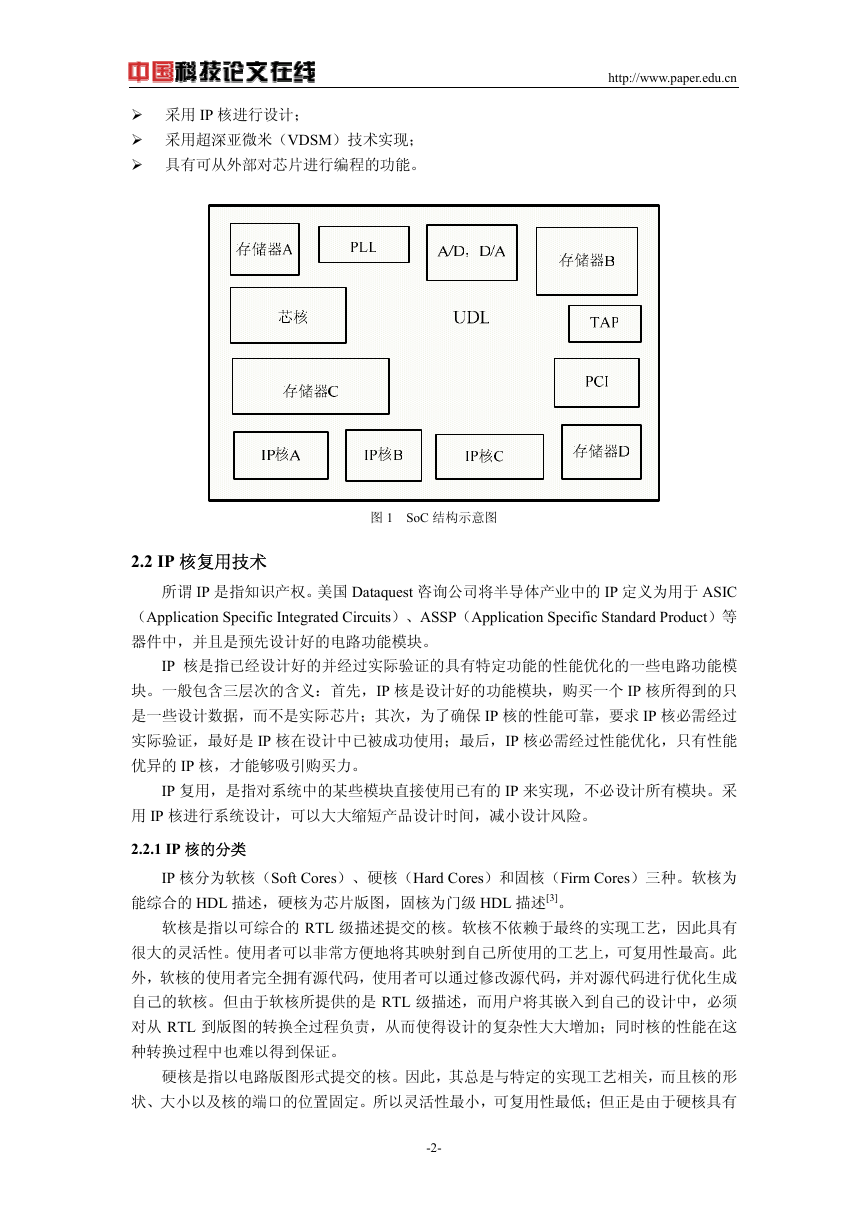

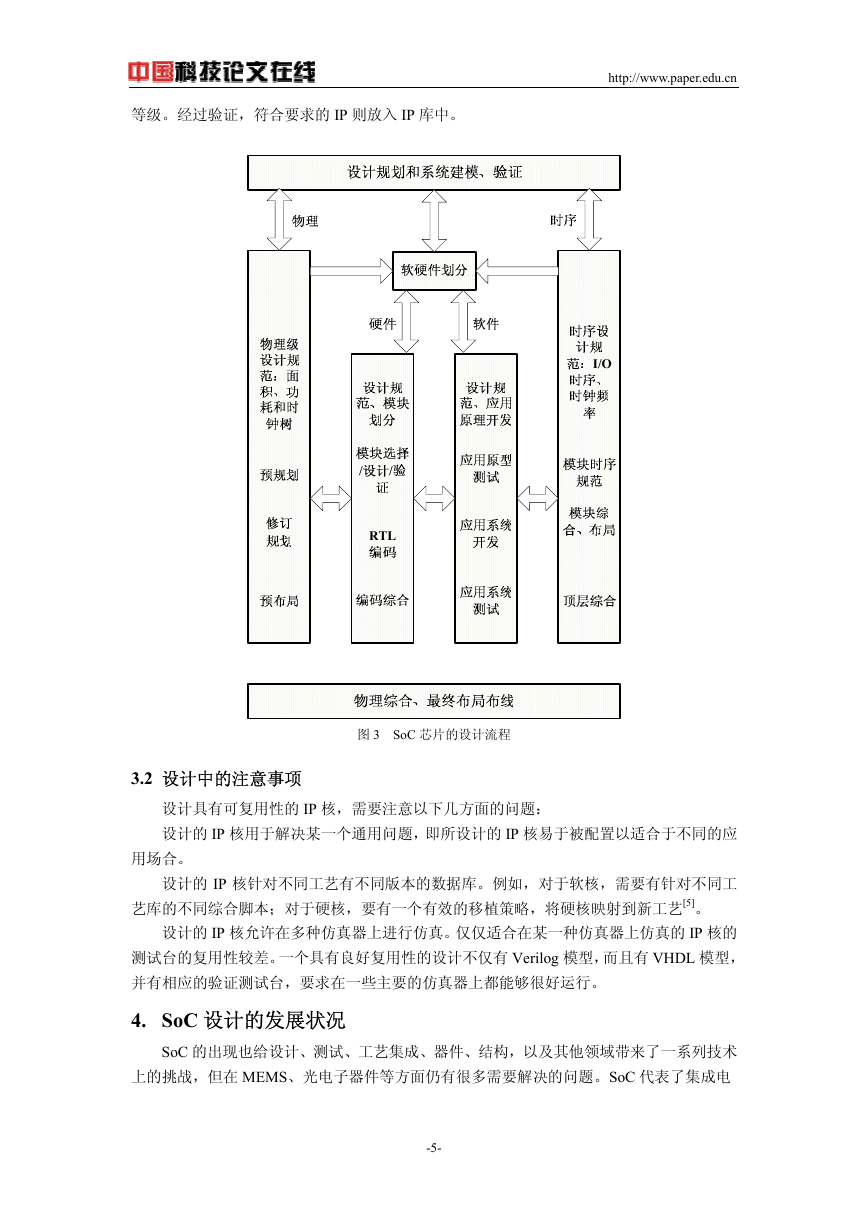

从广义上讲,SoC 可将信息获取、信息处理、信息存储、交换甚至执行的功能集成在一

起;在狭义上,SoC 则主要将具有信息处理、存储和交换等功能。SoC 结构如图 1 所示。

SoC 具有如下特征[2]:

含实现复杂功能的超大规模集成电路(VLSI);

使用了微处理器 MPU、微控制器 MCU 及数字信号处理器 DSP;

-1-

�

采用 IP 核进行设计;

采用超深亚微米(VDSM)技术实现;

具有可从外部对芯片进行编程的功能。

http://www.paper.edu.cn

图 1 SoC 结构示意图

2.2 IP 核复用技术

所谓 IP 是指知识产权。美国 Dataquest 咨询公司将半导体产业中的 IP 定义为用于 ASIC

(Application Specific Integrated Circuits)、ASSP(Application Specific Standard Product)等

器件中,并且是预先设计好的电路功能模块。

IP 核是指已经设计好的并经过实际验证的具有特定功能的性能优化的一些电路功能模

块。一般包含三层次的含义:首先,IP 核是设计好的功能模块,购买一个 IP 核所得到的只

是一些设计数据,而不是实际芯片;其次,为了确保 IP 核的性能可靠,要求 IP 核必需经过

实际验证,最好是 IP 核在设计中已被成功使用;最后,IP 核必需经过性能优化,只有性能

优异的 IP 核,才能够吸引购买力。

IP 复用,是指对系统中的某些模块直接使用已有的 IP 来实现,不必设计所有模块。采

用 IP 核进行系统设计,可以大大缩短产品设计时间,减小设计风险。

2.2.1 IP 核的分类

IP 核分为软核(Soft Cores)、硬核(Hard Cores)和固核(Firm Cores)三种。软核为

能综合的 HDL 描述,硬核为芯片版图,固核为门级 HDL 描述[3]。

软核是指以可综合的 RTL 级描述提交的核。软核不依赖于最终的实现工艺,因此具有

很大的灵活性。使用者可以非常方便地将其映射到自己所使用的工艺上,可复用性最高。此

外,软核的使用者完全拥有源代码,使用者可以通过修改源代码,并对源代码进行优化生成

自己的软核。但由于软核所提供的是 RTL 级描述,而用户将其嵌入到自己的设计中,必须

对从 RTL 到版图的转换全过程负责,从而使得设计的复杂性大大增加;同时核的性能在这

种转换过程中也难以得到保证。

硬核是指以电路版图形式提交的核。因此,其总是与特定的实现工艺相关,而且核的形

状、大小以及核的端口的位置固定。所以灵活性最小,可复用性最低;但正是由于硬核具有

-2-

�

http://www.paper.edu.cn

不可更改性,使得其性能最稳定,可靠性最高。

固核处于软核和硬核之间,一般是以门级网表的形式提交。通常对应于某一特定的实现

工艺,因此,与软核相比,性能更加可靠。此外,固核一般由使用者来完成布局布线,核的

形状、大小以及核的端口的位置不固定,与硬核相比,具有更大的灵活性。但是,固核也有

其自身的弱点,即与实现工艺的相关性以及网表的难读性。与实现工艺的相关性限制了固核

的使用范围;而网表的难读性使得一旦用户在布局布线过程中出现时序违反时,如何排除它

就显得非常困难。三种 IP 核之间的特点如表 2 所示。

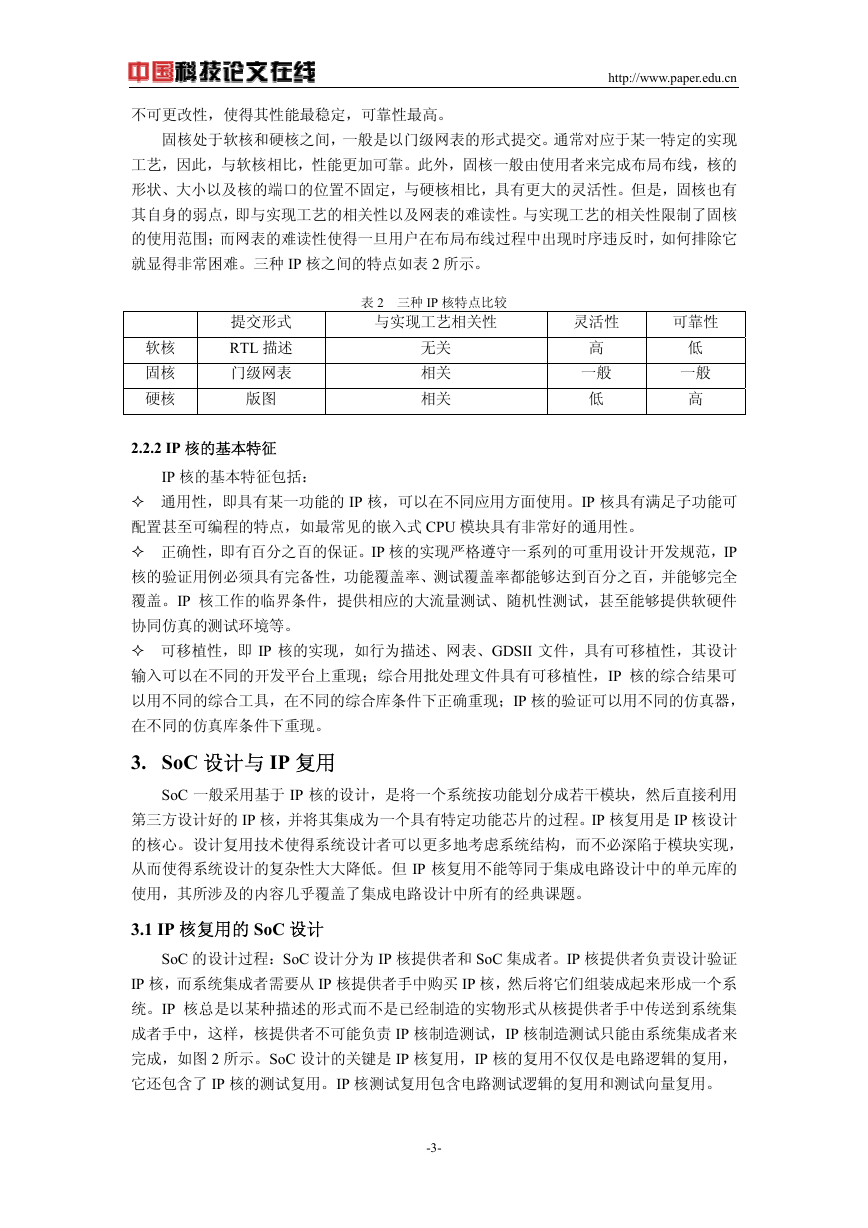

表 2 三种 IP 核特点比较

与实现工艺相关性

无关

相关

相关

灵活性

可靠性

高

一般

低

低

一般

高

软核

固核

硬核

提交形式

RTL 描述

门级网表

版图

2.2.2 IP 核的基本特征

IP 核的基本特征包括:

通用性,即具有某一功能的 IP 核,可以在不同应用方面使用。IP 核具有满足子功能可

配置甚至可编程的特点,如最常见的嵌入式 CPU 模块具有非常好的通用性。

正确性,即有百分之百的保证。IP 核的实现严格遵守一系列的可重用设计开发规范,IP

核的验证用例必须具有完备性,功能覆盖率、测试覆盖率都能够达到百分之百,并能够完全

覆盖。IP 核工作的临界条件,提供相应的大流量测试、随机性测试,甚至能够提供软硬件

协同仿真的测试环境等。

可移植性,即 IP 核的实现,如行为描述、网表、GDSII 文件,具有可移植性,其设计

输入可以在不同的开发平台上重现;综合用批处理文件具有可移植性,IP 核的综合结果可

以用不同的综合工具,在不同的综合库条件下正确重现;IP 核的验证可以用不同的仿真器,

在不同的仿真库条件下重现。

3. SoC 设计与 IP 复用

SoC 一般采用基于 IP 核的设计,是将一个系统按功能划分成若干模块,然后直接利用

第三方设计好的 IP 核,并将其集成为一个具有特定功能芯片的过程。IP 核复用是 IP 核设计

的核心。设计复用技术使得系统设计者可以更多地考虑系统结构,而不必深陷于模块实现,

从而使得系统设计的复杂性大大降低。但 IP 核复用不能等同于集成电路设计中的单元库的

使用,其所涉及的内容几乎覆盖了集成电路设计中所有的经典课题。

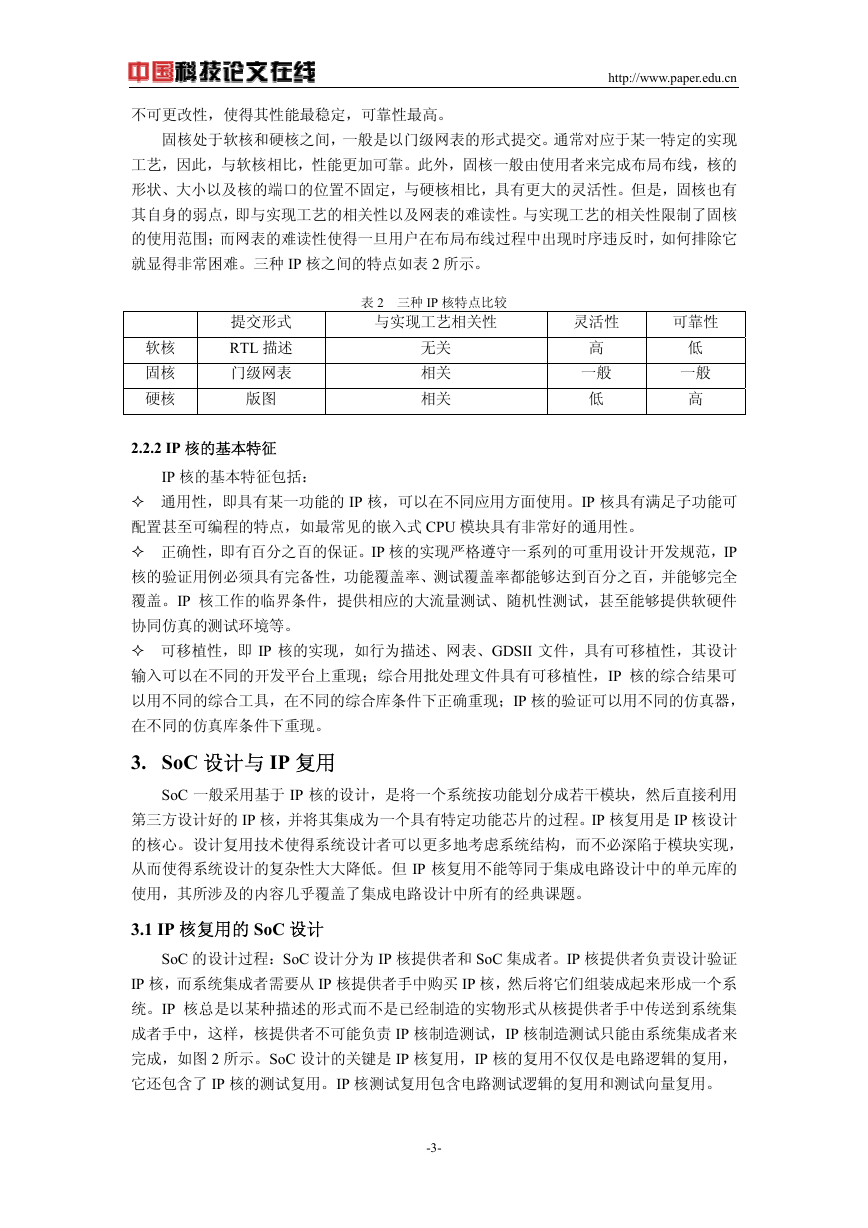

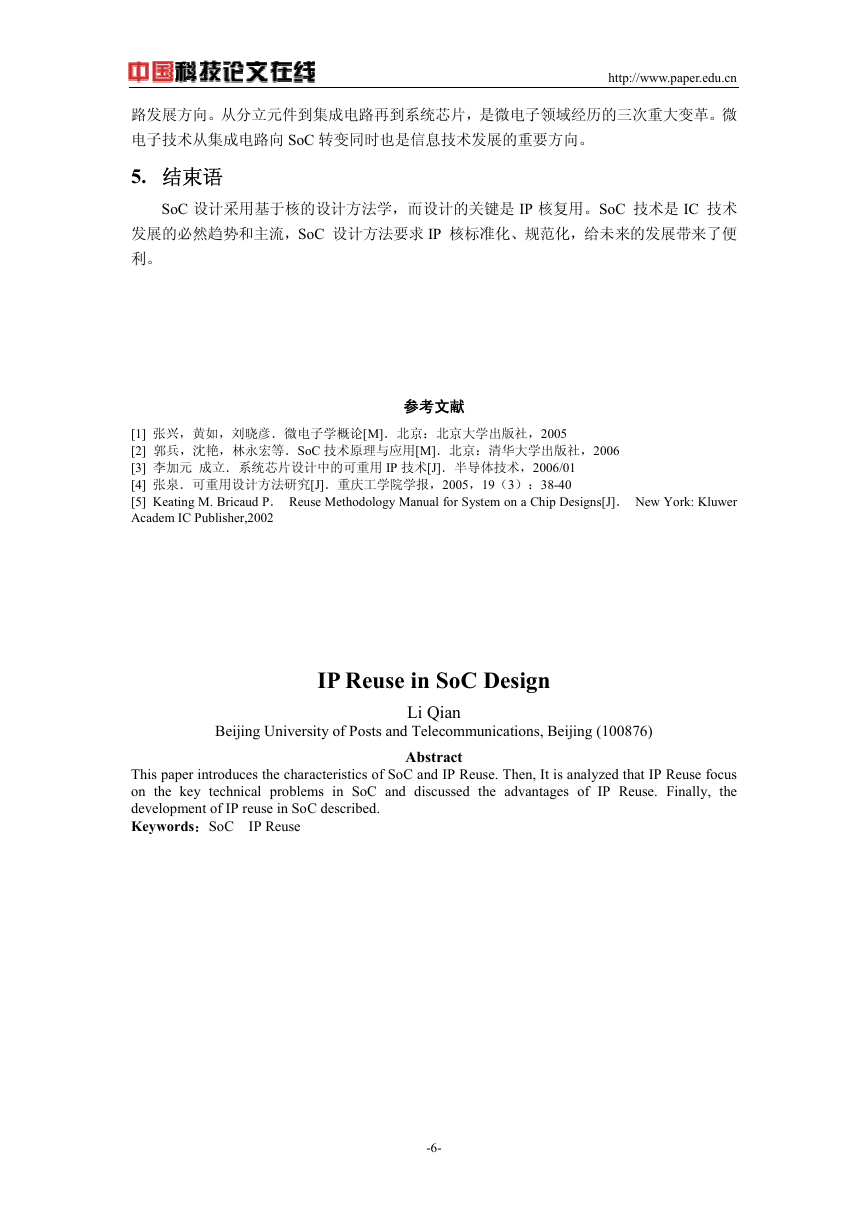

3.1 IP 核复用的 SoC 设计

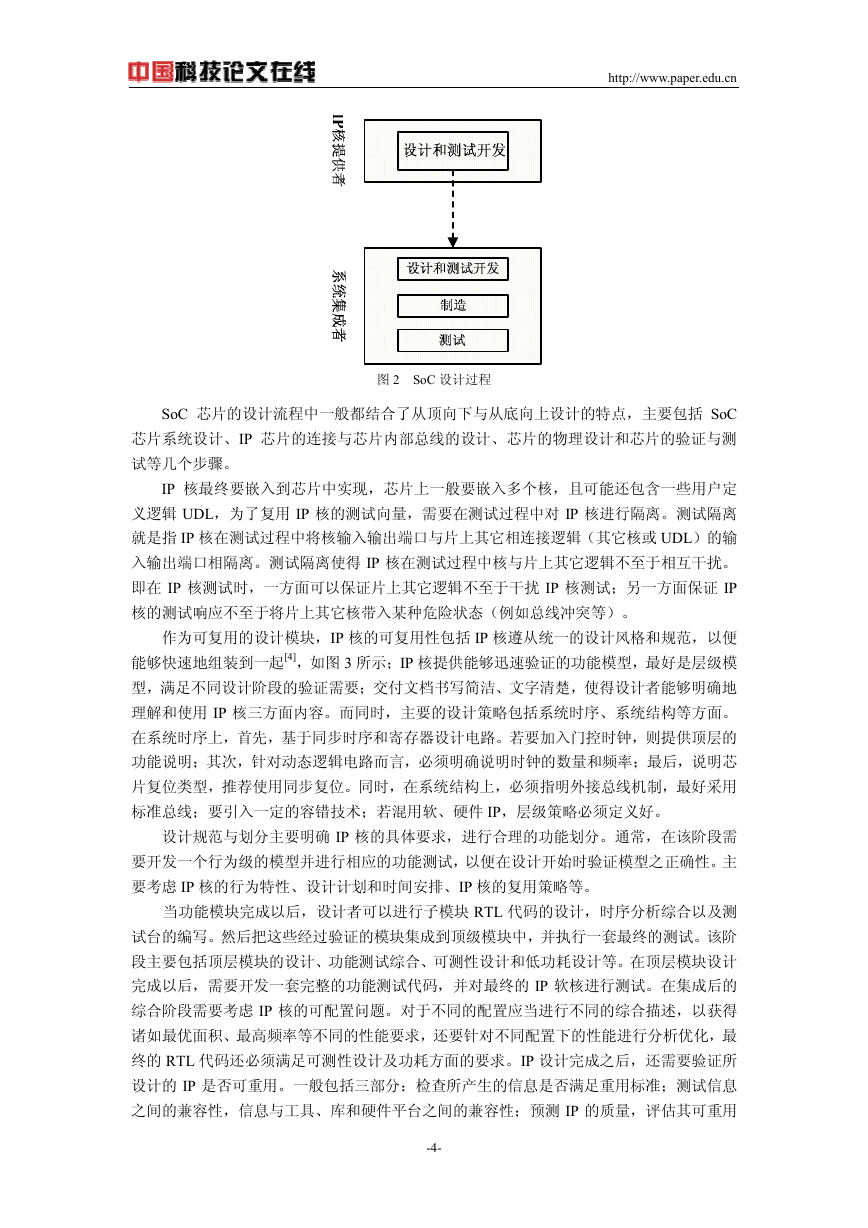

SoC 的设计过程:SoC 设计分为 IP 核提供者和 SoC 集成者。IP 核提供者负责设计验证

IP 核,而系统集成者需要从 IP 核提供者手中购买 IP 核,然后将它们组装成起来形成一个系

统。IP 核总是以某种描述的形式而不是已经制造的实物形式从核提供者手中传送到系统集

成者手中,这样,核提供者不可能负责 IP 核制造测试,IP 核制造测试只能由系统集成者来

完成,如图 2 所示。SoC 设计的关键是 IP 核复用,IP 核的复用不仅仅是电路逻辑的复用,

它还包含了 IP 核的测试复用。IP 核测试复用包含电路测试逻辑的复用和测试向量复用。

-3-

�

http://www.paper.edu.cn

图 2 SoC 设计过程

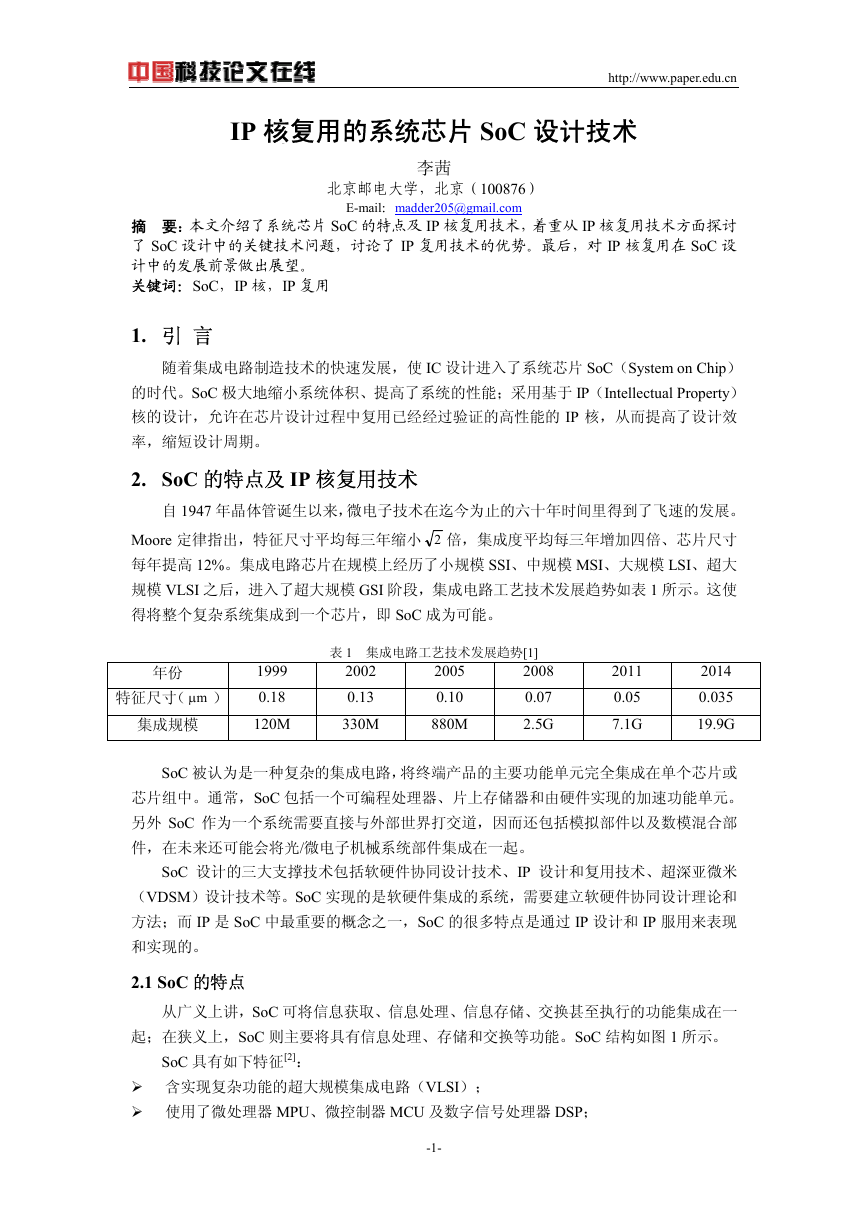

SoC 芯片的设计流程中一般都结合了从顶向下与从底向上设计的特点,主要包括 SoC

芯片系统设计、IP 芯片的连接与芯片内部总线的设计、芯片的物理设计和芯片的验证与测

试等几个步骤。

IP 核最终要嵌入到芯片中实现,芯片上一般要嵌入多个核,且可能还包含一些用户定

义逻辑 UDL,为了复用 IP 核的测试向量,需要在测试过程中对 IP 核进行隔离。测试隔离

就是指 IP 核在测试过程中将核输入输出端口与片上其它相连接逻辑(其它核或 UDL)的输

入输出端口相隔离。测试隔离使得 IP 核在测试过程中核与片上其它逻辑不至于相互干扰。

即在 IP 核测试时,一方面可以保证片上其它逻辑不至于干扰 IP 核测试;另一方面保证 IP

核的测试响应不至于将片上其它核带入某种危险状态(例如总线冲突等)。

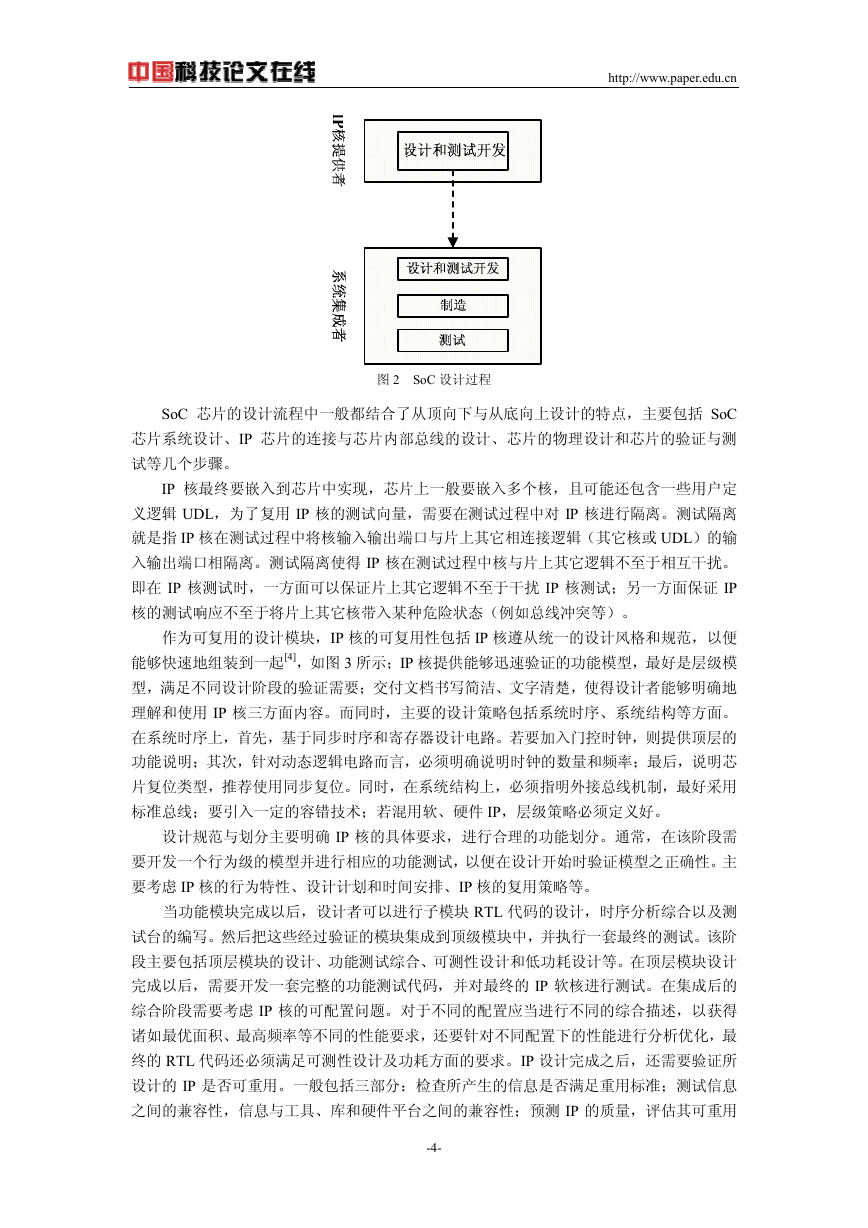

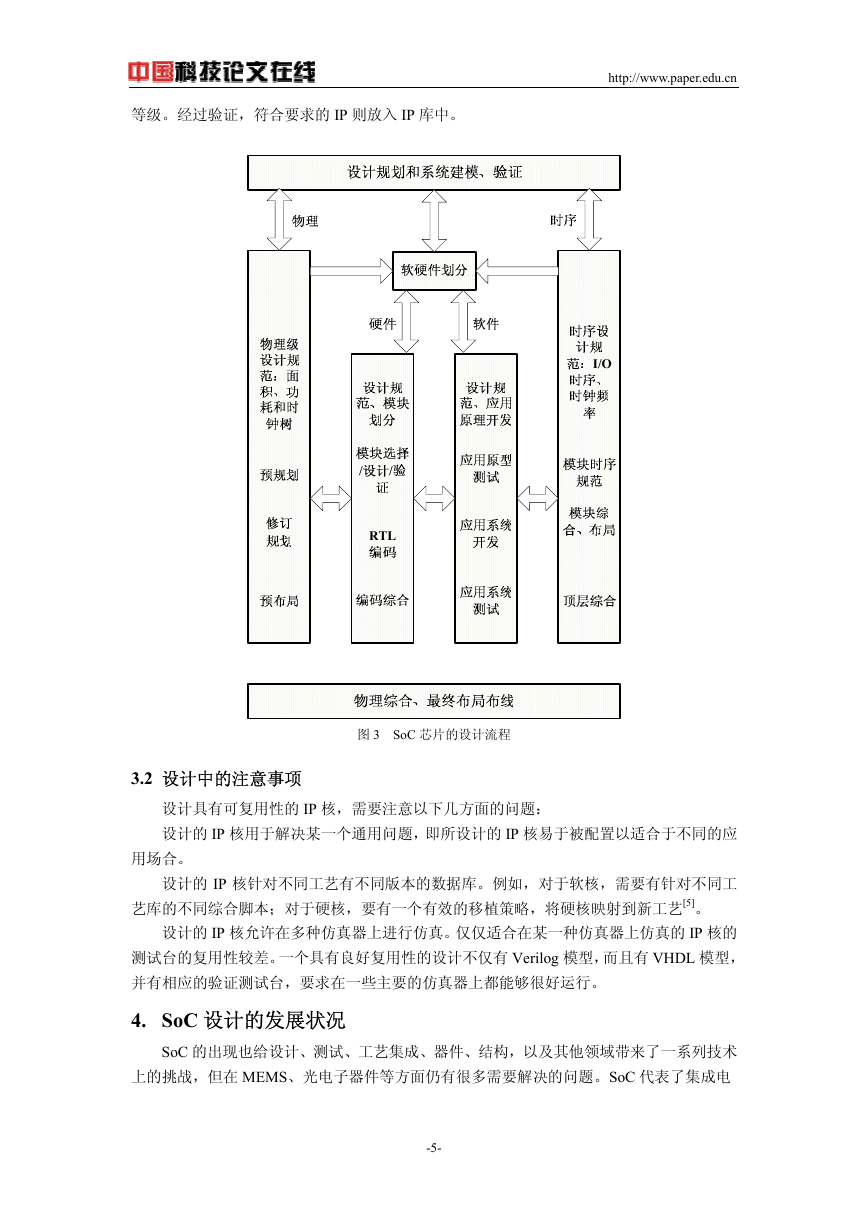

作为可复用的设计模块,IP 核的可复用性包括 IP 核遵从统一的设计风格和规范,以便

能够快速地组装到一起[4],如图 3 所示;IP 核提供能够迅速验证的功能模型,最好是层级模

型,满足不同设计阶段的验证需要;交付文档书写简洁、文字清楚,使得设计者能够明确地

理解和使用 IP 核三方面内容。而同时,主要的设计策略包括系统时序、系统结构等方面。

在系统时序上,首先,基于同步时序和寄存器设计电路。若要加入门控时钟,则提供顶层的

功能说明;其次,针对动态逻辑电路而言,必须明确说明时钟的数量和频率;最后,说明芯

片复位类型,推荐使用同步复位。同时,在系统结构上,必须指明外接总线机制,最好采用

标准总线;要引入一定的容错技术;若混用软、硬件 IP,层级策略必须定义好。

设计规范与划分主要明确 IP 核的具体要求,进行合理的功能划分。通常,在该阶段需

要开发一个行为级的模型并进行相应的功能测试,以便在设计开始时验证模型之正确性。主

要考虑 IP 核的行为特性、设计计划和时间安排、IP 核的复用策略等。

当功能模块完成以后,设计者可以进行子模块 RTL 代码的设计,时序分析综合以及测

试台的编写。然后把这些经过验证的模块集成到顶级模块中,并执行一套最终的测试。该阶

段主要包括顶层模块的设计、功能测试综合、可测性设计和低功耗设计等。在顶层模块设计

完成以后,需要开发一套完整的功能测试代码,并对最终的 IP 软核进行测试。在集成后的

综合阶段需要考虑 IP 核的可配置问题。对于不同的配置应当进行不同的综合描述,以获得

诸如最优面积、最高频率等不同的性能要求,还要针对不同配置下的性能进行分析优化,最

终的 RTL 代码还必须满足可测性设计及功耗方面的要求。IP 设计完成之后,还需要验证所

设计的 IP 是否可重用。一般包括三部分:检查所产生的信息是否满足重用标准;测试信息

之间的兼容性,信息与工具、库和硬件平台之间的兼容性;预测 IP 的质量,评估其可重用

-4-

�

等级。经过验证,符合要求的 IP 则放入 IP 库中。

http://www.paper.edu.cn

I/O

/

/

RTL

图 3 SoC 芯片的设计流程

3.2 设计中的注意事项

设计具有可复用性的 IP 核,需要注意以下几方面的问题:

设计的 IP 核用于解决某一个通用问题,即所设计的 IP 核易于被配置以适合于不同的应

用场合。

设计的 IP 核针对不同工艺有不同版本的数据库。例如,对于软核,需要有针对不同工

艺库的不同综合脚本;对于硬核,要有一个有效的移植策略,将硬核映射到新工艺[5]。

设计的 IP 核允许在多种仿真器上进行仿真。仅仅适合在某一种仿真器上仿真的 IP 核的

测试台的复用性较差。一个具有良好复用性的设计不仅有 Verilog 模型,而且有 VHDL 模型,

并有相应的验证测试台,要求在一些主要的仿真器上都能够很好运行。

4. SoC 设计的发展状况

SoC 的出现也给设计、测试、工艺集成、器件、结构,以及其他领域带来了一系列技术

上的挑战,但在 MEMS、光电子器件等方面仍有很多需要解决的问题。SoC 代表了集成电

-5-

�

http://www.paper.edu.cn

路发展方向。从分立元件到集成电路再到系统芯片,是微电子领域经历的三次重大变革。微

电子技术从集成电路向 SoC 转变同时也是信息技术发展的重要方向。

5. 结束语

SoC 设计采用基于核的设计方法学,而设计的关键是 IP 核复用。SoC 技术是 IC 技术

发展的必然趋势和主流,SoC 设计方法要求 IP 核标准化、规范化,给未来的发展带来了便

利。

参考文献

[1] 张兴,黄如,刘晓彦.微电子学概论[M].北京:北京大学出版社,2005

[2] 郭兵,沈艳,林永宏等.SoC 技术原理与应用[M].北京:清华大学出版社,2006

[3] 李加元 成立.系统芯片设计中的可重用 IP 技术[J].半导体技术,2006/01

[4] 张泉.可重用设计方法研究[J].重庆工学院学报,2005,19(3):38-40

[5] Keating M. Bricaud P. Reuse Methodology Manual for System on a Chip Designs[J]. New York: Kluwer

Academ IC Publisher,2002

IP Reuse in SoC Design

Beijing University of Posts and Telecommunications, Beijing (100876)

Li Qian

This paper introduces the characteristics of SoC and IP Reuse. Then, It is analyzed that IP Reuse focus

on the key technical problems in SoC and discussed the advantages of IP Reuse. Finally, the

development of IP reuse in SoC described.

Keywords:SoC IP Reuse

Abstract

-6-

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc