数字IC低功耗设计综述

数字IC低功耗设计综述

梁允萍 章成旻 李烨

摘 要 数字IC的低功耗设计是一个系统问题,必须在设计的各个层次上发展适当的技术,综合应用不同的设计策略,才

能达到在降低功耗的同时还能维持较高的系统性能的目的。本文系统地总结了当前系统级芯片设计中的低功耗技术,并对

不同设计层次的功耗优化方法分别进行了讨论。

关键词 低功耗;时钟门控;多阈值电压;电源门控

1 引言

对便携式、电池供电等电子系统的市场需求,

使得低功耗技术从上世纪九十年代开始受到广泛关

注并迅速发展起来。一直以来,集成度和性能都是

衡量集成电路设计的两个关键因素。但随着芯片集

成度和设计复杂度的提升,IC芯片面临着日益严重

的热量管理的挑战,即使采用节省功耗的CMOS电

路也难以解决这一问题。可以说,功耗指标已经成

为芯片设计中的又一关键因素。动态功耗是IC功耗

的主要组成部分,但随着深亚微米工艺的发展,之

前微不足道的漏电流功耗呈指数级增大,甚至有超

越动态功耗的趋势,这也使得新兴低功耗技术的研

究显得更加重要和紧迫。

本文第二部分将首先介绍芯片功耗的主要来

源、基本概念及其影响因素;针对这些功耗来源和

影响因素,文章第三部分将分别考虑IC设计中不同

抽象层次对电路功耗的影响,并比较各项低功耗技

术的效果和存在的问题。

2 电路功耗分析

研究低功耗技术,我们首先要分析功耗的来

源。CMOS是当今使用最普遍的IC设计工艺。在一

个CMOS电路中,功耗主要有三部分[1]:

/

/

P

ShortCircu

it

PP

Switching

P

P

ShortCircu

it

Leakage

2

ACV

f

short VI

leak

f A

(2)

2

f

AVI

其中f是系统的频率;A是跳变因子,即整个电路的平

均翻转比例;C是门电路的总电容; V是供电电压;

P

Leakage

C V

short VI

AVI

(1)

leak

C V

是电平信号上升/下降的时间。

V

th

VA

(

dd

3)

公式(1)中,P是一个CMOS电路的总功耗;

VA

(

PSwitch是跳变功耗,也叫动态功耗,是器件在工作过

dd

AVI

short

3)

V

th

PP

Switching

ACV

f A

AVI

short

VI

Ve

leak

qv

th

nkT

qv

th

nkT

Ve

leak

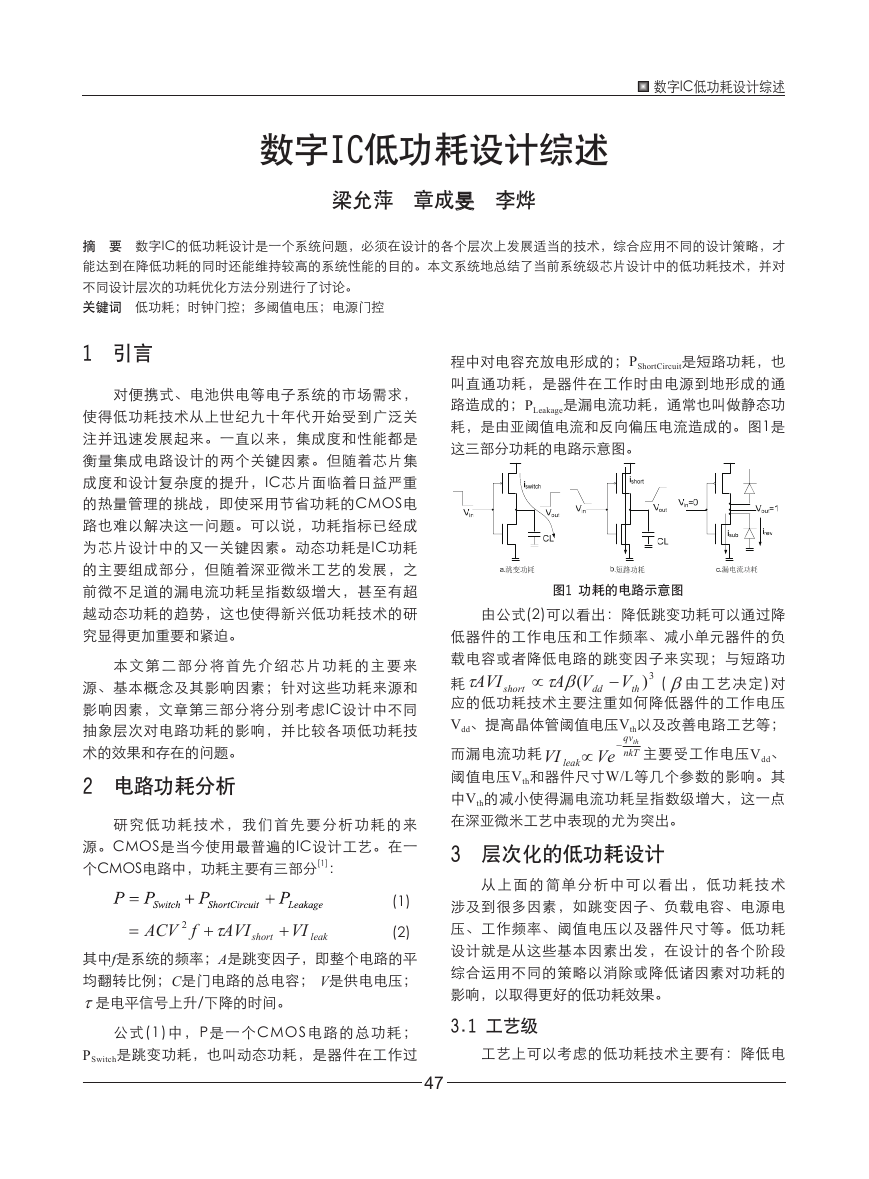

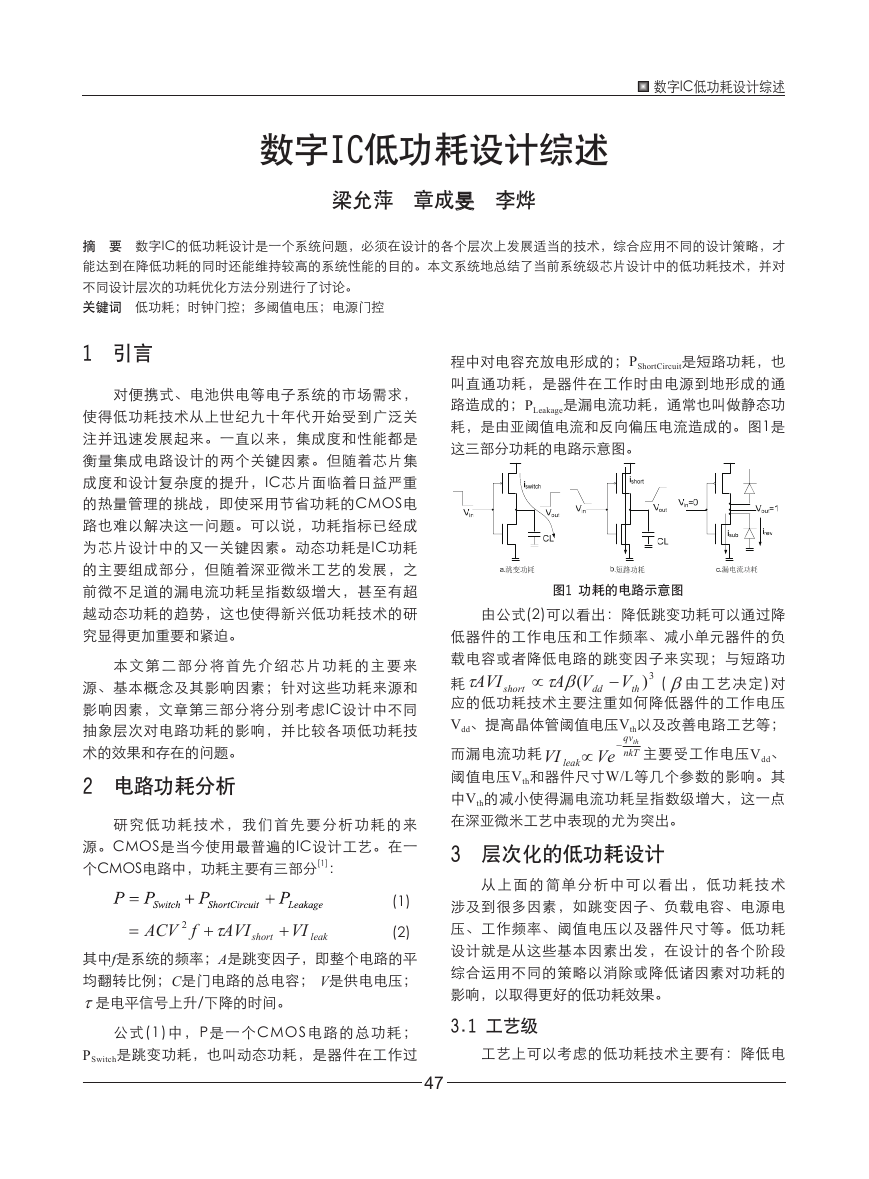

程中对电容充放电形成的;PShortCircuit是短路功耗,也

叫直通功耗,是器件在工作时由电源到地形成的通

路造成的;PLeakage是漏电流功耗,通常也叫做静态功

耗,是由亚阈值电流和反向偏压电流造成的。图1是

这三部分功耗的电路示意图。

/

/

AVI

ACV

f A

PP

2

f

PP

Switching

PP

P

P

Switching

it

Leakage

ShortCircu

P

P

2

ACV

f

it

ShortCircu

Switching

Leakage

/

2

ACV

f

short VI

AVI

leak

short VI

AVI

f A

C V

图1 功耗的电路示意图

leak

f A

C V

由公式(2)可以看出:降低跳变功耗可以通过降

C V

低器件的工作电压和工作频率、减小单元器件的负

VA

AVI

(

short

3)

V

AVI

载电容或者降低电路的跳变因子来实现;与短路功

th

short

dd

VA

(

耗

由工艺决定)对

应的低功耗技术主要注重如何降低器件的工作电压

Vdd、提高晶体管阈值电压Vth以及改善电路工艺等;

而漏电流功耗

主要受工作电压Vdd、

VI

qv

th

阈值电压Vth和器件尺寸W/L等几个参数的影响。其

Ve

nkT

中Vth的减小使得漏电流功耗呈指数级增大,这一点

在深亚微米工艺中表现的尤为突出。

VA

(

3)

V

(

th

AVI

qv

th

nkT

qv

th

nkT

Ve

Ve

VI

VI

short

leak

leak

leak

dd

P

ShortCircu

it

P

Leakage

short VI

leak

V

th

3)

dd

3 层次化的低功耗设计

从上面的简单分析中可以看出,低功耗技术

涉及到很多因素,如跳变因子、负载电容、电源电

压、工作频率、阈值电压以及器件尺寸等。低功耗

设计就是从这些基本因素出发,在设计的各个阶段

综合运用不同的策略以消除或降低诸因素对功耗的

影响,以取得更好的低功耗效果。

3.1 工艺级

工艺上可以考虑的低功耗技术主要有:降低电

47

�

源电压,减小晶体管尺寸,增加金属层数以及采用

其它特殊工艺等。

电源电压随着工艺水平的提高不断降低,为

满足性能的要求,阈值电压也随之不断的降低。然

而,阈值电压的减小会导致泄漏电流呈指数级增

长,而且越来越薄的栅氧化层也使得栅沟道泄漏电

流不断加大。在90nm和更先进的工艺下,泄漏功

耗的处理成为芯片设计中的主要部分。针对这一问

题,可以采用一些特殊工艺如绝缘体上硅(Silicon on

Insulator,SOI)工艺、多阈值工艺和变阈值工艺等

[2]。多阈值工艺在关键路径上采用阈值较低的器件,

而在非关键路径上用高阈值器件,虽然会因此增大

延迟,但可换得漏电流功耗的降低;变阈值工艺通

过动态地改变衬底偏置电压以改变阈值,同样可降

低漏电流功耗。

采用先进的工艺,能获得更小的晶体管尺寸,

有助于减小互连线长度和开关电容,从而有助于降低

电路功耗[3]。同样地,多层金属布线可以避免使用大

范围连线,减少开关电容降低功耗。但是多层金属会

导致耦合寄生电容的增加,抵消部分降低的功耗。

3.2 版图级

3.2.1 布局布线

以前,布局布线技术大多只需要考虑面积和延

时的因素[4],进入深亚微米工艺后,互连线的功耗逐

渐成为整个电路功耗的主要部分,布局布线也就成

为低功耗设计需要考虑的一个方面。布线时应考虑

将开关频繁的路径设为高优先级,同时减小互连线

的长度以降低整体功耗。

时钟树是数字电路中最大的负载网络,其功耗

可达系统功耗的40%。时钟树生成时,可以在保证

时序约束的条件下,对时钟树的结构、驱动方式进

行选择,并通过缓冲器的插入和尺寸优化来减小功

耗。另外,在对同步时钟容差分析的基础上,不再

追求时钟偏移最小化,而是在保证电路时序的条件

下减小功耗。

3.3 电路级

电路级低功耗设计主要针对跳变功耗,涉及电

源电压、物理电容和开关频率等几个方面。

由于动态功耗和电源电压呈二次方关系,所

以减少电源电压是降低跳变功耗最有效的方法,不

Vol. 3 No.4 / Apr. 2009

过,降低电源电压会使得延迟增加、性能下降。作

为折中,可以在阈值电压不变的情况下,采取多电

源电压(Multi Supply Multi Voltage, MSMV)的方

法。即在系统的关键时序路径上,采用较高的电源

电压保证整个系统的性能,而在其它路径上,采用

低的电源电压以减少功耗。不过,电平转换电路的

增加是其主要的制约因素。

CMOS数字电路的物理电容大致有三种:栅电

容、扩散电容和连线电容。降低这三种电容,则对

应的节点的功耗也随之降低。栅电容和扩散电容主

要是由所选的工艺的单元库决定的,而连线电容则

受后端设计的布局布线的影响。

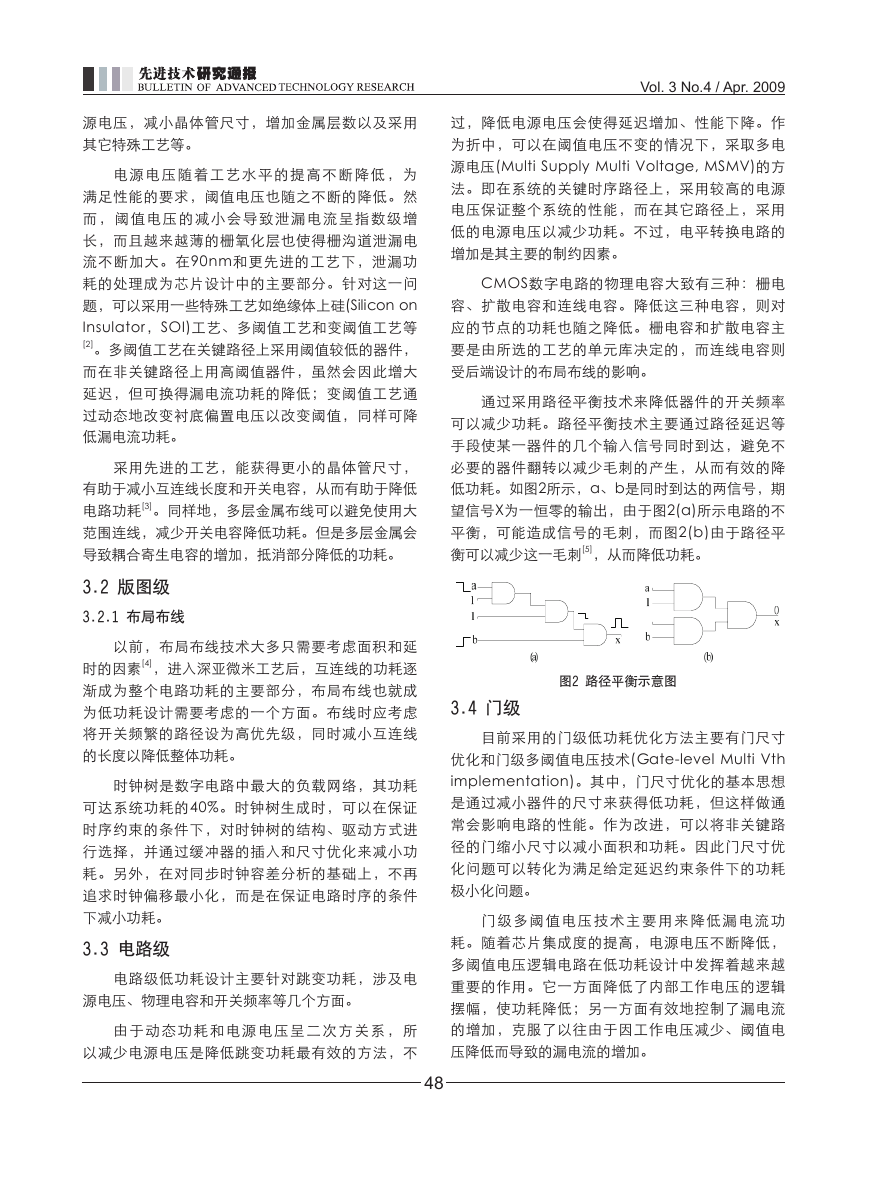

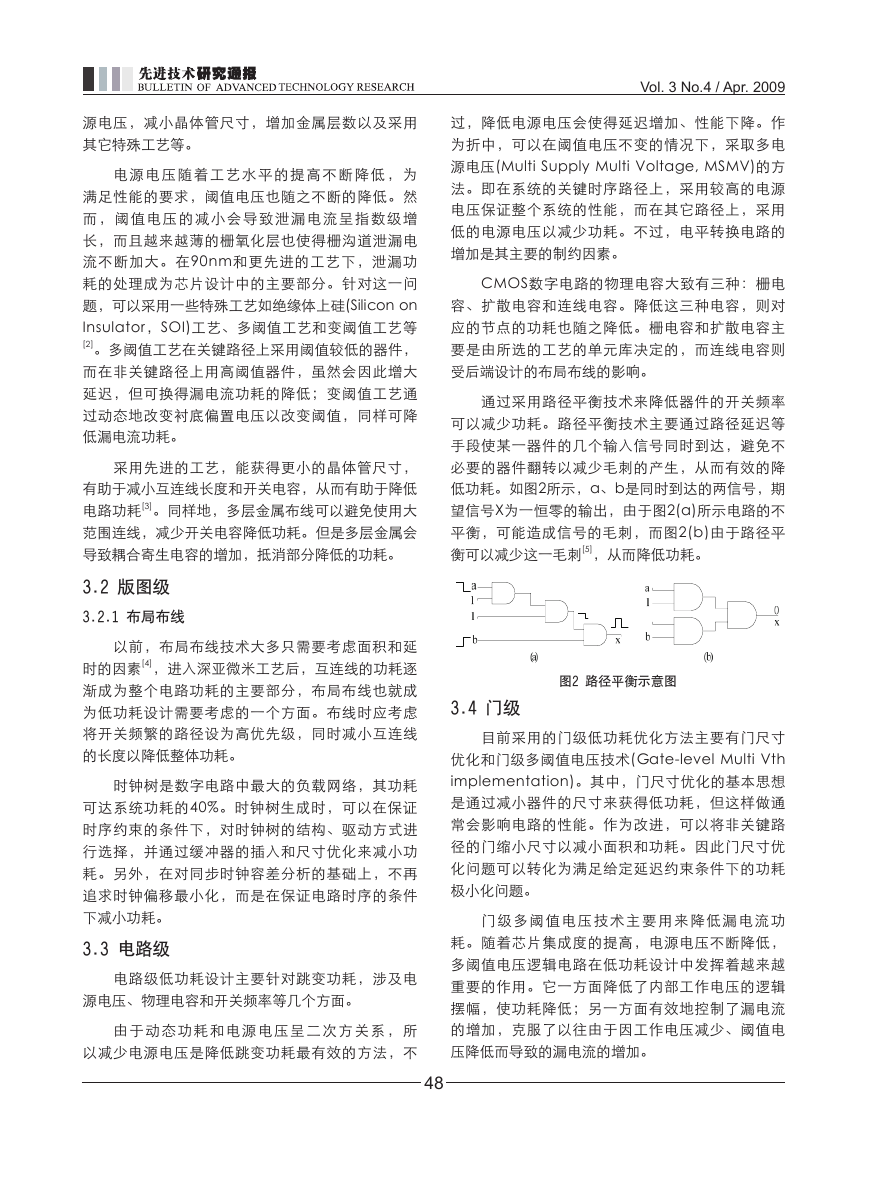

通过采用路径平衡技术来降低器件的开关频率

可以减少功耗。路径平衡技术主要通过路径延迟等

手段使某一器件的几个输入信号同时到达,避免不

必要的器件翻转以减少毛刺的产生,从而有效的降

低功耗。如图2所示,a、b是同时到达的两信号,期

望信号X为一恒零的输出,由于图2(a)所示电路的不

平衡,可能造成信号的毛刺,而图2(b)由于路径平

衡可以减少这一毛刺[5],从而降低功耗。

图2 路径平衡示意图

3.4 门级

目前采用的门级低功耗优化方法主要有门尺寸

优化和门级多阈值电压技术(Gate-level Multi Vth

implementation)。其中,门尺寸优化的基本思想

是通过减小器件的尺寸来获得低功耗,但这样做通

常会影响电路的性能。作为改进,可以将非关键路

径的门缩小尺寸以减小面积和功耗。因此门尺寸优

化问题可以转化为满足给定延迟约束条件下的功耗

极小化问题。

门级多阈值电压技术主要用来降低漏电流功

耗。随着芯片集成度的提高,电源电压不断降低,

多阈值电压逻辑电路在低功耗设计中发挥着越来越

重要的作用。它一方面降低了内部工作电压的逻辑

摆幅,使功耗降低;另一方面有效地控制了漏电流

的增加,克服了以往由于因工作电压减少、阈值电

压降低而导致的漏电流的增加。

48

�

3.5 寄存器传输(RTL)级

RTL级低功耗技术主要通过减少寄存器不希望的

跳变(glitch--Spurious switch)来降低功耗。这种跳变

虽然对电路的逻辑功能没有负面的影响,但会导致跳

变因子A的增加,从而导致功耗的增加。减少glitch

的方法主要是消除其产生的条件,如用时钟信号同

步、结构重构以及时钟门控(Clock Gating)等。

在电路中插入由时钟信号控制的寄存器将待传

递的信号同步[6],可以将寄存器前面的glitch阻隔在

寄存器外,避免其层层传递累积。但此时需要权衡

引入时钟树和寄存器增加的功耗和面积与得到的改

善相比是否值得。

结构重构是利用在电路中插入缓冲器或冗余电

路的方法来消除由于路径延迟不同而引起的glitch,

消除glitch对输出的影响,而且不改变原电路实现的

功能。不过,冗余电路本身会增加一定的功耗。

数字电路中,时钟的翻转必然会引起各时序单

元的动作,使得相同的输入值在每个时钟周期都被

重复加载进后面的寄存器中,使后面的寄存器、时

钟网络和多选器产生不必要的功耗。插入门控电路

可以将寄存器的时钟关闭,防止时钟触发寄存器,

大幅度降低功耗[7]。时钟门控[8]技术可以说是当前最

有效的低功耗技术,可以减少30% ~ 40%的功耗。时

钟门控技术可以作用于局部电路或一个模块,也可

以作用于整个电路。作用范围越大,功耗减少越显

著,但是门控时钟的插入可以引起时钟脉冲相位差

不平衡和额外的插入延迟。

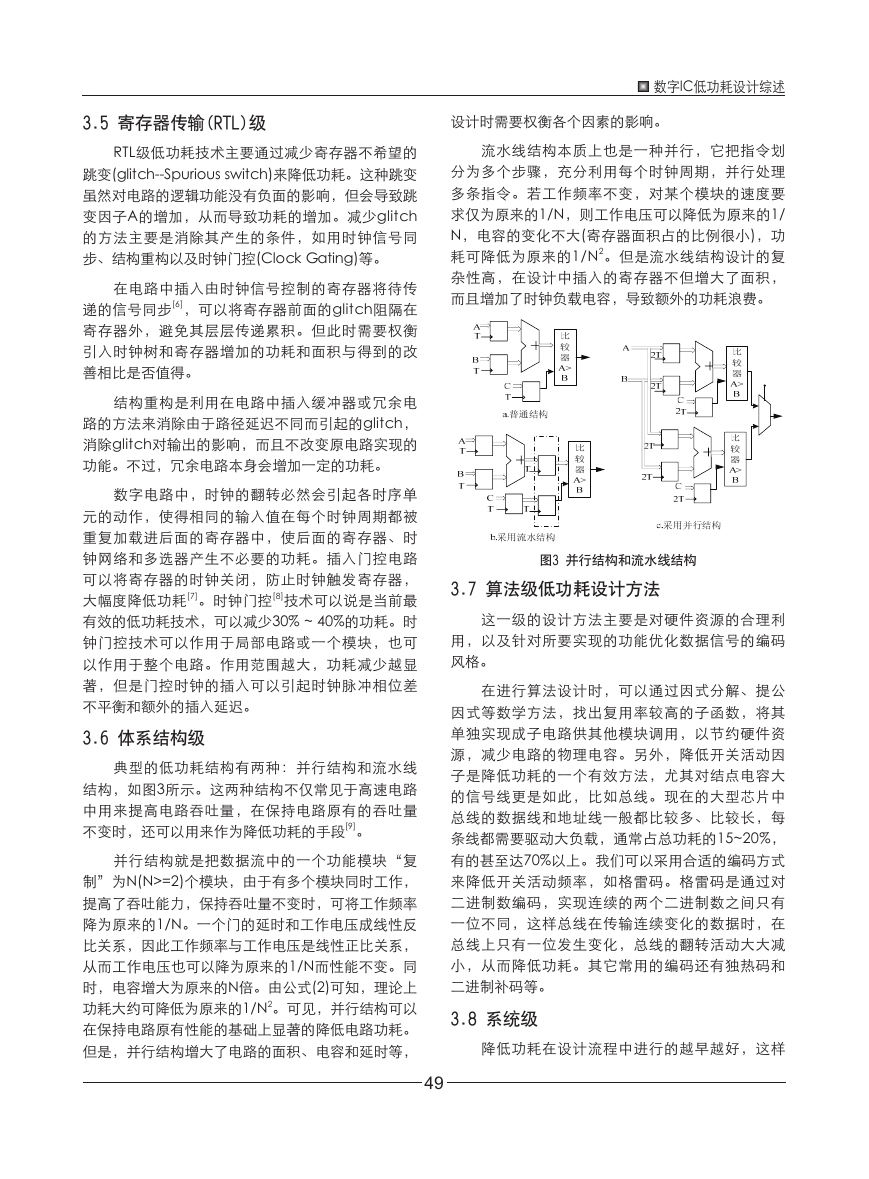

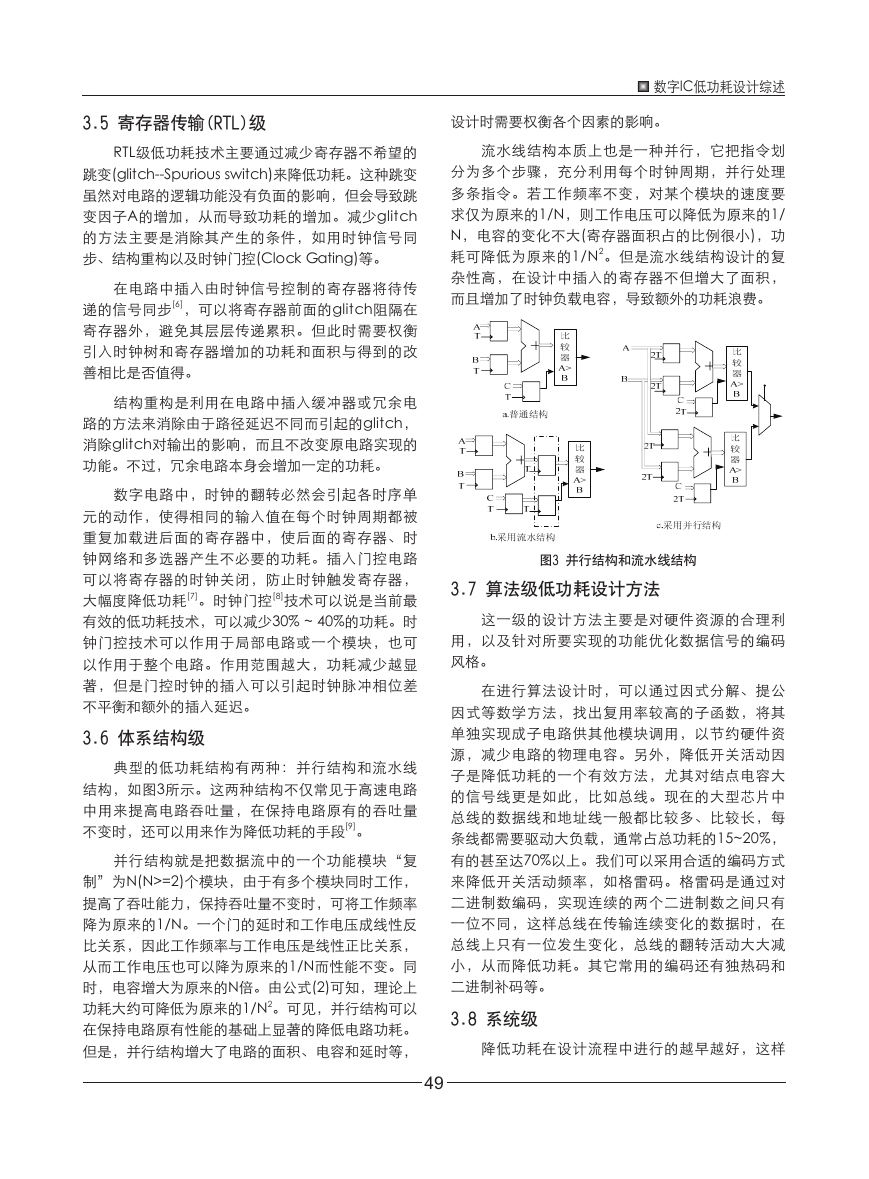

3.6 体系结构级

典型的低功耗结构有两种:并行结构和流水线

结构,如图3所示。这两种结构不仅常见于高速电路

中用来提高电路吞吐量,在保持电路原有的吞吐量

不变时,还可以用来作为降低功耗的手段[9]。

并行结构就是把数据流中的一个功能模块“复

制”为N(N>=2)个模块,由于有多个模块同时工作,

提高了吞吐能力,保持吞吐量不变时,可将工作频率

降为原来的1/N。一个门的延时和工作电压成线性反

比关系,因此工作频率与工作电压是线性正比关系,

从而工作电压也可以降为原来的1/N而性能不变。同

时,电容增大为原来的N倍。由公式(2)可知,理论上

功耗大约可降低为原来的1/N2。可见,并行结构可以

在保持电路原有性能的基础上显著的降低电路功耗。

但是,并行结构增大了电路的面积、电容和延时等,

数字IC低功耗设计综述

设计时需要权衡各个因素的影响。

流水线结构本质上也是一种并行,它把指令划

分为多个步骤,充分利用每个时钟周期,并行处理

多条指令。若工作频率不变,对某个模块的速度要

求仅为原来的1/N,则工作电压可以降低为原来的1/

N,电容的变化不大(寄存器面积占的比例很小),功

耗可降低为原来的1/N2。但是流水线结构设计的复

杂性高,在设计中插入的寄存器不但增大了面积,

而且增加了时钟负载电容,导致额外的功耗浪费。

图3 并行结构和流水线结构

3.7 算法级低功耗设计方法

这一级的设计方法主要是对硬件资源的合理利

用,以及针对所要实现的功能优化数据信号的编码

风格。

在进行算法设计时,可以通过因式分解、提公

因式等数学方法,找出复用率较高的子函数,将其

单独实现成子电路供其他模块调用,以节约硬件资

源,减少电路的物理电容。另外,降低开关活动因

子是降低功耗的一个有效方法,尤其对结点电容大

的信号线更是如此,比如总线。现在的大型芯片中

总线的数据线和地址线一般都比较多、比较长,每

条线都需要驱动大负载,通常占总功耗的15~20%,

有的甚至达70%以上。我们可以采用合适的编码方式

来降低开关活动频率,如格雷码。格雷码是通过对

二进制数编码,实现连续的两个二进制数之间只有

一位不同,这样总线在传输连续变化的数据时,在

总线上只有一位发生变化,总线的翻转活动大大减

小,从而降低功耗。其它常用的编码还有独热码和

二进制补码等。

3.8 系统级

降低功耗在设计流程中进行的越早越好,这样

49

�

可以有效地降低功耗预算,避免重新设计带来的成

本浪费。系统级的低功耗技术主要有动态电源电压

管理(DVS),动态阈值调节(DTS)和休眠模式(Sleep

Mode)下的节能问题等几个方面[10]。

动态电源电压管理类似于前面提到的降低电源

电压技术,所不同的在于它是根据工作负荷动态地

调整电源电压,而不是硬性地划分模块电源电压,

因此,具有很强的灵活性。动态阈值调节主要针对

降低电路漏电流,和前者相似,也是根据实际工作

速度来动态调节管子的阈值电压。不过要动态地改

变阈值电压,需要自适应体偏置,这要用到三阱工

艺。

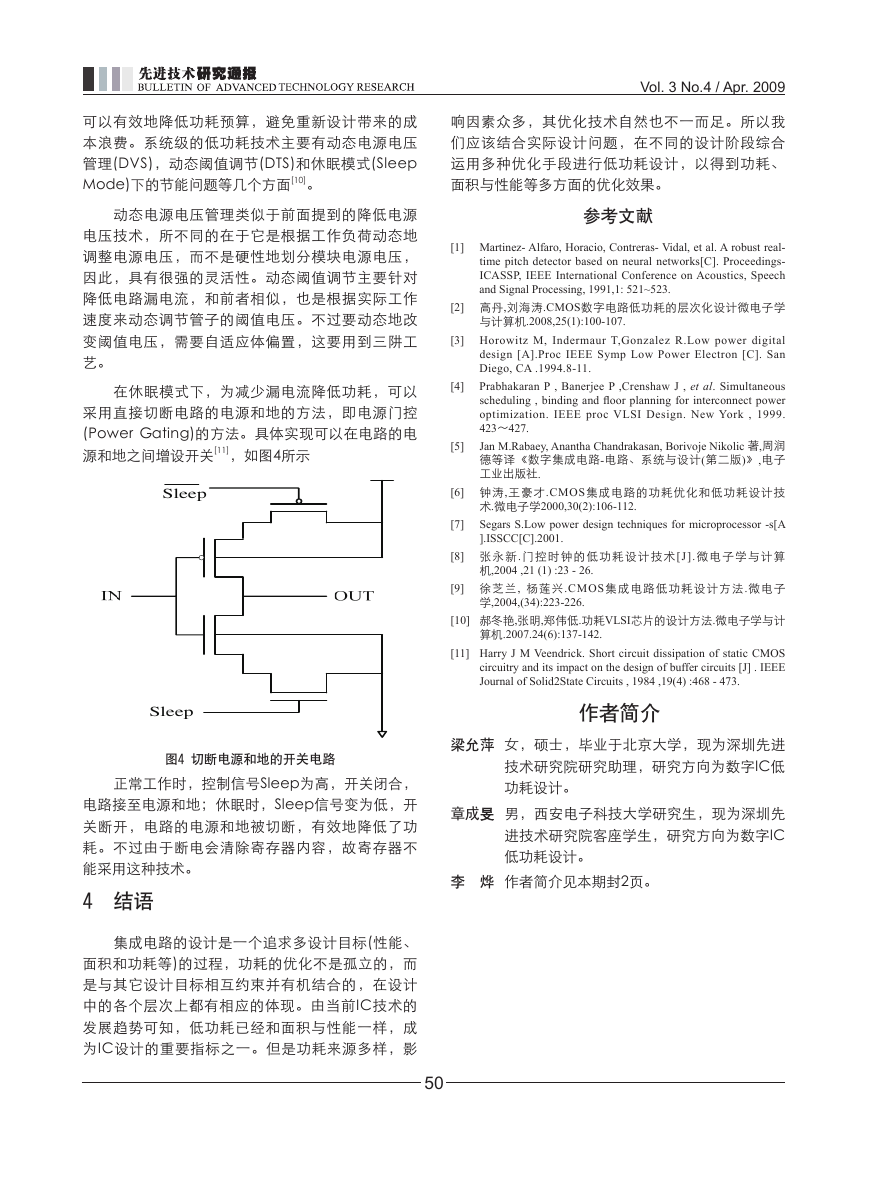

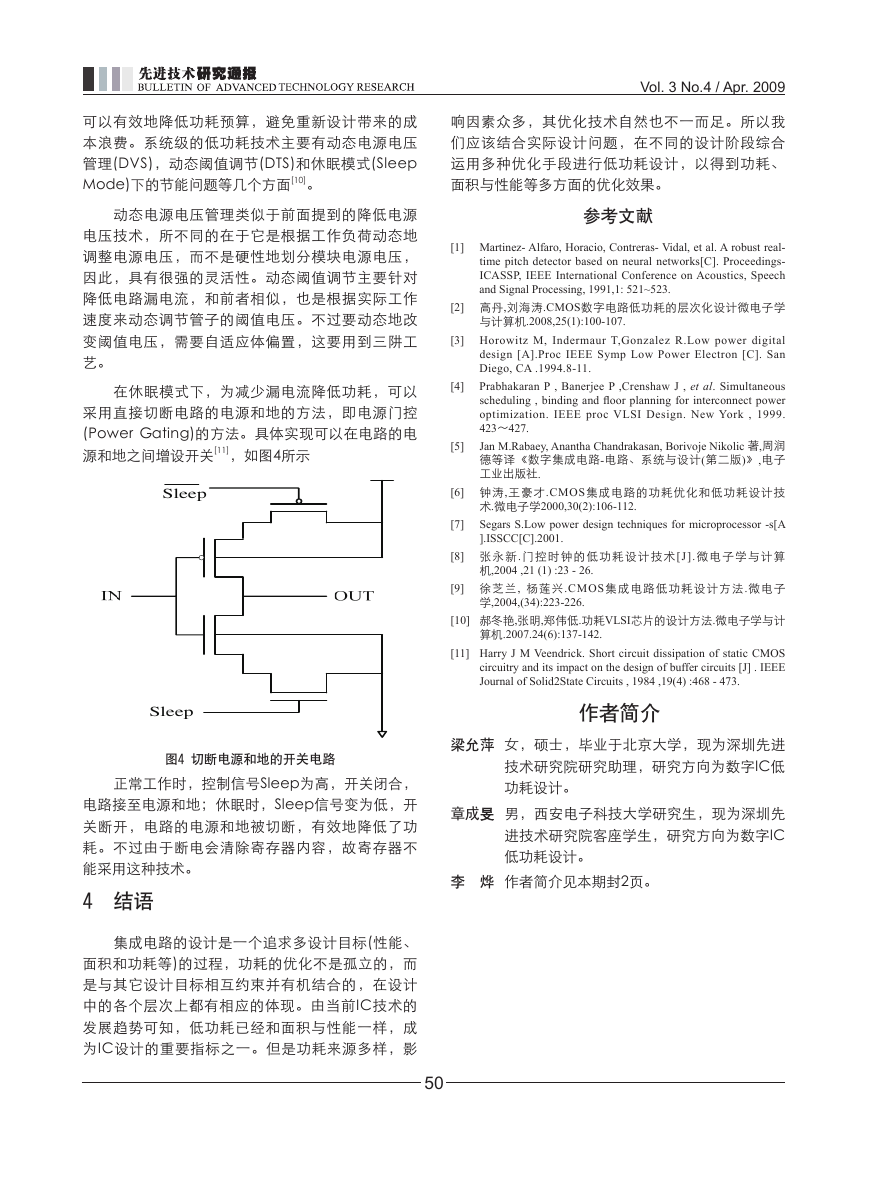

在休眠模式下,为减少漏电流降低功耗,可以

采用直接切断电路的电源和地的方法,即电源门控

(Power Gating)的方法。具体实现可以在电路的电

源和地之间增设开关[11],如图4所示

Sleep

Vol. 3 No.4 / Apr. 2009

响因素众多,其优化技术自然也不一而足。所以我

们应该结合实际设计问题,在不同的设计阶段综合

运用多种优化手段进行低功耗设计,以得到功耗、

面积与性能等多方面的优化效果。

参考文献

[1] Martinez- Alfaro, Horacio, Contreras- Vidal, et al. A robust real-

time pitch detector based on neural networks[C]. Proceedings-

ICASSP, IEEE International Conference on Acoustics, Speech

and Signal Processing, 1991,1: 521~523.

[2] 高丹,刘海涛.CMOS数字电路低功耗的层次化设计微电子学

与计算机.2008,25(1):100-107.

[3] Horowitz M, Indermaur T,Gonzalez R.Low power digital

design [A].Proc IEEE Symp Low Power Electron [C]. San

Diego, CA .1994.8-11.

[4] Prabhakaran P , Banerjee P ,Crenshaw J , et al. Simultaneous

scheduling , binding and floor planning for interconnect power

optimization. IEEE proc VLSI Design. New York , 1999.

423~427.

Jan M.Rabaey, Anantha Chandrakasan, Borivoje Nikolic 著,周润

德等译《数字集成电路-电路、系统与设计(第二版)》,电子

工业出版社.

[5]

[6] 钟涛,王豪才.CMOS集成电路的功耗优化和低功耗设计技

术.微电子学2000,30(2):106-112.

[7] Segars S.Low power design techniques for microprocessor -s[A

].ISSCC[C].2001.

[8] 张永新.门控时钟的低功耗设计技术[J].微电子学与计算

机,2004 ,21 (1) :23 - 26.

[9] 徐芝兰, 杨莲兴.CMOS集成电路低功耗设计方法.微电子

学,2004,(34):223-226.

[10] 郝冬艳,张明,郑伟低.功耗VLSI芯片的设计方法.微电子学与计

算机.2007.24(6):137-142.

[11] Harry J M Veendrick. Short circuit dissipation of static CMOS

circuitry and its impact on the design of buffer circuits [J] . IEEE

Journal of Solid2State Circuits , 1984 ,19(4) :468 - 473.

Sleep

作者简介

梁允萍 女,硕士,毕业于北京大学,现为深圳先进

技术研究院研究助理,研究方向为数字IC低

功耗设计。

章成旻 男,西安电子科技大学研究生,现为深圳先

进技术研究院客座学生,研究方向为数字IC

低功耗设计。

李 烨 作者简介见本期封2页。

图4 切断电源和地的开关电路

正常工作时,控制信号Sleep为高,开关闭合,

电路接至电源和地;休眠时,Sleep信号变为低,开

关断开,电路的电源和地被切断,有效地降低了功

耗。不过由于断电会清除寄存器内容,故寄存器不

能采用这种技术。

4 结语

集成电路的设计是一个追求多设计目标(性能、

面积和功耗等)的过程,功耗的优化不是孤立的,而

是与其它设计目标相互约束并有机结合的,在设计

中的各个层次上都有相应的体现。由当前IC技术的

发展趋势可知,低功耗已经和面积与性能一样,成

为IC设计的重要指标之一。但是功耗来源多样,影

50

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc