数字电路课程设计报告

院系: 电气信息工程学院

班级:

08 测控 2 班

学号:

08314237

姓名:

合作:

董 亮

虞 波

指导教师:

翟 丽 芳

2010 年 12 月 10 日

第 0 页 共 17 页

�

目 录

引言······················································2

一 设计任务和设计要求·········································2

二 电路工作原理及方案设计································3

三 软件设计与调试········································4

1. 分频模块的设计及仿真图·································4

2. 控制器设计及仿真图····································6

3. 计数器的设计及仿真图···································7

4. 分位模块的设计·······································9

5.数码管驱动设计·······································10

6.顶层文件设置·········································14

四 硬件焊接与组装调试···································15

五 心得体会·············································16

六 参考文献·············································16

第 1 页 共 17 页

�

交通灯控制电路设计

引言:

随着社会的发展以及人类生活水平的提高,基于 CPLD 的 EDA 技术的发展和应

用领域的扩大与深入,EDA 技术在电子信息、通信、自动控制用计算机等领域的

重要性日益突出。

如今,交通的问题日益突出,单单依靠人力来指挥交通已经不可行了,所以,

设计交通灯来完成这个需求就显的越加迫切了。为了确保十字路口的行人和车辆

顺利、畅通地通过,往往采用电子控制的交通信号来进行指挥。以下就是运用数

字电子设计出的交通灯。

本程序设计的是交通灯的设计。采用 EDA 作为开发工具,VHDL 语言为硬件

描述语言,quartusII 作为程序运行平台,所开发的程序通过调试运行、波形仿

真验证,实现设计目标。

一.设计任务与设计要求

1. 设计任务

设计一个基于 FPGA 的十字路口交通控制器,假设南北方向和东西方向,两

个方向分别设置红灯、绿灯、黄灯三盏灯,设置一组倒计时显示器,用以指挥车

辆和行人有序的通行。红灯亮表示直行车辆禁行;绿灯亮表示直行车辆可以通行;

黄灯亮表示直行车辆即将禁行;倒计时显示器用来显示允许通行或禁止通行的时

间 。尽量采用层次化设计。

2. 设计要求

在十字路口南北和东西两个方向各设一组红灯、黄灯、绿灯。设一组倒计时

显示器。

自动控制:

设置一组数码管,以倒计时的方式显示允许通行或禁止通行的时间,南北方

向为主干道,红灯、黄灯和绿灯显示时间分别是 55、5s、50s。东西方向为次干

道,红灯、黄灯绿灯显示时间分别为 35s、5s、30s。

特殊功能:

第 2 页 共 17 页

�

(1)

紧急状态时,手动拨动紧急开关,主干道以及次干道都显示红灯,

禁止通行,并由蜂鸣其报警。

(2)

黄灯显示信号为脉冲信号,使得黄灯为“一闪一闪”的显示状态。

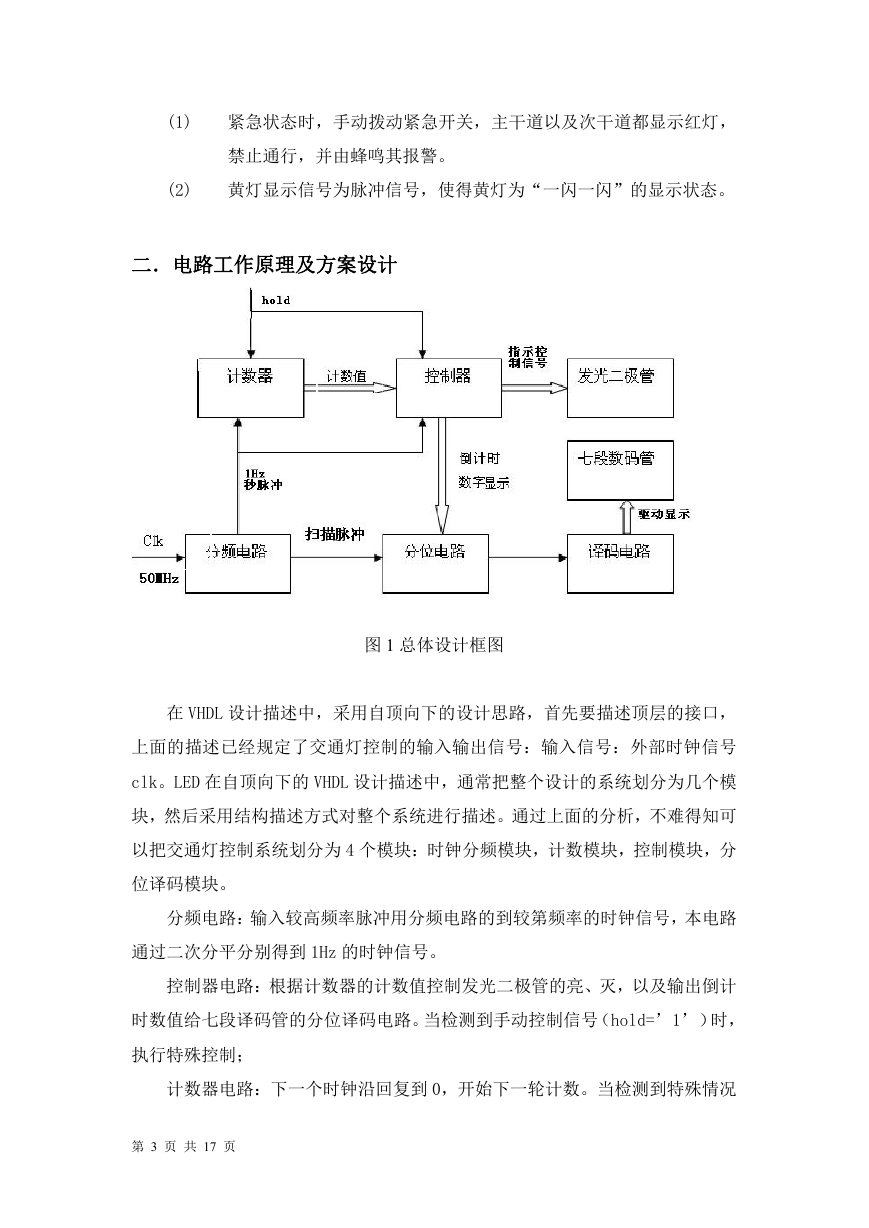

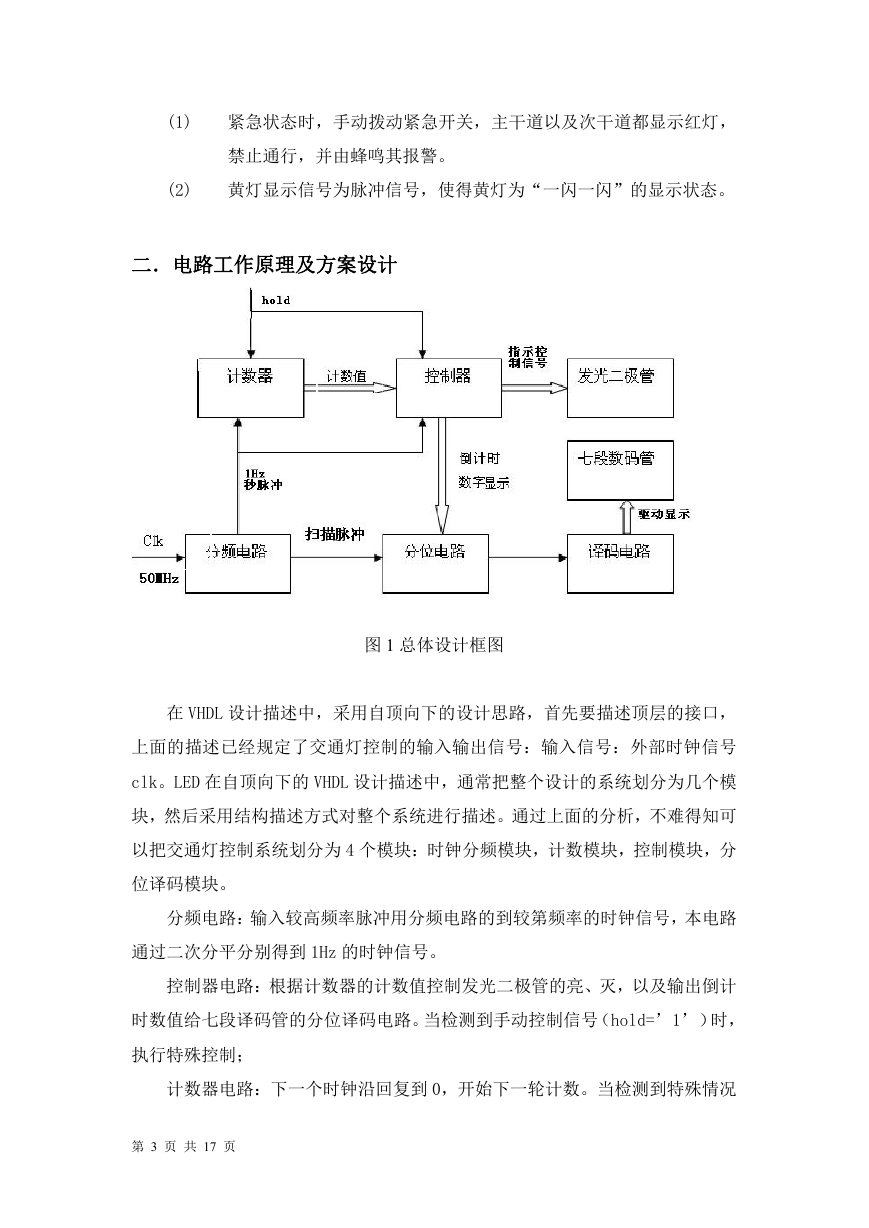

二.电路工作原理及方案设计

图 1 总体设计框图

在 VHDL 设计描述中,采用自顶向下的设计思路,首先要描述顶层的接口,

上面的描述已经规定了交通灯控制的输入输出信号:输入信号:外部时钟信号

clk。LED 在自顶向下的 VHDL 设计描述中,通常把整个设计的系统划分为几个模

块,然后采用结构描述方式对整个系统进行描述。通过上面的分析,不难得知可

以把交通灯控制系统划分为 4 个模块:时钟分频模块,计数模块,控制模块,分

位译码模块。

分频电路:输入较高频率脉冲用分频电路的到较第频率的时钟信号,本电路

通过二次分平分别得到 1Hz 的时钟信号。

控制器电路:根据计数器的计数值控制发光二极管的亮、灭,以及输出倒计

时数值给七段译码管的分位译码电路。当检测到手动控制信号(hold=’1’)时,

执行特殊控制;

计数器电路:下一个时钟沿回复到 0,开始下一轮计数。当检测到特殊情况

第 3 页 共 17 页

�

(HOLD=‘1’)发生是,计数器暂停计数。

分位译码电路:因为控制器输出的倒计时数值可能是 1 位或者 2 位十进制数,

所以在七段数码管的译码电路前要加上分位电路(即将其分为 2 个 1 位的十进制

数)。七段数码管的译码电路根据控制电路的控制信号,驱动交通灯的显示,通

过输入二进制数值,输出信号点亮二极管,我们用的是共阴极数码管,因此译码

电路输出逻辑数值‘1’点亮二极管,译码电路输出逻辑数值‘0’熄灭二极管。

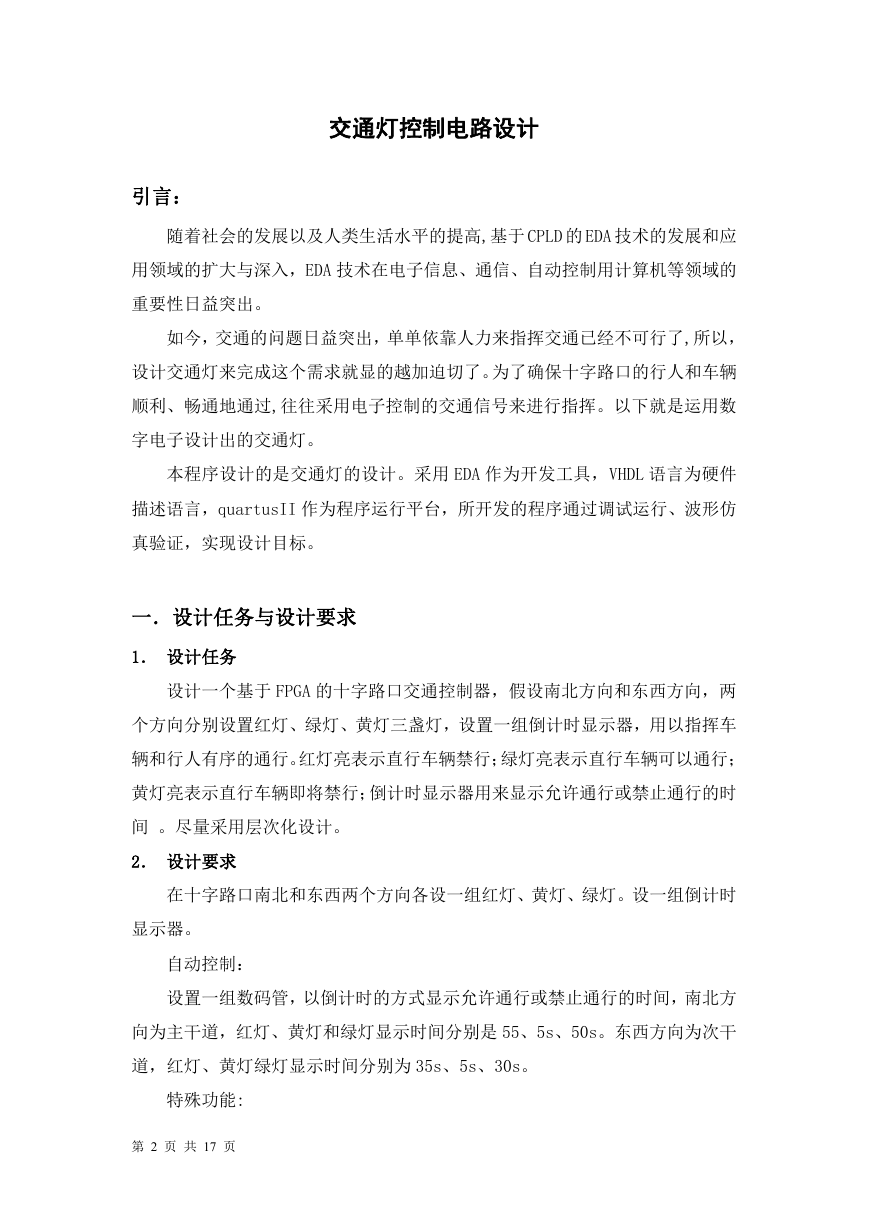

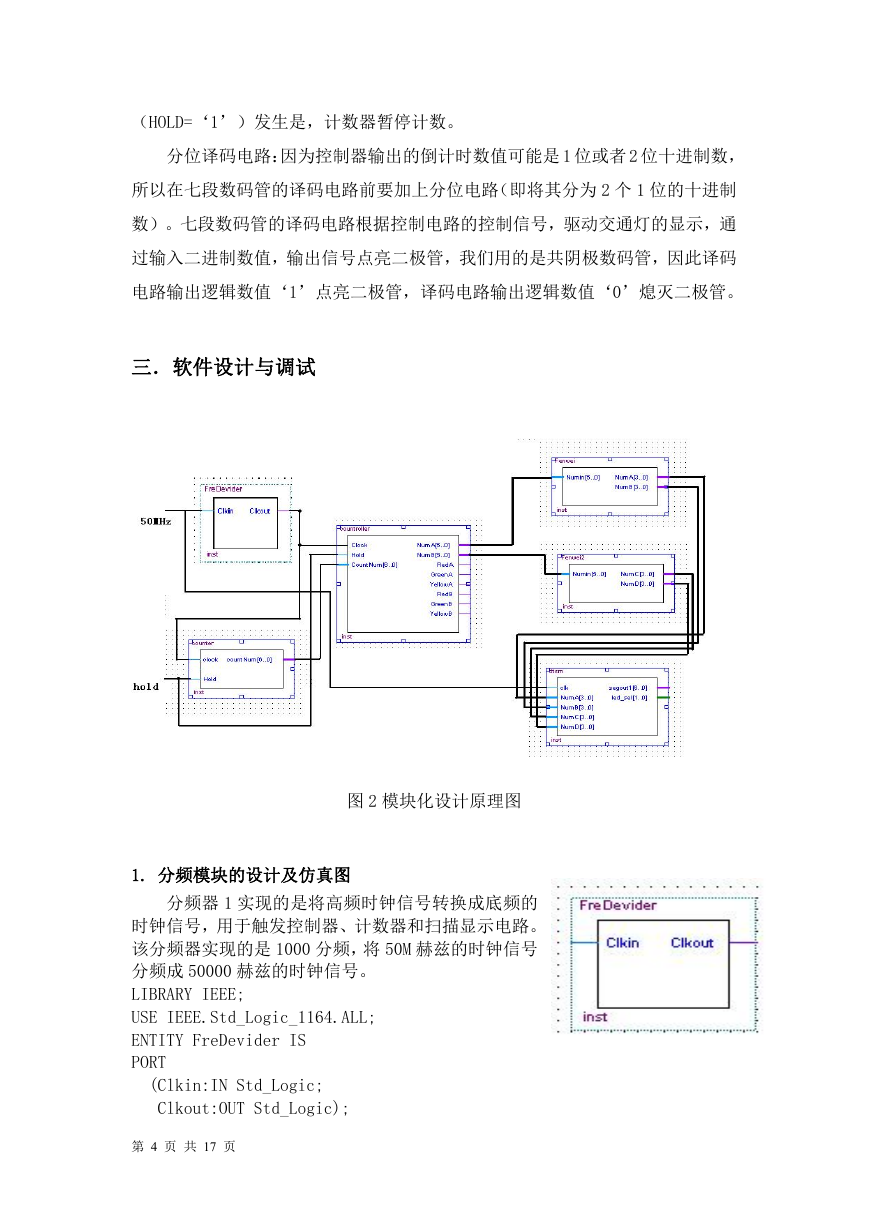

三.软件设计与调试

图 2 模块化设计原理图

1. 分频模块的设计及仿真图

分频器 1 实现的是将高频时钟信号转换成底频的

时钟信号,用于触发控制器、计数器和扫描显示电路。

该分频器实现的是 1000 分频,将 50M 赫兹的时钟信号

分频成 50000 赫兹的时钟信号。

LIBRARY IEEE;

USE IEEE.Std_Logic_1164.ALL;

ENTITY FreDevider IS

PORT

(Clkin:IN Std_Logic;

Clkout:OUT Std_Logic);

第 4 页 共 17 页

�

END;

ARCHITECTURE Devider OF FreDevider IS

CONSTANT N:Integer:=499;

Signal counter:Integer range 0 to N;

signal Clk:Std_Logic;

BEGIN

PROCESS(Clkin)

begin

IF rising_edge(Clkin)THEN

IF Counter=N then

counter<=0;

Clk<=not clk;

else

counter<=counter+1;

end if;

end if;

end process;

clkout<=clk;

end;

分频器 2 实现的是 50000 分频,将 50000 赫兹的时钟信号分频成 1 赫兹的时

钟信号。

LIBRARY IEEE;

USE IEEE.Std_Logic_1164.ALL;

ENTITY FreDevider1 IS

PORT

(Clkin:IN Std_Logic;

Clkout:OUT Std_Logic);

END;

ARCHITECTURE Devider1 OF FreDevider1 IS

CONSTANT N:Integer:=24999;

signal counter:Integer range 0 to N;

signal Clk:Std_Logic;

BEGIN

PROCESS(Clkin)

begin

IF rising_edge(Clkin)THEN

IF Counter=N then

counter<=0;

Clk<=not clk;

else

counter<=counter+1;

end if;

end if;

end process;

第 5 页 共 17 页

�

clkout<=clk;

end;

2. 控制器设计及仿真图

控制器的作用是根据计数器的计数值控制发光二极管的亮、灭,以及输出倒

计时数值给七段译管的分译码电路。此外,当检测到特殊情况(Hold=‘1’)发

生时,无条件点亮红色的发光二极管。

功能:控制发光二极管的亮、灭,以及输出倒

计时数值给七段译码管的分位译码电路。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY countroller IS

PORT (Clock:IN STD_LOGIC;

Hold:in std_logic;

CountNum:in INTEGER RANGE 0 TO

89;

NumA:out INTEGER RANGE 0 TO 90;

RedA,GreenA,YellowA:out std_logic;

RedB,GreenB,YellowB:out std_logic);

END;

ARCHITECTURE behavior OF Countroller IS

BEGIN

process(Clock)

BEGIN

IF falling_edge(Clock)THEN

IF Hold='1' THEN

RedA<='1';

RedB<='1';

GreenA<='0';

GreenA<='0';

YellowA<='0';

YellowB<='0';

第 6 页 共 17 页

�

ELSIF CountNum<=54 THEN

NumA<=55-CountNum;

RedA<='0';

GreenA<='1';

YellowA<='0';

ELSIF CountNum<=59 THEN

NumA<=60;

RedA<='0';

GreenA<='0';

YellowA<='1';

ELSE

NumA<=90-CountNum;

RedA<='1';

GreenA<='0';

YellowA<='0';

END IF;

IF CountNum<=54 THEN

RedB<='1';

GreenB<='0';

YellowB<='0';

ELSIF CountNum<=84 THEN

RedB<='0';

GreenB<='1';

YellowB<='0';

ELSe

RedB<='0';

GreenB<='0';

YellowB<='1';

END IF;

end if;

END PROCESS;

END;

3. 计数器的设计及仿真图

这里计数器的计数范围为 0—90S ,下一个

时钟沿回复到 0,开始下一轮计数.此外,当检测

到特殊情况(Hold=‘1‘)发生时,计数器暂停

计数。

程序如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY counter IS

PORT (clock:IN STD_LOGIC;

Hold:in std_logic;

countNum:BuFFeR INTEGER RANGE 0 TO 90);

第 7 页 共 17 页

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc