The Report of Cache

Include simulating the cache lantecy

谷雨 121220026

实验概述

本次实验旨在通过软件实现对计算机缓存 Cache 的模拟。能够支持直接映射、

任意相关路数(2^k)的组相联映射、全相联映射。支持 LRU 替换与随机替换两

种机制。包含对时间延迟的评估。

一、 实验目的

通过软件模拟 cache 功能,更加深入透彻地了解 cache 的工作原理。

二、实验过程设计

完成本次实验的核心是构建一个整体的数据结构。

我主要使用了一个 Cache 的类,一个 Manage 控制接口。Cache 类的数据成员

为 Cacheline 结构体的数组,其中 Cacheline 用于存储 Cache 中一行的数据。

包含 valid 位,tag 标记位,data 数据区(本实验中并不实际存储数据,仅用于模

拟)write back 策略的 dirty_bit,还有一个用于 LRU 替换算法的 LRU_bit(此处程

序还可以优化,因为对于随机替换策略来说,LRU_bit 浪费了一位数据空间)。

对于 Cache 的三种映射方式。我采用了两种数据结构,开始我为 cache 加了

一个 kind 标记位,后来发现这样很不聪明。与是我将原本的代码全部注释掉,

改写成了第二种统一的数据结构。三种映射方式可以很简单地完成统一。直接映

射相当于关联路数为 1 的组相联,全相联相当于关联路数为全部行数的组相联。

这样,只需要在 Cache 类里再定义一个数据成员,用 int 型表示的关联路数

ways,ways 为 1 时即表示直接映射,为行数时即表示全相联。

这样,对于 Cache 类数据结构的构建就基本完成了。

剩下还有一项重要的任务就是对主存地址 16 进制串的处理。考虑到将地址

分段其实就是基本的除法运算与取模运算,所以我直接将输入的主存地址作为

�

int 型数据处理,为避免溢出,我采用了 long long int 作为数据类型(其实只

要 unsigned long int 就刚刚好,此处又是一个浪费空间,可以优化的地方。)

对于内存地址的处理无疑就是两个问题,一是去除 tag 标记位,而是确定其

在 Cache 所应该的存储位置(即行号或组号)。

作为一个接触了数学十几年的学生,不难写出去 TAG 和确定位置的函数。

很直观的数学表达式,很精简的代码。

完成整体框架与数据结构的设计后,算法内容本身并不存在多少困难之处。

三、细节实现

Tag 与确定位置函数:

long long int tag(long long int x,Cache c)//地址的标记位

{

}

return (x/c.Linesize)/(c.getline()/c.ways);

long long int location(long long int x,Cache c)//根据映射方式所对应的地址在cache中存储的位置

{

return (x/c.Linesize)%(c.getline()/c.ways);

}

随机算法的取随机数函数:

long long int x=0x88888888;

long long int random_number(long long int a,long long int b)//自己写的生成伪随机数的算法,伪的程度相当高(保证范围内每个值都

有机会取到,但是取各数的概率显然不等。。)

{

GetSystemTime(&time);

int k=time.wSecond;

x=((x+33)*k+6)%(b-a)+a+1;

return x;

}

四、cache 工作原理

高速缓冲存储器通常由高速存储器、联想存储器、替换逻辑电路和相

应的控制线路组成。在有高速缓冲存储器的计算机系统中,中央处理器存取主

存储器的地址划分为行号、列号和组内地址三个字段。于是,主存储器就在逻

�

辑上划分为若干行;每行划分为若干的存储单元组;每组包含几个或几十个字。

高速存储器也相应地划分为行和列的存储单元组。二者的列数相同,组的大小

也相同,但高速存储器的行数却比主存储器的行数少得多。

联想存储器用于地址联想,有与高速存储器相同行数和列数的存储单元。

当主存储器某一列某一行存储单元组调入高速存储器同一列某一空着的存储单

元组时,与联想存储器对应位置的存储单元就记录调入的存储单元组在主存储

器中的行号。

当中央处理器存取主存储器时,硬件首先自动对存取地址的列号字段进行

译码,以便将联想存储器该列的全部行号与存取主存储器地址的行号字段进行

比较:若有相同的,表明要存取的主存储器单元已在高速存储器中,称为命中,

硬件就将存取主存储器的地址映射为高速存储器的地址并执行存取操作;若都

不相同,表明该单元不在高速存储器中,称为脱靶,硬件将执行存取主存储器

操作并自动将该单元所在的那一主存储器单元组调入高速存储器相同列中空着

的存储单元组中,同时将该组在主存储器中的行号存入联想存储器对应位置的

单元内。

当出现脱靶而高速存储器对应列中没有空的位置时,便淘汰该列中的某一

组以腾出位置存放新调入的组,这称为替换。确定替换的规则叫替换算法,常

用的替换算法有:最近最少使用法(LRU)、先进先出法(FIFO)和随机法(RAND)

等。替换逻辑电路就是执行这个功能的。另外,当执行写主存储器操作时,为

保持主存储器和高速存储器内容的一致性,对命中和脱靶须分别处理:

①写操作命中时,可采用写直达法(即同时写入主存储器和高速存储器)

或写回法(即只写入高速存储器并标记该组修改过。淘汰该组时须将内容写回

主存储器);

②写操作脱靶时,可采用写分配法(即写入主存储器并将该组调入高速存

储器)或写不分配法(即只写入主存储器但不将该组调入高速存储器)。高速

缓冲存储器的性能常用命中率来衡量。影响命中率的因素是高速存储器的容量、

存储单元组的大小、组数多少、地址联想比较方法、替换算法、写操作处理方

法和程序特性等。

采用高速缓冲存储器技术的计算机已相当普遍。有的计算机还采用多个高

速缓冲存储器,如系统高速缓冲存储器、指令高速缓冲存储器和地址变换高速

缓冲存储器等,以提高系统性能。随着主存储器容量不断增大,高速缓冲存储器

的容量也越来越大。

五、输入输出

Input: 操作类型(s or l)、主存地址(十六进制串)、指令时钟周期数

�

Output: 指令条数、读指令条数、写指令条数、读命中率、写命中率、平

均命中率、读命中计数、写命中计数、总时钟周期数

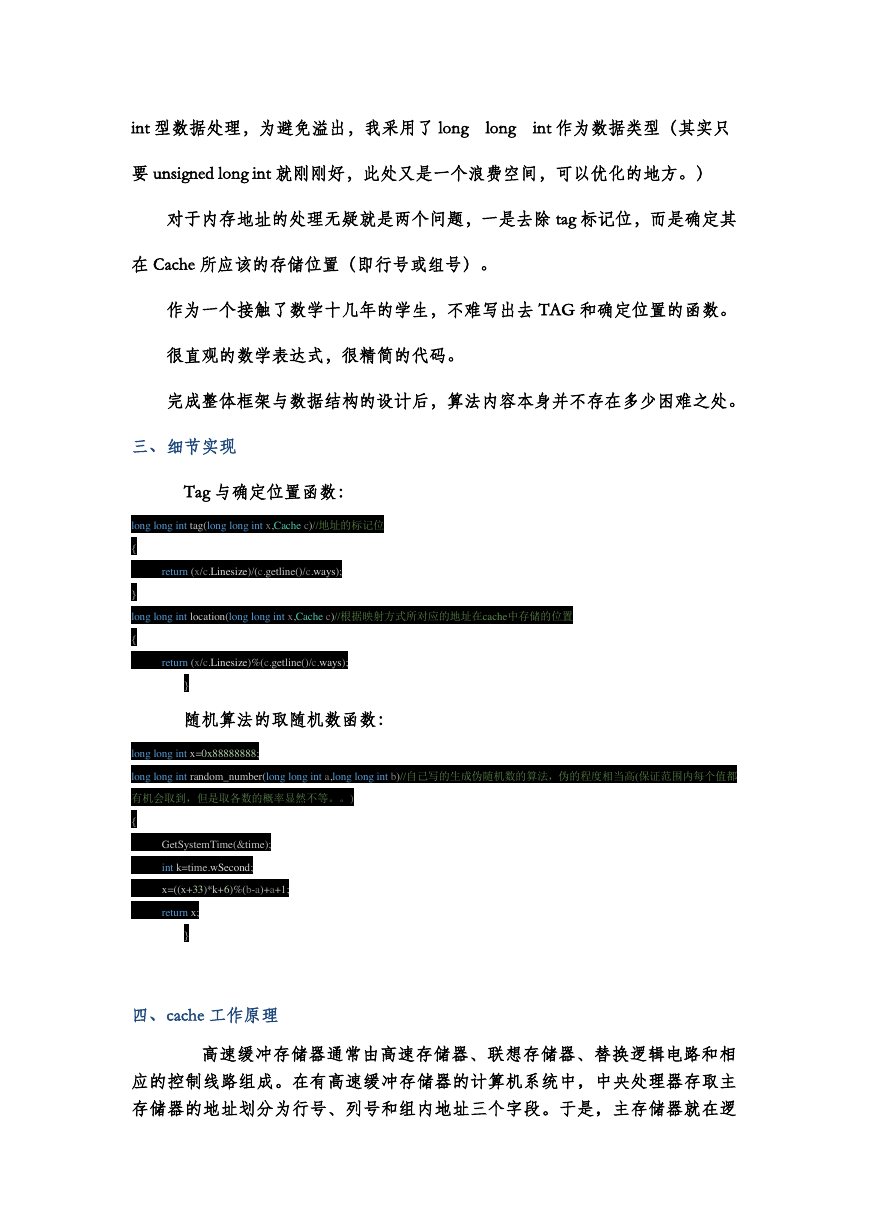

六、实验结果

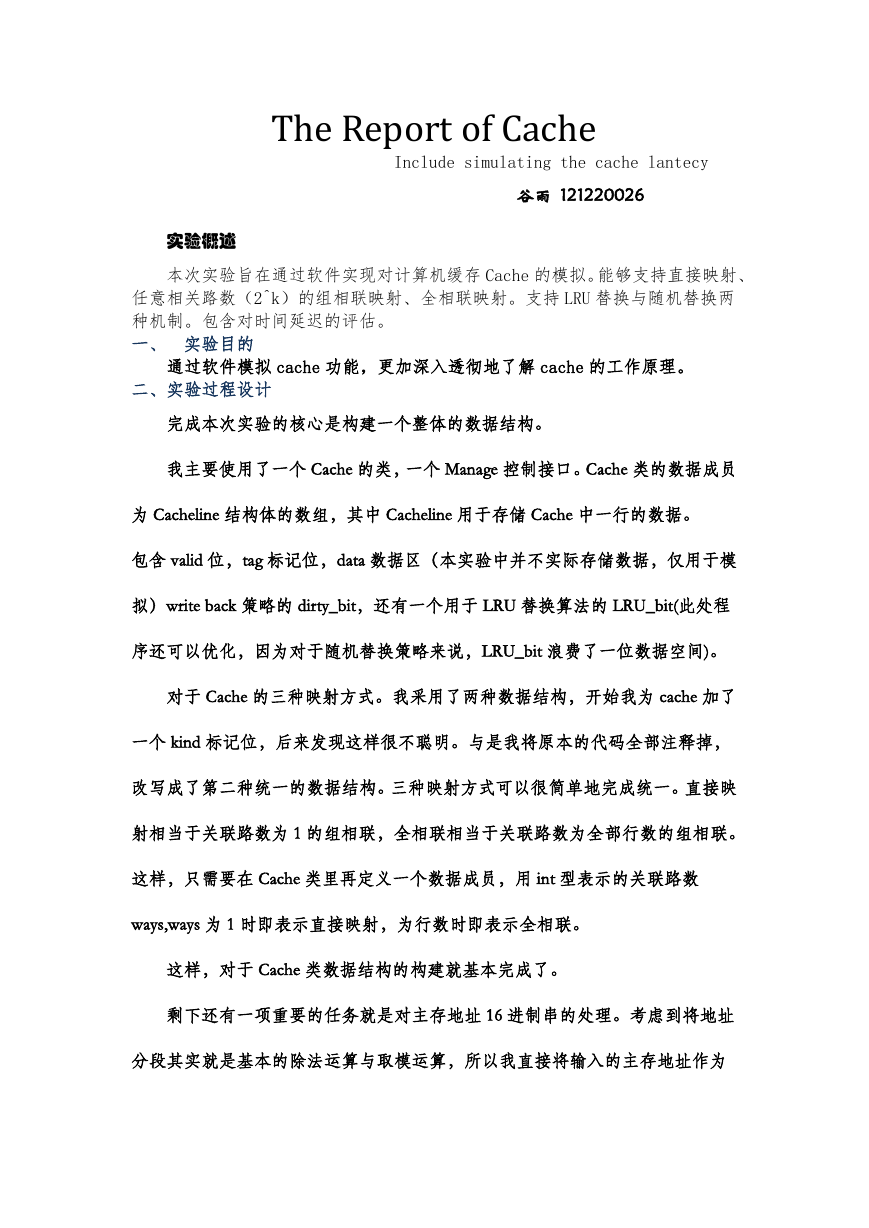

输入文件

指令总数

读指令总数

写指令总数

gcc

gzip

mcf

swim

twolf

515683

481044

727230

303193

482824

318197

320441

5972

220668

351403

197486

160603

721258

82525

131421

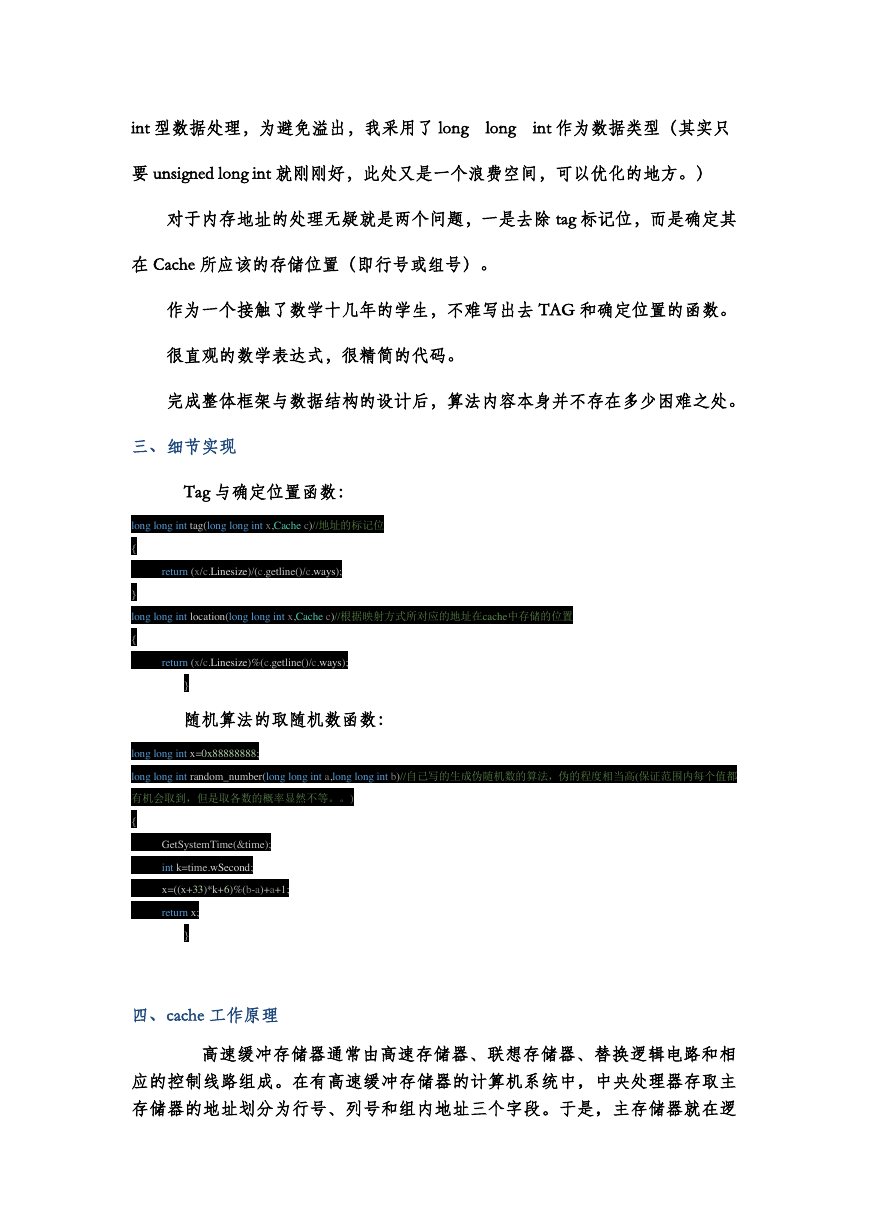

配置: (1)Cache 大小 256KB,块大小 8B,直接映射

(2)Cache 大小 64KB,块大小 32B,四路组相联,LRU

(3)Cache 大小 64KB,块大小 32B,四路组相联,random

(4)Cache 大小 8KB,块大小 64B,全相联,LRU

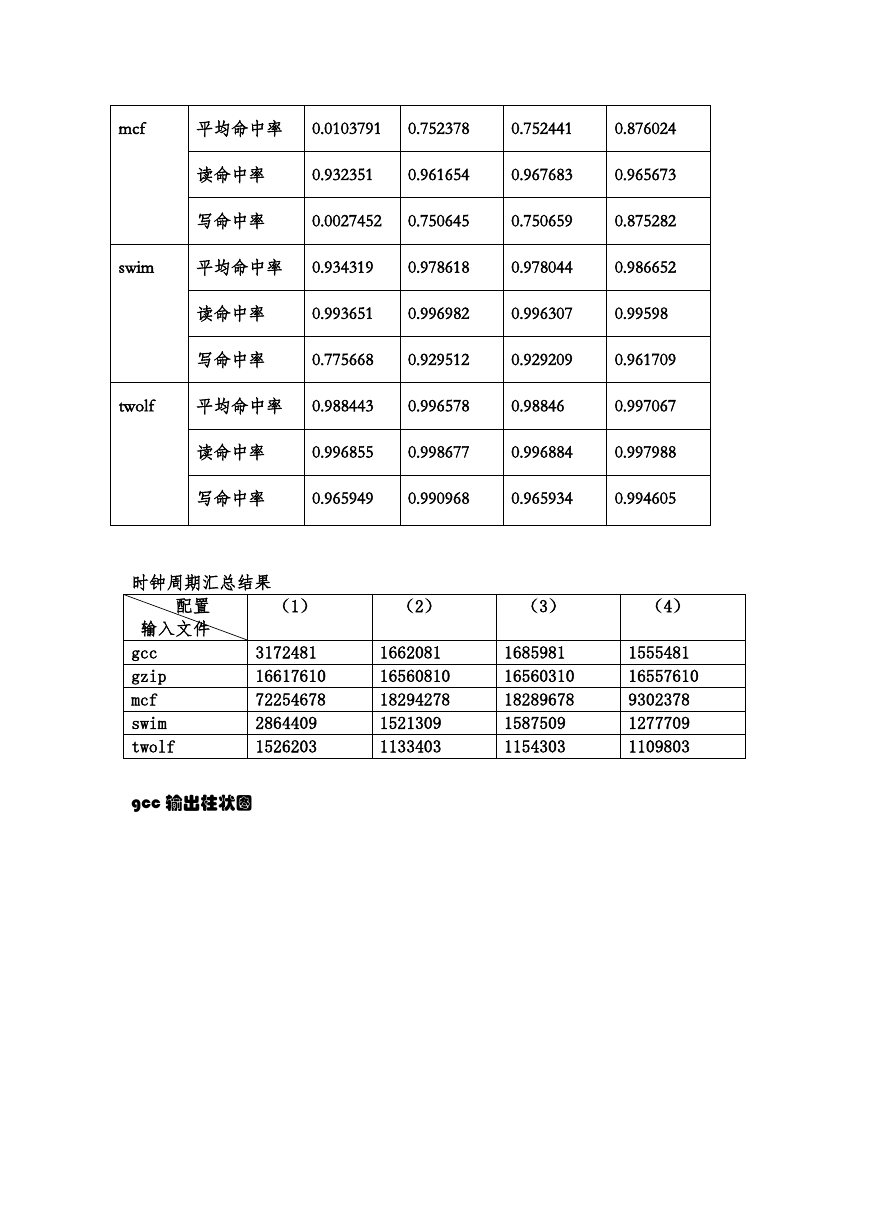

命中率汇总结果

输入文件 配置

(1)

(2)

(3)

(4)

gcc

平均命中率

0.958347

0.987636

0.986802

0.989703

读命中率

0.987215

0.994362

0.993388

0.992112

写命中率

0.911832

0.976798

0.976191

0.985822

gzip

平均命中率

0.667072

0.668253

0.668263

0.668319

读命中率

0.50232

0.502576

0.502592

0.502467

写命中率

0.995791

0.99817

0.998817

0.999234

�

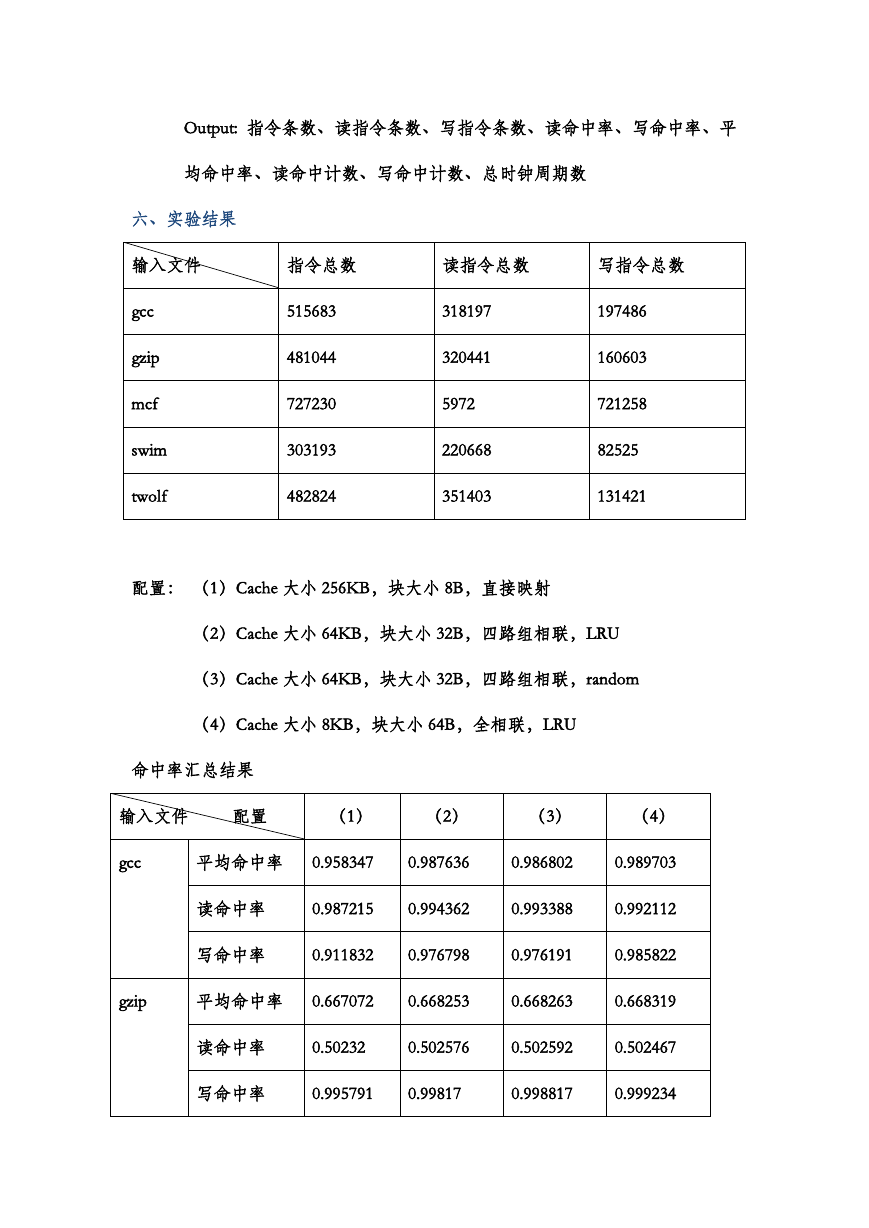

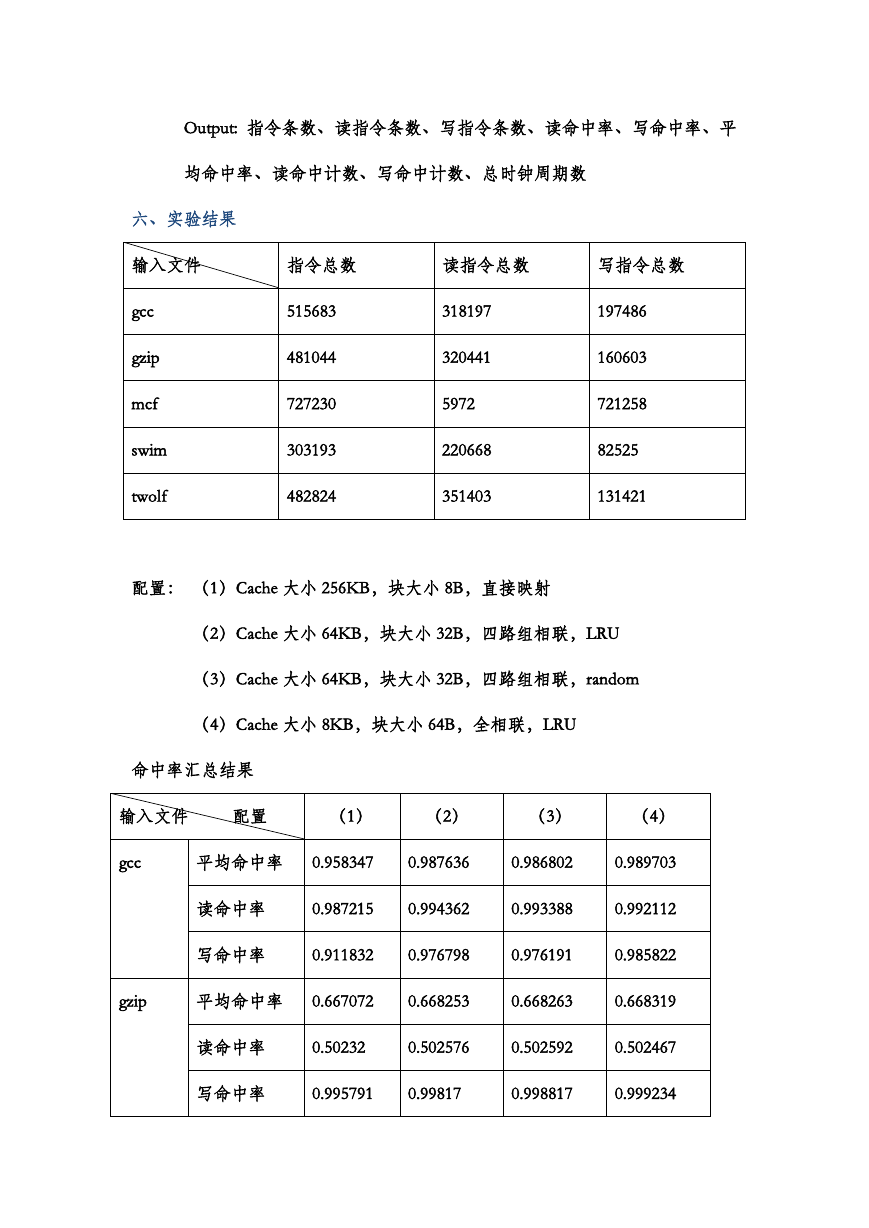

mcf

平均命中率

0.0103791

0.752378

0.752441

0.876024

读命中率

0.932351

0.961654

0.967683

0.965673

写命中率

0.0027452

0.750645

0.750659

0.875282

swim

平均命中率

0.934319

0.978618

0.978044

0.986652

读命中率

0.993651

0.996982

0.996307

0.99598

写命中率

0.775668

0.929512

0.929209

0.961709

twolf

平均命中率

0.988443

0.996578

0.98846

0.997067

读命中率

0.996855

0.998677

0.996884

0.997988

写命中率

0.965949

0.990968

0.965934

0.994605

(1)

时钟周期汇总结果

配置

输入文件

gcc

gzip

mcf

swim

twolf

3172481

16617610

72254678

2864409

1526203

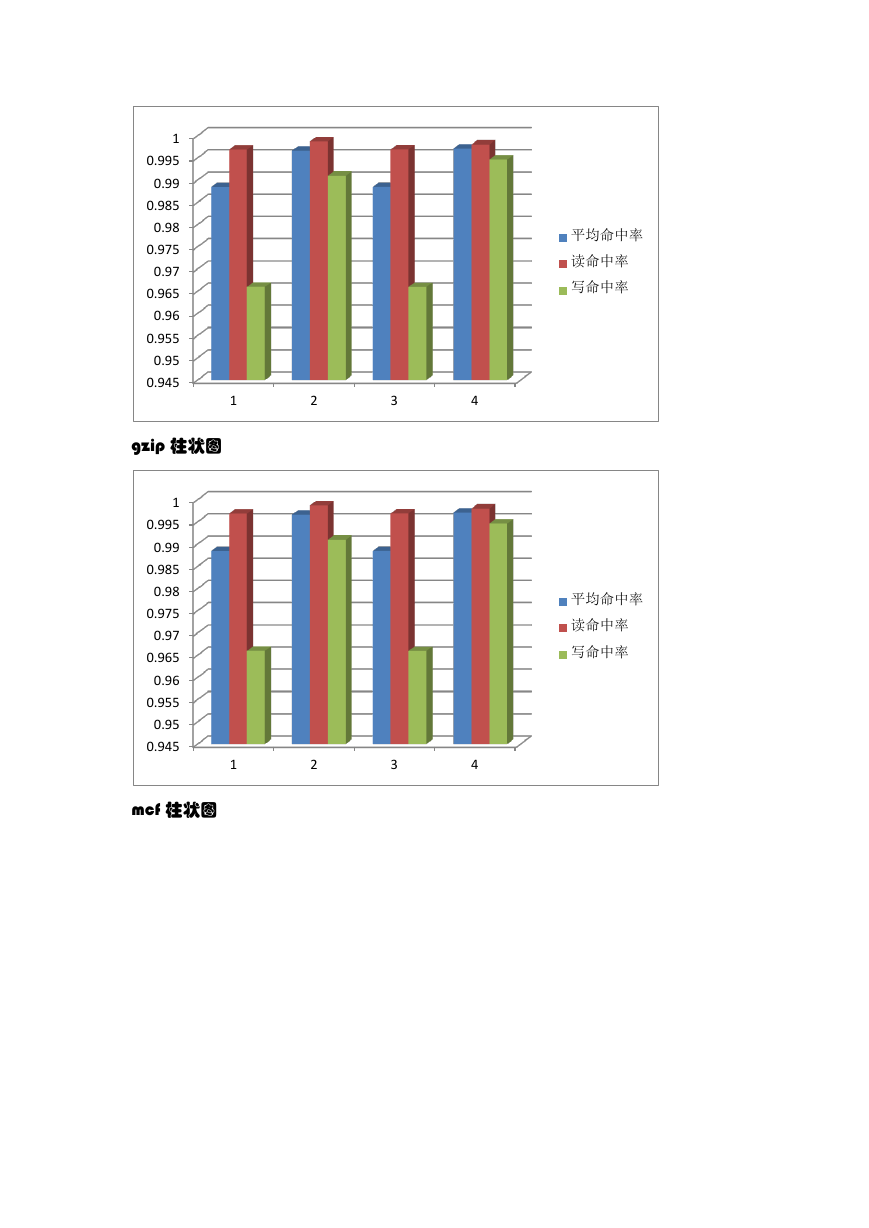

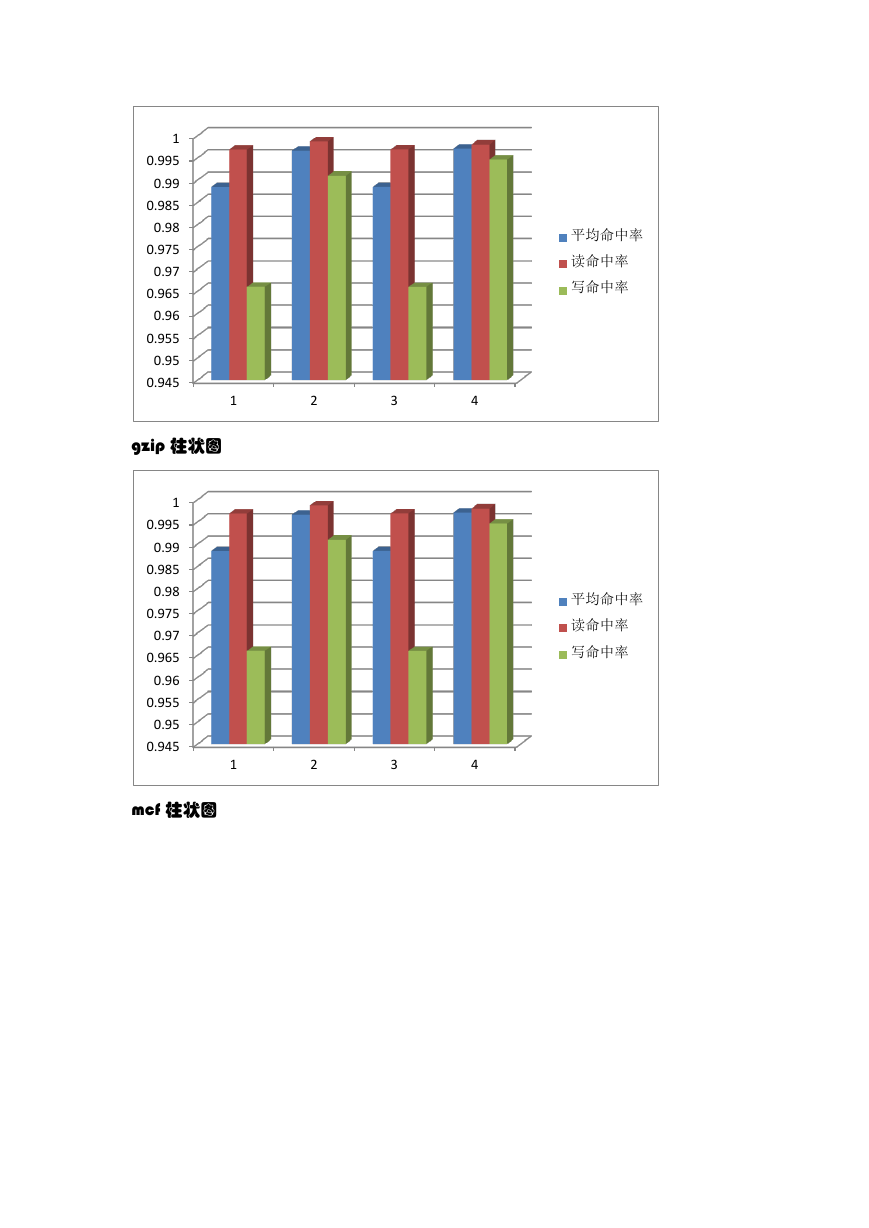

gcc 输出柱状图

(2)

(3)

(4)

1662081

16560810

18294278

1521309

1133403

1685981

16560310

18289678

1587509

1154303

1555481

16557610

9302378

1277709

1109803

�

1

0.995

0.99

0.985

0.98

0.975

0.97

0.965

0.96

0.955

0.95

0.945

1

2

3

4

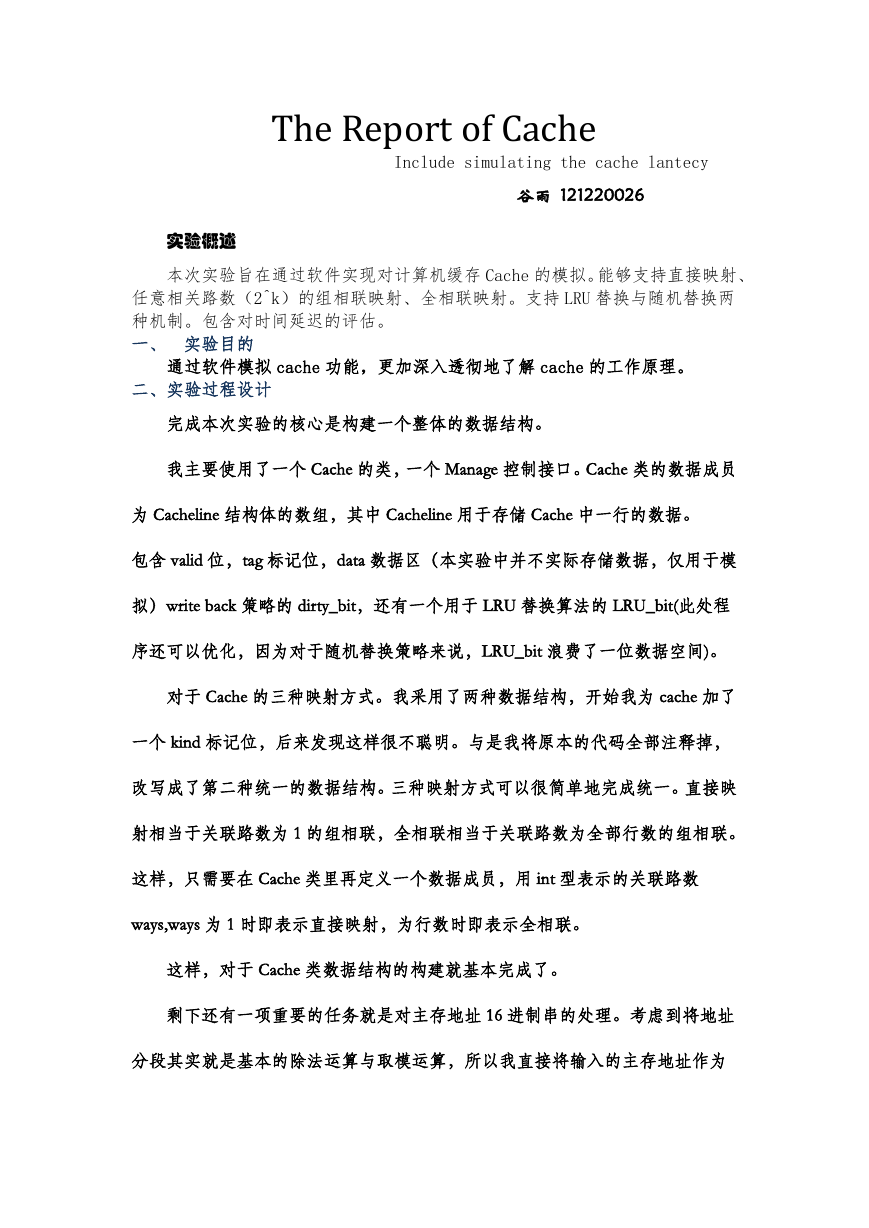

gzip 柱状图

1

0.995

0.99

0.985

0.98

0.975

0.97

0.965

0.96

0.955

0.95

0.945

1

2

3

4

mcf 柱状图

平均命中率

读命中率

写命中率

平均命中率

读命中率

写命中率

�

1

0.995

0.99

0.985

0.98

0.975

0.97

0.965

0.96

0.955

0.95

0.945

1

2

3

4

Swim 柱状图

1

0.995

0.99

0.985

0.98

0.975

0.97

0.965

0.96

0.955

0.95

0.945

1

2

3

4

Twolf 柱状图

平均命中率

读命中率

写命中率

平均命中率

读命中率

写命中率

�

1

0.995

0.99

0.985

0.98

0.975

0.97

0.965

0.96

0.955

0.95

0.945

1

2

3

4

对于五种文件输入的平均命中率

1

0.9

0.8

0.7

0.6

0.5

0.4

0.3

0.2

0.1

0

gcc

gzip

mcf

swim

twolf

平均命中率

读命中率

写命中率

1

2

3

4

七、实验反思与总结

本次实验花费了我总共大约 5 个小时的时间,整体过程算是比较顺利。由于

这两周处于期中考试周,程序有几处明显可以优化的地方并没有修改,是本次

实验的疏漏之处。譬如我在本次实验中对 LRU 的使用,我定义的 LRU 函数只在

未命中时调用,而在命中时在工作程序中修改 cache 行的 LRUbit。所以当选择

random 替换时仍然需要进行此操作,浪费了时间和空间。

Random 替换模式下,随机数生成函数是完全我自己写的,不需验证都知道取

到各数的概率十分不平均,离真实的随机数有一定差距。

虽然今天是 deadline,但是今天提交了实验之后我自己仍会对本次实验的内

容进行改进。对程序进行优化。

从本次实验的结果可以看出,相较之下全相联的命中率最高,直接映射的命

中率最低。但是全相联效率最低下,程序运行时间最长。而组相联结合了两者

的优点,命中率较高,且效率较高。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc