锁相环常见问题解答

编写人

版本号

CAST (Y/D)

V1.3_Draft

------------------------------------------------------------------------------------------------------------

本报告为 Analog Devices Inc. (ADI) 中国技术支持中心专用,ADI 可以随时修改本

报告而不用通知任何使用本报告的人员。

如有任何问题请与 china.support@analog.com 联系。

------------------------------------------------------------------------------------------------------------

�

目 录

3.2

1 ADI 公司锁相环产品概述........................................................................................................................3

2

PLL 主要技术指标....................................................................................................................................6

相位噪声....................................................................................................................................6

2.1

参考杂散....................................................................................................................................7

2.2

2.3

锁定时间....................................................................................................................................9

3 应用中常见问题......................................................................................................................................10

PLL 芯片接口相关问题..........................................................................................................10

3.1.1 参考晶振有哪些要求?我该如何选择参考源?...........................................................10

3.1.2 请详细解释一下控制时序,电平及要求。...................................................................11

3.1.3 控制多片 PLL 芯片时,串行控制线是否可以复用 .....................................................12

3.1.4 请简要介绍一下环路滤波器参数的设置 ......................................................................12

3.1.5 环路滤波器采用有源滤波器还是无源滤波器?...........................................................13

3.1.6

PLL 对于 VCO 有什么要求?以及如何设计 VCO 输出功率分配器?......................13

3.1.7 如何设置电荷泵的极性? ..............................................................................................14

3.1.8 锁定指示电路如何设计? ..............................................................................................14

PLL 对射频输入信号有什么要求? ..............................................................................16

3.1.9

3.1.10

PLL 芯片对电源的要求有哪些? ..................................................................................16

3.1.11 内部集成了 VCO 的 ADF4360-x,其 VCO 中心频率如何设定?..............................16

PLL 芯片性能相关问题..........................................................................................................18

3.2.1 锁相环输出的谐波 ..........................................................................................................18

3.2.2 锁相环系统的相位噪声来源有哪些?减小相位噪声的措施有哪些?.......................18

3.2.3 为何我测出的相位噪声性能低于 ADIsimPLL 仿真预期值?.......................................19

3.2.4 锁相环锁定时间取决于哪些因素?如何加速锁定?...................................................20

3.2.5 为何我的锁相环在做高低温试验的时候,出现频率失锁?.......................................21

3.2.6 非跳频(单频)应用中,最高的鉴相频率有什么限制?...........................................21

3.2.7 频繁地开关锁相环芯片的电源会对锁相环有何影响?...............................................21

3.2.8 在使用 ADIsimPLL 过程中发现有的芯片有 1/f 噪声指标,而有的没有,请问 1/f 噪

声指什么?......................................................................................................................................21

3.2.9 在使用 ADF4150HV 时,RF 输出级可以通过硬件或软件进行使能或非使能选择。为

了实现省电模式,想了解一下,当输出级被非使能时,电流消耗是否为 0A?此外,当 RF 输

出级非使能时,RF 输出分频部分是否也同时被非使能了?.....................................................22

3.2.10 使用 ADF4350 做宽频本振,输出不同频点测量功率不同,是否正常?.................22

3.2.11 在小数 N 分频频率合成器中,什么是整数边界杂散?如何避免?..........................22

3.2.12 使用不同源输入时,相噪基本相同,但是输出相噪差别很大,请问这是为什么?.22

3.2.13 使用 ADF4107 做本振,参考输入分别为 10MHz 正弦波和方波,发现使用方波时,

本振输出信噪比要比正弦波时好 10dB 左右,请问是怎么回事?............................................24

PLL 的调试步骤......................................................................................................................25

3.3.1 使用 ADF7012 单片收发芯片,通过其中 PLL 模块,输入 11.0592MHz,想要得到输

出 162.2016MHz,但是正常配置并设计环路滤波器后没有输出? ..........................................26

3.3.2 使用 ADF4350,硬件按照评估板电路搭建,软件参照参考代码及使用评估板软件生

成控制字,仍不能锁定,请问是为什么? ..................................................................................26

3.3.3 使用 ADF4158 进行锯齿波扫频工作,但输出只有点频,并不扫频,请问可能是什

3.1

3.3

1

�

3.4

么原因?..........................................................................................................................................28

为您的设计选择合适的 PLL 芯片 .........................................................................................30

3.4.1 评价 PLL 频率合成器噪声性能的依据是什么? .........................................................30

3.4.2 小数分频的锁相环杂散的分布规律是什么?...............................................................30

3.4.3 到底用小数分频好还是整数分频好? ..........................................................................30

3.4.4

ADI 提供的锁相环仿真工具 ADIsimPLL 支持哪些芯片,有什么优点?.................31

3.4.5 使用 ADF4350,但是数据手册中描述温度变化有可能导致失锁。请问我的设计要应

用在温度变化比较大的环境下,是否适用? ..............................................................................32

3.4.6

ADF4360-7 频率输出 范围为 300-1800MHz,请问 1500-1800MHz 频率 范围 ,

ADF4360-7 该如何使用,L 值该如何选取?...............................................................................32

PLL 的几个特殊应用..............................................................................................................34

3.5.1 分频 – 获得高精度时钟参考源 ....................................................................................34

3.5.2

PLL,VCO 闭环调制,短程无线发射芯片..................................................................34

3.5.3

PLL,VCO 开环调制......................................................................................................34

3.5.4 解调 ..................................................................................................................................35

3.5.5 时钟净化----时钟抖动(jitter)更小..............................................................................35

3.5.6 时钟恢复(Clock Recovery).........................................................................................35

4 参考资料..................................................................................................................................................36

3.5

2

�

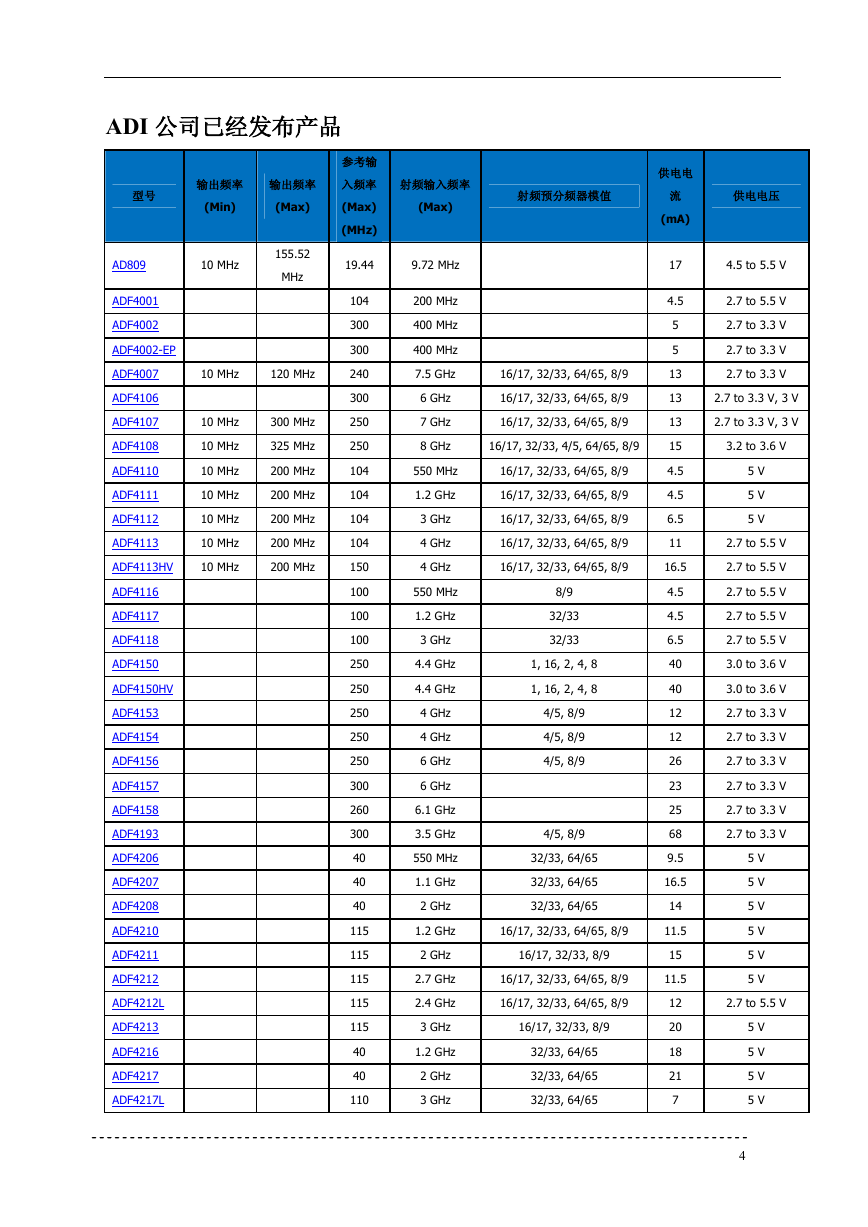

1 ADI 公司锁相环产品概述

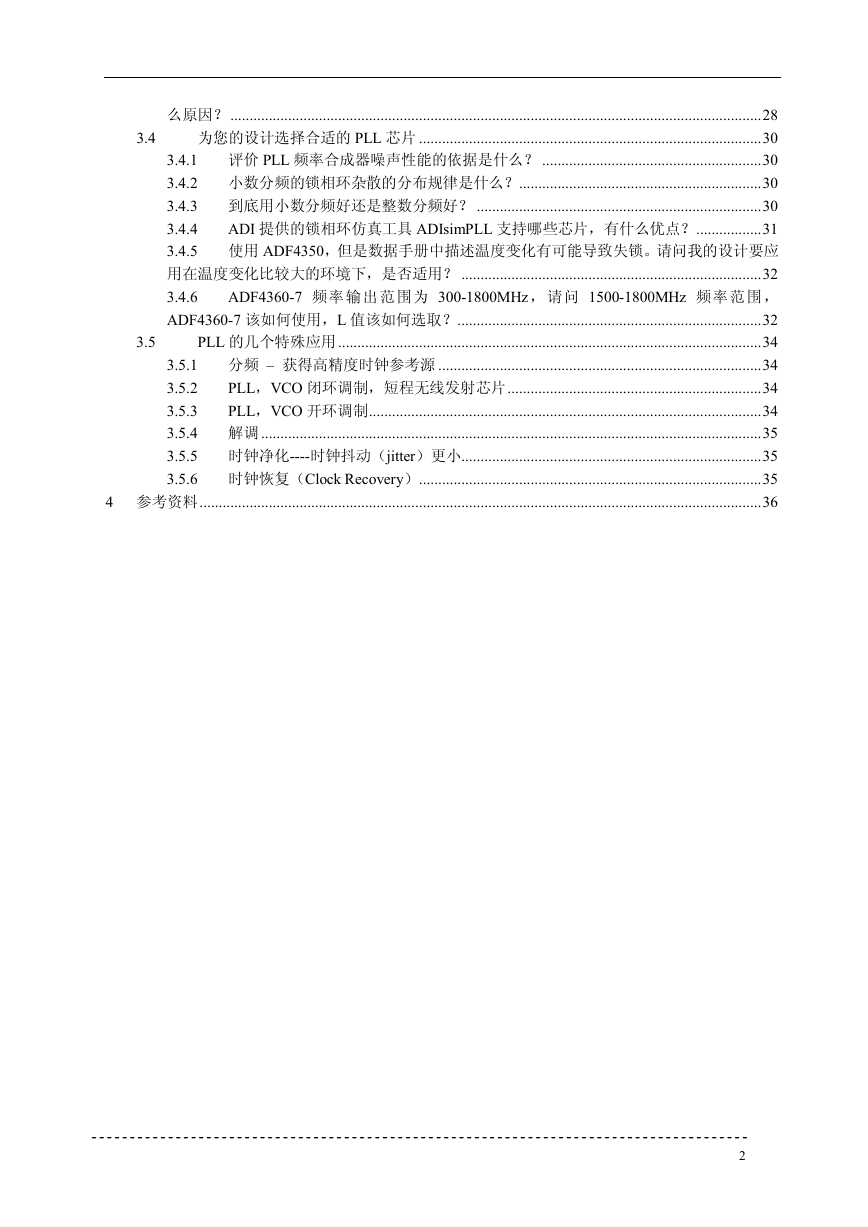

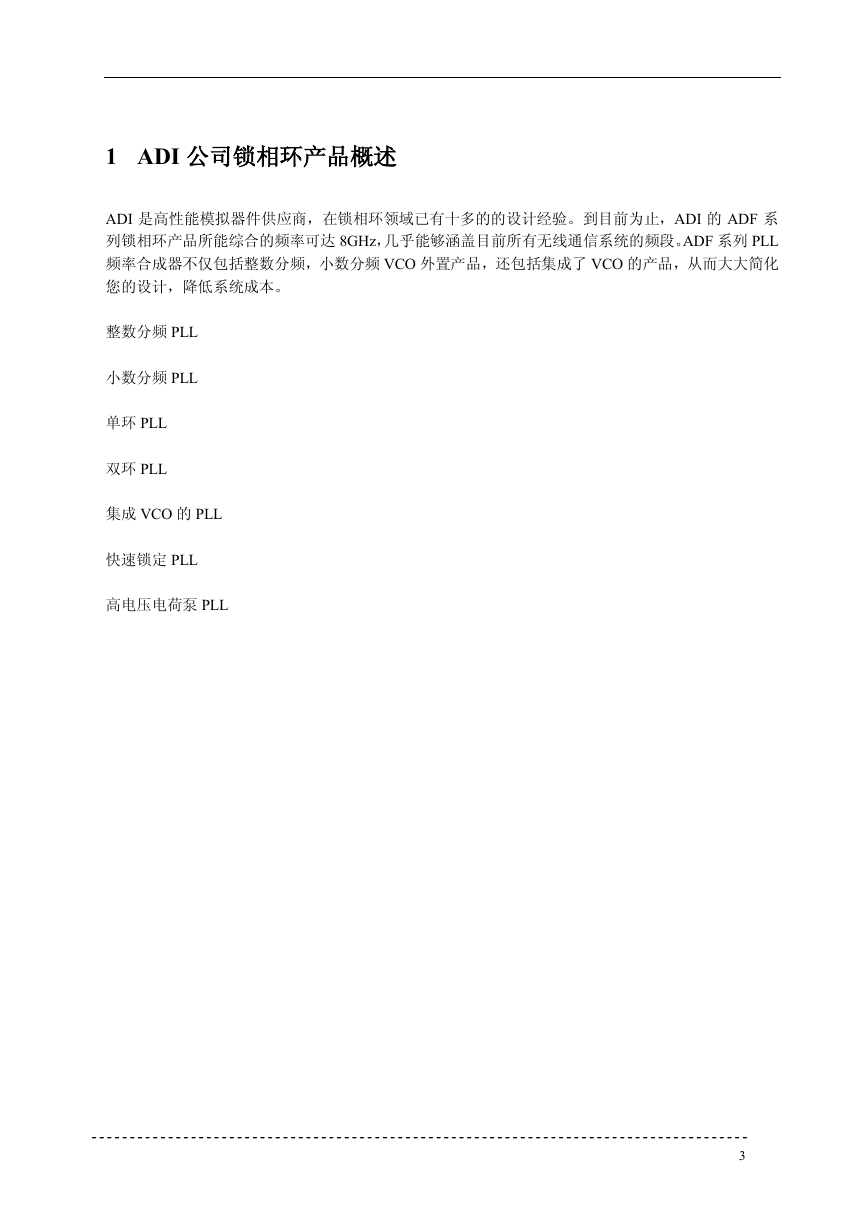

ADI 是高性能模拟器件供应商,在锁相环领域已有十多的的设计经验。到目前为止,ADI 的 ADF 系

列锁相环产品所能综合的频率可达 8GHz,几乎能够涵盖目前所有无线通信系统的频段。ADF 系列 PLL

频率合成器不仅包括整数分频,小数分频 VCO 外置产品,还包括集成了 VCO 的产品,从而大大简化

您的设计,降低系统成本。

整数分频 PLL

小数分频 PLL

单环 PLL

双环 PLL

集成 VCO 的 PLL

快速锁定 PLL

高电压电荷泵 PLL

3

�

ADI 公司已经发布产品

输出频率

输出频率

入频率

射频输入频率

参考输

型号

(Min)

(Max)

AD809

10 MHz

ADF4001

ADF4002

ADF4002-EP

155.52

MHz

ADF4007

ADF4106

ADF4107

ADF4108

ADF4110

ADF4111

ADF4112

ADF4113

10 MHz

120 MHz

10 MHz

300 MHz

10 MHz

325 MHz

10 MHz

200 MHz

10 MHz

200 MHz

10 MHz

200 MHz

10 MHz

200 MHz

ADF4113HV

10 MHz

200 MHz

ADF4116

ADF4117

ADF4118

ADF4150

ADF4150HV

ADF4153

ADF4154

ADF4156

ADF4157

ADF4158

ADF4193

ADF4206

ADF4207

ADF4208

ADF4210

ADF4211

ADF4212

ADF4212L

ADF4213

ADF4216

ADF4217

ADF4217L

(Max)

(MHz)

(Max)

19.44

9.72 MHz

104

300

300

240

300

250

250

104

104

104

104

150

100

100

100

250

250

250

250

250

300

260

300

40

40

40

115

115

115

115

115

40

40

110

200 MHz

400 MHz

400 MHz

7.5 GHz

6 GHz

7 GHz

8 GHz

550 MHz

1.2 GHz

3 GHz

4 GHz

4 GHz

550 MHz

1.2 GHz

3 GHz

4.4 GHz

4.4 GHz

4 GHz

4 GHz

6 GHz

6 GHz

6.1 GHz

3.5 GHz

550 MHz

1.1 GHz

2 GHz

1.2 GHz

2 GHz

2.7 GHz

2.4 GHz

3 GHz

1.2 GHz

2 GHz

3 GHz

射频预分频器模值

16/17, 32/33, 64/65, 8/9

16/17, 32/33, 64/65, 8/9

16/17, 32/33, 64/65, 8/9

16/17, 32/33, 4/5, 64/65, 8/9

16/17, 32/33, 64/65, 8/9

16/17, 32/33, 64/65, 8/9

16/17, 32/33, 64/65, 8/9

16/17, 32/33, 64/65, 8/9

供电电

流

(mA)

17

4.5

5

5

13

13

13

15

4.5

4.5

6.5

11

供电电压

4.5 to 5.5 V

2.7 to 5.5 V

2.7 to 3.3 V

2.7 to 3.3 V

2.7 to 3.3 V

2.7 to 3.3 V, 3 V

2.7 to 3.3 V, 3 V

3.2 to 3.6 V

5 V

5 V

5 V

2.7 to 5.5 V

16/17, 32/33, 64/65, 8/9

16.5

2.7 to 5.5 V

8/9

32/33

32/33

1, 16, 2, 4, 8

1, 16, 2, 4, 8

4/5, 8/9

4/5, 8/9

4/5, 8/9

4/5, 8/9

32/33, 64/65

32/33, 64/65

32/33, 64/65

16/17, 32/33, 64/65, 8/9

16/17, 32/33, 8/9

16/17, 32/33, 64/65, 8/9

16/17, 32/33, 64/65, 8/9

16/17, 32/33, 8/9

32/33, 64/65

32/33, 64/65

32/33, 64/65

4.5

4.5

6.5

40

40

12

12

26

23

25

68

9.5

16.5

14

11.5

15

11.5

12

20

18

21

7

2.7 to 5.5 V

2.7 to 5.5 V

2.7 to 5.5 V

3.0 to 3.6 V

3.0 to 3.6 V

2.7 to 3.3 V

2.7 to 3.3 V

2.7 to 3.3 V

2.7 to 3.3 V

2.7 to 3.3 V

2.7 to 3.3 V

5 V

5 V

5 V

5 V

5 V

5 V

2.7 to 5.5 V

5 V

5 V

5 V

5 V

4

�

ADF4218

ADF4218L

ADF4219L

ADF4251

ADF4252

ADF4350

137.5 MHz

4.4 GHz

ADF4360-0

2.4 GHz

2.725 GHz

ADF4360-1

2.05 GHz

2.45 GHz

ADF4360-2

1.85 GHz

2.15 GHz

ADF4360-3

1.6 GHz

1.95 GHz

ADF4360-4

1.45 GHz

1.75 GHz

ADF4360-5

1.2 GHz

1.4 GHz

ADF4360-6

1.05 GHz

1.25 GHz

ADF4360-7

350 MHz

1.8 GHz

ADF4360-8

65 MHz

400 MHz

ADF4360-9

1.1 MHz

200 MHz

40

110

110

150

150

250

250

250

250

250

250

250

250

250

250

250

2.5 GHz

3 GHz

3 GHz

3 GHz

3 GHz

32/33, 64/65

32/33, 64/65

32/33, 64/65

4/5, 8/9

4/5, 8/9

4/5, 8/9

16/17, 32/33, 8/9

16/17, 32/33, 8/9

16/17, 32/33, 8/9

16/17, 32/33, 8/9

16/17, 32/33, 8/9

16/17, 32/33, 8/9

16/17, 32/33, 8/9

16/17, 8/9

16/17, 32/33, 8/9

25.6

7

7

13

12

27

35

35

35

35

35

35

35

35

35

23

5 V

5 V

5 V

3 V

2.7 to 3.3 V

3.0 to 3.6 V

3.0 to 3.6 V

3.0 to 3.6 V

3.0 to 3.6 V

3.0 to 3.6 V

3.0 to 3.6 V

3.0 to 3.6 V

3.0 to 3.6 V

3.0 to 3.6 V, 3.3

V

3.0 to 3.6 V

3.0 to 3.6 V

5

�

2 PLL 主要技术指标

2.1 相位噪声

对一个给定载波功率的输出频率来说,相位噪声是载波功率相对于给定的频率偏移处(频率合成器通

常定义 1kHz 频率偏移)1-Hz 的带宽上的功率,单位为 dBc/Hz @ offset frequency。锁相环频率合成器

的带内相位噪声主要取决于频率合成器,VCO 的贡献很小。

相位噪声的测量需要频谱分析仪。注意一点,普通频谱分析仪读出的数据需要考虑分辨带宽的影响,

并且频谱仪要具有 Marker Noise 的功能,这样可以直接从频谱仪上得到 Marker Noise(PN)的值,

如果没有 Marker Noise 的功能,则需要通过 Marker 在指定偏移处测量噪声的值,然后再通过公式

(MKR Noise = MKR Value - 10logRBW)得出相噪值。高端的频谱分析仪或相位噪声测试仪往往可

以直接给出单边带相位噪声。

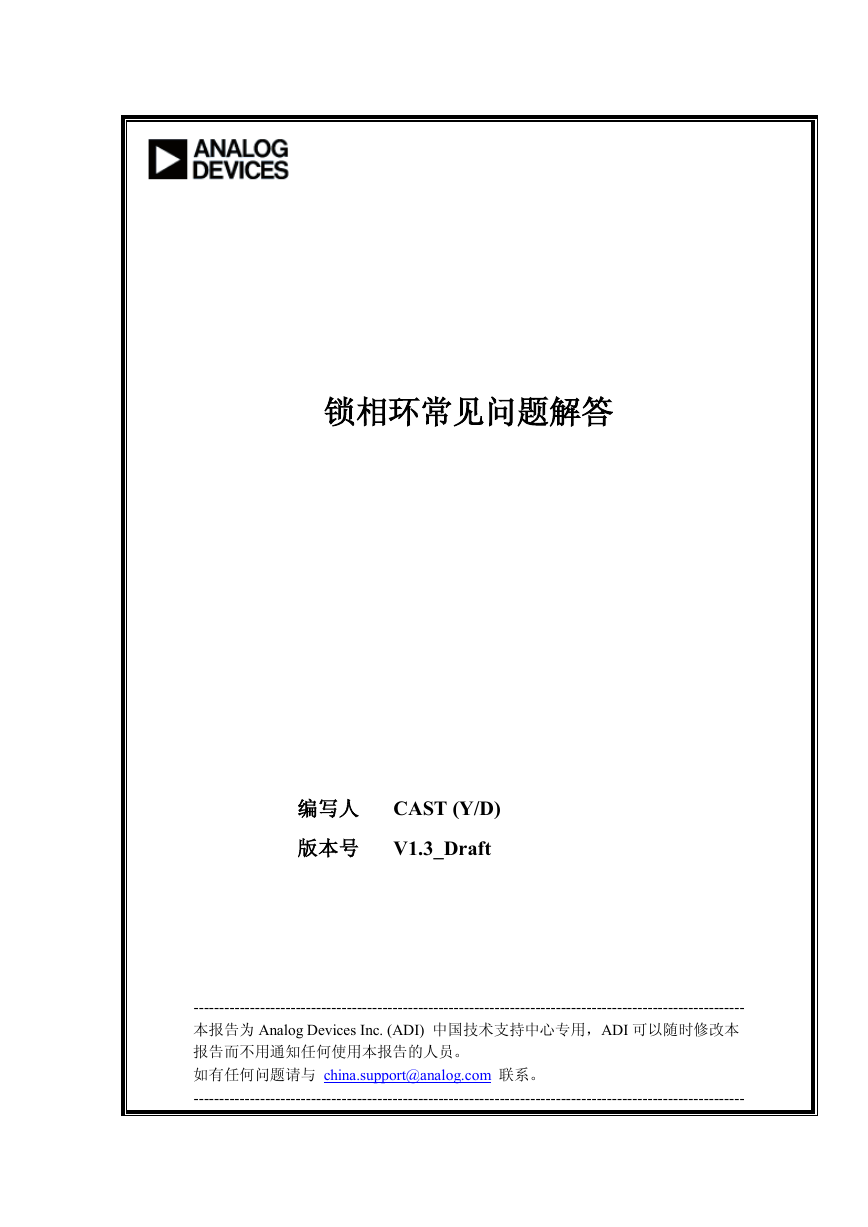

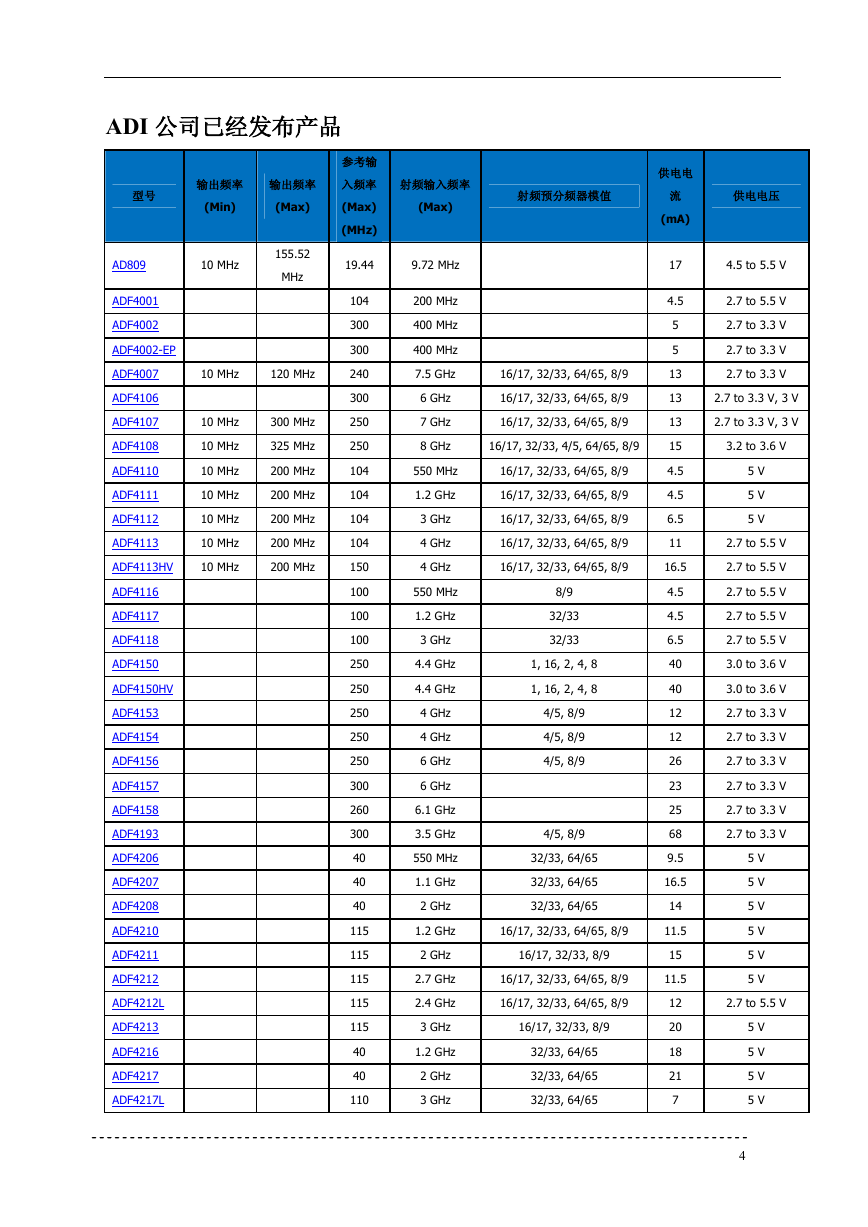

相位噪声是信号在频域的度量。在时域,与之对应的是时钟抖动(jitter),它是相位噪声在时间域里的

反映,大的时钟抖动在高速 ADC 应用中会严重恶化采样数据的信噪比,尤其是当 ADC 模拟前端信号

的频率较高时,更是要求低抖动的时钟。图 1 形象地描述了时钟抖动。

图 1 相位噪声和时钟抖动

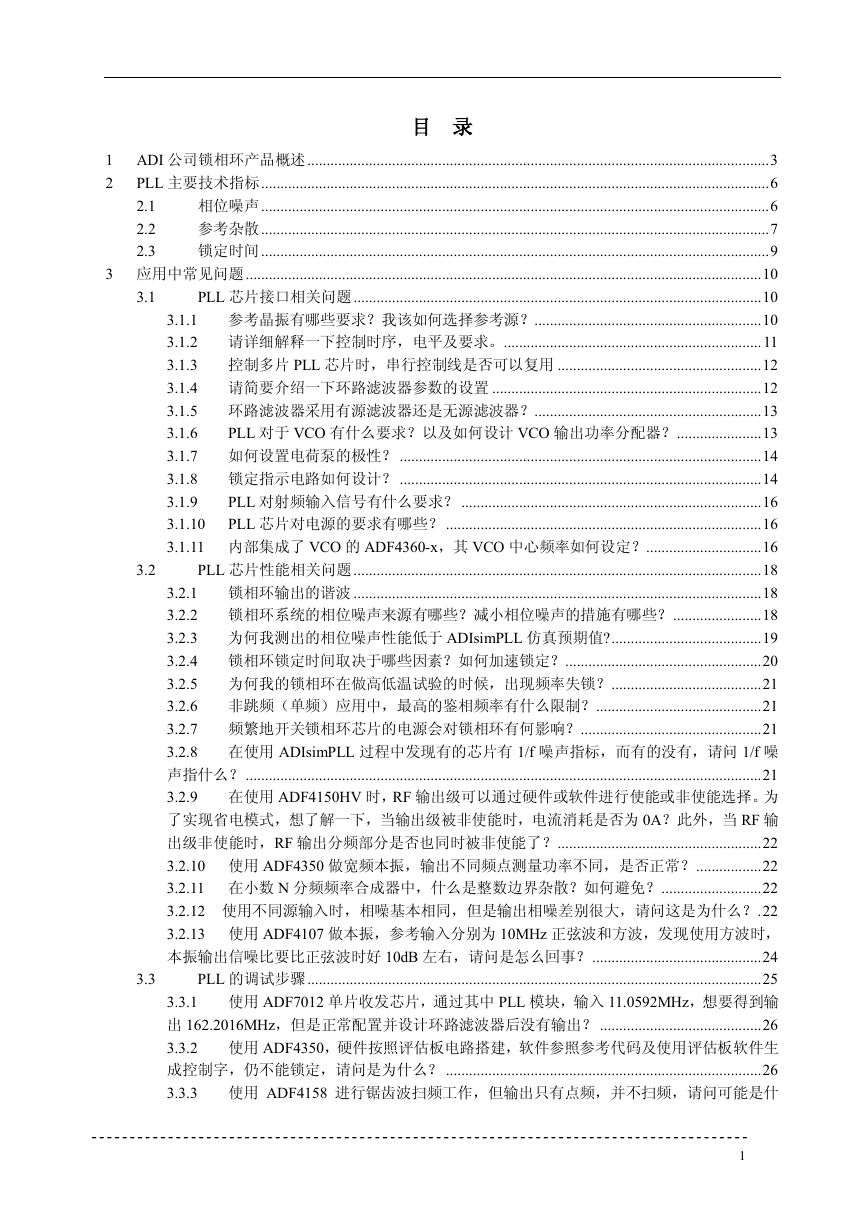

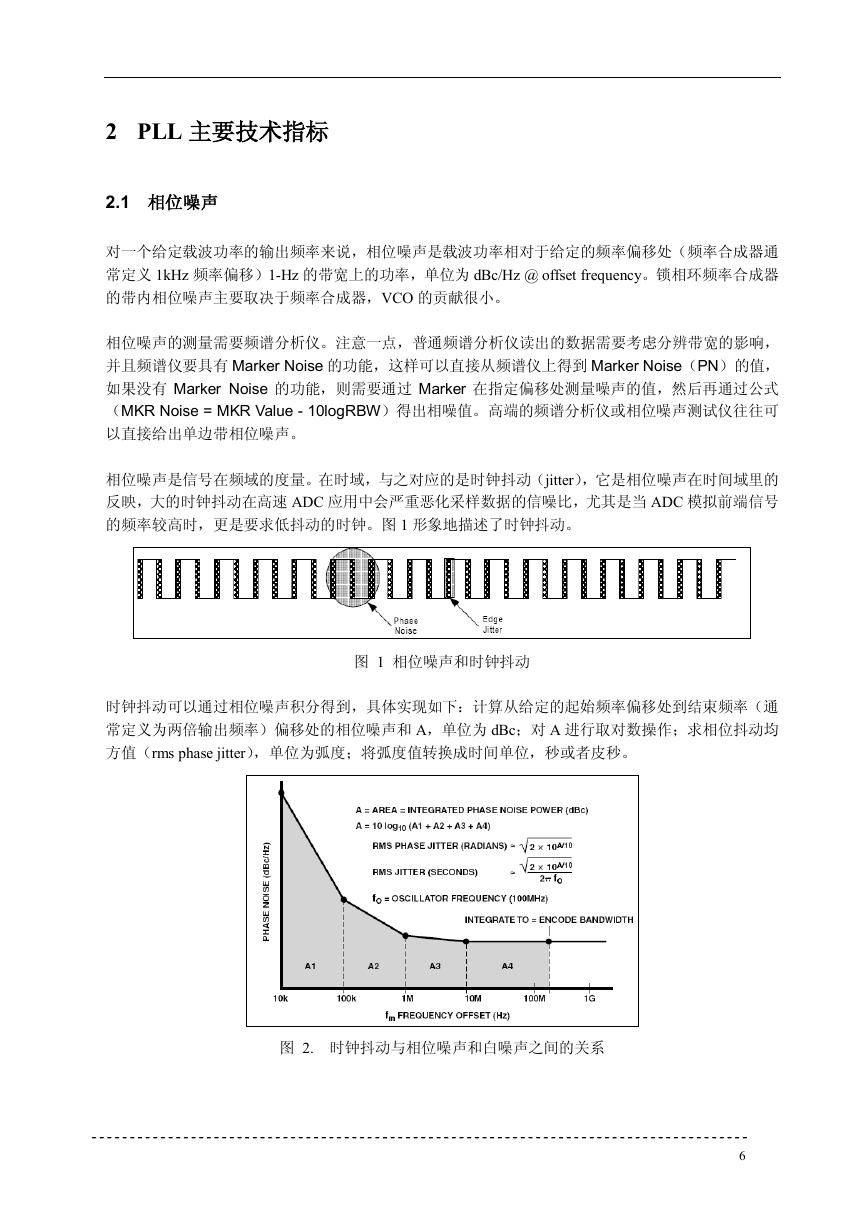

时钟抖动可以通过相位噪声积分得到,具体实现如下:计算从给定的起始频率偏移处到结束频率(通

常定义为两倍输出频率)偏移处的相位噪声和 A,单位为 dBc;对 A 进行取对数操作;求相位抖动均

方值(rms phase jitter),单位为弧度;将弧度值转换成时间单位,秒或者皮秒。

图 2. 时钟抖动与相位噪声和白噪声之间的关系

6

�

2.2 参考杂散

锁相环中最常见的杂散信号就是参考杂散。这些杂散信号会由于电荷泵源电流与汇电流的失配,电荷

泵漏电流,以及电源退耦不够而增大。在接收机设计中,杂散信号与其他干扰信号相混频有可能产生

有用信号频率从而降低接收机的灵敏度。锁相环处于锁定状态时,电荷泵会周期性的(频率等于鉴相

频率)产生交替变换(正负)脉冲电流给环路滤波器。环路滤波器对其进行积分产生稳定的控制电压。

图 3 环路锁定时,PLL 电荷泵电流输出波形

当鉴相频率较低时,由电荷泵的漏电流引起的杂散占主要地位。

当鉴相频率较高时,由电荷泵的交替电流(源电流 source

I

和汇电流 sink

I )引起的杂散占主要地位。

二者频率的界定。一般地,若电荷泵漏电流为 1nA,电荷泵电流为 1mA,电荷泵电流的失配在 4%时,

交界频率大约为 100k~200kHz。

当电荷泵处于三态的时候(绝大部分时间是如此),电荷泵的漏电流是杂散的主要来源。电荷泵漏电

流经过环路滤波器形成控制电压,以调谐 VCO,这样就相当于对 VCO 进行调频(FM),反映在 VCO

的输出,就会出现杂散信号。电荷泵漏电流越大,鉴相频率越低,这种参考杂散越大。在鉴相频率相

等的条件下,电荷泵的漏电流与电荷泵电流的比值越大,由电荷泵漏电流引起的参考杂散会越大。ADI

的 PLL 产品漏电流大部分在 1nA 左右的水平上。

为了对电荷泵漏电流引起的杂散有个清楚地认识,这里给出一些仿真波形。仿真条件如下:ADF4106,

输出频率 1GHz,鉴相频率 25kHz,三阶无源滤波器,带宽 2.5Hz,相位裕度 45 度,VCO 模型为 Sirenza

VCO190-1000T。参考晶振模型 10MHz。电荷泵漏电流 1nA。

Leakage Spurs at 1.00GHz

)

c

B

d

(

l

e

v

e

L

r

u

p

S

0

-10

-20

-30

-40

-50

-60

-70

-80

-90

-100

-110

-120

-250 -200 -150 -100

100

200

250

Offset Frequency (kHz)

150

-50

0

50

图 4

当环路滤波器变窄到 1kHz 后可以看到对这种杂散的衰减效果如下。

7

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc