武汉理工大学数字逻辑实验

实验 1

实验名称:一位全加器(综合验证性)

一、目的与要求

1、熟悉组合逻辑电路,通过用门电路构成一位全加器组合逻辑

电路。掌握组合逻辑电路的基本概念,组合逻辑电路的结构。

2、通过用门电路构成一位全加器组合逻辑电路。能够正确构成

的一位全加器组合逻辑电路。

3、能够正确,整洁画出逻辑电路图;正确标出集成电路引脚;

能够正确连接逻辑电路;能够分析和解决在实验中碰见的问题;解决

问题的思路和方法正确;实验结果满足题目要求。

二、实验器材和集成电路

1、数字逻辑实验板一块。

2、3 片 74LS00,连结导线 50 根。

(74LS00 可以用 74LS04、74LS08 组合代替)

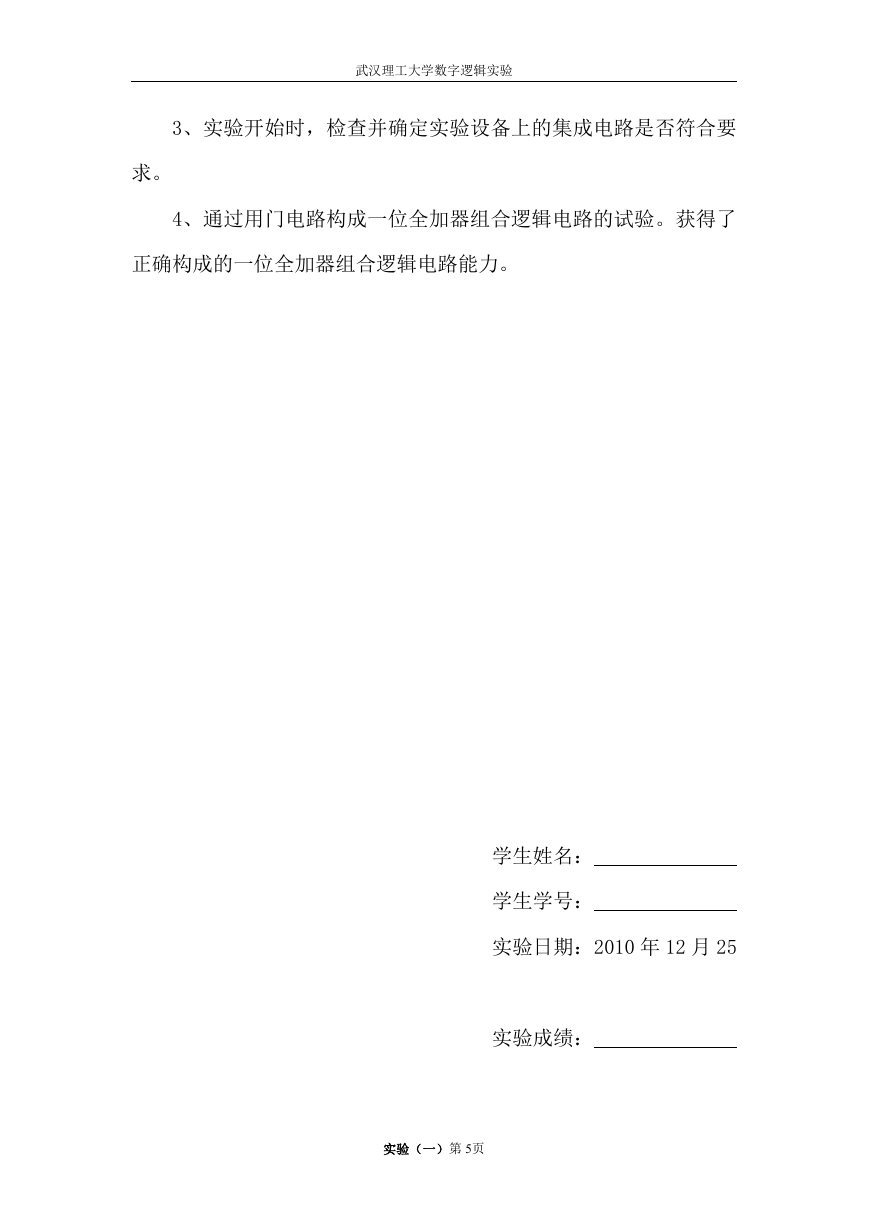

三、题目理解和功能描述

设一位全加器有三个输入端 Ai、Bi、Ci-1,两个输出端 Si、Ci。

以 k1、k2 两盏灯为显示输出。一位全加器

的逻辑符号如下图所示:

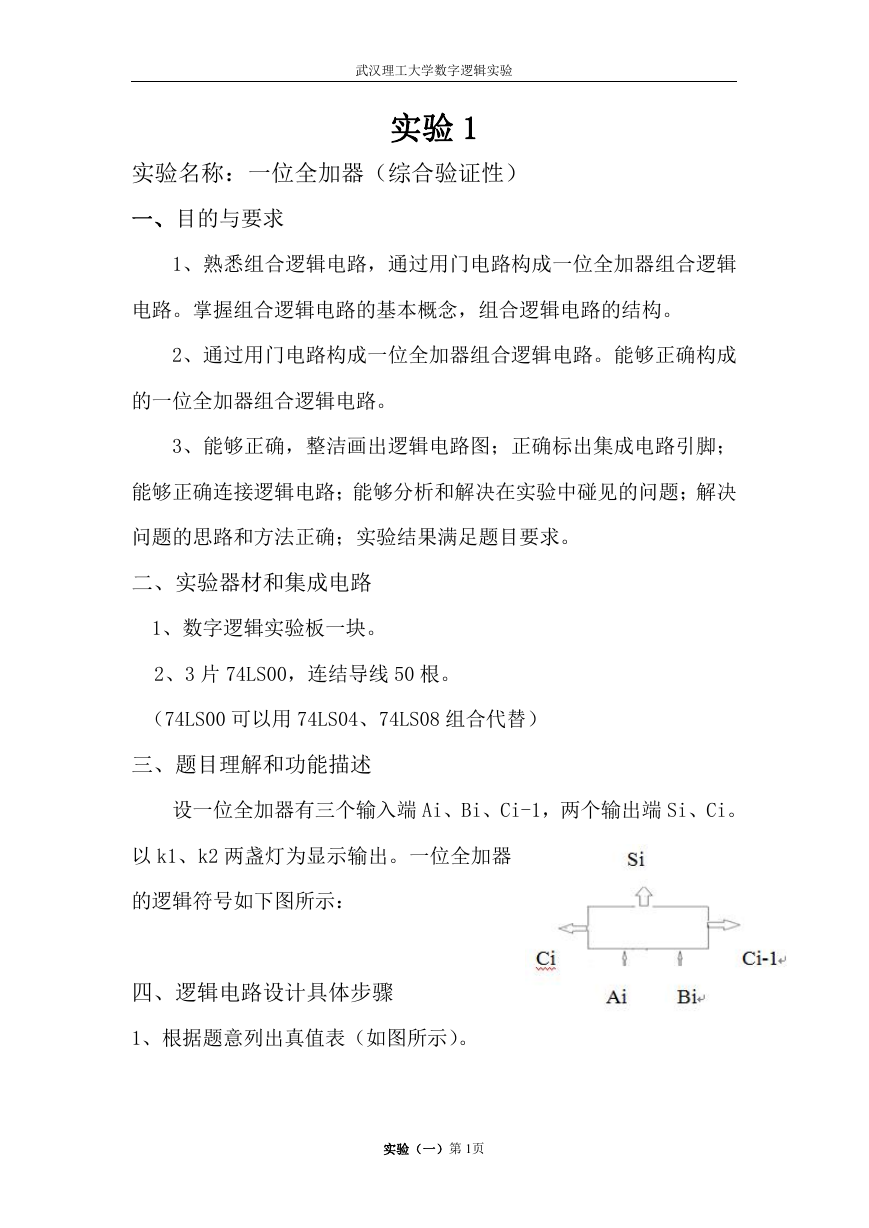

四、逻辑电路设计具体步骤

1、根据题意列出真值表(如图所示)。

实验(一)第 1页

�

武汉理工大学数字逻辑实验

表 1-1 真值表

Ci-1

0

1

0

1

0

1

0

1

Si

0

1

1

0

1

0

0

1

Ci

0

0

0

1

0

1

1

1

Ai

0

0

0

0

1

1

1

1

Bi

0

0

1

1

0

0

1

1

2、写出逻辑函数表达式。

S

i

A BC

i

i

i

1

A B C

i

i

i

1

A B C

i

i

i

1

A BC

i

i

i

1

C A BC

i

i

i

i

A BC

i

i

i

1

A B C

i

i

i

1

A BC

i

i

i

1

1

对逻辑函数表达式 iS , iC 进行变换,使用“与非”表达式。

S

i

SC C SSC

i

1

1

i

i

1

C SC A B

i

i

1

i

i

其中 S A B AB AB

。

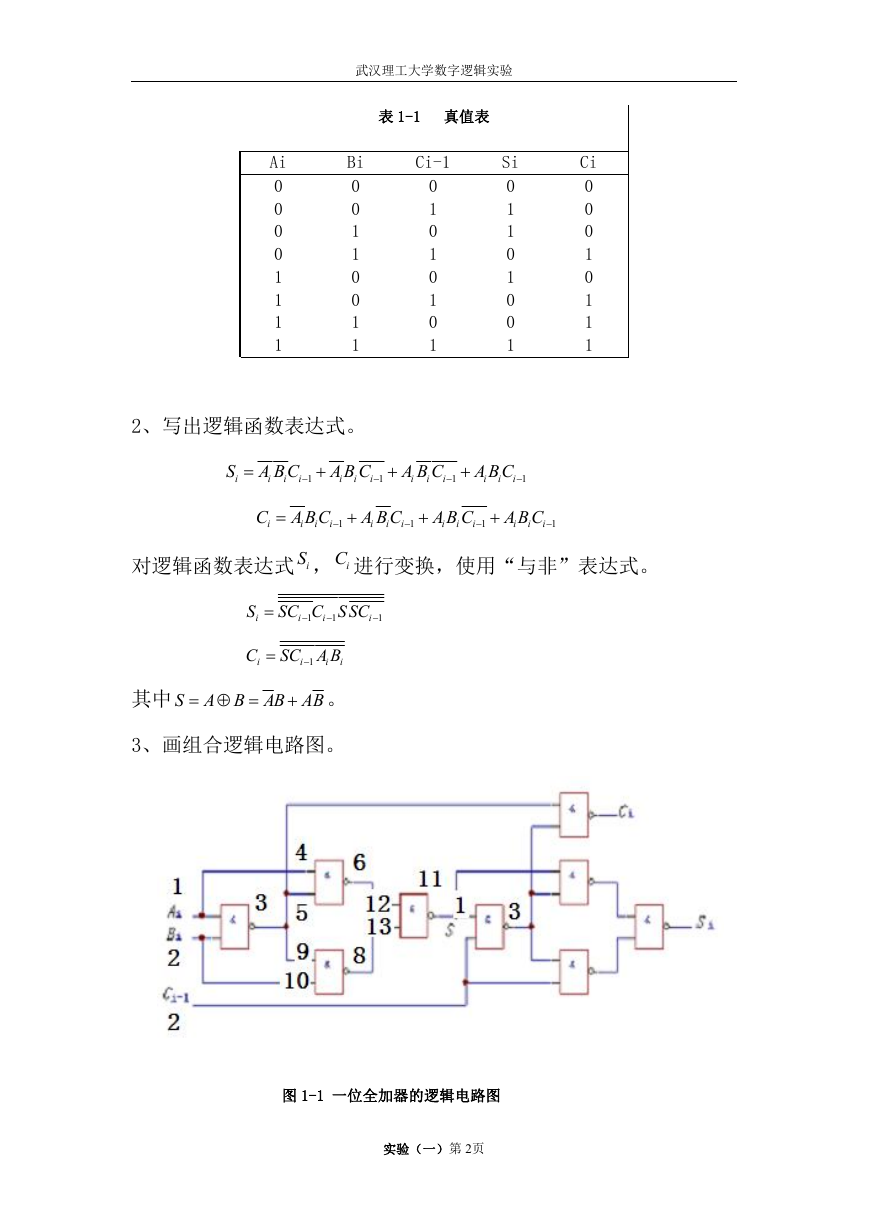

3、画组合逻辑电路图。

图 1-1 一位全加器的逻辑电路图

实验(一)第 2页

�

武汉理工大学数字逻辑实验

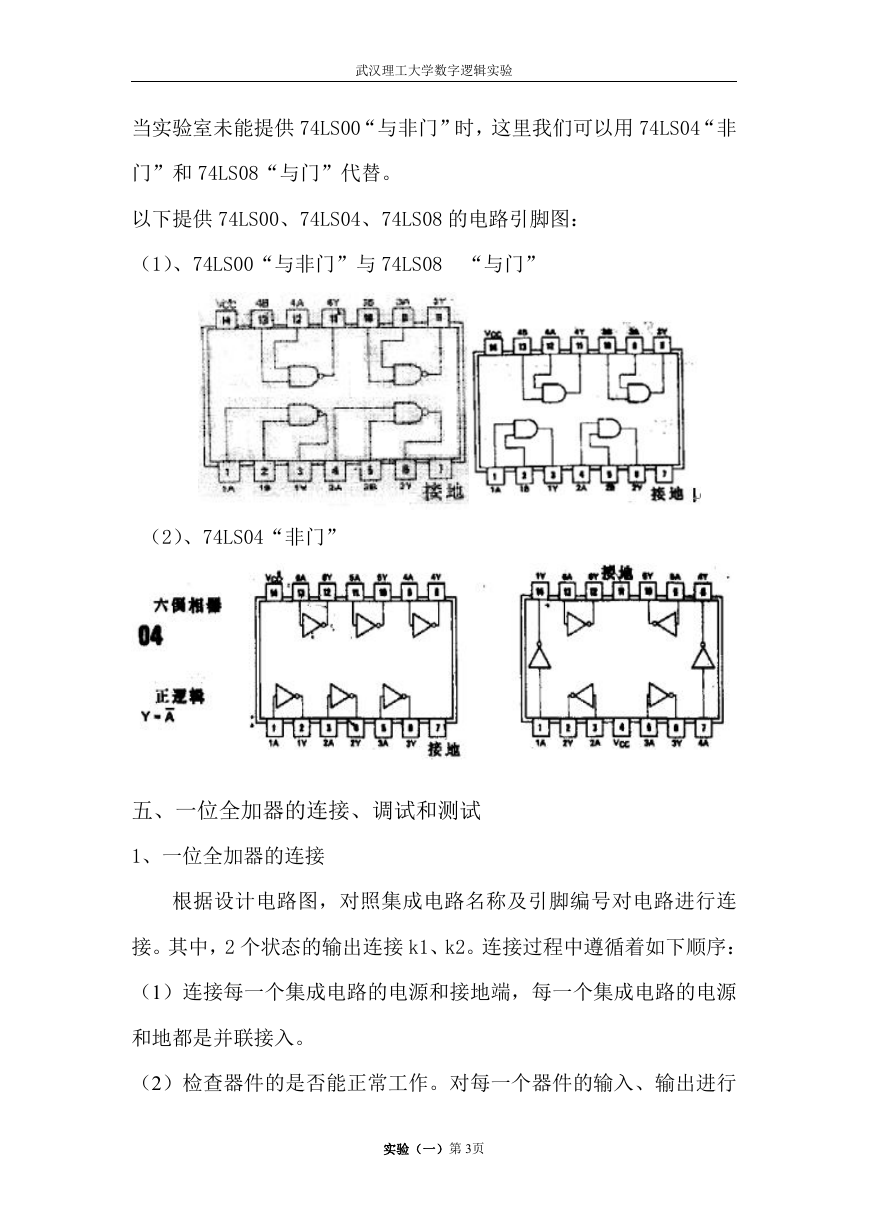

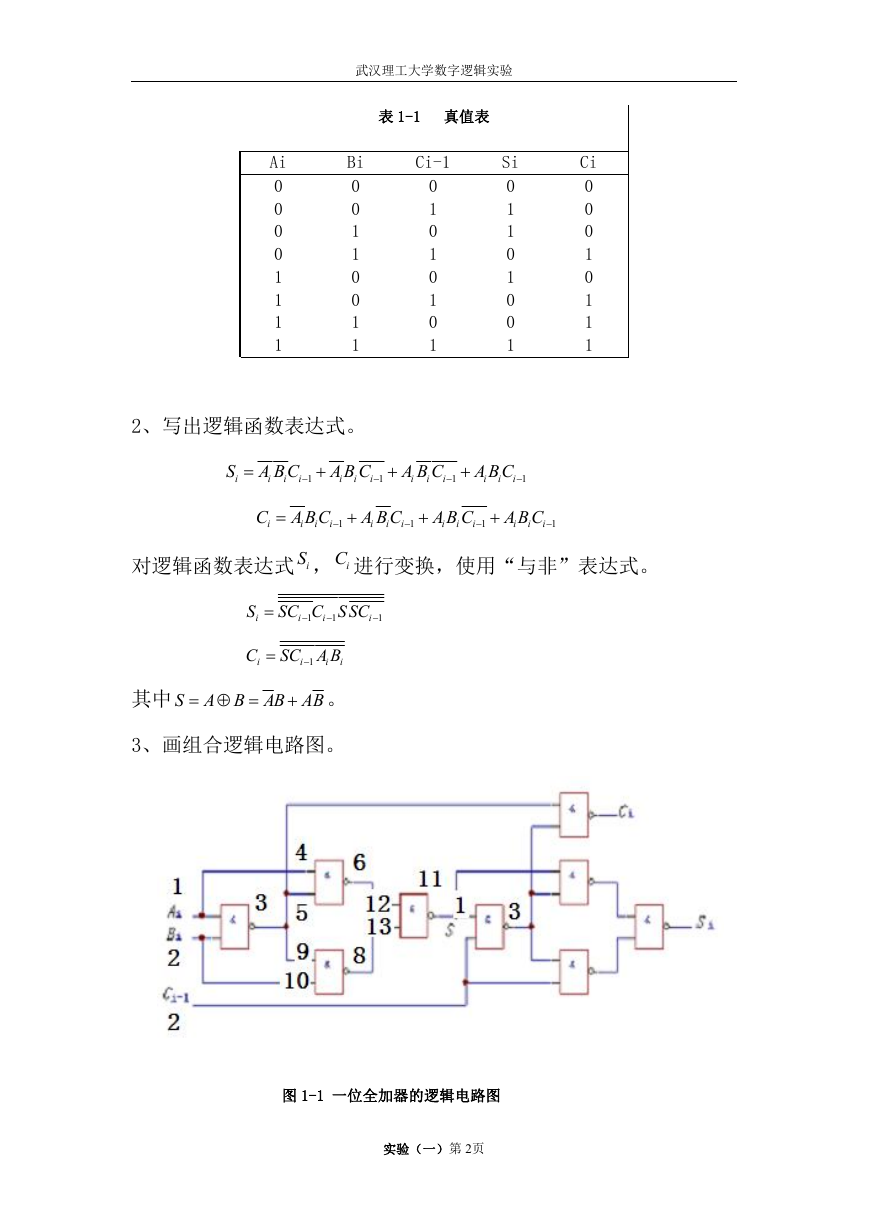

当实验室未能提供 74LS00“与非门”时,这里我们可以用 74LS04“非

门”和 74LS08“与门”代替。

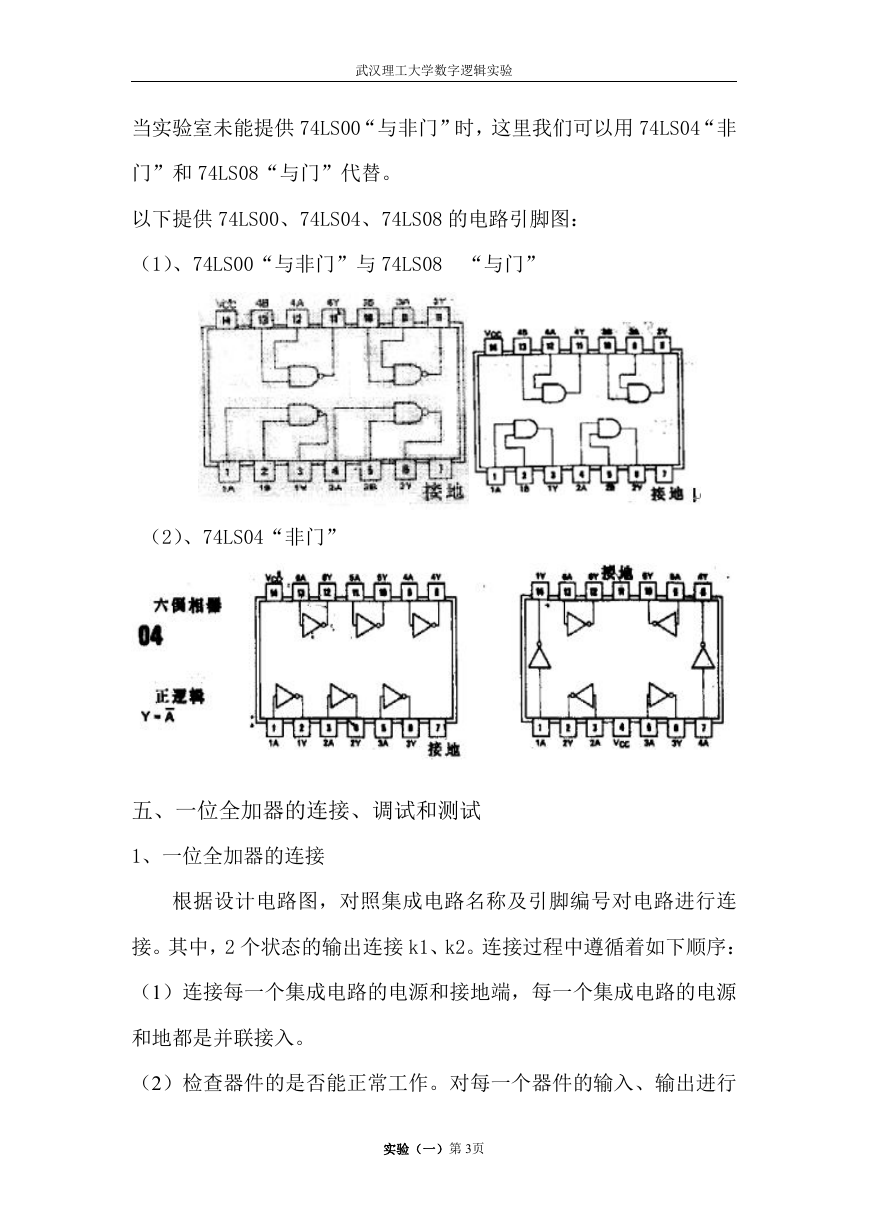

以下提供 74LS00、74LS04、74LS08 的电路引脚图:

(1)、74LS00“与非门”与 74LS08 “与门”

(2)、74LS04“非门”

五、一位全加器的连接、调试和测试

1、一位全加器的连接

根据设计电路图,对照集成电路名称及引脚编号对电路进行连

接。其中,2 个状态的输出连接 k1、k2。连接过程中遵循着如下顺序:

(1)连接每一个集成电路的电源和接地端,每一个集成电路的电源

和地都是并联接入。

(2)检查器件的是否能正常工作。对每一个器件的输入、输出进行

实验(一)第 3页

�

武汉理工大学数字逻辑实验

检查,以便顺利进入计数器的连接,较少错误的干扰。

(3)计数器接线,接线顺序依照激励函数表达式的顺序,以免出现

漏连、错连的现象。

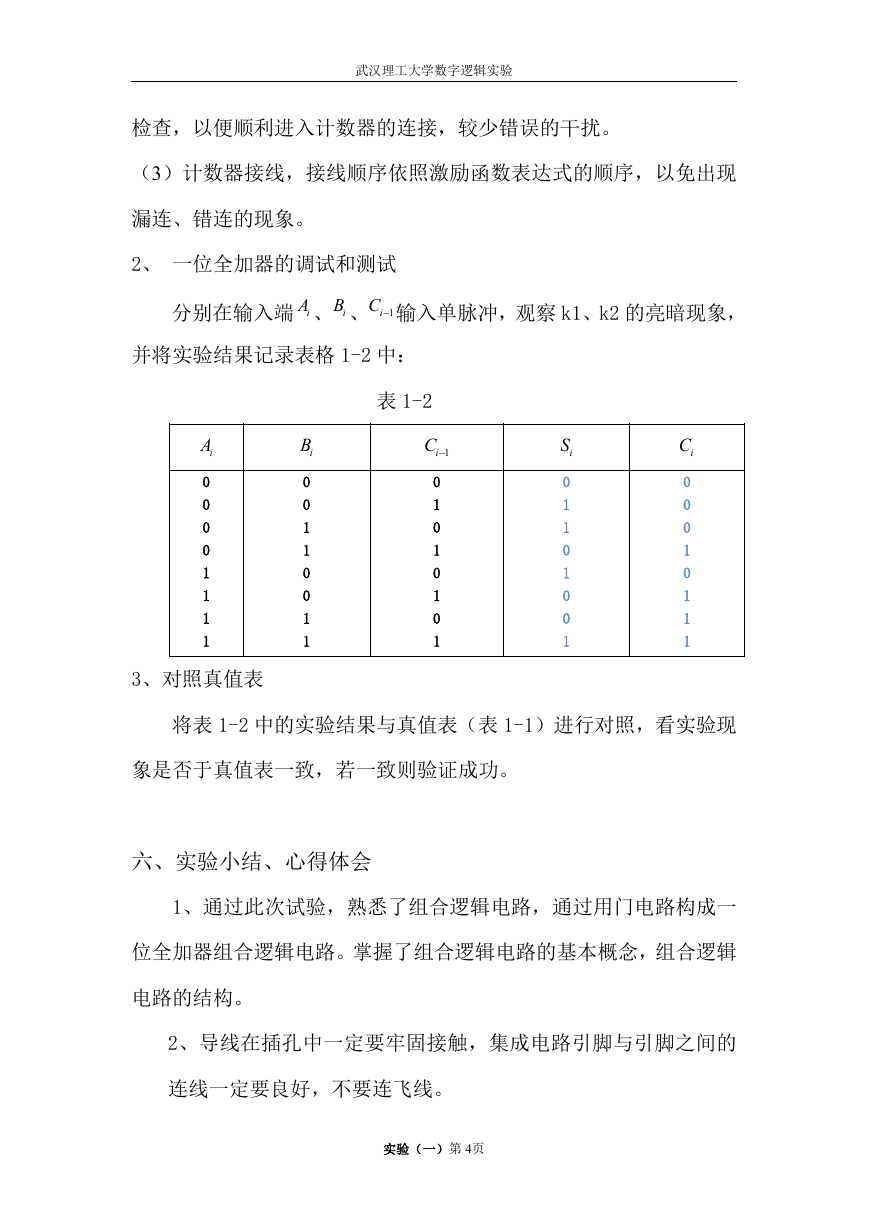

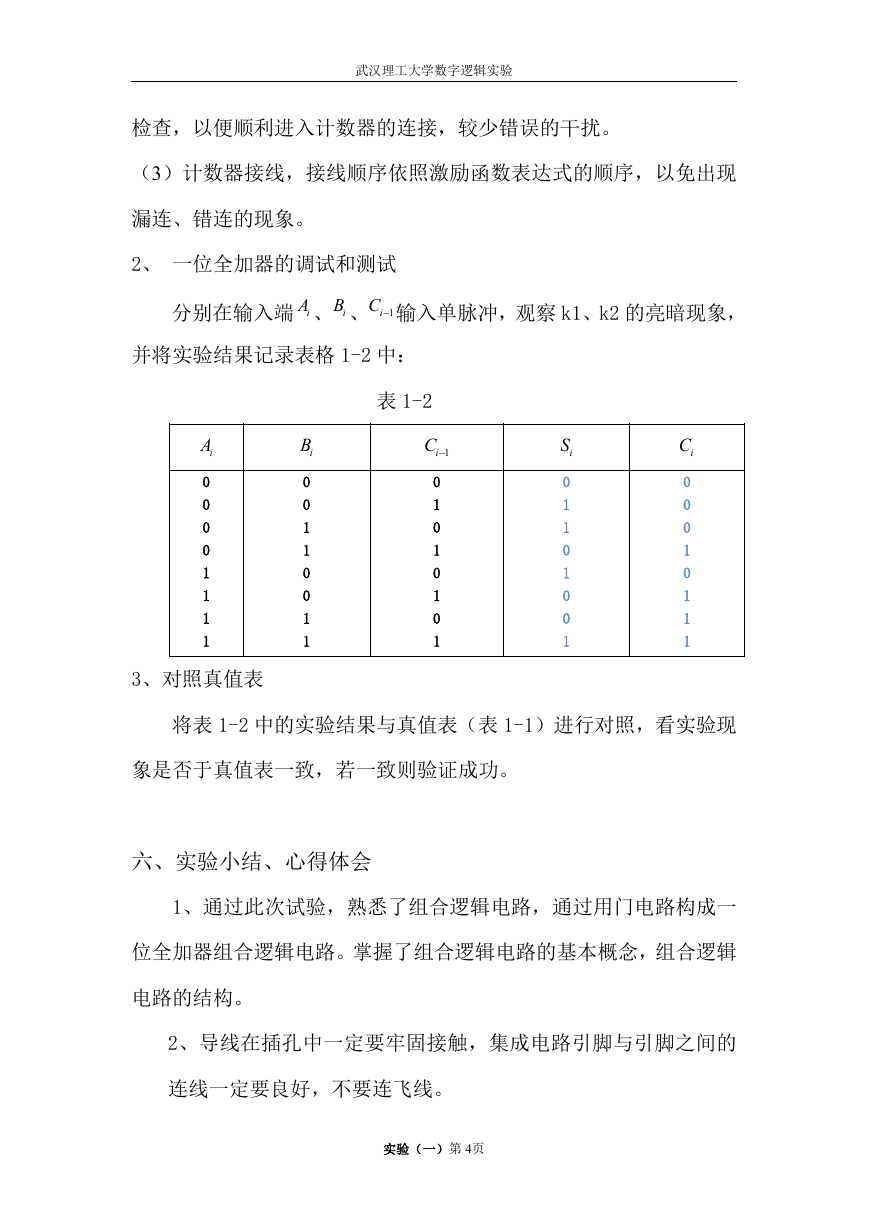

2、 一位全加器的调试和测试

分别在输入端 iA 、 iB 、 1iC 输入单脉冲,观察 k1、k2 的亮暗现象,

并将实验结果记录表格 1-2 中:

表 1-2

1iC

0

1

0

1

0

1

0

1

iB

0

0

1

1

0

0

1

1

iA

0

0

0

0

1

1

1

1

iS

0

1

1

0

1

0

0

1

iC

0

0

0

1

0

1

1

1

3、对照真值表

将表 1-2 中的实验结果与真值表(表 1-1)进行对照,看实验现

象是否于真值表一致,若一致则验证成功。

六、实验小结、心得体会

1、通过此次试验,熟悉了组合逻辑电路,通过用门电路构成一

位全加器组合逻辑电路。掌握了组合逻辑电路的基本概念,组合逻辑

电路的结构。

2、导线在插孔中一定要牢固接触,集成电路引脚与引脚之间的

连线一定要良好,不要连飞线。

实验(一)第 4页

�

武汉理工大学数字逻辑实验

3、实验开始时,检查并确定实验设备上的集成电路是否符合要

求。

4、通过用门电路构成一位全加器组合逻辑电路的试验。获得了

正确构成的一位全加器组合逻辑电路能力。

学生姓名:

学生学号:

实验日期:2010 年 12 月 25

实验成绩:

实验(一)第 5页

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc