计 算 机 组 成 原 理

实 验 教 程

山西大学计算机与信息技术学院

2013 年 8 月

1

�

计算机组成原理实验教程

山西大学计算机与信息技术学院

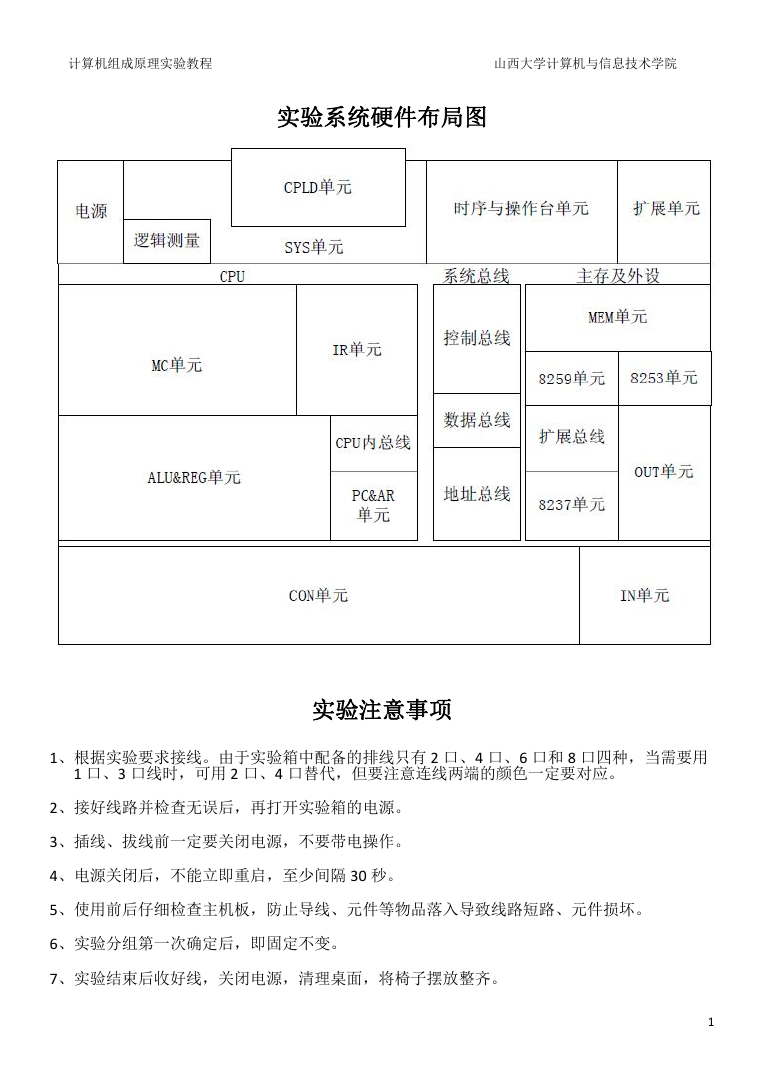

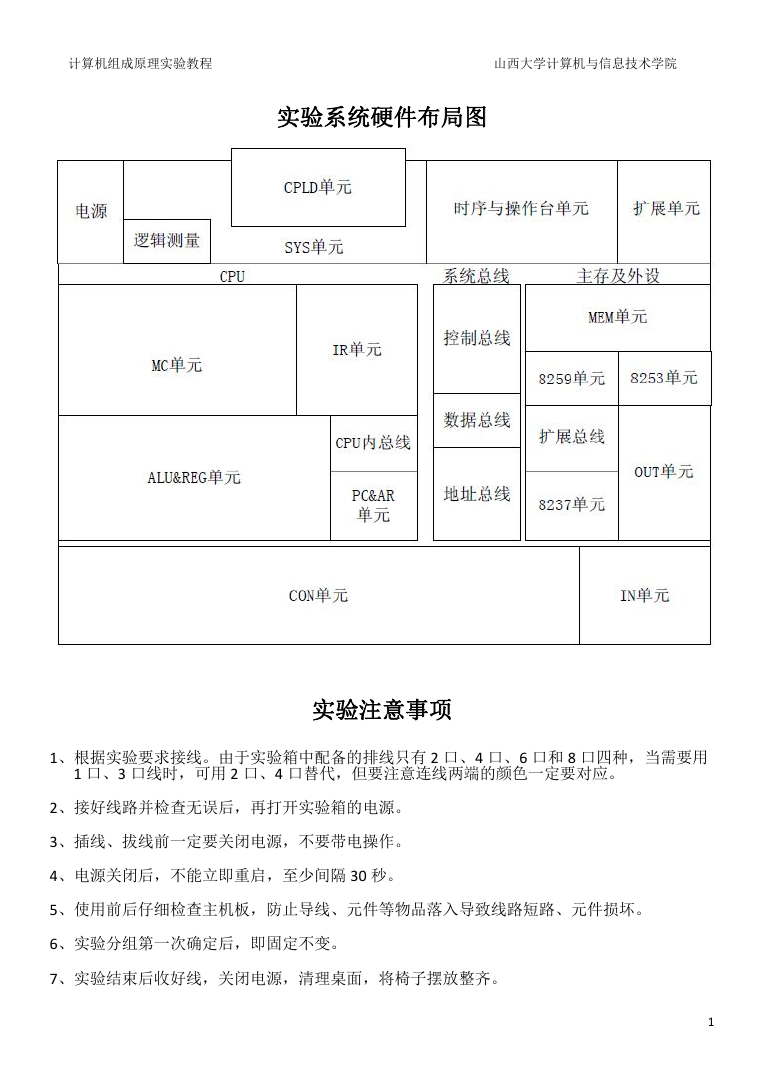

实验系统硬件布局图

实验注意事项

1、根据实验要求接线。由于实验箱中配备的排线只有 2 口、4 口、6 口和 8 口四种,当需要用

1 口、3 口线时,可用 2 口、4 口替代,但要注意连线两端的颜色一定要对应。

2、接好线路并检查无误后,再打开实验箱的电源。

3、插线、拔线前一定要关闭电源,不要带电操作。

4、电源关闭后,不能立即重启,至少间隔 30 秒。

5、使用前后仔细检查主机板,防止导线、元件等物品落入导致线路短路、元件损坏。

6、实验分组第一次确定后,即固定不变。

7、实验结束后收好线,关闭电源,清理桌面,将椅子摆放整齐。

1

�

计算机组成原理实验教程

山西大学计算机与信息技术学院

实验一 基本运算器实验

1.1 实验目的

(1) 了解运算器的组成结构。

(2) 掌握运算器的工作原理。

1.2 实验设备

PC 机一台,TD-CMA 实验系统一套。

1.3 实验原理

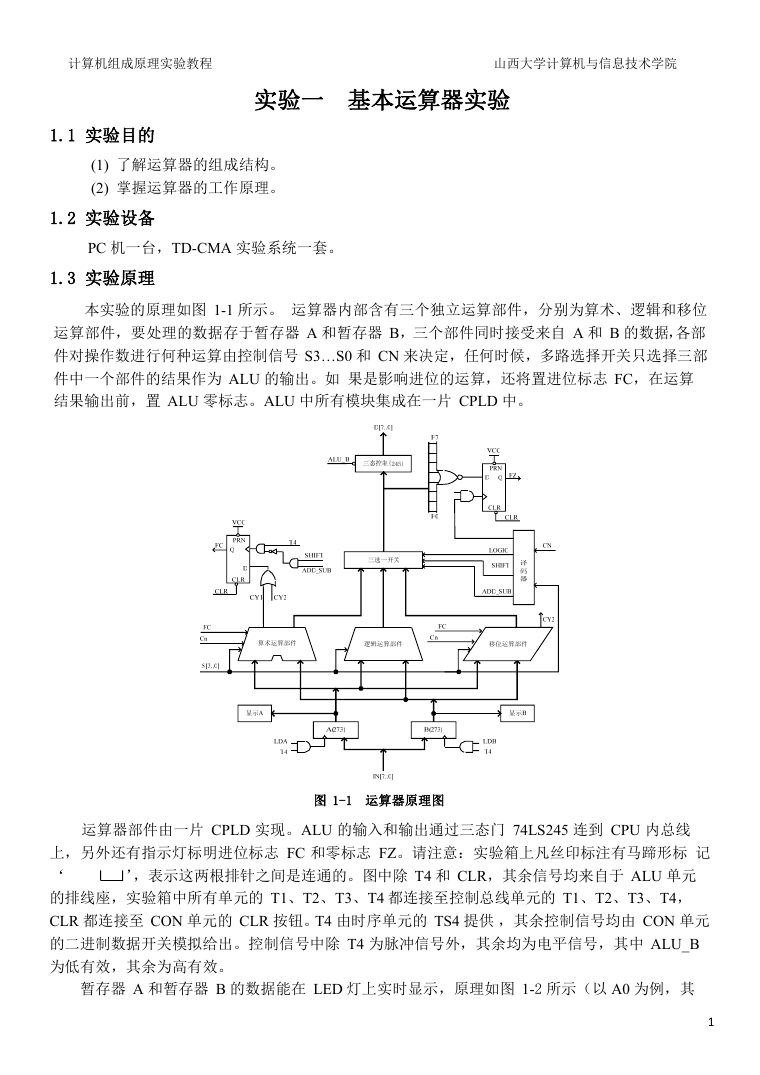

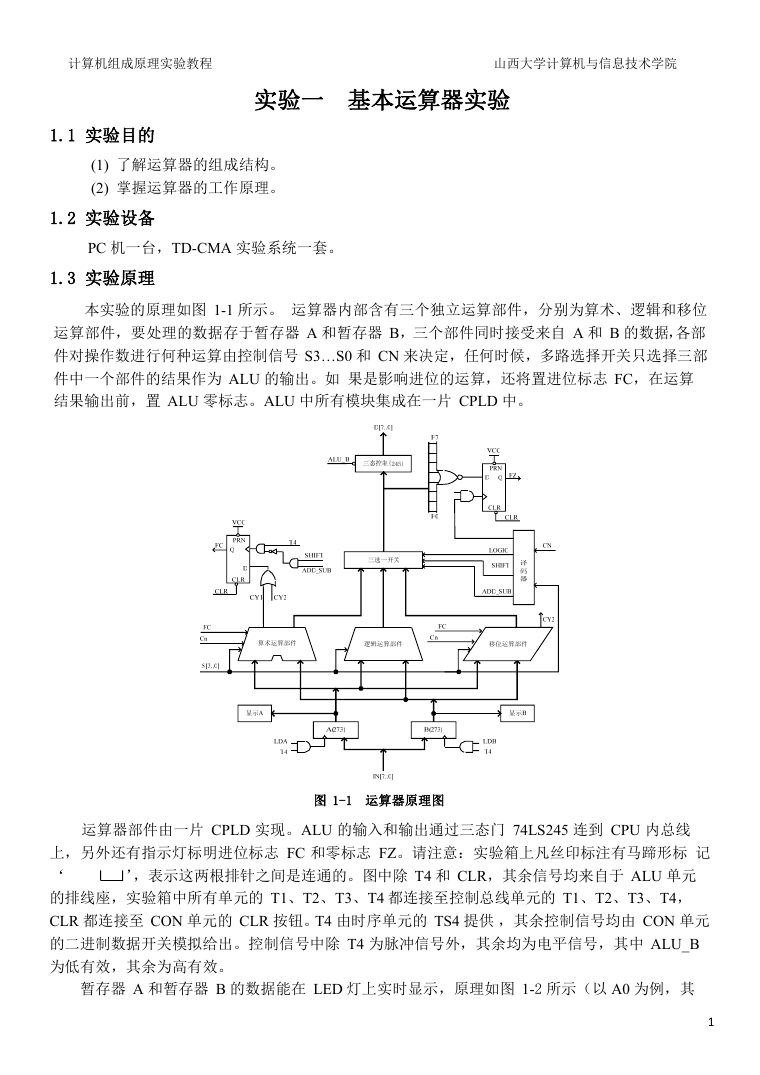

本实验的原理如图 1-1 所示。 运算器内部含有三个独立运算部件,分别为算术、逻辑和移位

运算部件,要处理的数据存于暂存器 A 和暂存器 B,三个部件同时接受来自 A 和 B 的数据,各部

件对操作数进行何种运算由控制信号 S3…S0 和 CN 来决定,任何时候,多路选择开关只选择三部

件中一个部件的结果作为 ALU 的输出。如 果是影响进位的运算,还将置进位标志 FC,在运算

结果输出前,置 ALU 零标志。ALU 中所有模块集成在一片 CPLD 中。

图 1-1 运算器原理图

运算器部件由一片 CPLD 实现。ALU 的输入和输出通过三态门 74LS245 连到 CPU 内总线

上,另外还有指示灯标明进位标志 FC 和零标志 FZ。请注意:实验箱上凡丝印标注有马蹄形标 记

’,表示这两根排针之间是连通的。图中除 T4 和 CLR,其余信号均来自于 ALU 单元

‘

的排线座,实验箱中所有单元的 T1、T2、T3、T4 都连接至控制总线单元的 T1、T2、T3、T4,

CLR 都连接至 CON 单元的 CLR 按钮。T4 由时序单元的 TS4 提供 ,其余控制信号均由 CON 单元

的二进制数据开关模拟给出。控制信号中除 T4 为脉冲信号外,其余均为电平信号,其中 ALU_B

为低有效,其余为高有效。

暂存器 A 和暂存器 B 的数据能在 LED 灯上实时显示,原理如图 1-2 所示(以 A0 为例,其

1

�

计算机组成原理实验教程

山西大学计算机与信息技术学院

它相同)。进位标志 FC、零标志 FZ 和数据总线 D7…D0 的显示原理也是如此。

VCC

1K

A0

图 1-2

A0 显示原理图

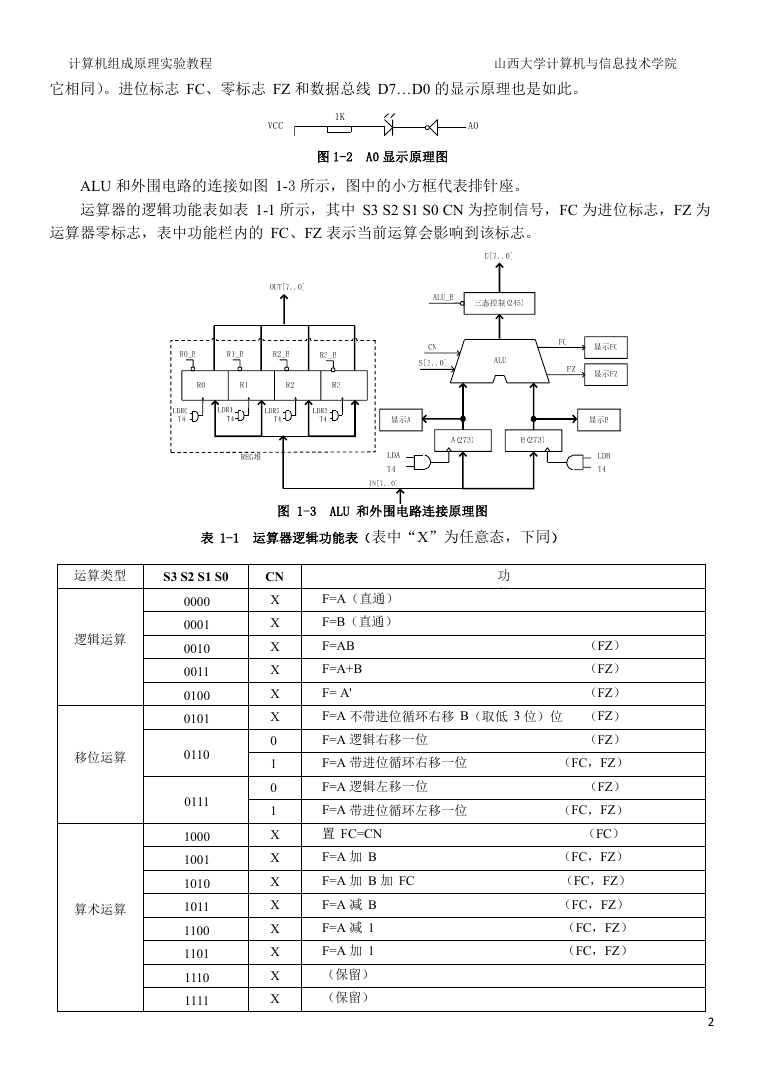

ALU 和外围电路的连接如图 1-3 所示,图中的小方框代表排针座。

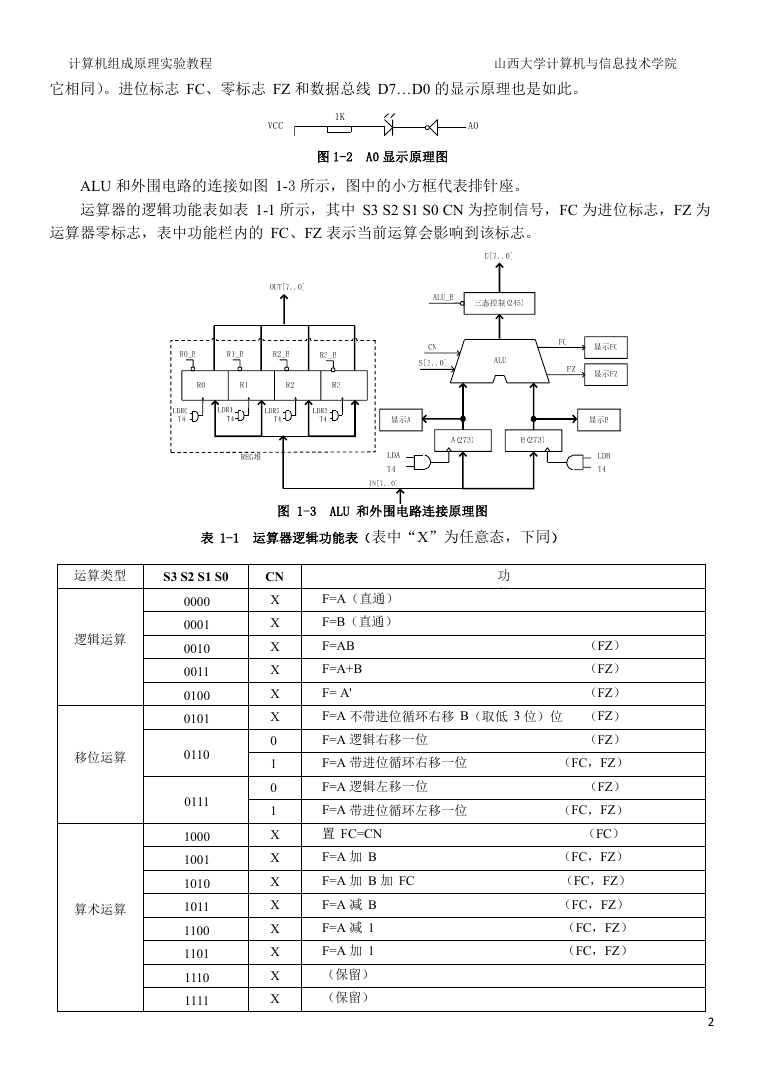

运算器的逻辑功能表如表 1-1 所示,其中 S3 S2 S1 S0 CN 为控制信号,FC 为进位标志,FZ 为

运算器零标志,表中功能栏内的 FC、FZ 表示当前运算会影响到该标志。

图 1-3

ALU 和外围电路连接原理图

表 1-1 运算器逻辑功能表(表中“X”为任意态,下同)

运算类型

S3 S2 S1 S0

逻辑运算

移位运算

算术运算

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

CN

X

X

X

X

X

X

0

1

0

1

X

X

X

X

X

X

X

X

功

能

F=A(直通)

F=B(直通)

F=AB

(FZ)

F=A+B

(FZ)

F= A'

(FZ)

F=A 不带进位循环右移 B(取低 3 位)位 (FZ)

F=A 逻辑右移一位

(FZ)

(FC,FZ)

F=A 带进位循环右移一位

F=A 逻辑左移一位

(FZ)

(FC,FZ)

F=A 带进位循环左移一位

置 FC=CN

(FC)

(FC,FZ)

F=A 加 B

(FC,FZ)

F=A 加 B 加 FC

F=A 减 B

(FC,FZ)

(FC,FZ)

F=A 减 1

F=A 加 1

(FC,FZ)

(保留)

(保留)

2

�

计算机组成原理实验教程

山西大学计算机与信息技术学院

1.4 实验步骤

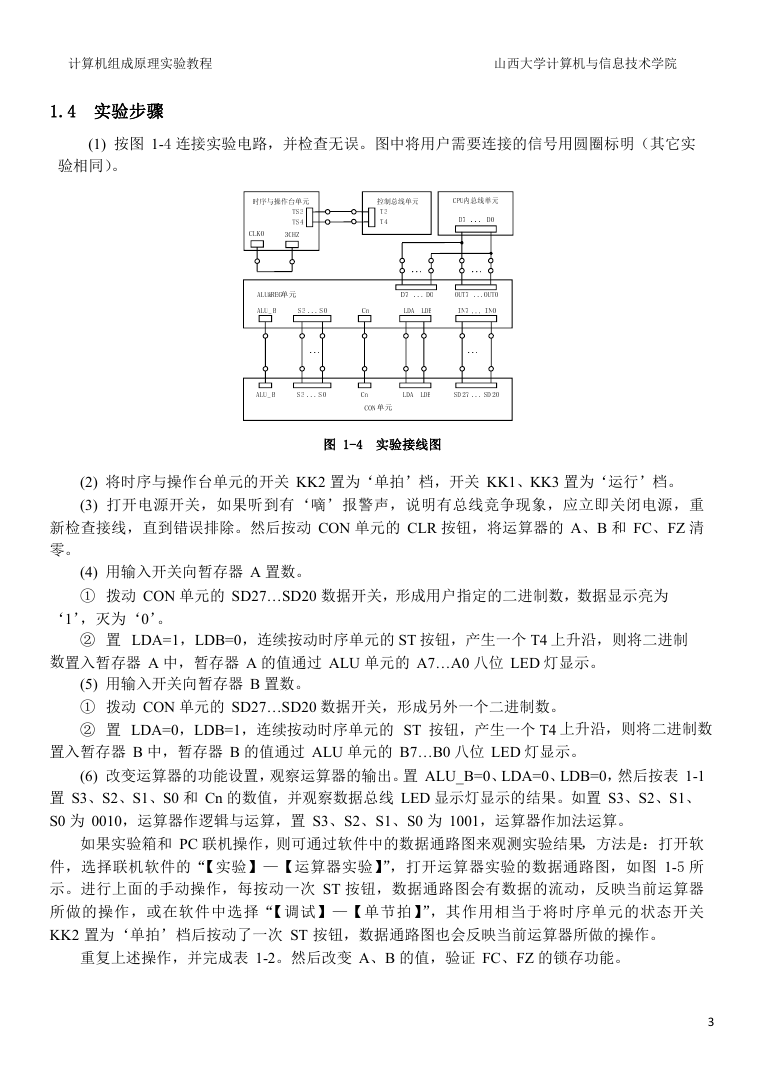

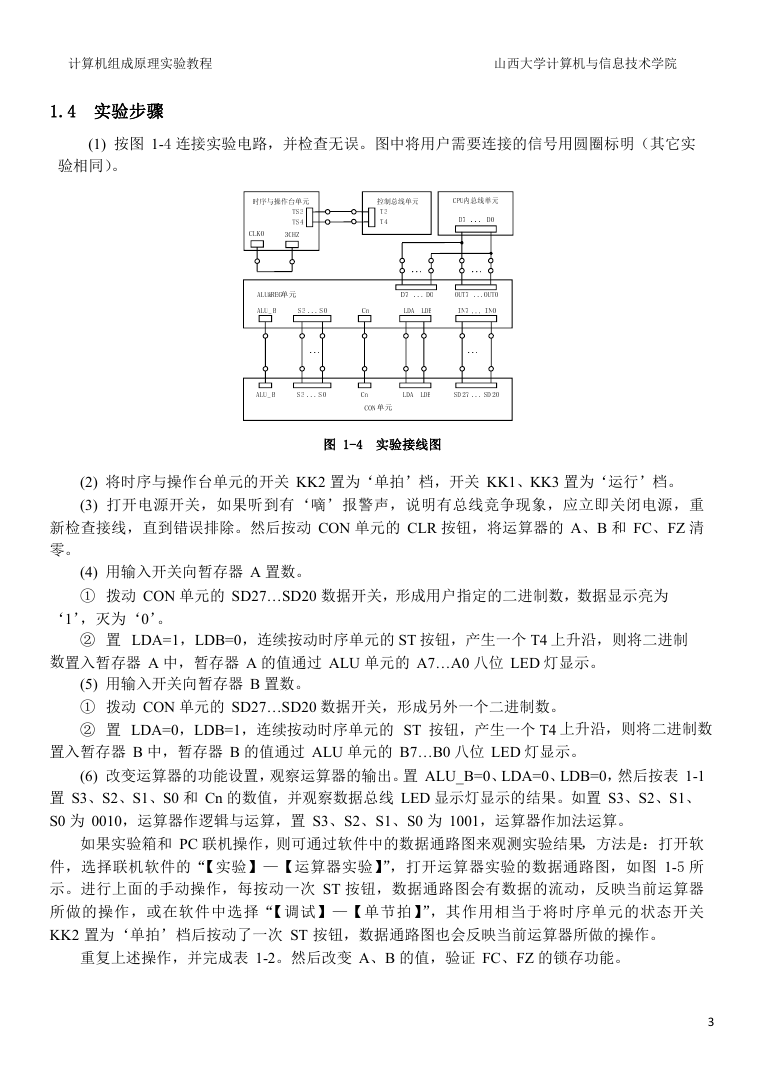

(1) 按图 1-4 连接实验电路,并检查无误。图中将用户需要连接的信号用圆圈标明(其它实

验相同)。

图 1-4 实验接线图

(2) 将时序与操作台单元的开关 KK2 置为‘单拍’档,开关 KK1、KK3 置为‘运行’档。

(3) 打开电源开关,如果听到有‘嘀’报警声,说明有总线竞争现象,应立即关闭电源,重

新检查接线,直到错误排除。然后按动 CON 单元的 CLR 按钮,将运算器的 A、B 和 FC、FZ 清

零。

(4) 用输入开关向暂存器 A 置数。

① 拨动 CON 单元的 SD27…SD20 数据开关,形成用户指定的二进制数,数据显示亮为

‘1’,灭为‘0’。

② 置 LDA=1,LDB=0,连续按动时序单元的 ST 按钮,产生一个 T4 上升沿,则将二进制

数置入暂存器 A 中,暂存器 A 的值通过 ALU 单元的 A7…A0 八位 LED 灯显示。

(5) 用输入开关向暂存器 B 置数。

① 拨动 CON 单元的 SD27…SD20 数据开关,形成另外一个二进制数。

② 置 LDA=0,LDB=1,连续按动时序单元的 ST 按钮,产生一个 T4 上升沿,则将二进制数

置入暂存器 B 中,暂存器 B 的值通过 ALU 单元的 B7…B0 八位 LED 灯显示。

(6) 改变运算器的功能设置,观察运算器的输出。置 ALU_B=0、LDA=0、LDB=0,然后按表 1-1

置 S3、S2、S1、S0 和 Cn 的数值,并观察数据总线 LED 显示灯显示的结果。如置 S3、S2、S1、

S0 为 0010,运算器作逻辑与运算,置 S3、S2、S1、S0 为 1001,运算器作加法运算。

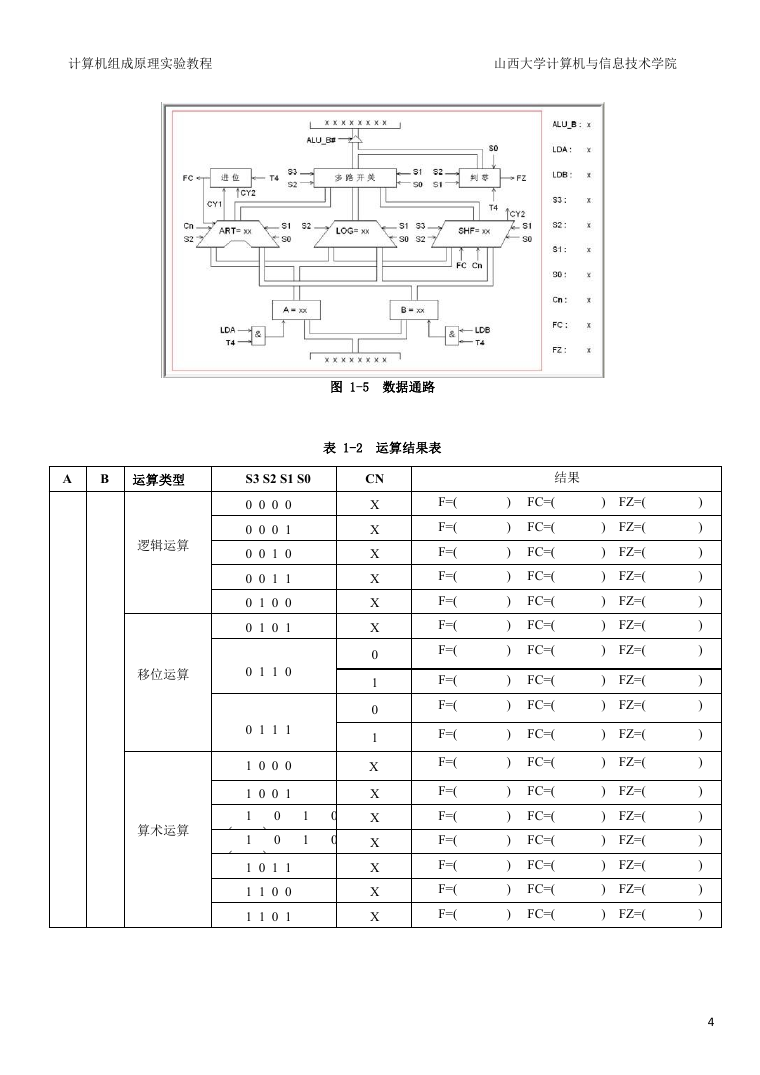

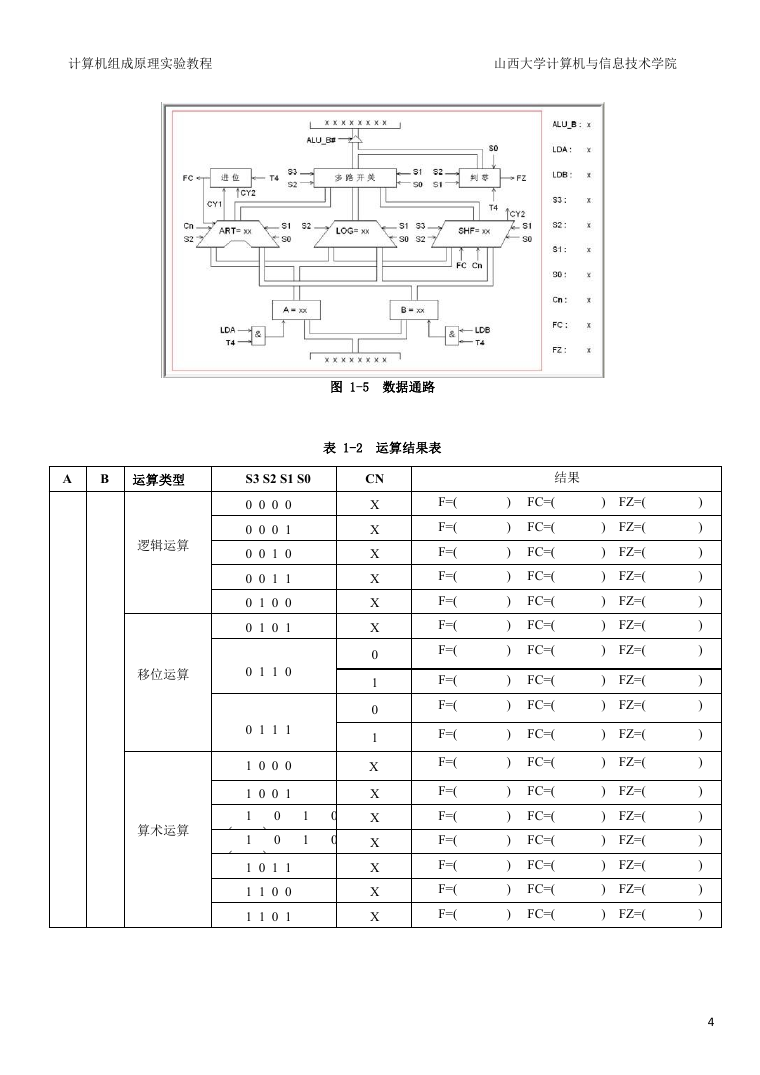

如果实验箱和 PC 联机操作,则可通过软件中的数据通路图来观测实验结果,方法是:打开软

件,选择联机软件的“【实验】—【运算器实验】”,打开运算器实验的数据通路图,如图 1-5 所

示。进行上面的手动操作,每按动一次 ST 按钮,数据通路图会有数据的流动,反映当前运算器

所做的操作,或在软件中选择“【调试】—【单节拍】”,其作用相当于将时序单元的状态开关

KK2 置为‘单拍’档后按动了一次 ST 按钮,数据通路图也会反映当前运算器所做的操作。

重复上述操作,并完成表 1-2。然后改变 A、B 的值,验证 FC、FZ 的锁存功能。

3

�

计算机组成原理实验教程

山西大学计算机与信息技术学院

图 1-5 数据通路

表 1-2 运算结果表

A

B 运算类型

逻辑运算

S3 S2 S1 S0

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

移位运算

0 1 1 0

0 1 1 1

1 0 0 0

算术运算

1

1

0

0

1 0 0 1

1

1

0

(FC=0)

0

(FC=1)

1 0 1 1

1 1 0 0

1 1 0 1

CN

X

X

X

X

X

X

0

1

0

1

X

X

X

X

X

X

X

F=(

F=(

F=(

F=(

F=(

F=(

F=(

F=(

F=(

F=(

F=(

F=(

F=(

F=(

F=(

F=(

F=(

结果

)

)

)

)

)

)

)

)

)

)

)

)

)

)

)

)

)

FC=(

FC=(

FC=(

FC=(

FC=(

FC=(

FC=(

FC=(

FC=(

FC=(

FC=(

FC=(

FC=(

FC=(

FC=(

FC=(

FC=(

) FZ=(

) FZ=(

) FZ=(

) FZ=(

) FZ=(

) FZ=(

) FZ=(

) FZ=(

) FZ=(

) FZ=(

) FZ=(

) FZ=(

) FZ=(

) FZ=(

) FZ=(

) FZ=(

) FZ=(

)

)

)

)

)

)

)

)

)

)

)

)

)

)

)

)

)

4

�

计算机组成原理实验教程

山西大学计算机与信息技术学院

实验二 静态随机存储器实验

2.1 实验目的

掌握静态随机存储器 RAM 工作特性及数据的读写方法。

2.2 实验设备

PC 机一台,TD-CMA 实验系统一套。

2.3 实验原理

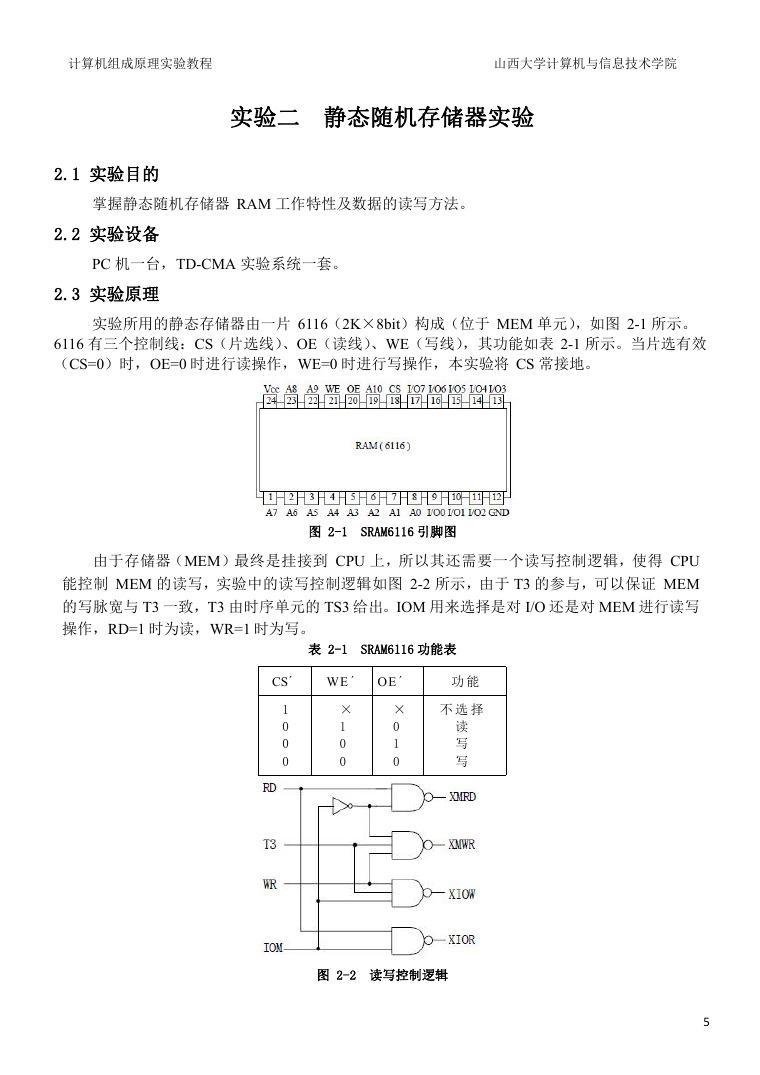

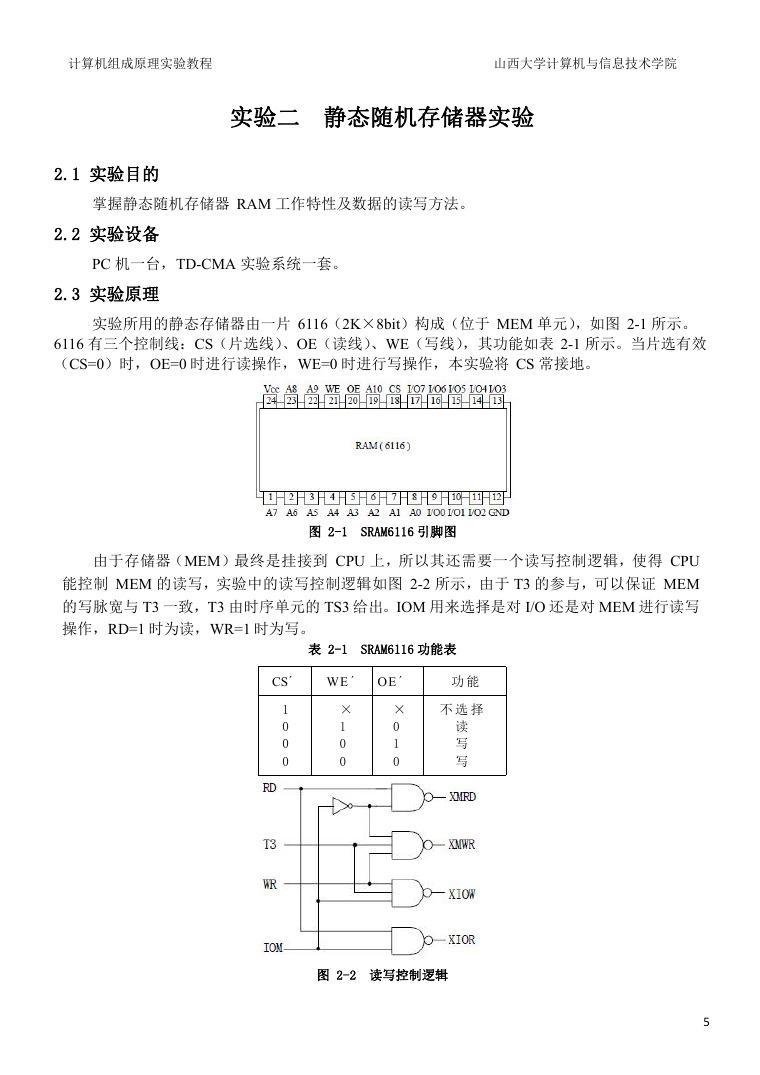

实验所用的静态存储器由一片 6116(2K×8bit)构成(位于 MEM 单元),如图 2-1 所示。

6116 有三个控制线:CS(片选线)、OE(读线)、WE(写线),其功能如表 2-1 所示。当片选有效

(CS=0)时,OE=0 时进行读操作,WE=0 时进行写操作,本实验将 CS 常接地。

图 2-1 SRAM6116 引脚图

由于存储器(MEM)最终是挂接到 CPU 上,所以其还需要一个读写控制逻辑,使得 CPU

能控制 MEM 的读写,实验中的读写控制逻辑如图 2-2 所示,由于 T3 的参与,可以保证 MEM

的写脉宽与 T3 一致,T3 由时序单元的 TS3 给出。IOM 用来选择是对 I/O 还是对 MEM 进行读写

操作,RD=1 时为读,WR=1 时为写。

表 2-1 SRAM6116 功能表

CS´

WE ´

OE ´

1

0

0

0

×

1

0

0

×

0

1

0

功 能

不 选 择

读

写

写

图 2-2 读写控制逻辑

5

�

计算机组成原理实验教程

山西大学计算机与信息技术学院

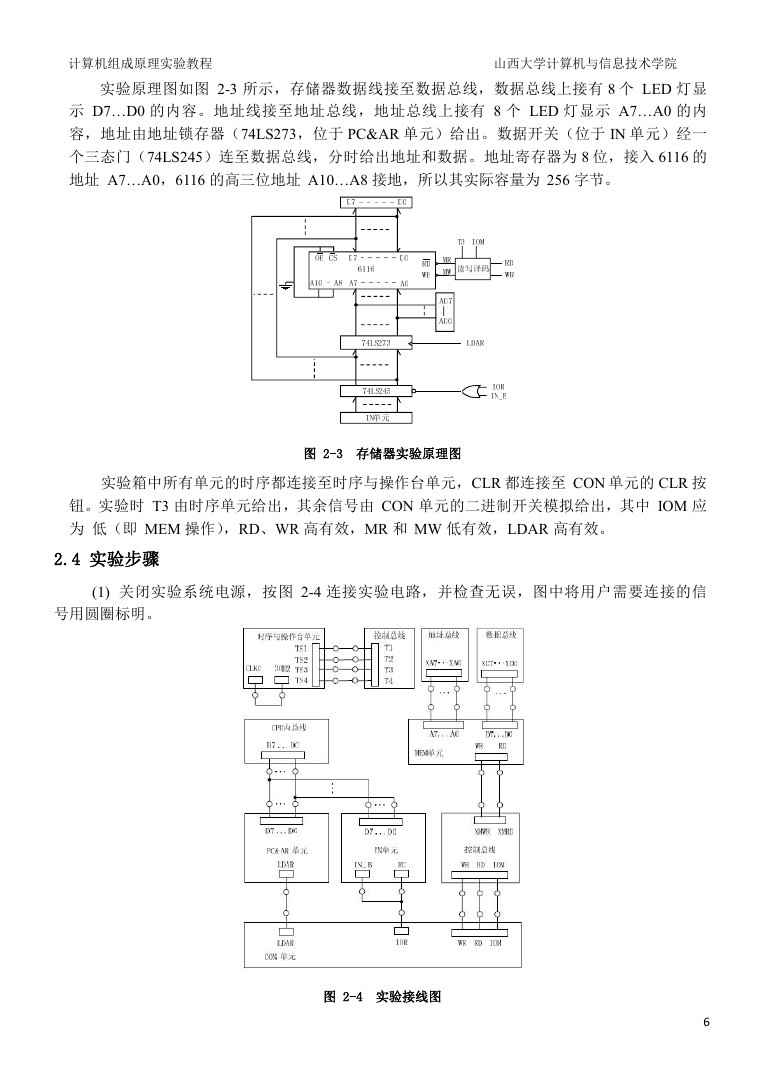

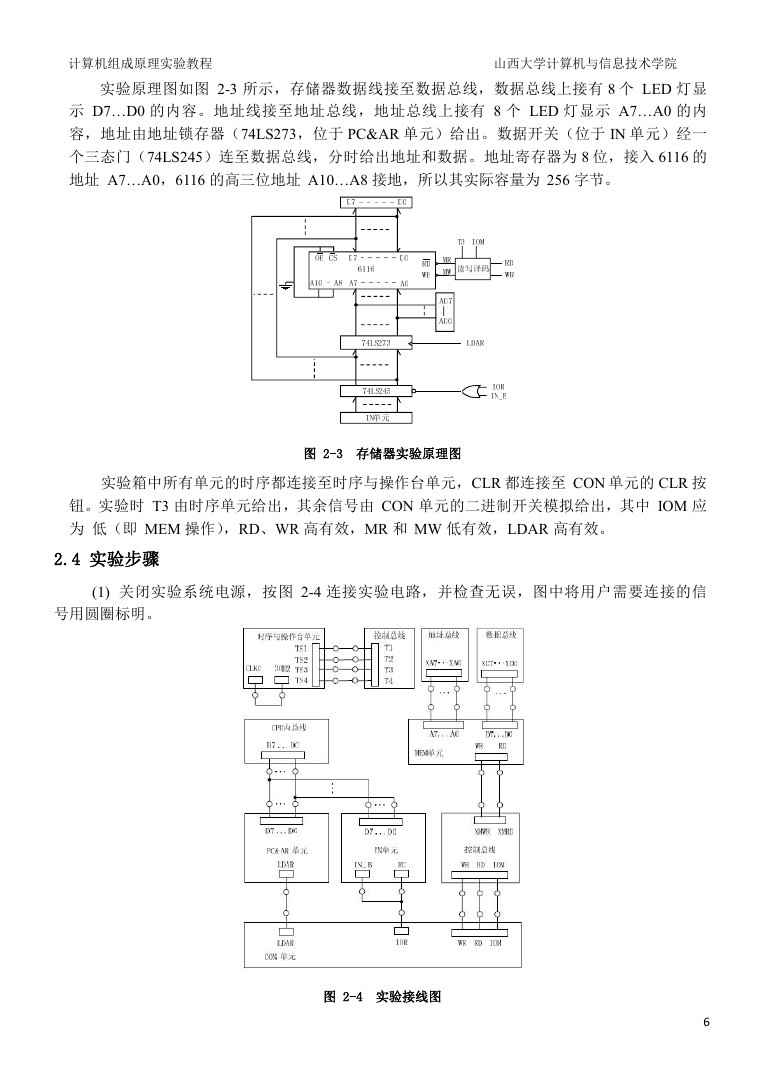

实验原理图如图 2-3 所示,存储器数据线接至数据总线,数据总线上接有 8 个 LED 灯显

示 D7…D0 的内容。地址线接至地址总线,地址总线上接有 8 个 LED 灯显示 A7…A0 的内

容,地址由地址锁存器(74LS273,位于 PC&AR 单元)给出。数据开关(位于 IN 单元)经一

个三态门(74LS245)连至数据总线,分时给出地址和数据。地址寄存器为 8 位,接入 6116 的

地址 A7…A0,6116 的高三位地址 A10…A8 接地,所以其实际容量为 256 字节。

图 2-3 存储器实验原理图

实验箱中所有单元的时序都连接至时序与操作台单元,CLR 都连接至 CON 单元的 CLR 按

钮。实验时 T3 由时序单元给出,其余信号由 CON 单元的二进制开关模拟给出,其中 IOM 应

为 低(即 MEM 操作),RD、WR 高有效,MR 和 MW 低有效,LDAR 高有效。

2.4 实验步骤

(1) 关闭实验系统电源,按图 2-4 连接实验电路,并检查无误,图中将用户需要连接的信

号用圆圈标明。

图 2-4 实验接线图

6

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc