�

DATA CONVERTERS

Data Converters

by

FRANCO MALOBERTI

Pavia University, Italy

�

A C.I.P. Catalogue record for this book is available from the Library of Congress.

ISBN-10 0-387-32485-2 (HB)

ISBN-13 978-0-387-32485-2(HB)

ISBN-10 0-387-32486-0 (e-book)

ISBN-13 978-0-387-32486-9 (e-book)

Published by Springer,

P.O. Box 17, 3300 AA Dordrecht, The Netherlands.

www.springer.com

Printed on acid-free paper

All Rights Reserved

© 2007 Springer

No part of this work may be reproduced, stored in a retrieval system, or transmitted

in any form or by any means, electronic, mechanical, photocopying, microfilming, recording

or otherwise, without written permission from the Publisher, with the exception

of any material supplied specifically for the purpose of being entered

and executed on a computer system, for exclusive use by the purchaser of the work.

�

To Pina, Am´elie, and Matteo

�

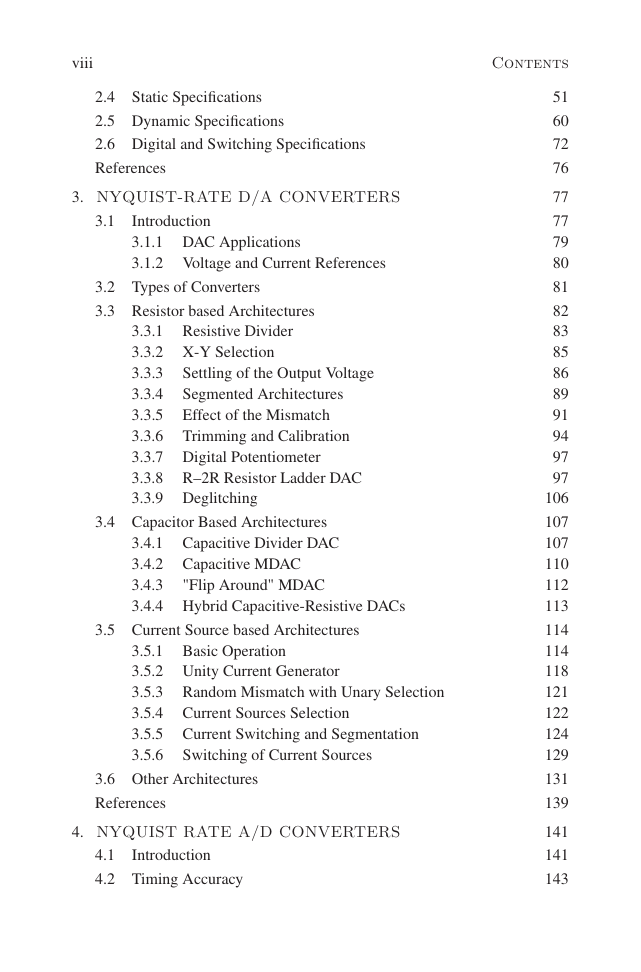

Contents

Dedication

Preface

1. BACKGROUND ELEMENTS

1.1 The Ideal Data Converter

1.2 Sampling

1.2.1 Undersampling

1.2.2

Sampling-time Jitter

1.3 Amplitude Quantization

1.3.1 Quantization Noise

1.3.2

kT/C Noise

1.4

1.5 Discrete and Fast Fourier Transforms

Properties of the Quantization Noise

1.5.1 Windowing

1.6 Coding Schemes

1.7 The D/A Converter

1.7.1

Ideal Reconstruction

1.7.2 Real Reconstruction

The Z-Transform

1.8

References

2. DATA CONVERTERS SPECIFICATIONS

2.1 Type of Converter

2.2 Conditions of Operation

2.3 Converter Specifications

2.3.1 General Features

vii

v

xiii

1

1

2

10

12

15

17

18

22

25

26

32

33

34

34

38

46

47

47

48

50

50

�

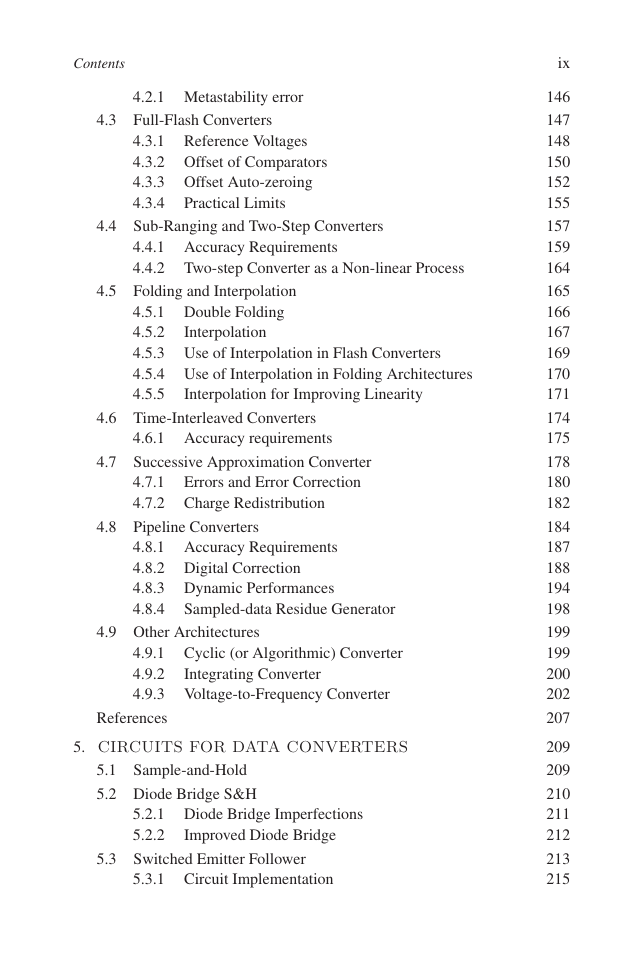

viii

Contents

2.4 Static Specifications

2.5 Dynamic Specifications

2.6 Digital and Switching Specifications

References

3. NYQUIST-RATE D/A CONVERTERS

3.1

Introduction

3.1.1 DAC Applications

3.1.2 Voltage and Current References

3.2 Types of Converters

3.3 Resistor based Architectures

Settling of the Output Voltage

Segmented Architectures

3.3.1 Resistive Divider

3.3.2 X-Y Selection

3.3.3

3.3.4

3.3.5 Effect of the Mismatch

3.3.6 Trimming and Calibration

3.3.7 Digital Potentiometer

3.3.8 R–2R Resistor Ladder DAC

3.3.9 Deglitching

3.4 Capacitor Based Architectures

3.4.1 Capacitive Divider DAC

3.4.2 Capacitive MDAC

3.4.3

3.4.4 Hybrid Capacitive-Resistive DACs

"Flip Around" MDAC

3.5 Current Source based Architectures

3.5.1 Basic Operation

3.5.2 Unity Current Generator

3.5.3 Random Mismatch with Unary Selection

3.5.4 Current Sources Selection

3.5.5 Current Switching and Segmentation

3.5.6

Switching of Current Sources

3.6 Other Architectures

References

4. NYQUIST RATE A/D CONVERTERS

Introduction

4.1

4.2 Timing Accuracy

51

60

72

76

77

77

79

80

81

82

83

85

86

89

91

94

97

97

106

107

107

110

112

113

114

114

118

121

122

124

129

131

139

141

141

143

�

Contents

4.2.1 Metastability error

4.3 Full-Flash Converters

4.3.1 Reference Voltages

4.3.2 Offset of Comparators

4.3.3 Offset Auto-zeroing

4.3.4

Practical Limits

4.4 Sub-Ranging and Two-Step Converters

4.4.1 Accuracy Requirements

4.4.2 Two-step Converter as a Non-linear Process

4.5 Folding and Interpolation

Interpolation

4.5.1 Double Folding

4.5.2

4.5.3 Use of Interpolation in Flash Converters

4.5.4 Use of Interpolation in Folding Architectures

4.5.5

Interpolation for Improving Linearity

4.6 Time-Interleaved Converters

4.6.1 Accuracy requirements

4.7 Successive Approximation Converter

4.7.1 Errors and Error Correction

4.7.2 Charge Redistribution

4.8 Pipeline Converters

4.8.1 Accuracy Requirements

4.8.2 Digital Correction

4.8.3 Dynamic Performances

4.8.4

Sampled-data Residue Generator

4.9 Other Architectures

4.9.1 Cyclic (or Algorithmic) Converter

4.9.2

4.9.3 Voltage-to-Frequency Converter

Integrating Converter

References

5. CIRCUITS FOR DATA CONVERTERS

5.1 Sample-and-Hold

5.2 Diode Bridge S&H

5.2.1 Diode Bridge Imperfections

5.2.2

Improved Diode Bridge

5.3 Switched Emitter Follower

5.3.1 Circuit Implementation

ix

146

147

148

150

152

155

157

159

164

165

166

167

169

170

171

174

175

178

180

182

184

187

188

194

198

199

199

200

202

207

209

209

210

211

212

213

215

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc