A Microchip Technology Company

16 Mb SPI 串行闪存

SST25VF016B

数据手册

SST 的25 系列串行闪存采用四线、兼容SPI 的接口,从而实现占用较少电路板空

间的低引脚数封装,并最终降低总系统成本。SST25VF016B 器件是增强型器件,

提高了工作频率并降低了功耗。SST25VF016B SPI 串行闪存采用SST 专有的高性

能CMOS SuperFlash® 技术制造。与其他方法相比,分离栅极单元设计(split-gate

cell design)和厚氧化层隧穿注入器(thick-oxide tunneling injector)可实现更高

的可靠性和可制造性。

特性

• 单电压读写操作

– 2.7-3.6V

• 串行接口架构

– 兼容 SPI:模式 0 和模式 3

• 高速时钟频率

– 高达 80 MHz

• 超高可靠性

– 可擦写次数:100,000 次 (典型值)

– 数据保存时间大于 100 年

• 低功耗:

– 读操作工作电流:10 mA (典型值)

– 待机电流:5 µA (典型值)

• 灵活的擦除功能

– 均一 4 KB 扇区

– 均一 32 KB 覆盖块

– 均一 64 KB 覆盖块

• 快速擦除和字节编程:

– 全片擦除时间:35 ms (典型值)

– 扇区 / 块擦除时间:18 ms (典型值)

– 字节编程时间:7 µs (典型值)

• 自动地址递增 (Auto Address Increment, AAI)

编程

– 减少字节编程操作期间的总芯片编程时间

• 写操作结束检测

– 软件轮询状态寄存器中的 BUSY 位

– AAI 模式下 SO 引脚上的忙状态读出

• 保持引脚 (HOLD#)

– 在不取消选择器件的情况下暂停存储器的串行序列

• 写保护 (WP#)

– 使能 / 禁止状态寄存器的锁定功能

• 软件写保护

– 通过状态寄存器中的块保护位实现写保护

• 温度范围

– 商业级:0°C 至 +70°C

– 工业级:-40°C 至 +85°C

• 可用封装

– 8 引脚 SOIC (200 mil)

– 8 触点 WSON (6 mm x 5 mm)

• 所有器件均符合 RoHS 标准

© 2011 Silicon Storage Technology, Inc.

www.microchip.com

DS25044A_CN

11/11

�

A Microchip Technology Company

产品描述

16 Mb SPI 串行闪存

SST25VF016B

数据手册

SST 的 25 系列串行闪存采用四线、兼容 SPI 的接口,从而实现占用较少电路板空间的低引脚数封装,

并最终降低总系统成本。 SST25VF016B 器件是增强型器件,与原有的 SST25VFxxxA 器件相比,提高

了工作频率并降低了功耗。 SST25VF016B SPI 串行闪存采用 SST 专有的高性能 CMOS SuperFlash®

技术制造。与其他方法相比,分离栅极单元设计 (split-gate cell design)和厚氧化层隧穿注入器 (thick-

oxide tunneling injector)可实现更高的可靠性和可制造性。

SST25VF016B 器件可以显著提高性能和可靠性,同时降低功耗。对于 SST25VF016B,器件使用 2.7-3.6V

单电源进行写操作 (编程或擦除)。消耗的总能量是应用中施加电压、电流和时间的函数。对于任何给

定的电压范围, SuperFlash® 技术的编程电流更低、擦除时间更短;因此,在任何擦除或编程操作期间

消耗的总能量低于其他闪存技术。

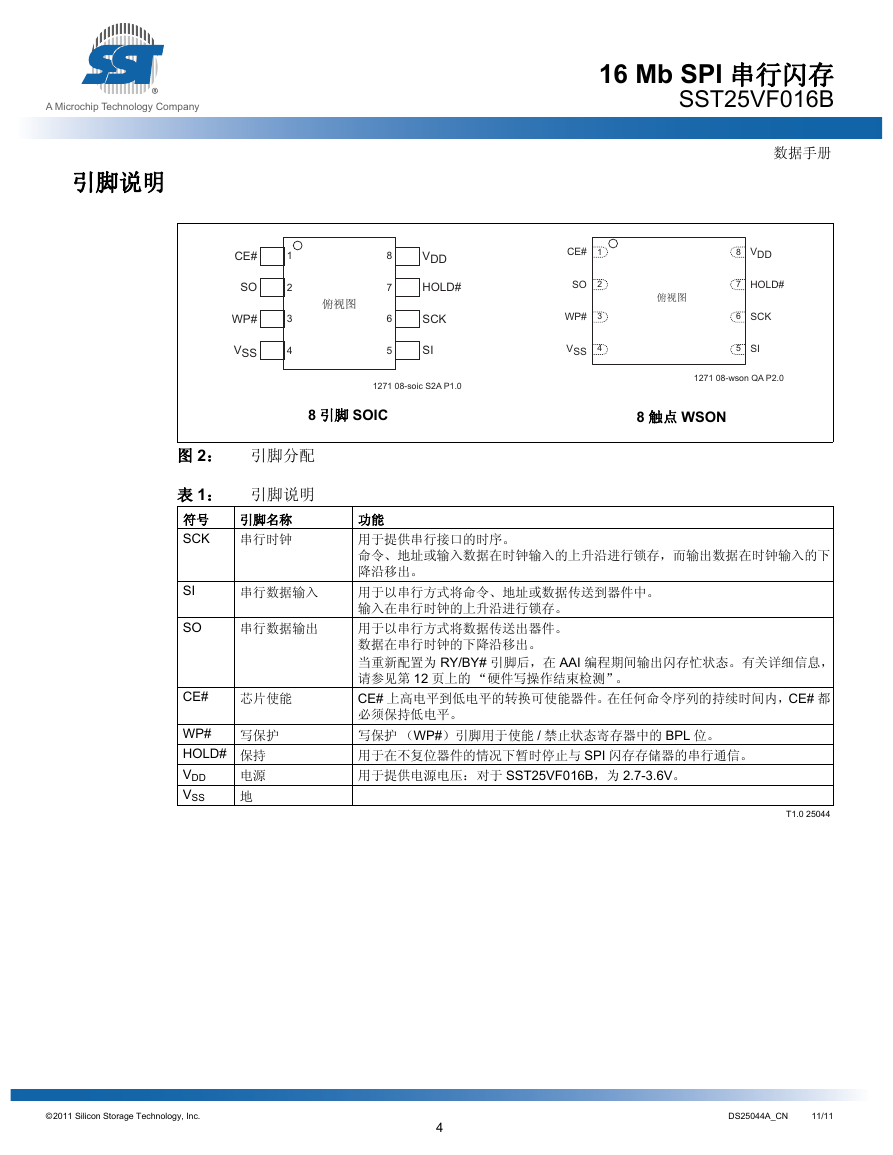

SST25VF016B 器件提供 8 引脚 SOIC (200 mil)和 8 触点 WSON (6 mm x 5 mm)封装。有关引脚

分配,请参见图 2。

© 2011 Silicon Storage Technology, Inc.

2

DS25044A_CN

11/11

�

A Microchip Technology Company

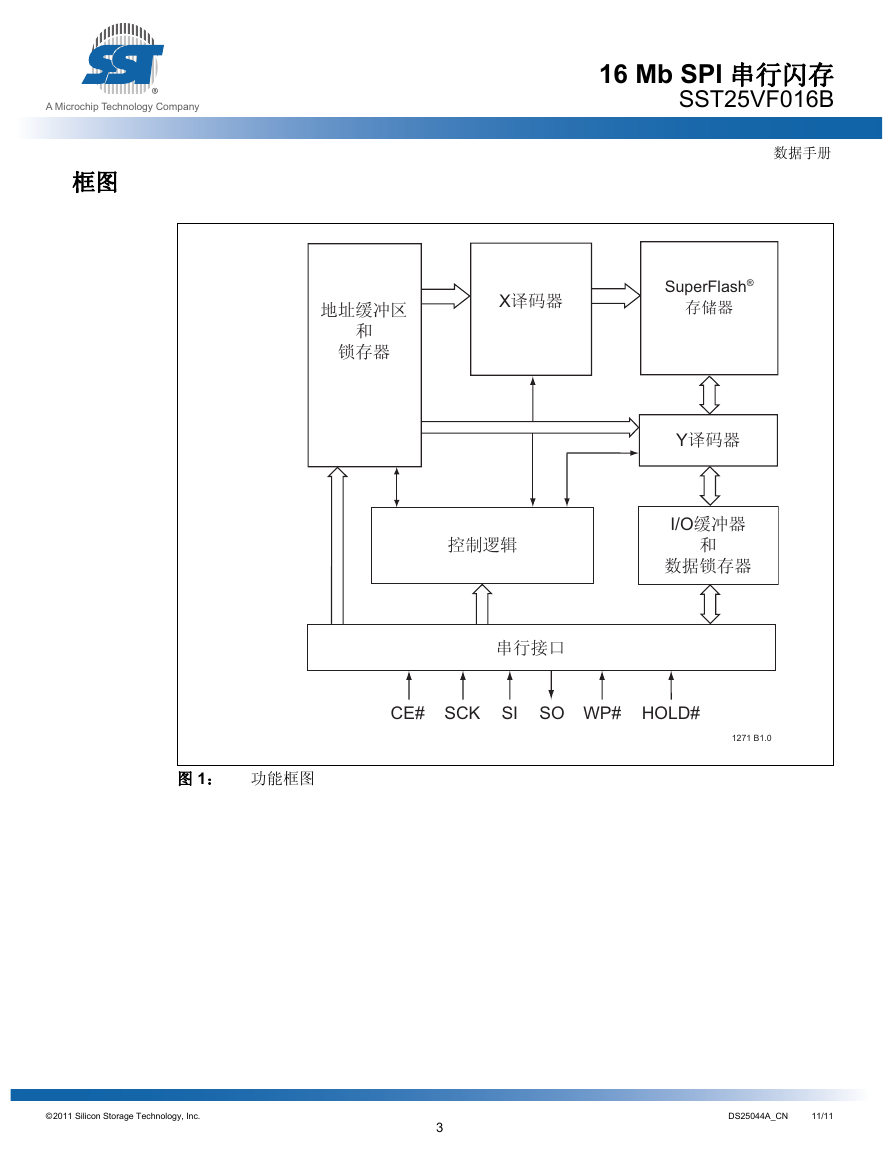

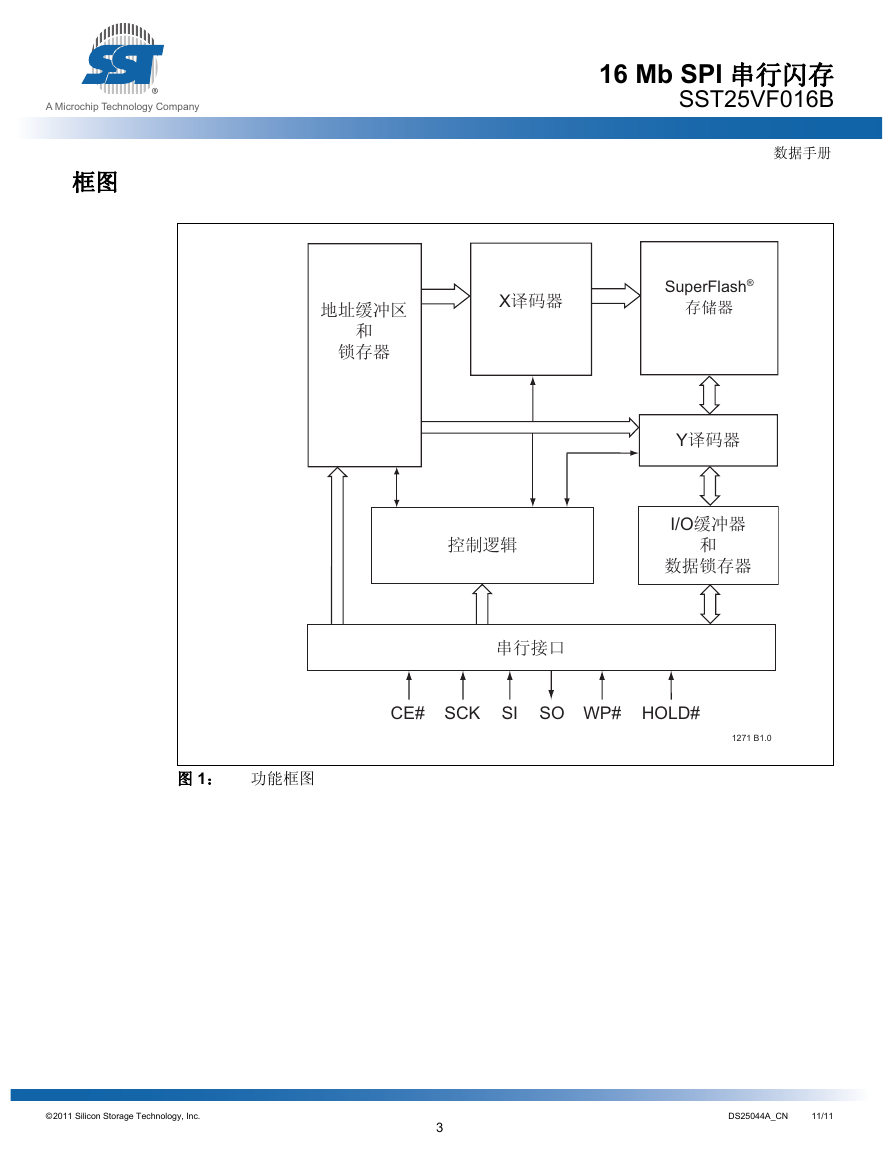

框图

16 Mb SPI 串行闪存

SST25VF016B

数据手册

X

SuperFlash®

Y

I/O

CE#

SCK SI SO WP# HOLD#

1271 B1.0

图 1: 功能框图

© 2011 Silicon Storage Technology, Inc.

3

DS25044A_CN

11/11

�

A Microchip Technology Company

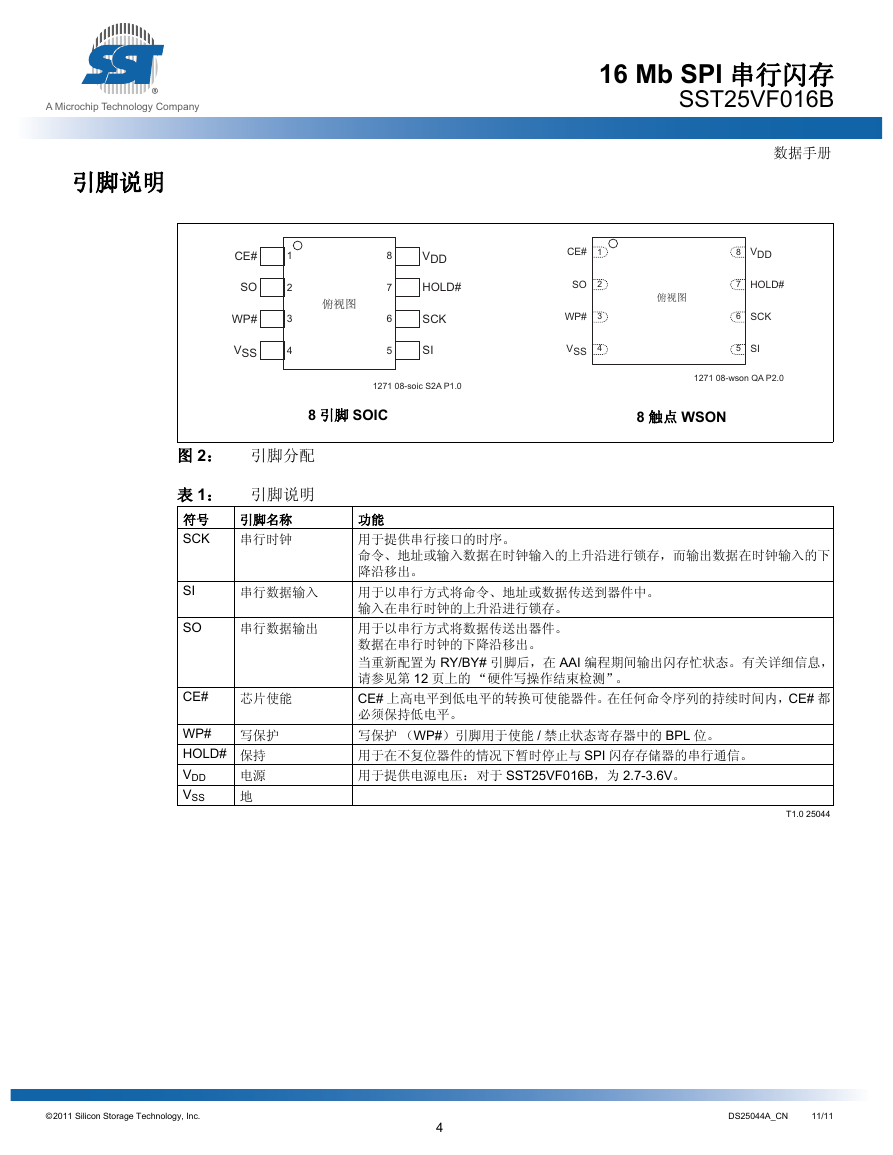

引脚说明

16 Mb SPI 串行闪存

SST25VF016B

数据手册

CE#

SO

WP#

VSS

1

2

3

4

8

7

6

5

VDD

HOLD#

SCK

SI

1271 08-soic S2A P1.0

8 引脚 SOIC

图 2: 引脚分配

CE#

SO

WP#

VSS

1

2

3

4

8

7

6

5

VDD

HOLD#

SCK

SI

1271 08-wson QA P2.0

8 触点 WSON

表 1: 引脚说明

符号

SCK

引脚名称

串行时钟

SI

SO

串行数据输入

串行数据输出

CE#

芯片使能

写保护

WP#

HOLD# 保持

VDD

电源

VSS

地

功能

用于提供串行接口的时序。

命令、地址或输入数据在时钟输入的上升沿进行锁存,而输出数据在时钟输入的下

降沿移出。

用于以串行方式将命令、地址或数据传送到器件中。

输入在串行时钟的上升沿进行锁存。

用于以串行方式将数据传送出器件。

数据在串行时钟的下降沿移出。

当重新配置为 RY/BY# 引脚后,在 AAI 编程期间输出闪存忙状态。有关详细信息,

请参见第 12 页上的 “硬件写操作结束检测”。

CE# 上高电平到低电平的转换可使能器件。在任何命令序列的持续时间内,CE# 都

必须保持低电平。

写保护 (WP#)引脚用于使能 / 禁止状态寄存器中的 BPL 位。

用于在不复位器件的情况下暂时停止与 SPI 闪存存储器的串行通信。

用于提供电源电压:对于 SST25VF016B,为 2.7-3.6V。

T1.0 25044

© 2011 Silicon Storage Technology, Inc.

4

DS25044A_CN

11/11

�

A Microchip Technology Company

存储器构成

16 Mb SPI 串行闪存

SST25VF016B

数据手册

SST25VF016B SuperFlash 存储器阵列由均一 4 KB 可擦除扇区以及 32 KB 覆盖块和 64 KB 覆盖可擦除

块组成。

器件操作

SST25VF016B 通过兼容 SPI (串行外设接口)总线的协议进行访问。 SPI 总线包含四条控制线;芯片

使能 (CE#)用于选择器件,数据通过串行数据输入 (SI)、串行数据输出 (SO)和串行时钟 (SCK)

进行访问。

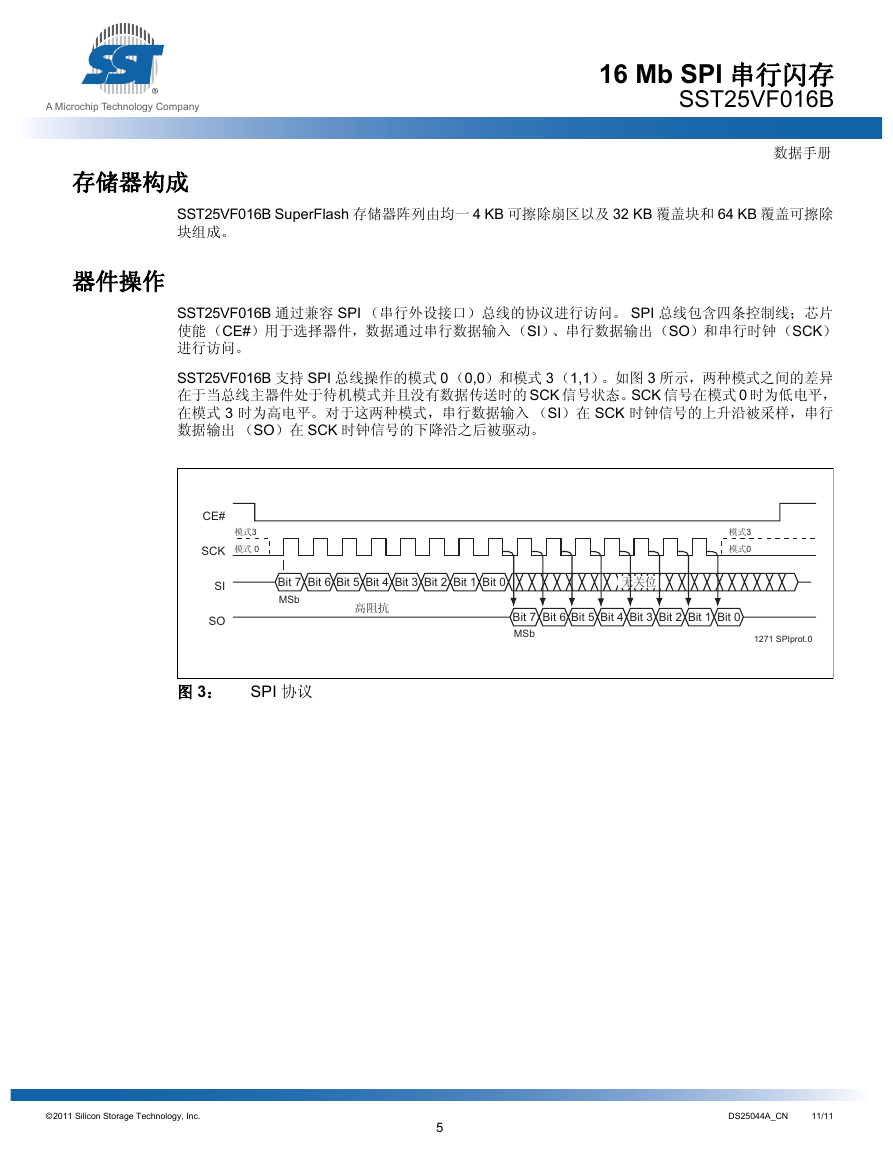

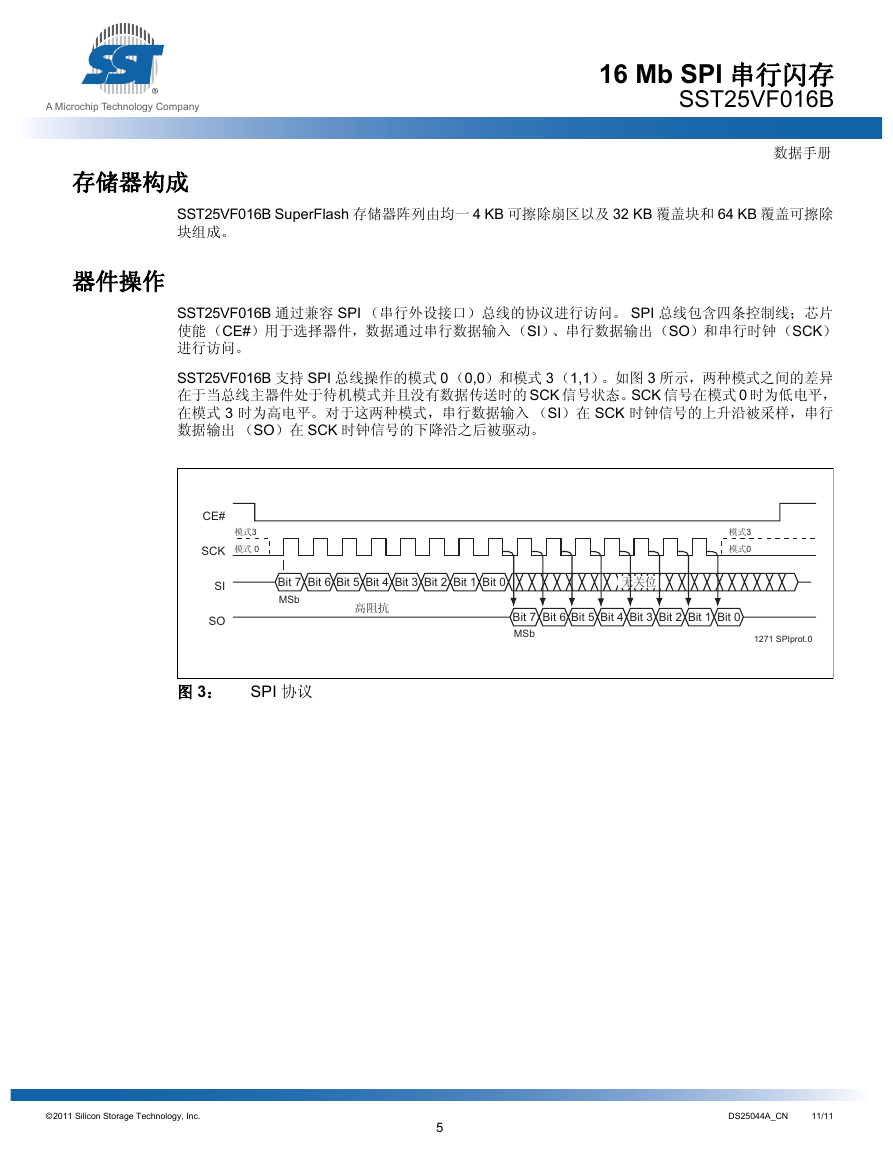

SST25VF016B 支持 SPI 总线操作的模式 0 (0,0)和模式 3 (1,1)。如图 3 所示,两种模式之间的差异

在于当总线主器件处于待机模式并且没有数据传送时的 SCK 信号状态。SCK 信号在模式 0 时为低电平,

在模式 3 时为高电平。对于这两种模式,串行数据输入 (SI)在 SCK 时钟信号的上升沿被采样,串行

数据输出 (SO)在 SCK 时钟信号的下降沿之后被驱动。

3

0

CE#

SCK

SI

SO

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

MSb

3

0

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

MSb

1271 SPIprot.0

图 3: SPI 协议

© 2011 Silicon Storage Technology, Inc.

5

DS25044A_CN

11/11

�

A Microchip Technology Company

保持操作

16 Mb SPI 串行闪存

SST25VF016B

数据手册

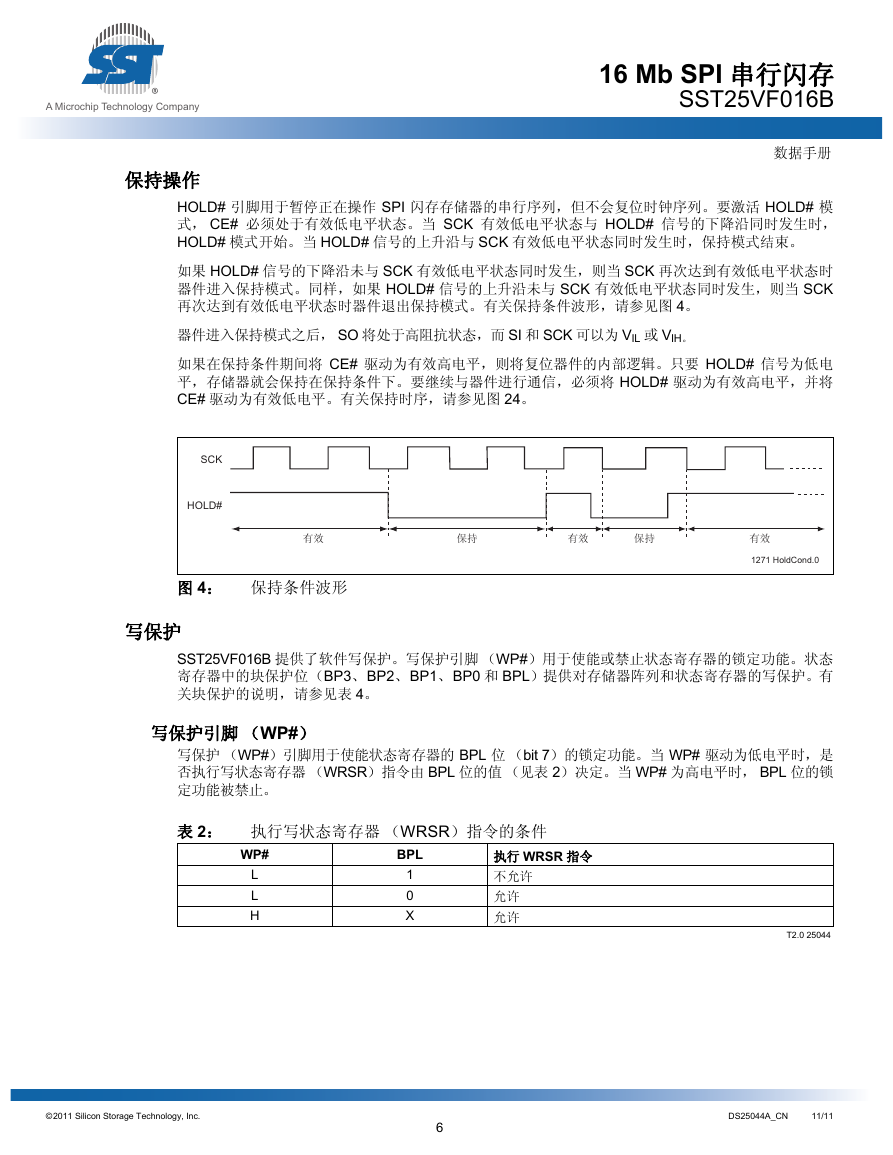

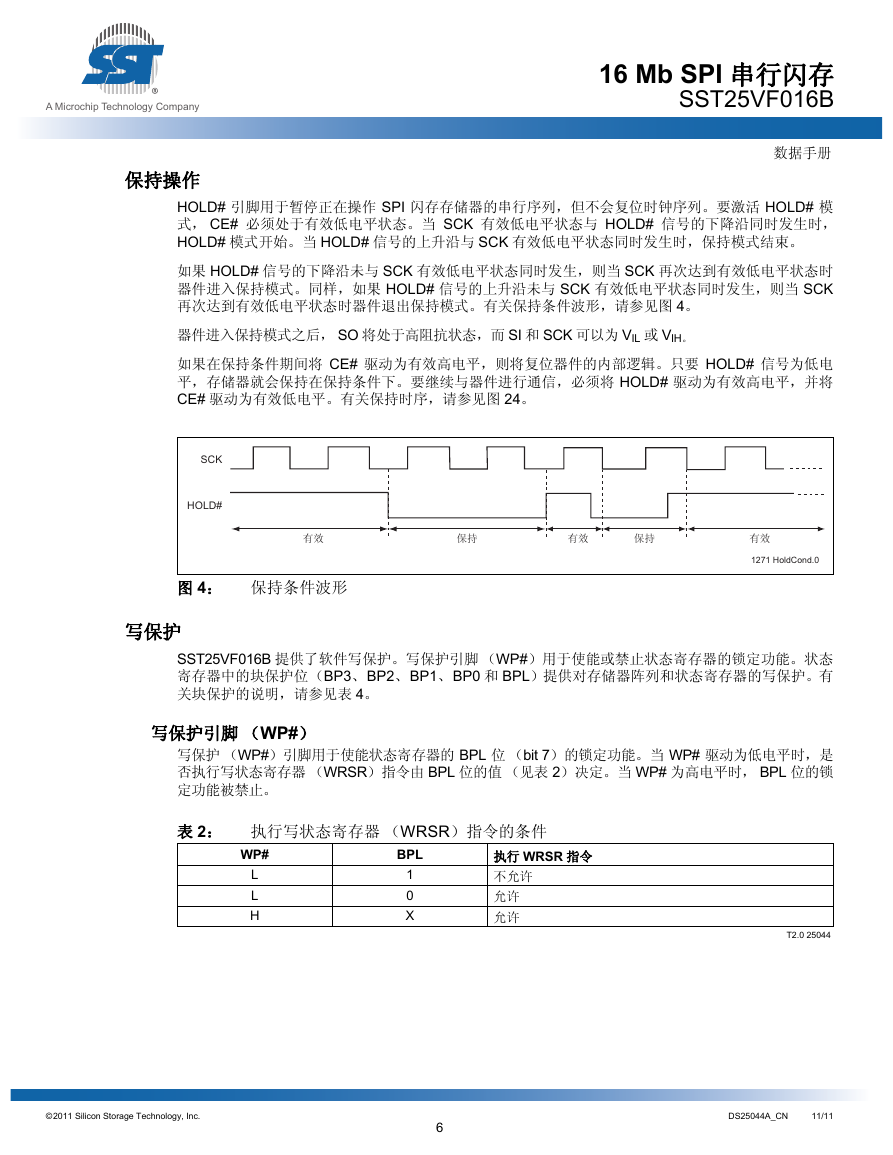

HOLD# 引脚用于暂停正在操作 SPI 闪存存储器的串行序列,但不会复位时钟序列。要激活 HOLD# 模

式, CE# 必须处于有效低电平状态。当 SCK 有效低电平状态与 HOLD# 信号的下降沿同时发生时,

HOLD# 模式开始。当 HOLD# 信号的上升沿与 SCK 有效低电平状态同时发生时,保持模式结束。

如果 HOLD# 信号的下降沿未与 SCK 有效低电平状态同时发生,则当 SCK 再次达到有效低电平状态时

器件进入保持模式。同样,如果 HOLD# 信号的上升沿未与 SCK 有效低电平状态同时发生,则当 SCK

再次达到有效低电平状态时器件退出保持模式。有关保持条件波形,请参见图 4。

器件进入保持模式之后, SO 将处于高阻抗状态,而 SI 和 SCK 可以为 VIL 或 VIH。

如果在保持条件期间将 CE# 驱动为有效高电平,则将复位器件的内部逻辑。只要 HOLD# 信号为低电

平,存储器就会保持在保持条件下。要继续与器件进行通信,必须将 HOLD# 驱动为有效高电平,并将

CE# 驱动为有效低电平。有关保持时序,请参见图 24。

SCK

HOLD#

1271 HoldCond.0

图 4: 保持条件波形

写保护

SST25VF016B 提供了软件写保护。写保护引脚 (WP#)用于使能或禁止状态寄存器的锁定功能。状态

寄存器中的块保护位(BP3、BP2、BP1、BP0 和 BPL)提供对存储器阵列和状态寄存器的写保护。有

关块保护的说明,请参见表 4。

写保护引脚 (WP#)

写保护 (WP#)引脚用于使能状态寄存器的 BPL 位 (bit 7)的锁定功能。当 WP# 驱动为低电平时,是

否执行写状态寄存器 (WRSR)指令由 BPL 位的值 (见表 2)决定。当 WP# 为高电平时, BPL 位的锁

定功能被禁止。

表 2: 执行写状态寄存器 (WRSR)指令的条件

WP#

L

L

H

BPL

1

0

X

执行 WRSR 指令

不允许

允许

允许

T2.0 25044

© 2011 Silicon Storage Technology, Inc.

6

DS25044A_CN

11/11

�

A Microchip Technology Company

状态寄存器

16 Mb SPI 串行闪存

SST25VF016B

数据手册

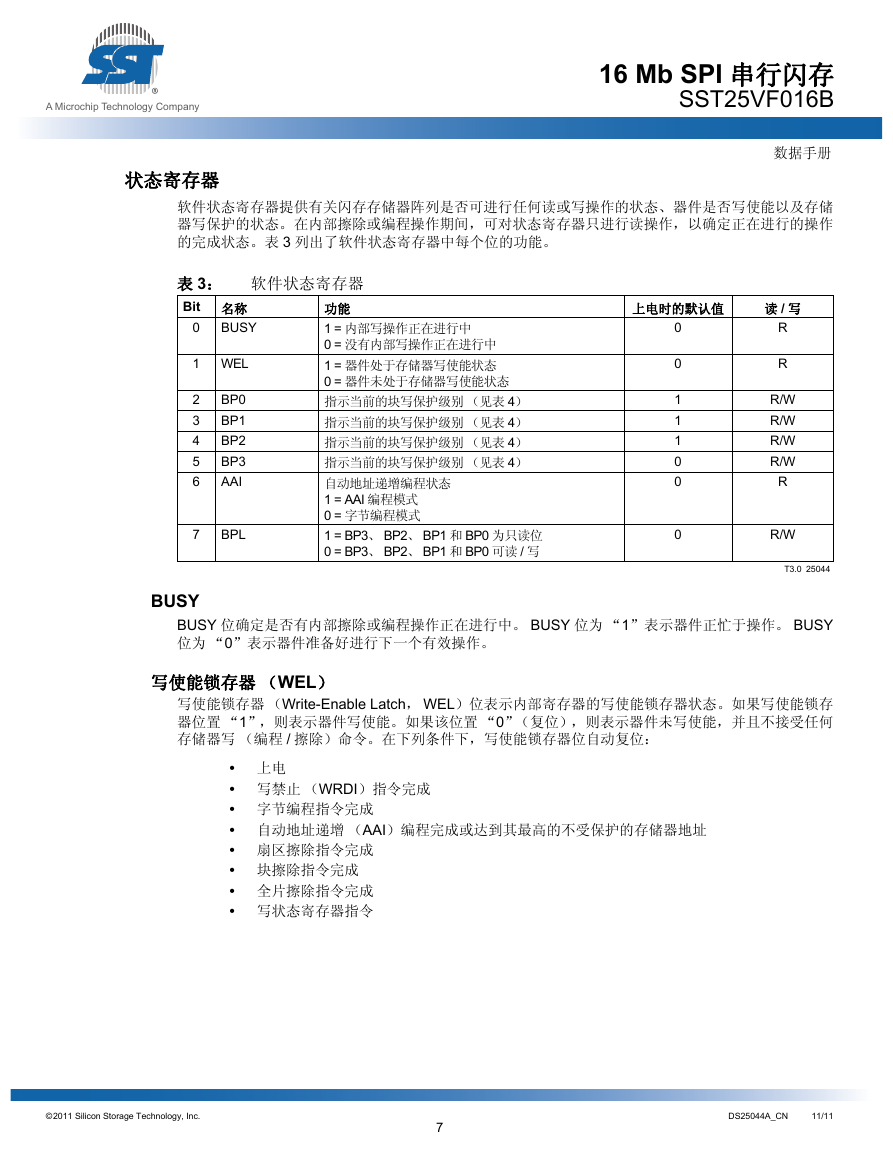

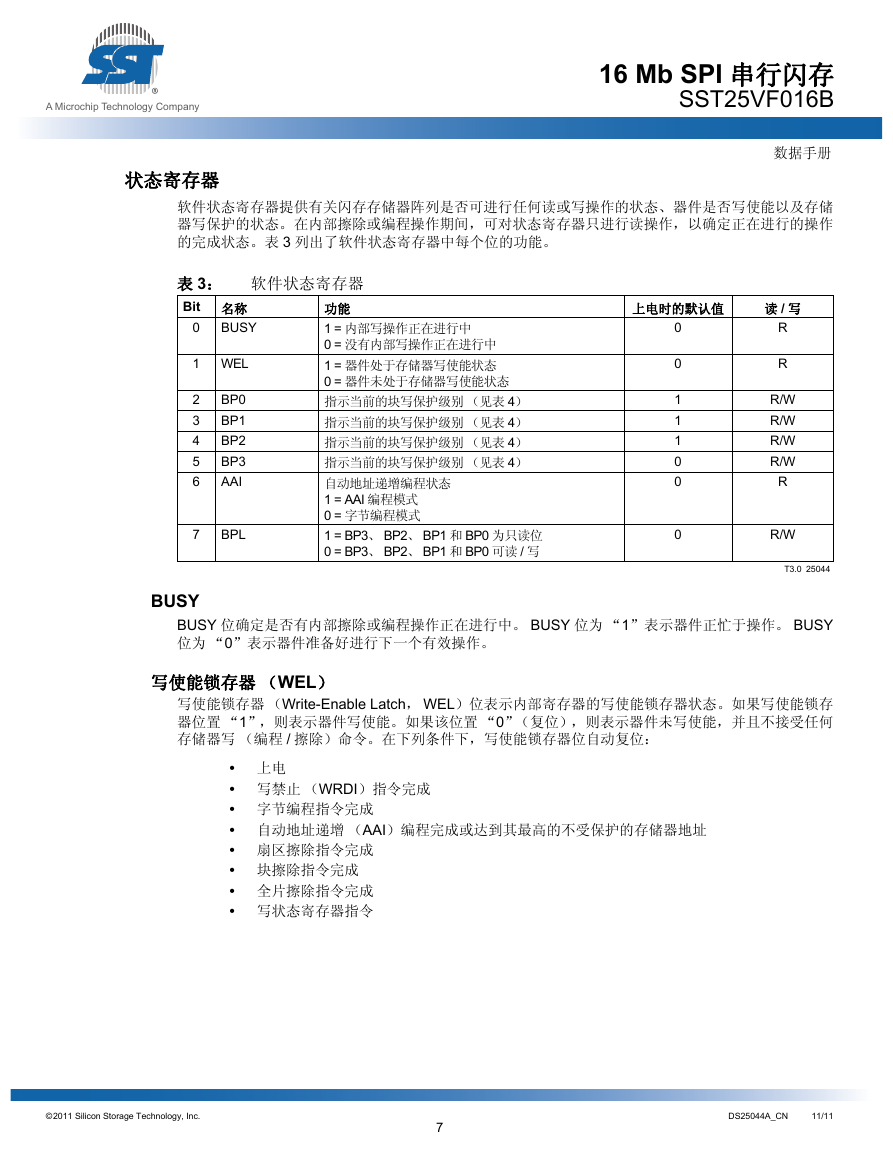

软件状态寄存器提供有关闪存存储器阵列是否可进行任何读或写操作的状态、器件是否写使能以及存储

器写保护的状态。在内部擦除或编程操作期间,可对状态寄存器只进行读操作,以确定正在进行的操作

的完成状态。表 3 列出了软件状态寄存器中每个位的功能。

表 3: 软件状态寄存器

Bit 名称

BUSY

0

1 WEL

2

3

4

5

6

7

BP0

BP1

BP2

BP3

AAI

BPL

BUSY

功能

1 = 内部写操作正在进行中

0 = 没有内部写操作正在进行中

1 = 器件处于存储器写使能状态

0 = 器件未处于存储器写使能状态

指示当前的块写保护级别 (见表 4)

指示当前的块写保护级别 (见表 4)

指示当前的块写保护级别 (见表 4)

指示当前的块写保护级别 (见表 4)

自动地址递增编程状态

1 = AAI 编程模式

0 = 字节编程模式

1 = BP3、 BP2、 BP1 和 BP0 为只读位

0 = BP3、 BP2、 BP1 和 BP0 可读 / 写

上电时的默认值

读 / 写

0

0

1

1

1

0

0

0

R

R

R/W

R/W

R/W

R/W

R

R/W

T3.0 25044

BUSY 位确定是否有内部擦除或编程操作正在进行中。 BUSY 位为 “1”表示器件正忙于操作。 BUSY

位为 “0”表示器件准备好进行下一个有效操作。

写使能锁存器 (WEL)

写使能锁存器 (Write-Enable Latch, WEL)位表示内部寄存器的写使能锁存器状态。如果写使能锁存

器位置 “1”,则表示器件写使能。如果该位置 “0”(复位),则表示器件未写使能,并且不接受任何

存储器写 (编程 / 擦除)命令。在下列条件下,写使能锁存器位自动复位:

• 上电

• 写禁止 (WRDI)指令完成

• 字节编程指令完成

• 自动地址递增 (AAI)编程完成或达到其最高的不受保护的存储器地址

• 扇区擦除指令完成

• 块擦除指令完成

• 全片擦除指令完成

• 写状态寄存器指令

© 2011 Silicon Storage Technology, Inc.

7

DS25044A_CN

11/11

�

A Microchip Technology Company

16 Mb SPI 串行闪存

SST25VF016B

数据手册

自动地址递增 (AAI)

自动地址递增编程状态位提供有关器件处于自动地址递增 (Auto Address Increment, AAI)编程模式

还是字节编程模式的状态。上电时默认为字节编程模式。

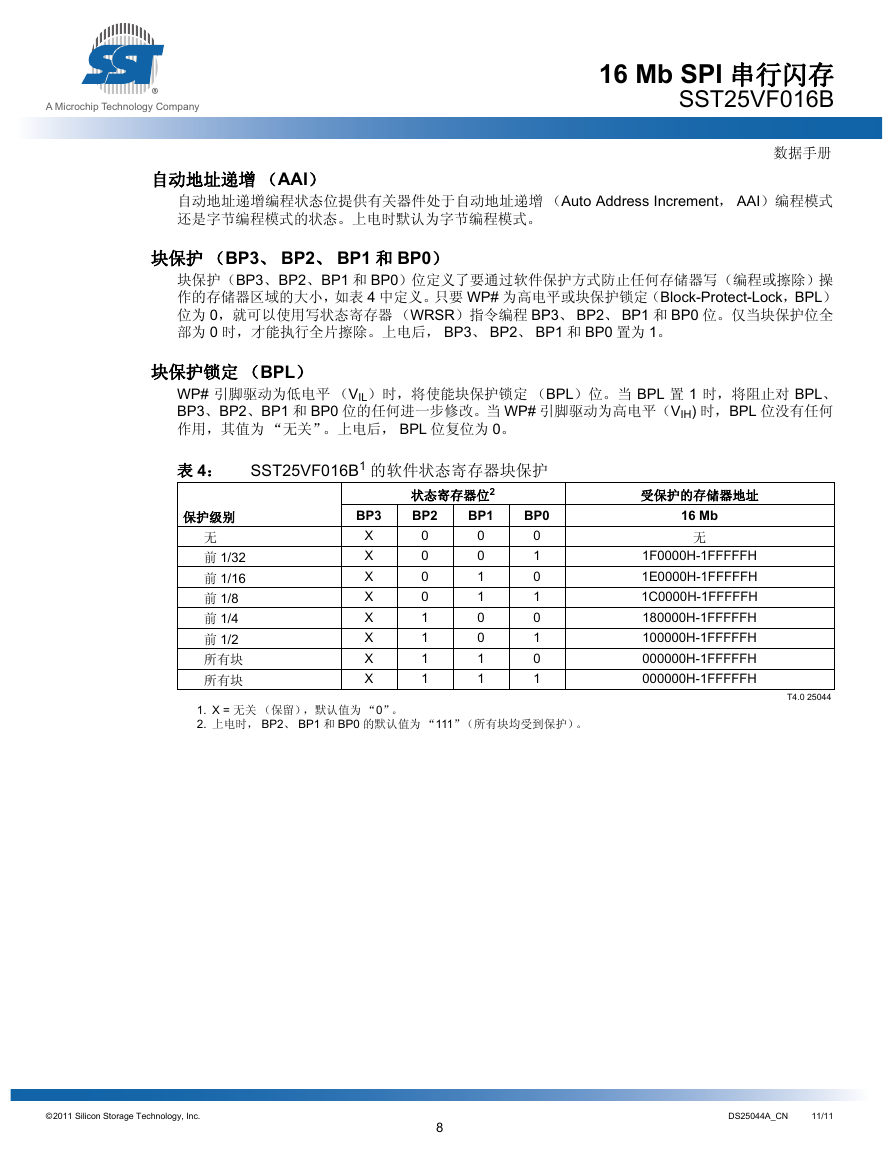

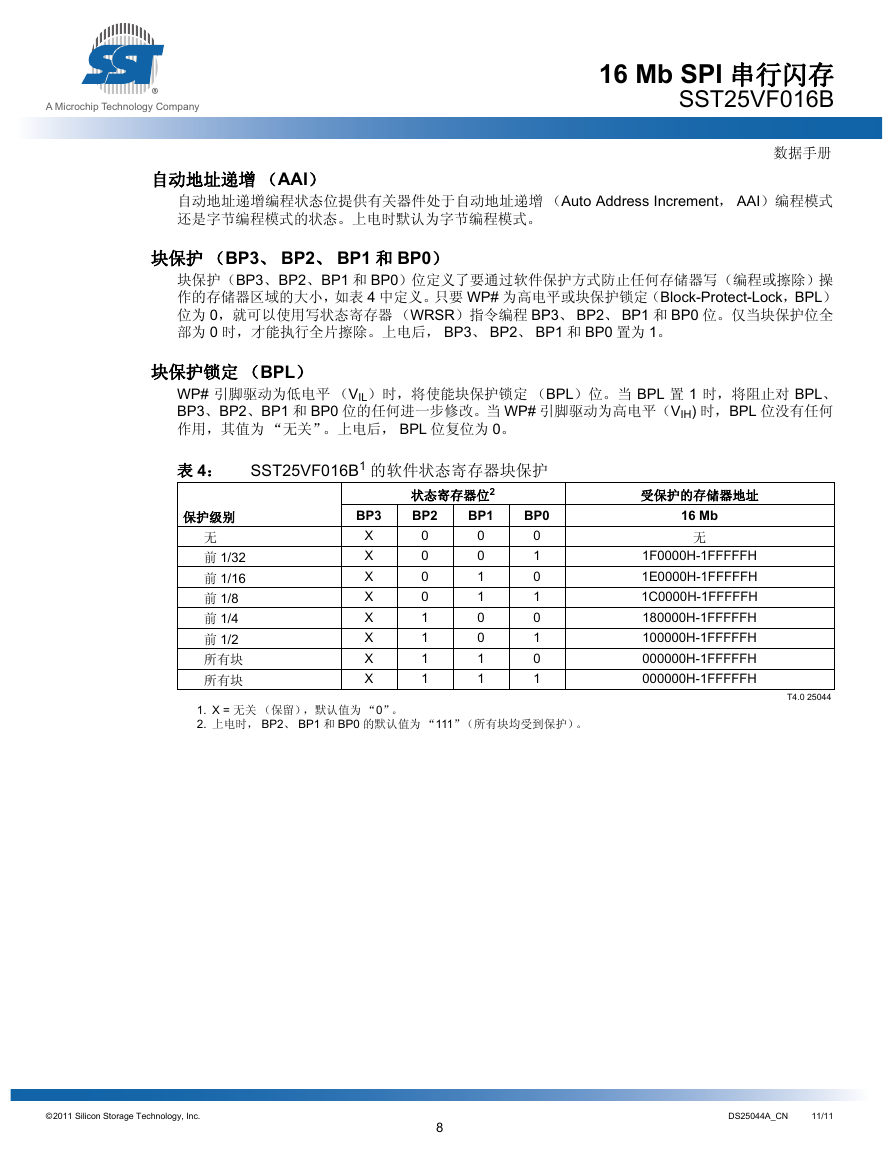

块保护 (BP3、 BP2、 BP1 和 BP0)

块保护(BP3、BP2、BP1 和 BP0)位定义了要通过软件保护方式防止任何存储器写(编程或擦除)操

作的存储器区域的大小,如表 4 中定义。只要 WP# 为高电平或块保护锁定(Block-Protect-Lock,BPL)

位为 0,就可以使用写状态寄存器 (WRSR)指令编程 BP3、 BP2、 BP1 和 BP0 位。仅当块保护位全

部为 0 时,才能执行全片擦除。上电后, BP3、 BP2、 BP1 和 BP0 置为 1。

块保护锁定 (BPL)

WP# 引脚驱动为低电平 (VIL)时,将使能块保护锁定 (BPL)位。当 BPL 置 1 时,将阻止对 BPL、

BP3、BP2、BP1 和 BP0 位的任何进一步修改。当 WP# 引脚驱动为高电平(VIH) 时,BPL 位没有任何

作用,其值为 “无关”。上电后, BPL 位复位为 0。

表 4: SST25VF016B1 的软件状态寄存器块保护

保护级别

无

前 1/32

前 1/16

前 1/8

前 1/4

前 1/2

所有块

所有块

状态寄存器位2

BP2

BP1

0

0

0

0

1

0

1

0

1

0

0

1

1

1

1

1

BP3

X

X

X

X

X

X

X

X

BP0

0

1

0

1

0

1

0

1

受保护的存储器地址

16 Mb

无

1F0000H-1FFFFFH

1E0000H-1FFFFFH

1C0000H-1FFFFFH

180000H-1FFFFFH

100000H-1FFFFFH

000000H-1FFFFFH

000000H-1FFFFFH

1. X = 无关 (保留),默认值为 “0”。

2. 上电时, BP2、 BP1 和 BP0 的默认值为 “111”(所有块均受到保护)。

T4.0 25044

© 2011 Silicon Storage Technology, Inc.

8

DS25044A_CN

11/11

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc