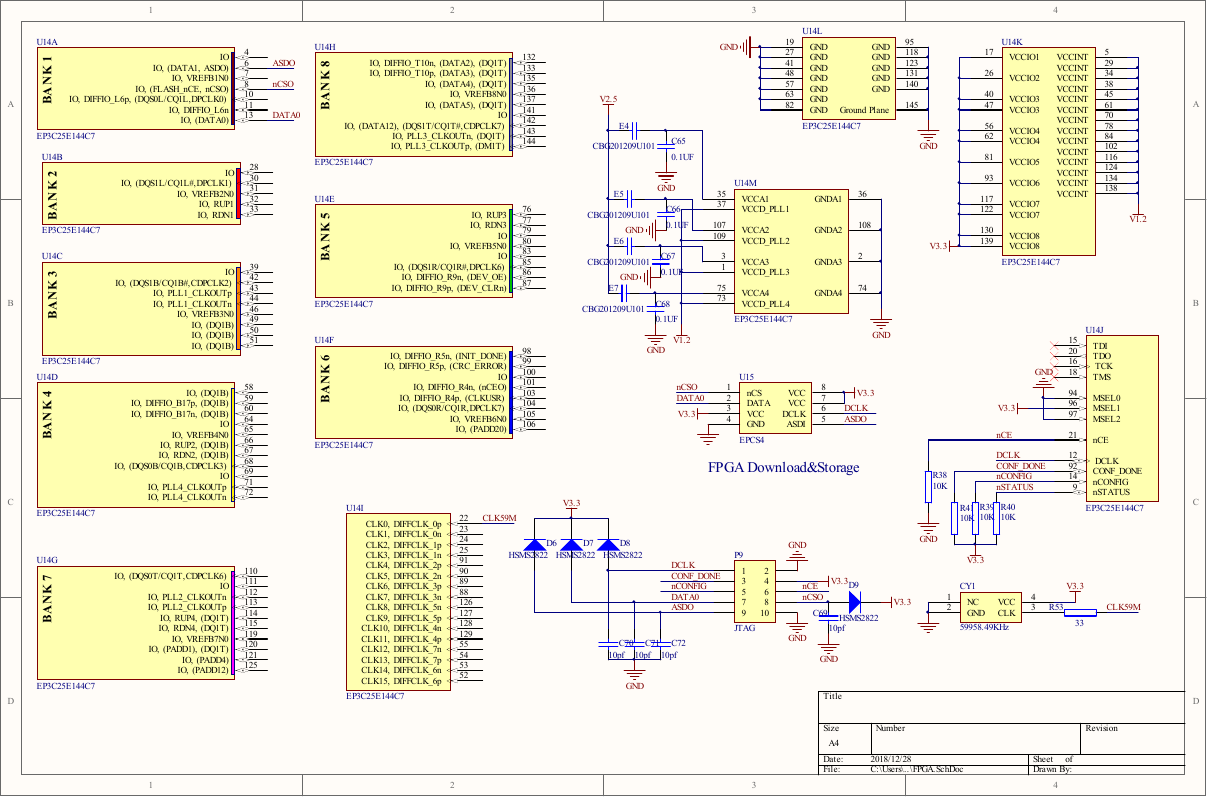

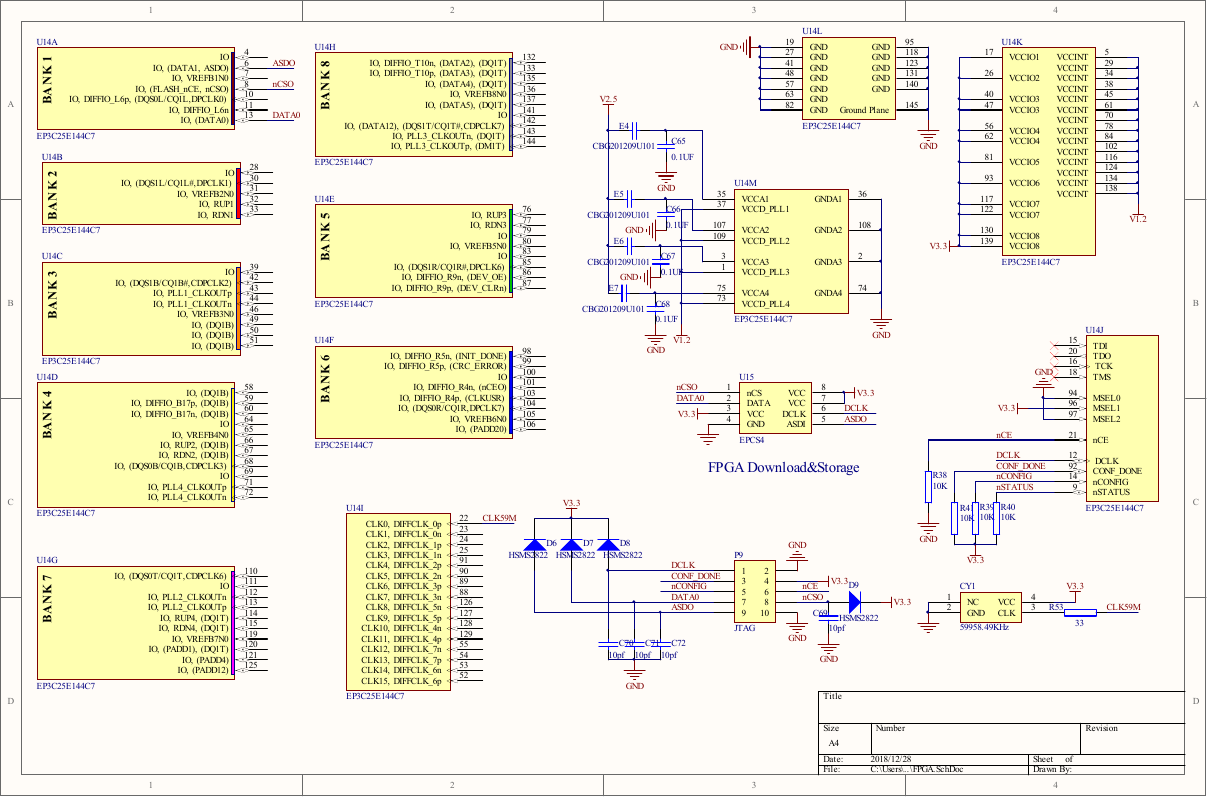

11223344DDCCBBAATitleNumberRevisionSizeA4Date:2018/12/28Sheet ofFile:C:\Users\..\FPGA.SchDocDrawn By:BANK 1IO4IO, (DATA1, ASDO)6IO, VREFB1N07IO, (FLASH_nCE, nCSO)8IO, DIFFIO_L6p, (DQS0L/CQ1L,DPCLK0)10IO, DIFFIO_L6n11IO, (DATA0)13U14AEP3C25E144C7BANK 2IO28IO, (DQS1L/CQ1L#,DPCLK1)30IO, VREFB2N031IO, RUP132IO, RDN133U14BEP3C25E144C7BANK 3IO39IO, (DQS1B/CQ1B#,CDPCLK2)42IO, PLL1_CLKOUTp43IO, PLL1_CLKOUTn44IO, VREFB3N046IO, (DQ1B)49IO, (DQ1B)50IO, (DQ1B)51U14CEP3C25E144C7BANK 4IO, (DQ1B)58IO, DIFFIO_B17p, (DQ1B)59IO, DIFFIO_B17n, (DQ1B)60IO64IO, VREFB4N065IO, RUP2, (DQ1B)66IO, RDN2, (DQ1B)67IO, (DQS0B/CQ1B,CDPCLK3)68IO69IO, PLL4_CLKOUTp71IO, PLL4_CLKOUTn72U14DEP3C25E144C7BANK 5IO, RUP376IO, RDN377IO79IO, VREFB5N080IO83IO, (DQS1R/CQ1R#,DPCLK6)85IO, DIFFIO_R9n, (DEV_OE)86IO, DIFFIO_R9p, (DEV_CLRn)87U14EEP3C25E144C7BANK 6IO, DIFFIO_R5n, (INIT_DONE)98IO, DIFFIO_R5p, (CRC_ERROR)99IO100IO, DIFFIO_R4n, (nCEO)101IO, DIFFIO_R4p, (CLKUSR)103IO, (DQS0R/CQ1R,DPCLK7)104IO, VREFB6N0105IO, (PADD20)106U14FEP3C25E144C7BANK 7IO, (DQS0T/CQ1T,CDPCLK6)110IO111IO, PLL2_CLKOUTn112IO, PLL2_CLKOUTp113IO, RUP4, (DQ1T)114IO, RDN4, (DQ1T)115IO, VREFB7N0119IO, (PADD1), (DQ1T)120IO, (PADD4)121IO, (PADD12)125U14GEP3C25E144C7BANK 8IO, DIFFIO_T10n, (DATA2), (DQ1T)132IO, DIFFIO_T10p, (DATA3), (DQ1T)133IO, (DATA4), (DQ1T)135IO, VREFB8N0136IO, (DATA5), (DQ1T)137IO141IO, (DATA12), (DQS1T/CQ1T#,CDPCLK7)142IO, PLL3_CLKOUTn, (DQ1T)143IO, PLL3_CLKOUTp, (DM1T)144U14HEP3C25E144C7CLK0, DIFFCLK_0p22CLK1, DIFFCLK_0n23CLK2, DIFFCLK_1p24CLK3, DIFFCLK_1n25CLK15, DIFFCLK_6p52CLK14, DIFFCLK_6n53CLK13, DIFFCLK_7p54CLK12, DIFFCLK_7n55CLK7, DIFFCLK_3n88CLK6, DIFFCLK_3p89CLK5, DIFFCLK_2n90CLK4, DIFFCLK_2p91CLK8, DIFFCLK_5n126CLK9, DIFFCLK_5p127CLK10, DIFFCLK_4n128CLK11, DIFFCLK_4p129U14IEP3C25E144C7nSTATUS9DCLK12nCONFIG14TDI15TCK16TMS18TDO20nCE21CONF_DONE92MSEL094MSEL196MSEL297U14JEP3C25E144C7VCCINT5VCCIO117VCCIO226VCCINT29VCCINT34VCCINT38VCCIO340VCCINT45VCCIO347VCCIO456VCCINT61VCCIO462VCCINT70VCCINT78VCCIO581VCCINT84VCCIO693VCCINT102VCCINT116VCCIO7117VCCIO7122VCCINT124VCCIO8130VCCINT134VCCINT138VCCIO8139U14KEP3C25E144C7GND19GND27GND41GND48GND57GND63GND82GND95GND118GND123GND131GND140Ground Plane145U14LEP3C25E144C7VCCD_PLL31GNDA32VCCA33VCCA135GNDA136VCCD_PLL137VCCD_PLL473GNDA474VCCA475VCCA2107GNDA2108VCCD_PLL2109U14MEP3C25E144C7V1.2V3.3GNDGNDR3810KGNDR4110KR3910KR4010KV3.3DCLKV3.3GNDV1.2V2.5GNDnCECONF_DONEnCONFIGnSTATUS12345678910P9JTAGGNDGNDV3.3nCS1DATA2VCC3GND4ASDI5DCLK6VCC7VCC8U15EPCS4V3.3FPGA Download&StorageV3.3ASDOnCSODATA0DCLKASDOnCSODATA0CONF_DONEnCONFIGnCEDATA0DCLKnCSOASDONC1GND2CLK3VCC4CY159958.49KHzV3.3CLK59MC7210pfC7110pfC7010pfGNDC6910pfGNDD8HSMS2822D7HSMS2822D6HSMS2822D9HSMS2822V3.3V3.3CLK59ME4CBG201209U101E5CBG201209U101E6CBG201209U101E7CBG201209U101C650.1UFGNDC660.1UFGNDC670.1UFGNDC680.1UFGNDR5333�

Bill of MaterialsBill of Materials For Project [Free Documents] (No PCB Document Selected)Source Data From:Free DocumentsProject:Free DocumentsVariant:NoneCreation Date:2018/12/2821:36:40Print Date:4346243462.90058#Column Name Error:Footprint#Column Name Error:Comment#Column Name Error:LibRef#Column Name Error:Designator#Column Name Error:Description#Column Name Error:Quantity0ApprovedNotes �

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc