DDC DUC detailed design specification V0.1

DDC & DUC for reference Design

DDC & DUC Detailed Design

Specification

Version 0.1

10/27/2008

Authors:

xxxx

Approvals:

Program/Project Manager ()

________________________________

(Signature) (Date)

Director, IP development ()

________________________________

(Signature) (Date)

�

Revision History

Revision

0.1

Author

xxxx

Date

xx/xx/xxxx

Description Of Changes

Initial document

�

Table of Content

2.1

2.2

1 设计简介 .................................................................................................................... 1

2 设计特征 .................................................................................................................... 1

DDC 设计参数 ................................................................................................... 1

DUC 设计参数: ............................................................................................... 2

3 系统设计框图及时钟单元说明 ................................................................................ 2

4 DDC 详细设计说明 ................................................................................................... 4

4.1 DDC 设计说明 ....................................................................................... 4

4.1.1 输入信号形式 ................................................................................ 4

4.1.2

DDC 实现框图说明 .................................................................... 4

Lattice Semiconductor Corp. i

�

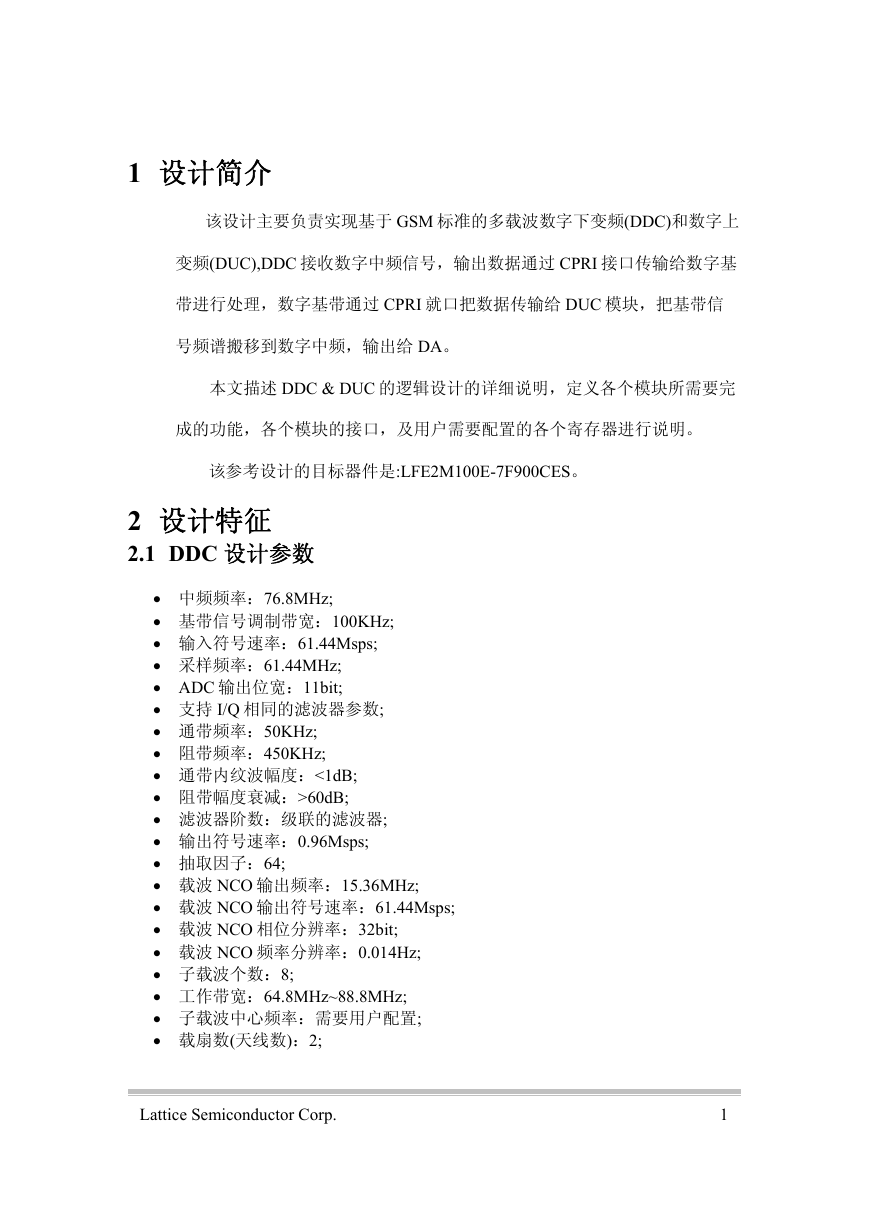

该设计主要负责实现基于 GSM 标准的多载波数字下变频(DDC)和数字上

变频(DUC),DDC 接收数字中频信号,输出数据通过 CPRI 接口传输给数字基

带进行处理,数字基带通过 CPRI 就口把数据传输给 DUC 模块,把基带信

号频谱搬移到数字中频,输出给 DA。

本文描述 DDC & DUC 的逻辑设计的详细说明,定义各个模块所需要完

成的功能,各个模块的接口,及用户需要配置的各个寄存器进行说明。

该参考设计的目标器件是:LFE2M100E-7F900CES。

2 设计特征

2.1 DDC 设计参数

1 设计简介

• 中频频率:76.8MHz;

• 基带信号调制带宽:100KHz;

• 输入符号速率:61.44Msps;

• 采样频率:61.44MHz;

• ADC 输出位宽:11bit;

• 支持 I/Q 相同的滤波器参数;

• 通带频率:50KHz;

• 阻带频率:450KHz;

• 通带内纹波幅度:<1dB;

• 阻带幅度衰减:>60dB;

• 滤波器阶数:级联的滤波器;

• 输出符号速率:0.96Msps;

• 抽取因子:64;

• 载波 NCO 输出频率:15.36MHz;

• 载波 NCO 输出符号速率:61.44Msps;

• 载波 NCO 相位分辨率:32bit;

• 载波 NCO 频率分辨率:0.014Hz;

• 子载波个数:8;

• 工作带宽:64.8MHz~88.8MHz;

• 子载波中心频率:需要用户配置;

• 载扇数(天线数):2;

Lattice Semiconductor Corp. 1

�

• 通道数:8;

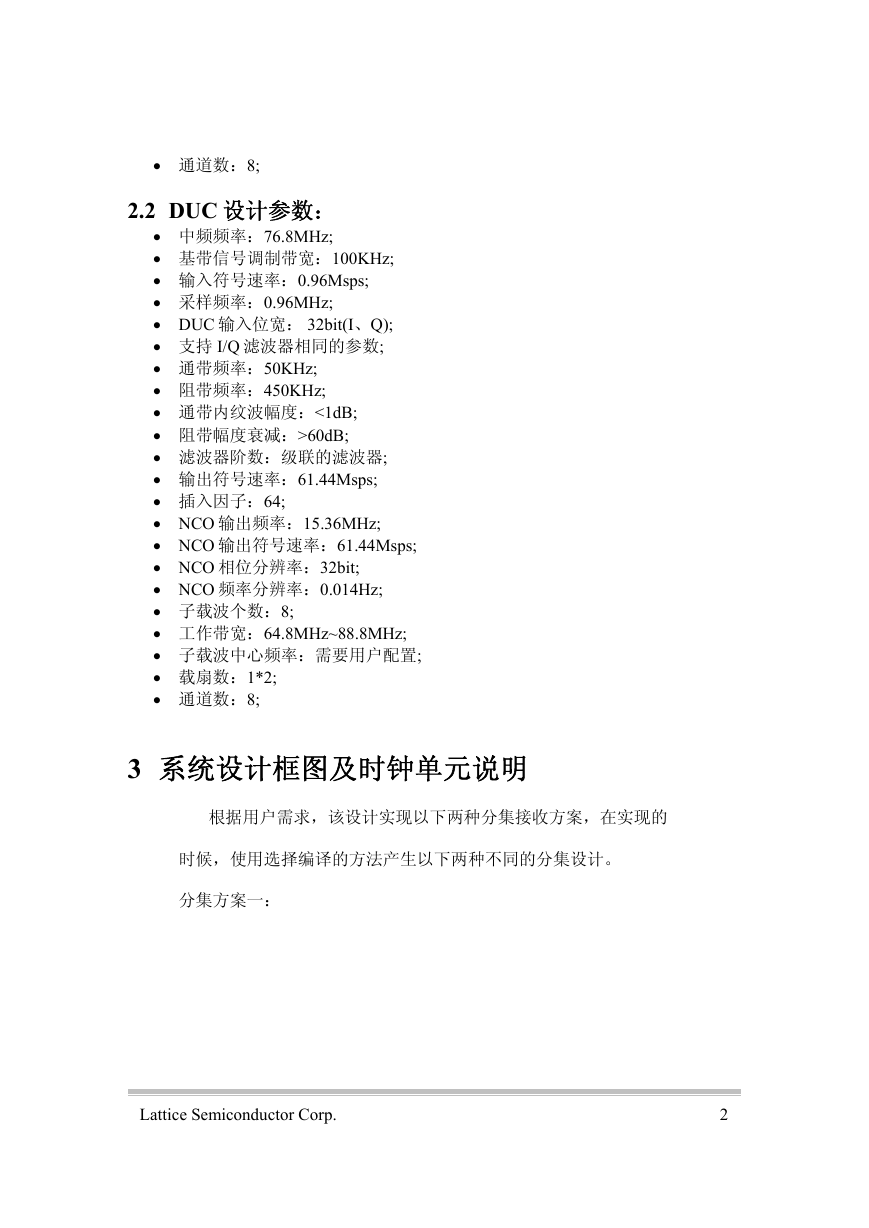

2.2 DUC 设计参数:

• 中频频率:76.8MHz;

• 基带信号调制带宽:100KHz;

• 输入符号速率:0.96Msps;

• 采样频率:0.96MHz;

• DUC 输入位宽: 32bit(I、Q);

• 支持 I/Q 滤波器相同的参数;

• 通带频率:50KHz;

• 阻带频率:450KHz;

• 通带内纹波幅度:<1dB;

• 阻带幅度衰减:>60dB;

• 滤波器阶数:级联的滤波器;

• 输出符号速率:61.44Msps;

• 插入因子:64;

• NCO 输出频率:15.36MHz;

• NCO 输出符号速率:61.44Msps;

• NCO 相位分辨率:32bit;

• NCO 频率分辨率:0.014Hz;

• 子载波个数:8;

• 工作带宽:64.8MHz~88.8MHz;

• 子载波中心频率:需要用户配置;

• 载扇数:1*2;

• 通道数:8;

3 系统设计框图及时钟单元说明

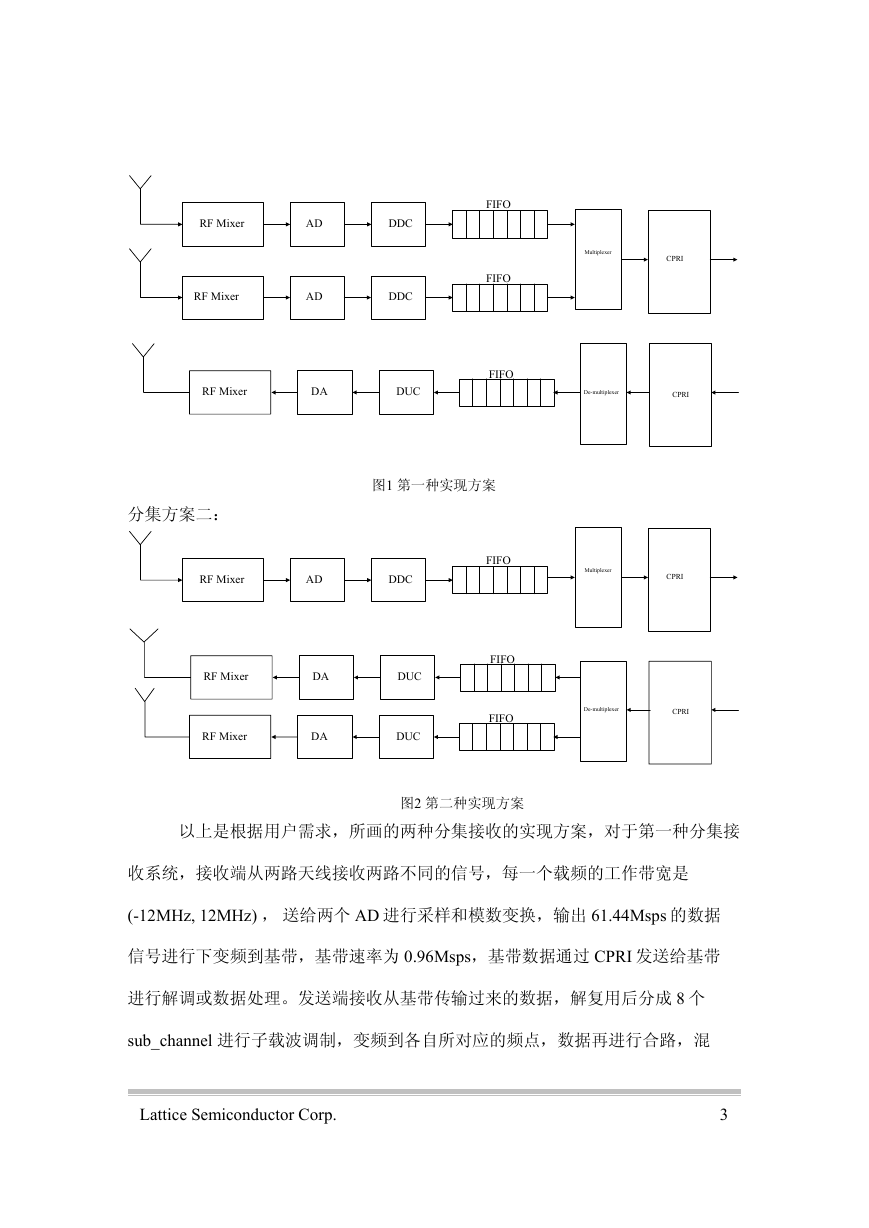

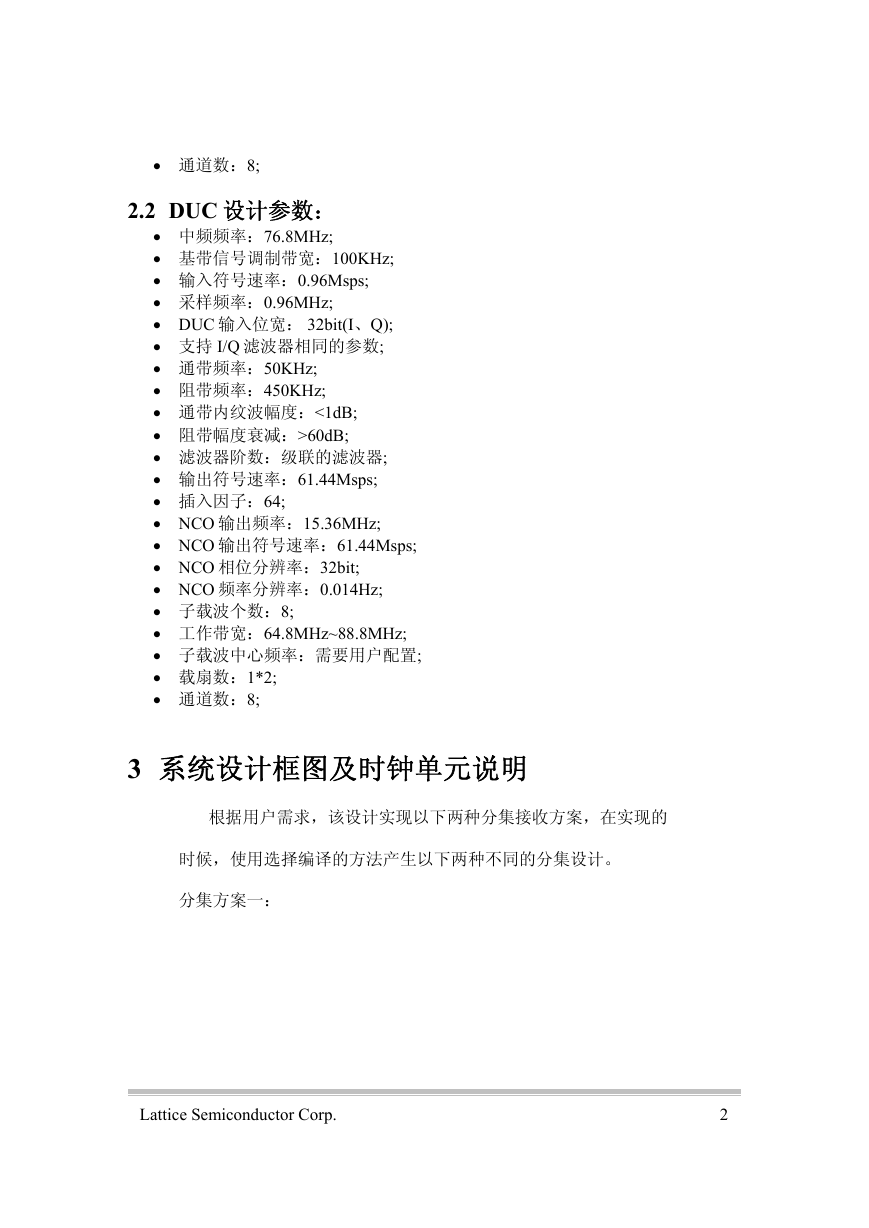

根据用户需求,该设计实现以下两种分集接收方案,在实现的

时候,使用选择编译的方法产生以下两种不同的分集设计。

分集方案一:

Lattice Semiconductor Corp. 2

�

RF Mixer

AD

DDC

RF Mixer

AD

DDC

Multiplexer

CPRI

FIFO

FIFO

FIFO

RF Mixer

DA

DUC

De-multiplexer

CPRI

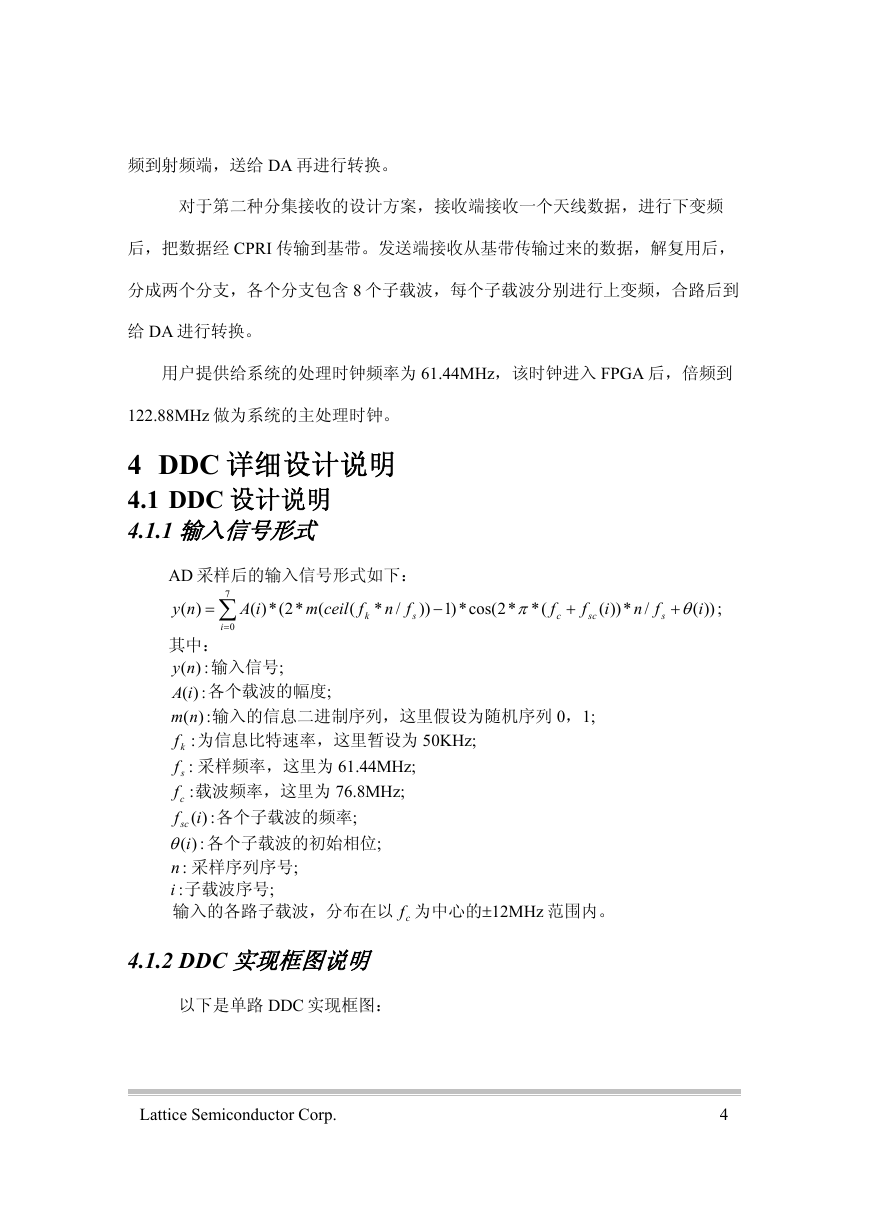

分集方案二:

图1 第一种实现方案

RF Mixer

AD

DDC

RF Mixer

RF Mixer

DA

DA

DUC

DUC

FIFO

FIFO

FIFO

Multiplexer

CPRI

De-multiplexer

CPRI

图2 第二种实现方案

以上是根据用户需求,所画的两种分集接收的实现方案,对于第一种分集接

收系统,接收端从两路天线接收两路不同的信号,每一个载频的工作带宽是

(-12MHz, 12MHz) , 送给两个 AD 进行采样和模数变换,输出 61.44Msps 的数据

信号进行下变频到基带,基带速率为 0.96Msps,基带数据通过 CPRI 发送给基带

进行解调或数据处理。发送端接收从基带传输过来的数据,解复用后分成 8 个

sub_channel 进行子载波调制,变频到各自所对应的频点,数据再进行合路,混

Lattice Semiconductor Corp. 3

�

对于第二种分集接收的设计方案,接收端接收一个天线数据,进行下变频

频到射频端,送给 DA 再进行转换。

后,把数据经 CPRI 传输到基带。发送端接收从基带传输过来的数据,解复用后,

分成两个分支,各个分支包含 8 个子载波,每个子载波分别进行上变频,合路后到

给 DA 进行转换。

用户提供给系统的处理时钟频率为 61.44MHz,该时钟进入 FPGA 后,倍频到

122.88MHz 做为系统的主处理时钟。

4 DDC 详细设计说明

4.1 DDC 设计说明

4.1.1 输入信号形式

fn

i

/*))(

+

θ

i

))(

;

s

k

−

s

=

0

f

sc

f

c

+

AD 采样后的输入信号形式如下:

ny

fn

)(

/*

))

iA

m

(*2(*)(

ceil

(

f

7

π

*)1

cos(

(**2

= ∑

i

其中:

:)(ny 输入信号;

:)(iA 各个载波的幅度;

:)(nm 输入的信息二进制序列,这里假设为随机序列 0,1;

:kf 为信息比特速率,这里暂设为 50KHz;

sf

: 采样频率,这里为 61.44MHz;

:cf 载波频率,这里为 76.8MHz;

f sc 各个子载波的频率;

:)(iθ 各个子载波的初始相位;

n : 采样序列序号;

:i 子载波序号;

输入的各路子载波,分布在以 cf 为中心的±12MHz 范围内。

:)(i

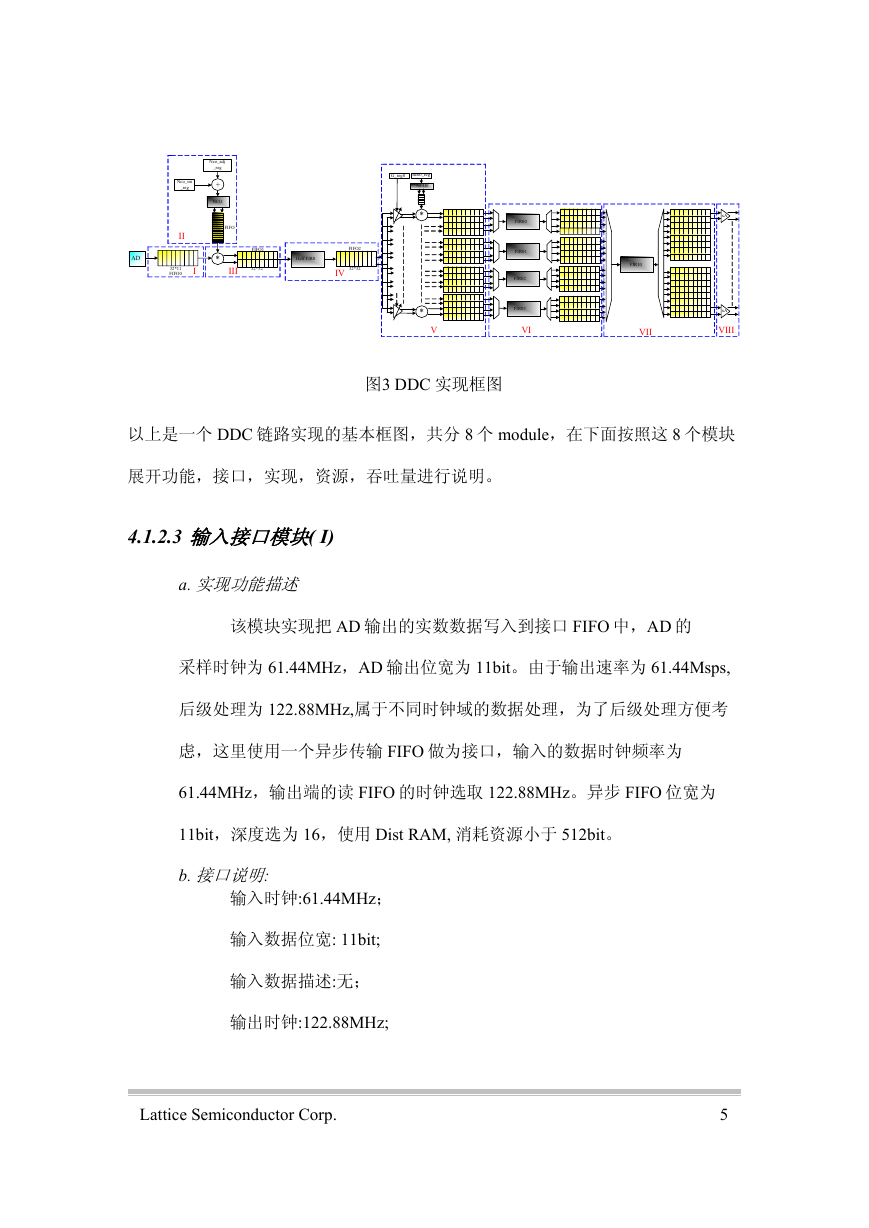

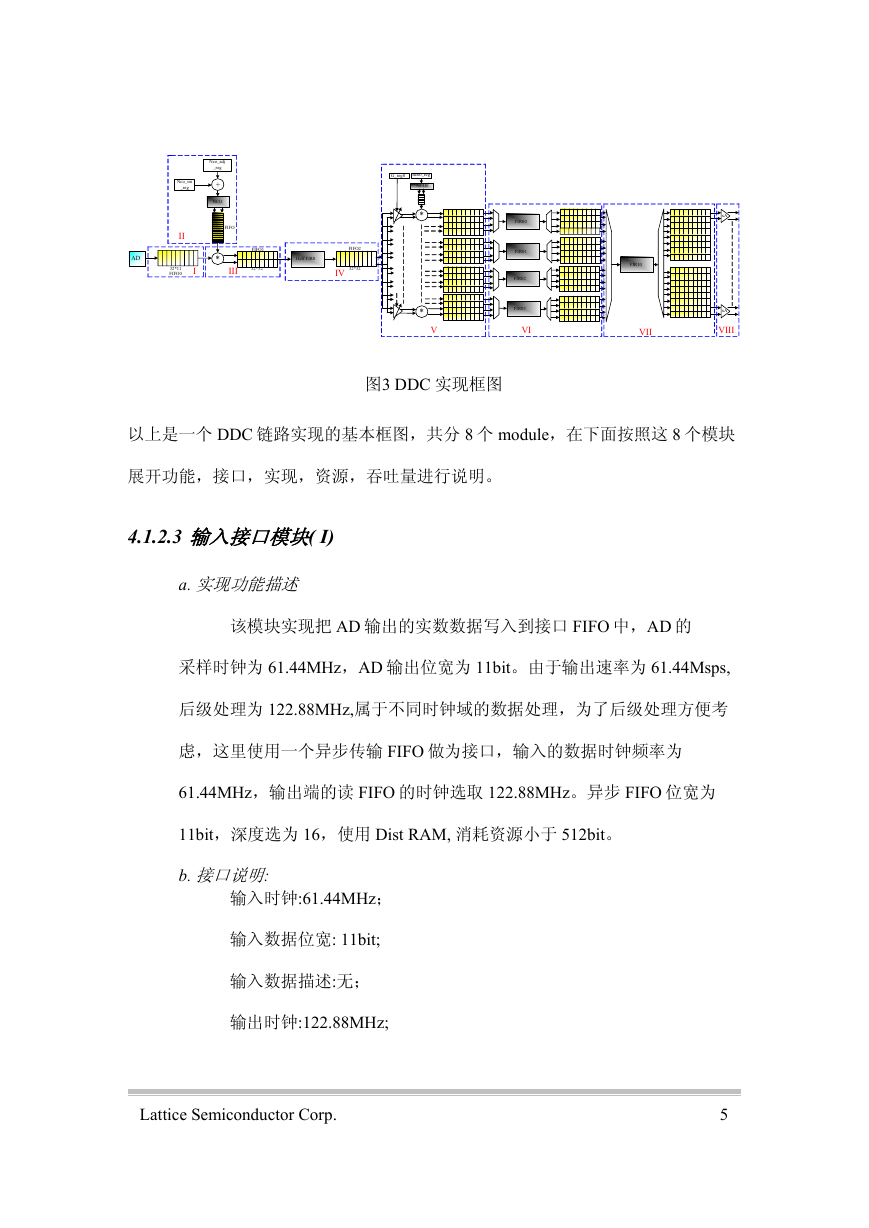

4.1.2 DDC 实现框图说明

以下是单路 DDC 实现框图:

Lattice Semiconductor Corp. 4

�

Nco_ini

_reg

II

AD

32*11

FIFO0

I

Nco_adj

_reg

+

NCO

FIFO

*

III

FIFO1

32*32

Half FIR0

FIFO2

32*32

IV

G_reg0

nco0_reg

NCO0

*

*

V

FIR00

FIR01

FIR02

FIR03

VI

xA

xA

VIII

FIR10

VII

图3 DDC 实现框图

以上是一个 DDC 链路实现的基本框图,共分 8 个 module,在下面按照这 8 个模块

展开功能,接口,实现,资源,吞吐量进行说明。

4.1.2.3 输入接口模块( I)

a. 实现功能描述

该模块实现把 AD 输出的实数数据写入到接口 FIFO 中,AD 的

采样时钟为 61.44MHz,AD 输出位宽为 11bit。由于输出速率为 61.44Msps,

后级处理为 122.88MHz,属于不同时钟域的数据处理,为了后级处理方便考

虑,这里使用一个异步传输 FIFO 做为接口,输入的数据时钟频率为

61.44MHz,输出端的读 FIFO 的时钟选取 122.88MHz。异步 FIFO 位宽为

11bit,深度选为 16,使用 Dist RAM, 消耗资源小于 512bit。

b. 接口说明:

输入时钟:61.44MHz;

输入数据位宽: 11bit;

输入数据描述:无;

输出时钟:122.88MHz;

Lattice Semiconductor Corp. 5

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc