BCM2711 ARM Peripherals

Raspberry Pi (Trading) Ltd.

Version 1, 5th February 2020

�

BCM2711 ARM Peripherals

Copyright 2012 Broadcom Europe Ltd., 2020 Raspberry Pi (Trading) Ltd.

Table of Contents

Colophon . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

List of Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

List of Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.2. Address map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.2.1. Diagrammatic overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.2.2. Full 35-bit address map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.2.3. ARM physical addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.2.4. Legacy master addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1.3. Peripheral access precautions for correct memory ordering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2. Auxiliaries: UART1, SPI1 & SPI2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.1.1. AUX registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.2. Mini UART . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.2.1. Mini UART implementation details . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.2.2. Mini UART register details . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.3. Universal SPI Master (2x). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.3.1. SPI implementation details . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.3.2. Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

2.3.3. Long bit streams. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2.3.4. SPI register details . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3. BSC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.2. Register View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.3. 10-Bit Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

3.3.1. Writing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

3.3.2. Reading. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4. DMA Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

4.1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

4.2. DMA Controller Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

4.2.1. DMA Channel Register Address Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Control Block Data Structure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Peripheral DREQ Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

4.3. AXI Bursts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

4.4. Error Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

ii

Release 1

�

BCM2711 ARM Peripherals

Copyright 2012 Broadcom Europe Ltd., 2020 Raspberry Pi (Trading) Ltd.

4.5. DMA LITE Engines. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

4.6. DMA4 Engines. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

5. General Purpose I/O (GPIO). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

5.1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

5.2. Register View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

5.3. Alternative Function Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

5.4. General Purpose GPIO Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

5.4.1. Operating Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

5.4.2. Register Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

6. Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

6.1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

6.2. Interrupt sources. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

6.2.1. ARM Core n interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

6.2.2. ARM_LOCAL interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

6.2.3. ARMC interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

6.2.4. VideoCore interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

6.2.5. ETH_PCIe interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

6.3. GIC-400 interrupt controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

6.4. Legacy interrupt controller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

6.5. Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

6.5.1. GIC-400 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

6.5.2. ARM_LOCAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

6.5.3. ARMC. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

7. PCM / I2S Audio . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

7.1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

7.2. Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

7.3. Typical Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

7.4. Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

7.5. Software Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

7.5.1. Operating in Polled mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

7.5.2. Operating in Interrupt mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

7.5.3. DMA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

7.6. Error Handling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

7.7. PDM Input Mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

7.8. GRAY Code Input Mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

7.9. PCM Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

8. Pulse Width Modulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

8.1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

8.2. Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

iii

Release 1

�

BCM2711 ARM Peripherals

Copyright 2012 Broadcom Europe Ltd., 2020 Raspberry Pi (Trading) Ltd.

8.3. PWM Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

8.4. Modes of Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

8.5. Quick Reference. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

8.6. Control and Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

9. SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

9.1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

9.2. SPI Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

9.2.1. Standard mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

9.2.2. Bidirectional mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

9.3. LoSSI mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

9.3.1. Command write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

9.3.2. Parameter write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

9.3.3. Byte read commands. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

9.3.4. 24-bit read command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

9.3.5. 32-bit read command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

9.4. Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

9.5. SPI Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

9.6. Software Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

9.6.1. Polled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

9.6.2. Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

9.6.3. DMA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

9.6.4. Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

10. System Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

10.1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

10.2. System Timer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

11. UART. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

11.1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

11.2. Variations from the 16C650 UART . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

11.3. Primary UART Inputs and Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

11.4. UART Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 180

11.5. Register View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

12. Timer (ARM side) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

12.1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

12.2. Timer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

13. ARM Mailboxes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

13.1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

13.2. Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

iv

Release 1

�

BCM2711 ARM Peripherals

Copyright 2012 Broadcom Europe Ltd., 2020 Raspberry Pi (Trading) Ltd.

Colophon

BCM2711 ARM Peripherals, based in large part on the earlier BCM2835 ARM Peripherals documentation.

© 2012 Broadcom Europe Ltd., 2020 Raspberry Pi (Trading) Ltd.

All rights reserved.

Release

1

Date

05/02/2020

Description

First release

Table 1. Release History

The latest release of this document can be found at https://www.raspberrypi.org

Colophon

1

Release 1

�

BCM2711 ARM Peripherals

Copyright 2012 Broadcom Europe Ltd., 2020 Raspberry Pi (Trading) Ltd.

List of Figures

Figure 1 . . . . . BCM2711 Address Maps

Figure 2 . . . . . Write to a slave with 10-bit address

Figure 3 . . . . . Read from slave with 10-bit address

Figure 4 . . . . . GPIO Block Diagram

Figure 5 . . . . . Interrupt sources and destinations

Figure 6 . . . . . Peripheral IRQ OR-ing

Figure 7 . . . . . GIC IRQ routing

Figure 8 . . . . . Legacy IRQ routing

Figure 9 . . . . . Legacy IRQ status registers

Figure 10 . . . . PCM Audio Interface Typical Timing

Figure 11 . . . . PCM Audio Interface Block Diagram

Figure 12 . . . . Timing at Start of Frame

Figure 13 . . . . Gray mode input format

Figure 14 . . . . PWM block diagram

Figure 15 . . . . Serial bit transmission when M/S Mode enabled

Figure 16 . . . . SPI Master Typical Usage

Figure 17 . . . . SPI Cycle

Figure 18 . . . . Different Clock Polarity/Phase

Figure 19 . . . . Bidirectional SPI Master Typical Usage

Figure 20 . . . . LoSSI mode Typical usage

Figure 21 . . . . Serial interface Block Diagram

List of Figures

2

Release 1

�

BCM2711 ARM Peripherals

Copyright 2012 Broadcom Europe Ltd., 2020 Raspberry Pi (Trading) Ltd.

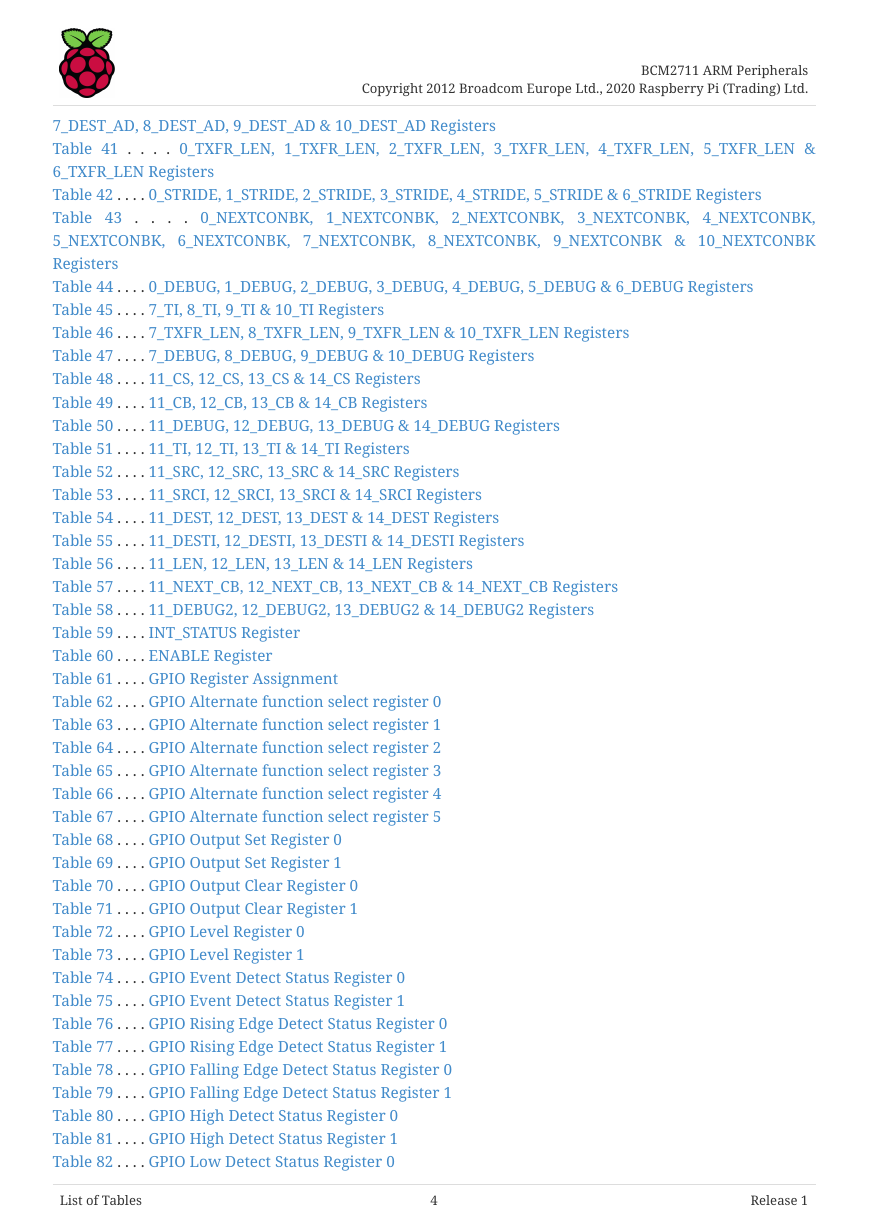

List of Tables

Table 1 . . . . . Release History

Table 2 . . . . . Auxiliary peripherals Address Map

Table 3 . . . . . AUX_IRQ Register

Table 4 . . . . . AUX_ENABLES Register

Table 5 . . . . . AUX_MU_IO_REG Register

Table 6 . . . . . AUX_MU_IER_REG Register

Table 7 . . . . . AUX_MU_IIR_REG Register

Table 8 . . . . . AUX_MU_LCR_REG Register

Table 9 . . . . . AUX_MU_MCR_REG Register

Table 10 . . . . AUX_MU_LSR_REG Register

Table 11 . . . . AUX_MU_MSR_REG Register

Table 12 . . . . AUX_MU_SCRATCH Register

Table 13 . . . . AUX_MU_CNTL_REG Register

Table 14 . . . . AUX_MU_STAT_REG Register

Table 15 . . . . AUX_MU_BAUD_REG Register

Table 16 . . . . AUX_SPI1_CNTL0_REG & AUX_SPI2_CNTL0_REG Registers

Table 17 . . . . AUX_SPI1_CNTL1_REG & AUX_SPI2_CNTL1_REG Registers

Table 18 . . . . AUX_SPI1_STAT_REG & AUX_SPI2_STAT_REG Registers

Table 19 . . . . AUX_SPI1_PEEK_REG & AUX_SPI2_PEEK_REG Registers

Table 20 . . . . AUX_SPI1_IO_REG & AUX_SPI2_IO_REG Registers

Table 21 . . . . AUX_SPI1_TXHOLD_REG & AUX_SPI2_TXHOLD_REG Registers

Table 22 . . . . I2C Address Map

Table 23 . . . . C Register

Table 24 . . . . S Register

Table 25 . . . . DLEN Register

Table 26 . . . . A Register

Table 27 . . . . FIFO Register

Table 28 . . . . DIV Register

Table 29 . . . . DEL Register

Table 30 . . . . CLKT Register

Table 31 . . . . DMA Controller Register Address Map

Table 32 . . . . DMA Control Block Definition

Table 33 . . . . DMA Lite Control Block Definition

Table 34 . . . . DMA4 Control Block Definition

Table 35 . . . . DMA Controller Register Map

Table 36 . . . . 0_CS, 1_CS, 2_CS, 3_CS, 4_CS, 5_CS, 6_CS, 7_CS, 8_CS, 9_CS & 10_CS Registers

Table 37

. 0_CONBLK_AD, 1_CONBLK_AD, 2_CONBLK_AD, 3_CONBLK_AD, 4_CONBLK_AD,

5_CONBLK_AD, 6_CONBLK_AD, 7_CONBLK_AD, 8_CONBLK_AD, 9_CONBLK_AD & 10_CONBLK_AD

Registers

Table 38 . . . . 0_TI, 1_TI, 2_TI, 3_TI, 4_TI, 5_TI & 6_TI Registers

Table 39 . . . . 0_SOURCE_AD, 1_SOURCE_AD, 2_SOURCE_AD, 3_SOURCE_AD, 4_SOURCE_AD, 5_SOURCE_AD,

6_SOURCE_AD, 7_SOURCE_AD, 8_SOURCE_AD, 9_SOURCE_AD & 10_SOURCE_AD Registers

Table 40 . . . . 0_DEST_AD, 1_DEST_AD, 2_DEST_AD, 3_DEST_AD, 4_DEST_AD, 5_DEST_AD, 6_DEST_AD,

.

.

.

List of Tables

3

Release 1

�

BCM2711 ARM Peripherals

Copyright 2012 Broadcom Europe Ltd., 2020 Raspberry Pi (Trading) Ltd.

.

.

.

7_DEST_AD, 8_DEST_AD, 9_DEST_AD & 10_DEST_AD Registers

Table 41 . . . . 0_TXFR_LEN, 1_TXFR_LEN, 2_TXFR_LEN, 3_TXFR_LEN, 4_TXFR_LEN, 5_TXFR_LEN &

6_TXFR_LEN Registers

Table 42 . . . . 0_STRIDE, 1_STRIDE, 2_STRIDE, 3_STRIDE, 4_STRIDE, 5_STRIDE & 6_STRIDE Registers

Table 43

. 0_NEXTCONBK, 1_NEXTCONBK, 2_NEXTCONBK, 3_NEXTCONBK, 4_NEXTCONBK,

5_NEXTCONBK, 6_NEXTCONBK, 7_NEXTCONBK, 8_NEXTCONBK, 9_NEXTCONBK & 10_NEXTCONBK

Registers

Table 44 . . . . 0_DEBUG, 1_DEBUG, 2_DEBUG, 3_DEBUG, 4_DEBUG, 5_DEBUG & 6_DEBUG Registers

Table 45 . . . . 7_TI, 8_TI, 9_TI & 10_TI Registers

Table 46 . . . . 7_TXFR_LEN, 8_TXFR_LEN, 9_TXFR_LEN & 10_TXFR_LEN Registers

Table 47 . . . . 7_DEBUG, 8_DEBUG, 9_DEBUG & 10_DEBUG Registers

Table 48 . . . . 11_CS, 12_CS, 13_CS & 14_CS Registers

Table 49 . . . . 11_CB, 12_CB, 13_CB & 14_CB Registers

Table 50 . . . . 11_DEBUG, 12_DEBUG, 13_DEBUG & 14_DEBUG Registers

Table 51 . . . . 11_TI, 12_TI, 13_TI & 14_TI Registers

Table 52 . . . . 11_SRC, 12_SRC, 13_SRC & 14_SRC Registers

Table 53 . . . . 11_SRCI, 12_SRCI, 13_SRCI & 14_SRCI Registers

Table 54 . . . . 11_DEST, 12_DEST, 13_DEST & 14_DEST Registers

Table 55 . . . . 11_DESTI, 12_DESTI, 13_DESTI & 14_DESTI Registers

Table 56 . . . . 11_LEN, 12_LEN, 13_LEN & 14_LEN Registers

Table 57 . . . . 11_NEXT_CB, 12_NEXT_CB, 13_NEXT_CB & 14_NEXT_CB Registers

Table 58 . . . . 11_DEBUG2, 12_DEBUG2, 13_DEBUG2 & 14_DEBUG2 Registers

Table 59 . . . . INT_STATUS Register

Table 60 . . . . ENABLE Register

Table 61 . . . . GPIO Register Assignment

Table 62 . . . . GPIO Alternate function select register 0

Table 63 . . . . GPIO Alternate function select register 1

Table 64 . . . . GPIO Alternate function select register 2

Table 65 . . . . GPIO Alternate function select register 3

Table 66 . . . . GPIO Alternate function select register 4

Table 67 . . . . GPIO Alternate function select register 5

Table 68 . . . . GPIO Output Set Register 0

Table 69 . . . . GPIO Output Set Register 1

Table 70 . . . . GPIO Output Clear Register 0

Table 71 . . . . GPIO Output Clear Register 1

Table 72 . . . . GPIO Level Register 0

Table 73 . . . . GPIO Level Register 1

Table 74 . . . . GPIO Event Detect Status Register 0

Table 75 . . . . GPIO Event Detect Status Register 1

Table 76 . . . . GPIO Rising Edge Detect Status Register 0

Table 77 . . . . GPIO Rising Edge Detect Status Register 1

Table 78 . . . . GPIO Falling Edge Detect Status Register 0

Table 79 . . . . GPIO Falling Edge Detect Status Register 1

Table 80 . . . . GPIO High Detect Status Register 0

Table 81 . . . . GPIO High Detect Status Register 1

Table 82 . . . . GPIO Low Detect Status Register 0

List of Tables

4

Release 1

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc