2011-2012 年北京工业大学实验学院 EDA 实验设计报告

课 程 设 计 说 明 书

学院

专业

题目

学号

姓名

同组人员

报告完成日期

成绩

指导教师

1

�

2011-2012 年北京工业大学实验学院 EDA 实验设计报告

实验一 层次化4位加法器设计

一. 实验目的

1、掌握用 VHDL 设计全加器的方法并实现。

2、熟悉设计平台及 VHDL 层次化设计。

二. 实验仪器

1、硬件:计算机 Gxsoc/sops-Dev-Lab

CycloneII EP2C35F672C8 核心板

2、软件:正版 Quartus8.0

三. 实验设计要求

学习用 VHDL 或原理图设计方法,掌握全加器的设计方式及表

示方式,极其与二进制表示的转换方法,完成编译、综合、适配、

仿真和实验箱上的硬件测试,通过数码管观察结果。

采用层次化方法实现 4 位加法器,完成编译,仿真,引脚锁

定,下载。

四. 实验原理

通过动态扫描两组 4BIT 的二进制数据,同时还有一个单 BIT

的进位,把三者按照二进制加法原理进行加,求出和及进位,并

通过电路显示出各部分数据(输入,输出)。

加数、被加数、“和”显示在共阳数码管上,进位输出显示在

LED 上。

2

�

2011-2012 年北京工业大学实验学院 EDA 实验设计报告

五. 程序代码

1、半加器Hadder代码

LIBRARY Ieee;

USE Ieee.Std_Logic_1164.all;

ENTITY HADDER IS

Port (a,b: In Bit;

Co, So: Out Bit);

END HADDER;

ARCHITECTURE fh1 Of HADDER Is

BEGIN

So <= (a Xor b);

Co <= (a And b);

END fh1;

2、或门 ora 代码

LIBRARY Ieee;

USE Ieee.Std_Logic_1164.all;

ENTITY ora IS

Port ( a: in Std_Logic;

b: in Std_Logic;

c: out Std_Logic);

END ora;

ARCHITECTURE org OF ora IS

BEGIN

c <= a Or b;

END org;

3、1 位全加器 f_hadder 代码

LIBRARY Ieee;

USE Ieee.Std_Logic_1164.all;

ENTITY f_ADDER IS

Port (x: In Std_Logic;

y: In Std_Logic;

cin: In Std_Logic;

cout: Out Std_Logic;

3

�

2011-2012 年北京工业大学实验学院 EDA 实验设计报告

sum: Out Std_Logic);

END f_ADDER;

f_ADDER Is

ARCHITECTURE fd1 Of

Component HADDER

Port( a,b: In Std_Logic;

co,so: Out Std_Logic);

END Component;

Component ora

Port(a,b: In Std_Logic;

c: Out Std_Logic);

END Component;

Signal d,e,f: Std_Logic;

Begin

U1: HADDER

Port Map(a=>X,b=>Y,Co=>d,so=>e);

U2:HADDER

Port Map(a=>e,b=>cin,Co=>f,so=>sum);

U3:ora Port Map(a=>d,b=>f,c=>cout);

END ARCHITECTURE fd1;

4、4 位全加器 Qadd:

Library ieee;

Use ieee.std_logic_1164.all;

Entity Qadd is

Port (a:in std_logic_VECTOR(3 DOWNTO 0);

b:in std_logic_VECTOR(3 DOWNTO 0);

--cin:in std_logic;

s:out std_logic_VECTOR(3 DOWNTO 0));

End Qadd;

Architecture one of Qadd is

Signal c0,c1,c2,c3 : std_logic;

Component f_ADDER

Port (x: In Std_Logic;

y: In Std_Logic;

4

�

2011-2012 年北京工业大学实验学院 EDA 实验设计报告

cin: In Std_Logic;

cout: Out Std_Logic;

sum: Out Std_Logic);

END Component;

Begin

u1 :F_ADDER

Port map(sum=>s(0),cout=>c0,X=>a(0),Y=>b(0),cin=>'0');

u2 :F_ADDER

Port map(sum=>s(1),cout=>c1,X=>a(1),Y=>b(1),cin=>c0 );

u3 : F_ADDER

Port map(sum=>s(2),cout=>c2,X=>a(2),Y=>b(2),cin=>c1 );

u4 : F_ADDER

Port map(sum=>s(3),cout=>c3,X=>a(3),Y=>b(3),cin=>c2 );

END;

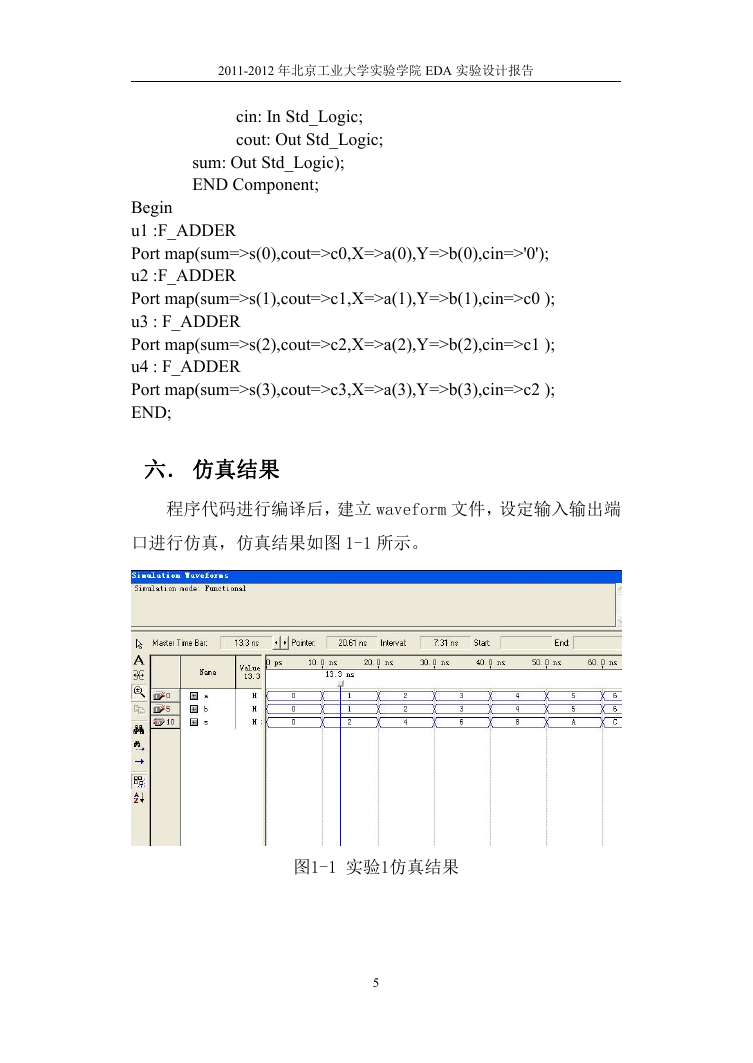

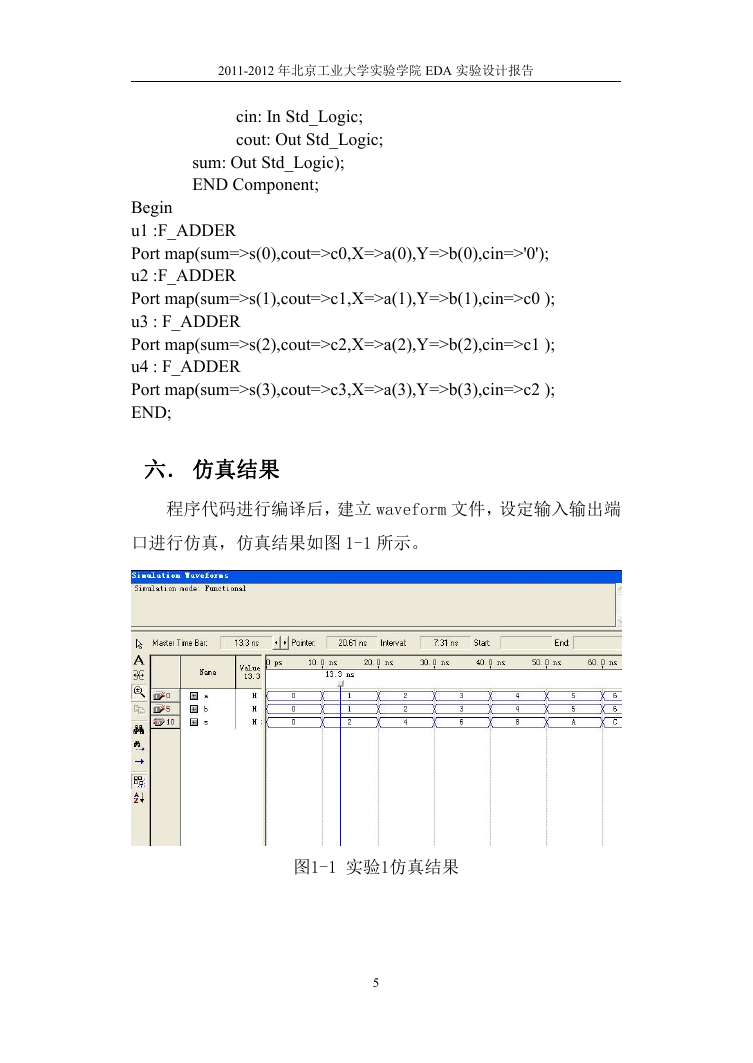

六. 仿真结果

程序代码进行编译后,建立 waveform 文件,设定输入输出端

口进行仿真,仿真结果如图 1-1 所示。

图1-1 实验1仿真结果

5

�

2011-2012 年北京工业大学实验学院 EDA 实验设计报告

七. 引脚定义及代码:

仿真成功后,在实验箱上进行验证,对其引脚设置的结果的

代码为:

Qadd.tcl:

# Copyright (C) 1991-2008 Altera Corporation

# Your use of Altera Corporation's design tools, logic functions

# and other software and tools, and its AMPP partner logic

# functions, and any output files from any of the foregoing

# (including device programming or simulation files), and any

# associated documentation or information are expressly subject

# to the terms and conditions of the Altera Program License

# Subscription Agreement, Altera MegaCore Function License

# Agreement, or other applicable license agreement, including,

# without limitation, that your use is for the sole purpose of

# programming logic devices manufactured by Altera and sold by

# Altera or its authorized distributors. Please refer to the

# applicable agreement for further details.

# Quartus II: Generate Tcl File for Project

# File: qadd.tcl

# Generated on: Mon Oct 26 14:44:09 2009

# Load Quartus II Tcl Project package

package require ::quartus::project

set need_to_close_project 0

set make_assignments 1

# Check that the right project is open

if {[is_project_open]} {

if {[string compare $quartus(project) "qadd"]} {

puts "Project qadd is not open"

set make_assignments 0

}

} else {

# Only open if not already open

if {[project_exists qadd]} {

6

�

2011-2012 年北京工业大学实验学院 EDA 实验设计报告

project_open -revision qadd qadd

} else {

project_new -revision qadd qadd

}

set need_to_close_project 1

}

# Make assignments

if {$make_assignments} {

set_global_assignment -name FAMILY "Cyclone II"

set_global_assignment -name DEVICE EP2C35F672C8

set_global_assignment

-name

ORIGINAL_QUARTUS_VERSION 8.0

set_global_assignment

PROJECT_CREATION_TIME_DATE "11:01:34

2009"

-name

OCTOBER 26,

set_global_assignment -name LAST_QUARTUS_VERSION 8.0

-name

set_global_assignment

USE_GENERATED_PHYSICAL_CONSTRAINTS OFF -section_id

eda_palace

set_global_assignment

-name DEVICE_FILTER_PACKAGE

FBGA

672

set_global_assignment -name DEVICE_FILTER_PIN_COUNT

set_global_assignment

DEVICE_FILTER_SPEED_GRADE 8

-name

set_global_assignment -name VHDL_FILE ora.vhd

set_global_assignment -name VHDL_FILE HADDER.vhd

set_global_assignment -name VHDL_FILE f_ADDER.vhd

set_global_assignment -name VHDL_FILE qadd.vhd

set_global_assignment

SOURCE -section_id Top

-name PARTITION_NETLIST_TYPE

set_global_assignment -name PARTITION_COLOR 14622752

-section_id Top

set_global_assignment

-section_id "Root Region"

-section_id "Root Region"

-name

LL_ROOT_REGION

ON

set_global_assignment -name LL_MEMBER_STATE LOCKED

7

�

set_global_assignment

qadd.vwf

set_global_assignment

FUNCTIONAL

set_global_assignment

"AS INPUT TRI-STATED"

set_global_assignment

STRATIX_DEVICE_IO_STANDARD "3.3-V LVTTL"

set_global_assignment -name RESERVE_ALL_UNUSED_PINS

INCREMENTAL_VECTOR_INPUT_SOURCE qadd.vwf

set_global_assignment

USE_CONFIGURATION_DEVICE ON

set_global_assignment

RESERVE_ALL_UNUSED_PINS_NO_OUTPUT_GND

INPUT TRI-STATED"

set_instance_assignment

-name

PARTITION_HIERARCHY

root_partition -to | -section_id Top

-name

-name

-name

-name

"AS

2011-2012 年北京工业大学实验学院 EDA 实验设计报告

-name VECTOR_WAVEFORM_FILE

-name

SIMULATION_MODE

set_location_assignment PIN_B21 -to b[0]

set_location_assignment PIN_B22 -to b[1]

set_location_assignment PIN_AC10 -to s[0]

set_location_assignment PIN_W11 -to s[1]

set_location_assignment PIN_W12 -to s[2]

set_location_assignment PIN_AE8 -to s[3]

set_location_assignment PIN_AF8 -to s[4]

set_location_assignment PIN_AE7 -to s[5]

set_location_assignment PIN_AF7 -to s[6]

set_location_assignment PIN_AA11 -to s[7]

set_location_assignment PIN_F6 -to a[0]

set_location_assignment PIN_A21 -to a[1]

# Commit assignments

export_assignments

# Close project

if {$need_to_close_project} {

project_close

}

}

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc