Vivado HLS 视频课程总结

(视频来源:http://xilinx.eetop.cn/category-83)

Darcy

2019-1-11

�

目录

1 从软件工程师的角度来看 FPGA 架构 ...................................................................................................... 3

2 Vivado HLS 的工作机制 .................................................................................................................................. 5

3-4 HLS 设计流程基本概念 ............................................................................................................................... 9

5 任意精度数据类型 ......................................................................................................................................... 15

5.1 C 语言支持的数据类型 .................................................................................................................... 15

5.2 sizeof()函数使用 ............................................................................................................................... 16

5.3 设置 Visual Studio 支持任意精度数据类型 ............................................................................ 17

6 数组类型转换 ................................................................................................................................................. 17

6.1 变量的定义和初始化 ........................................................................................................................ 17

6.2 定点数据类型 ................................................................................................................................... 18

6.3 浮点数据类型的定义和初始化 ................................................................................................... 19

6.4 隐式数据类型转换 .......................................................................................................................... 19

6.5 显示数据类型转换 .......................................................................................................................... 19

7 Vivado HLS 中的复合数据类型 ................................................................................................................... 20

7.1 结构体 ................................................................................................................................................. 20

7.2 枚举类型 ............................................................................................................................................ 22

8 Vivado HLS 中的 C++基本运算 .................................................................................................................. 23

9 测试平台的基本架构 .................................................................................................................................... 25

9.1 Test Bench ........................................................................................................................................ 25

9.2 C Test Bench .................................................................................................................................... 26

10 测试激励 ........................................................................................................................................................ 28

11 测试输出检测与格式控制 ......................................................................................................................... 28

11.1 Scoreboard ...................................................................................................................................... 28

11.2 输出格式控制 .................................................................................................................................. 30

12 接口综合基本介绍 ...................................................................................................................................... 33

12.1 接口综合概述 .................................................................................................................................. 33

12.2 block-level interface protocol 和 port-level interface protocol ..................... 34

13 接口综合之数组 ........................................................................................................................................... 35

14 接口综合案例演示 ...................................................................................................................................... 37

14.1 添加寄存器 ...................................................................................................................................... 37

14.2 添加时钟使能信号 ......................................................................................................................... 38

14.3 指令优化 ........................................................................................................................................... 38

15 for 循环优化-基本性能指标 ...................................................................................................................... 40

15.1 基本衡量指标 .................................................................................................................................. 40

15.2 for 循环 pipeline ......................................................................................................................... 41

15.3 for 循环 UNROLL 展开 .................................................................................................................... 41

15.4 for 循环变量 i ................................................................................................................................ 42

16 for 循环优化-循环合并 ............................................................................................................................... 42

17 for 循环优化-数据流 ................................................................................................................................... 46

18 for 循环优化-嵌套的 for 循环优化 .......................................................................................................... 54

18.1 循环嵌套类型 .................................................................................................................................. 54

18.2 Perfect loop nest 示例 ............................................................................................................. 55

�

18.3 Imperfect loop nest 示例 ......................................................................................................... 56

19 for 循环优化-其他优化方法 ...................................................................................................................... 59

19.1 for 循环的并行性 .......................................................................................................................... 59

19.2 for 循环 pipeline 时的 rewind 选项 ....................................................................................... 61

19.3 for 循环的循环边界是变量时处理方法 ................................................................................... 64

20 数组优化-数组分割 .................................................................................................................................... 67

20.1 数组接口 ........................................................................................................................................... 67

20.2 数组分割 ........................................................................................................................................... 67

21 数组优化-数组映射和重组 ....................................................................................................................... 69

21.1 数组的映射 ...................................................................................................................................... 69

21.2 数组的重组 ...................................................................................................................................... 72

21.3 综合对比 ........................................................................................................................................... 72

22 数组优化-其他优化方法 ........................................................................................................................... 72

22.1 定义 ROM ............................................................................................................................................ 72

22.2 数组的初始化 .................................................................................................................................. 74

23 函数层面优化 ............................................................................................................................................... 75

23.1 代码风格 ........................................................................................................................................... 75

23.2 Inline ............................................................................................................................................... 75

23.3 Allocation ...................................................................................................................................... 75

23.3 Dataflow........................................................................................................................................... 75

24 总结分析 ........................................................................................................................................................ 77

24.1 改善吞吐率(Throughput) .................................................................................................... 77

24.2 改善时延(Latency) ................................................................................................................. 78

24.3 改善资源(Area) ....................................................................................................................... 79

�

1 从软件工程师的角度来看 FPGA 架构

FPGA 属于可编程的 ASIC,这里的可编程是指硬件可编程(相对应的有软件可编程)

FPGA 可分为传统 FPGA,SOC(也就是嵌入 ARM 的 FPGA),由于其硬件可编程特性,所

以称之为“液体硬件”,而 CPU、DSP、GPU 属于软件可编程,CPU 适用于管理和调度(数

据的访问,文件的管理,人机交互),DSP 在管理方面有所减弱,但是在算法方面有所加

强,适合做一些递归的算法,而 GPU 则可以同时执行多个进程,所以特别适用于对大块

数据的流处理。为了加速处理,面对大的运算量,我们常见的手段有提高主频、增加处理

核的数量,但是这样带来的直接问题就是功耗的攀升,再一个局限性就是主频的提升空间

毕竟是有限的。而 FPGA 本身存在大量的乘法单元,所以在执行算法方面可以有很高的并

行度。此外 SOC 的出现即实现了把 ARM 嵌入 FPGA 中也使得 FPGA 在管理方面得到了加

强,相比 GPU 而言功耗更低,并且软件工程师们已经可以采用纯 C/C++来对 FPGA 进行

编程,相比以往采用 VHDL 或 Verilog 进行编程的方式来说更加容易上手,降低学习门槛

的同时也大大提升了编程的效率。

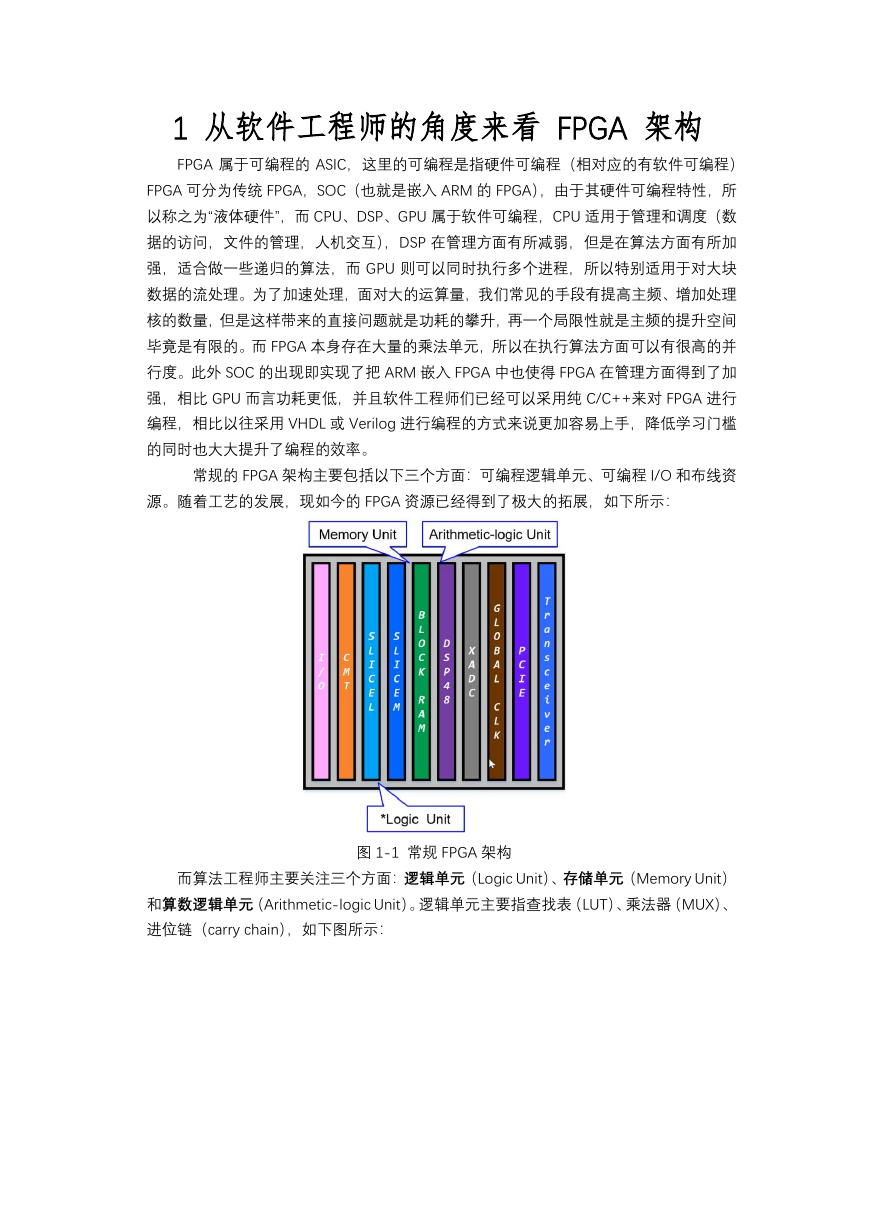

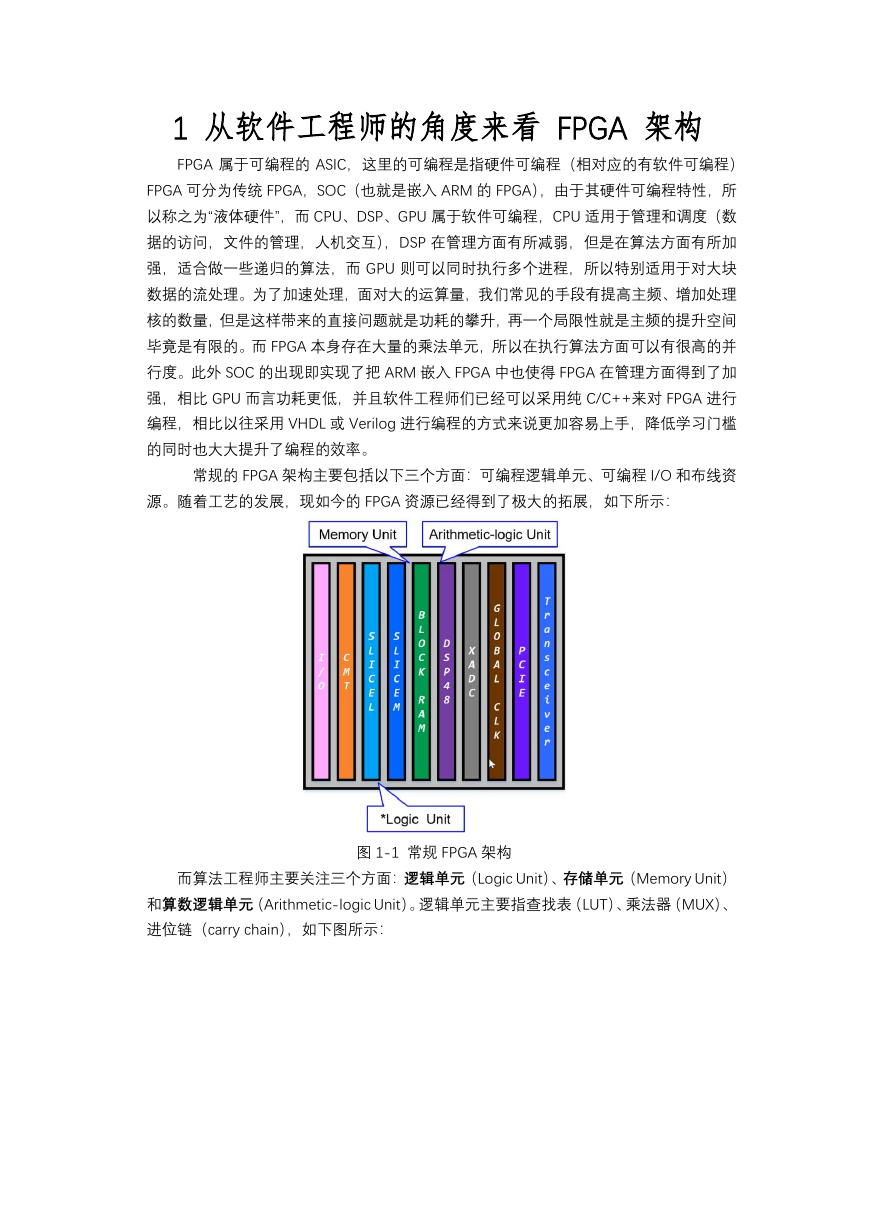

常规的 FPGA 架构主要包括以下三个方面:可编程逻辑单元、可编程 I/O 和布线资

源。随着工艺的发展,现如今的 FPGA 资源已经得到了极大的拓展,如下所示:

图 1-1 常规 FPGA 架构

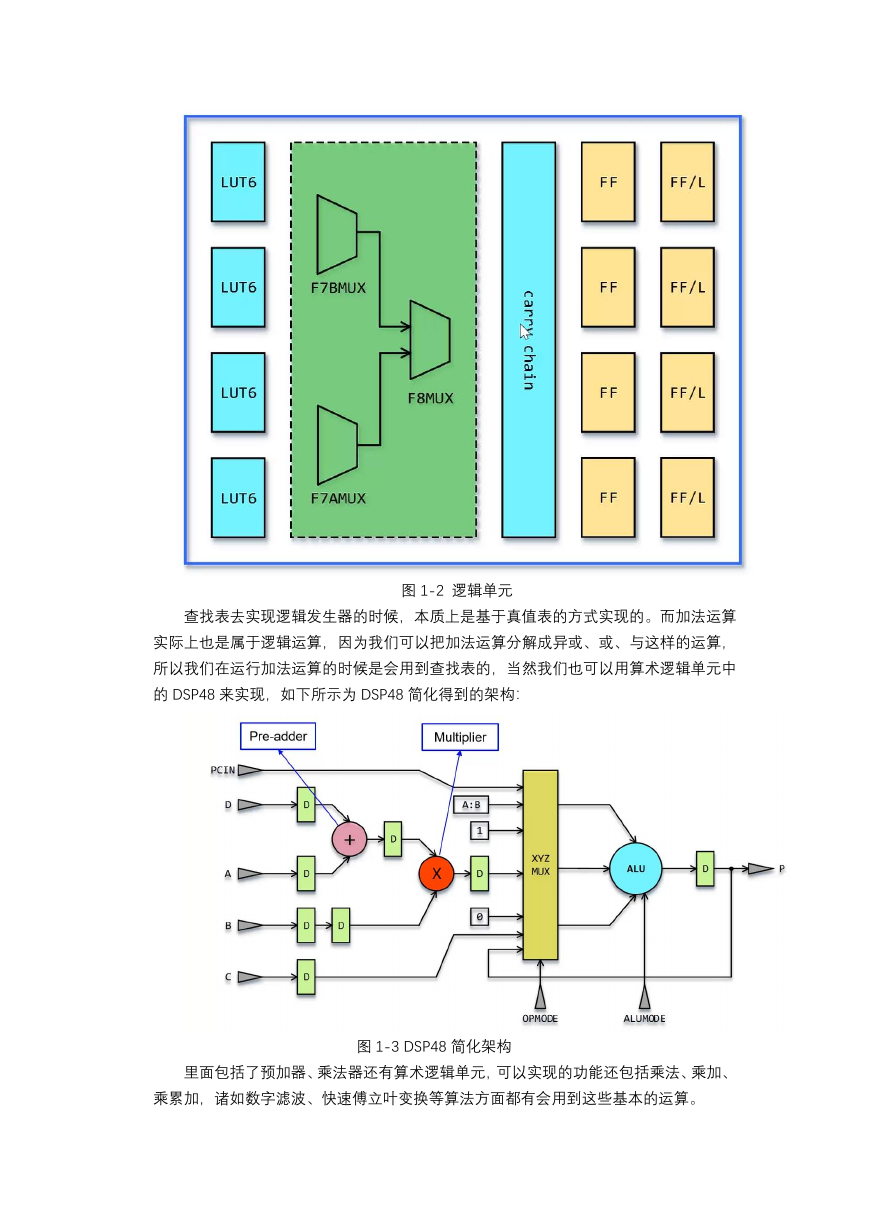

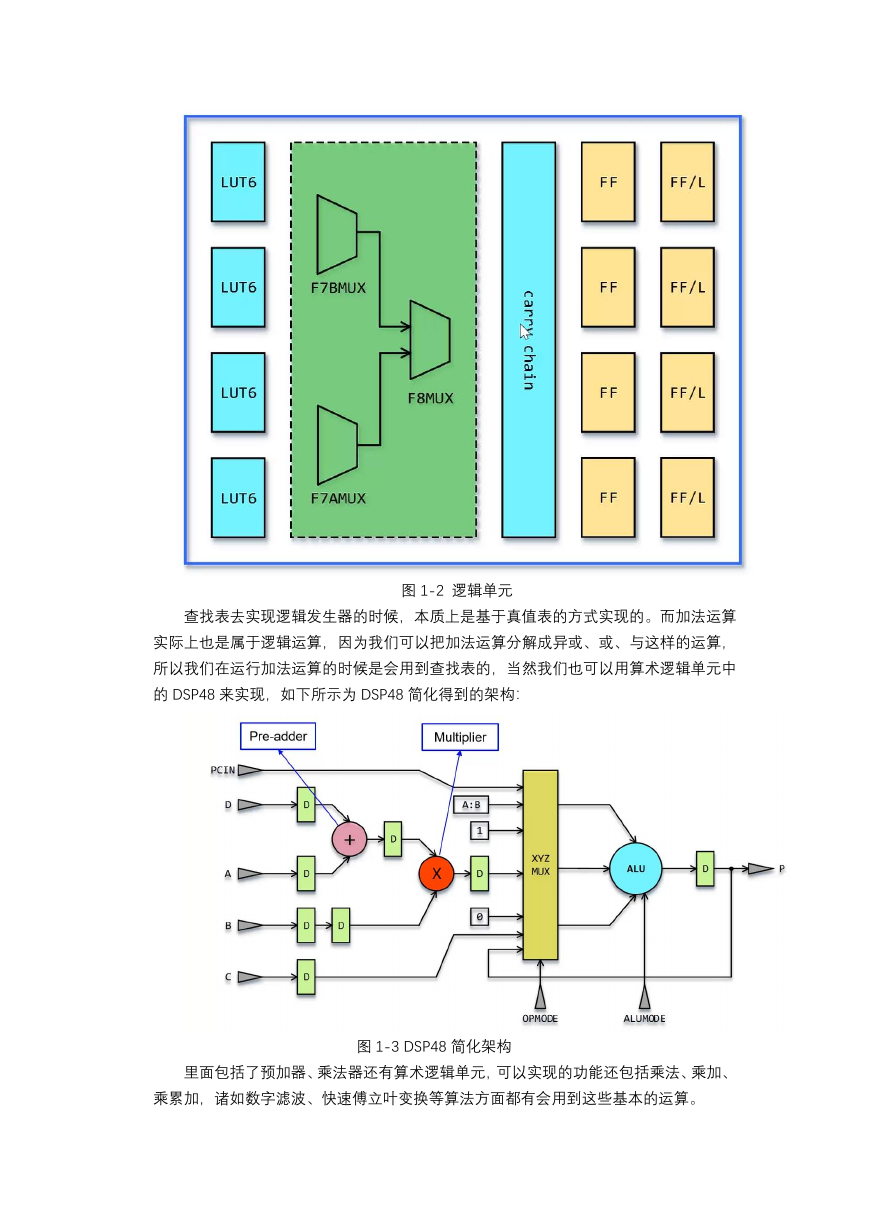

而算法工程师主要关注三个方面:逻辑单元(Logic Unit)、存储单元(Memory Unit)

和算数逻辑单元(Arithmetic-logic Unit)。逻辑单元主要指查找表(LUT)、乘法器(MUX)、

进位链(carry chain),如下图所示:

�

图 1-2 逻辑单元

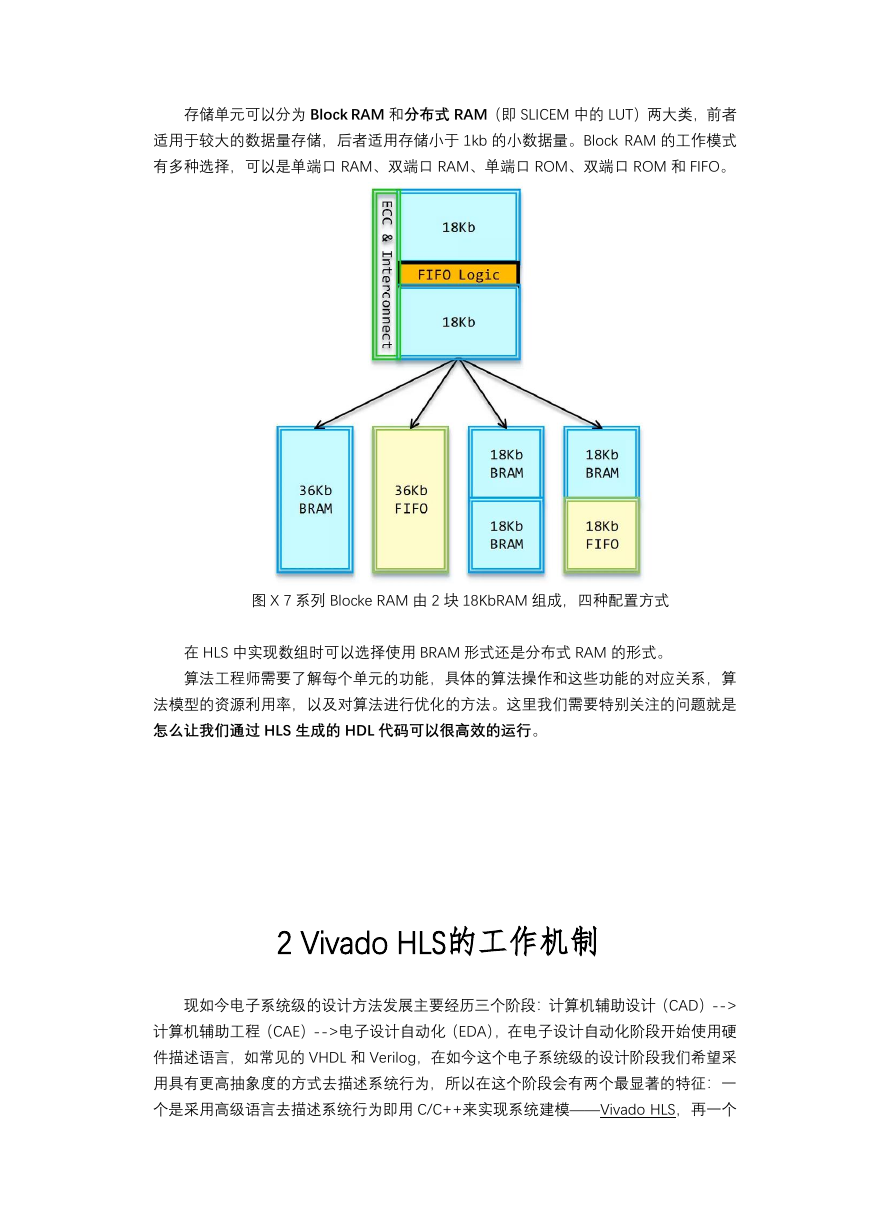

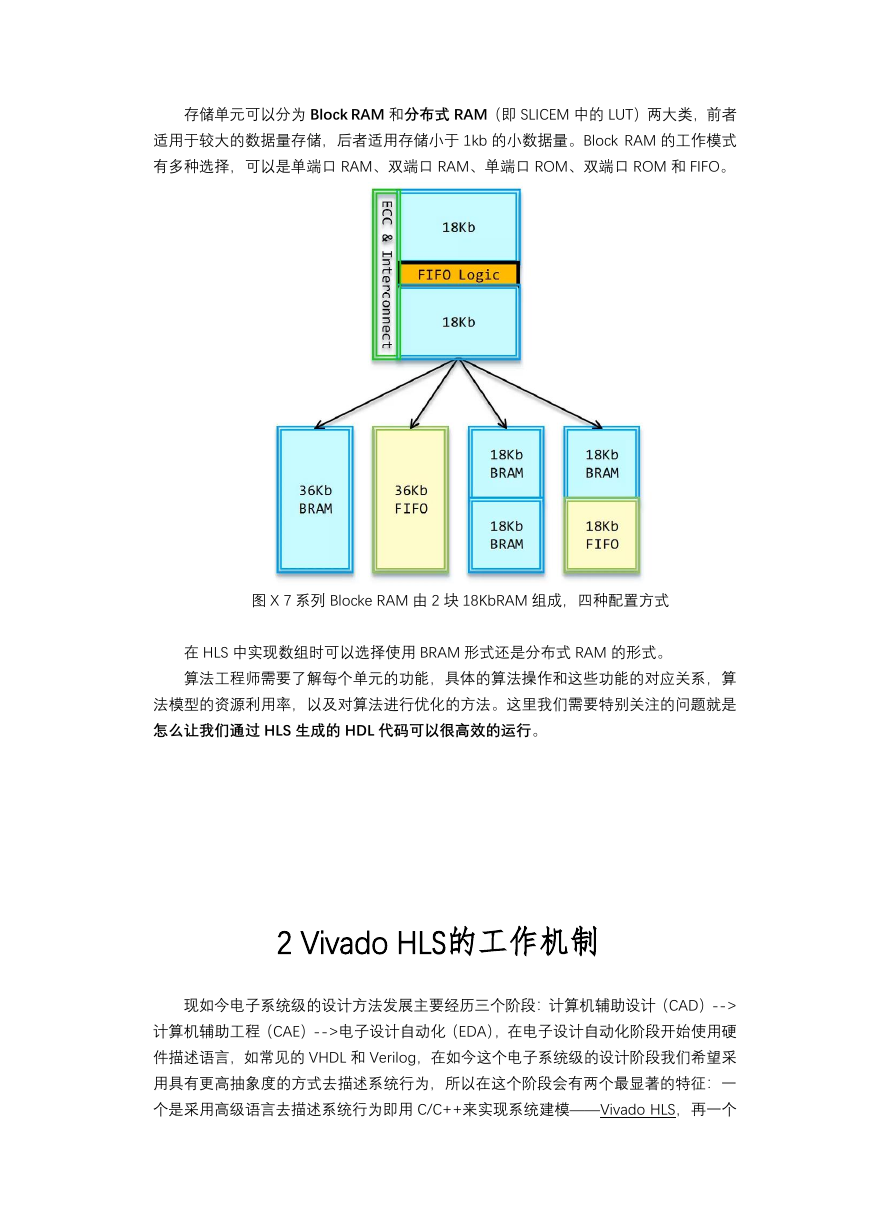

查找表去实现逻辑发生器的时候,本质上是基于真值表的方式实现的。而加法运算

实际上也是属于逻辑运算,因为我们可以把加法运算分解成异或、或、与这样的运算,

所以我们在运行加法运算的时候是会用到查找表的,当然我们也可以用算术逻辑单元中

的 DSP48 来实现,如下所示为 DSP48 简化得到的架构:

图 1-3 DSP48 简化架构

里面包括了预加器、乘法器还有算术逻辑单元,可以实现的功能还包括乘法、乘加、

乘累加,诸如数字滤波、快速傅立叶变换等算法方面都有会用到这些基本的运算。

�

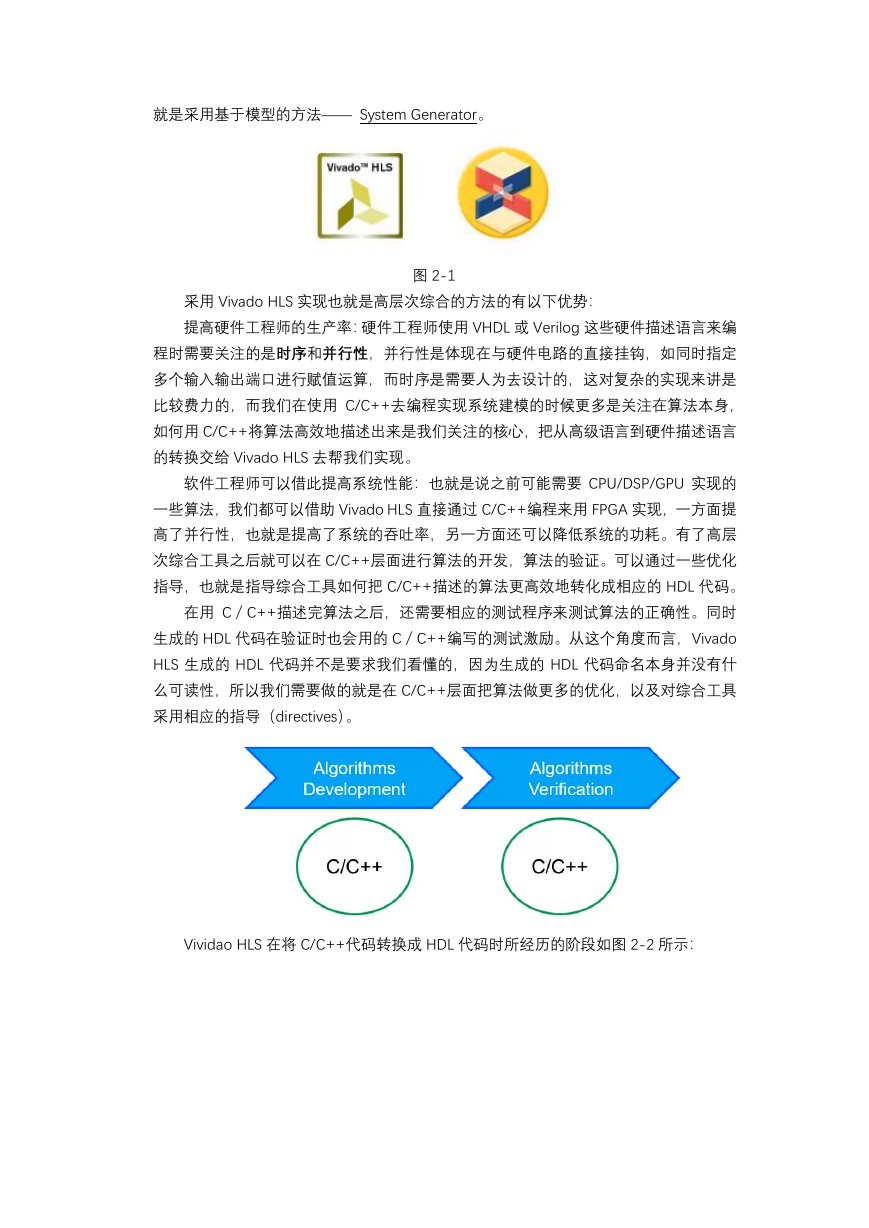

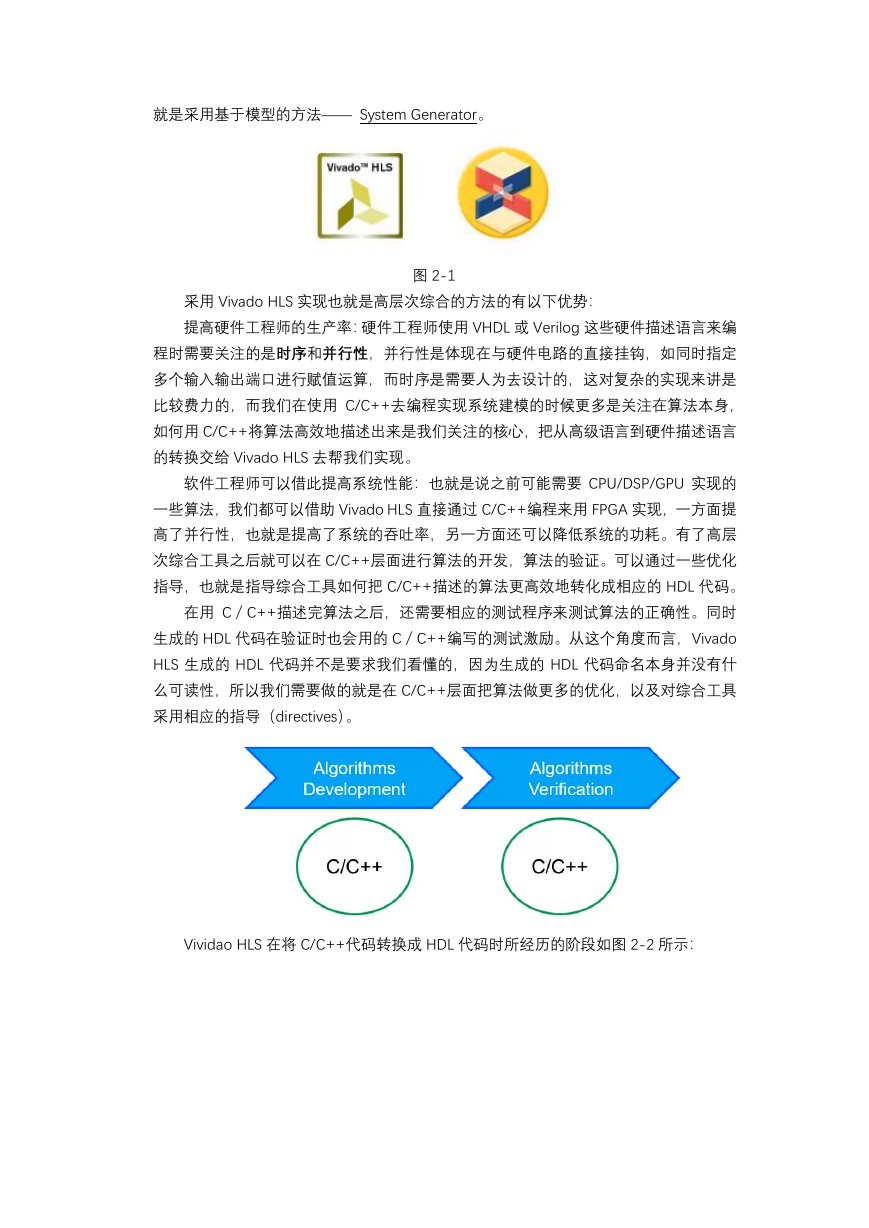

存储单元可以分为 Block RAM 和分布式 RAM(即 SLICEM 中的 LUT)两大类,前者

适用于较大的数据量存储,后者适用存储小于 1kb 的小数据量。Block RAM 的工作模式

有多种选择,可以是单端口 RAM、双端口 RAM、单端口 ROM、双端口 ROM 和 FIFO。

图 X 7 系列 Blocke RAM 由 2 块 18KbRAM 组成,四种配置方式

在 HLS 中实现数组时可以选择使用 BRAM 形式还是分布式 RAM 的形式。

算法工程师需要了解每个单元的功能,具体的算法操作和这些功能的对应关系,算

法模型的资源利用率,以及对算法进行优化的方法。这里我们需要特别关注的问题就是

怎么让我们通过 HLS 生成的 HDL 代码可以很高效的运行。

2 Vivado HLS的工作机制

现如今电子系统级的设计方法发展主要经历三个阶段:计算机辅助设计(CAD)-->

计算机辅助工程(CAE)-->电子设计自动化(EDA),在电子设计自动化阶段开始使用硬

件描述语言,如常见的 VHDL 和 Verilog,在如今这个电子系统级的设计阶段我们希望采

用具有更高抽象度的方式去描述系统行为,所以在这个阶段会有两个最显著的特征:一

个是采用高级语言去描述系统行为即用 C/C++来实现系统建模——Vivado HLS,再一个

�

就是采用基于模型的方法—— System Generator。

图 2-1

采用 Vivado HLS 实现也就是高层次综合的方法的有以下优势:

提高硬件工程师的生产率:硬件工程师使用 VHDL 或 Verilog 这些硬件描述语言来编

程时需要关注的是时序和并行性,并行性是体现在与硬件电路的直接挂钩,如同时指定

多个输入输出端口进行赋值运算,而时序是需要人为去设计的,这对复杂的实现来讲是

比较费力的,而我们在使用 C/C++去编程实现系统建模的时候更多是关注在算法本身,

如何用 C/C++将算法高效地描述出来是我们关注的核心,把从高级语言到硬件描述语言

的转换交给 Vivado HLS 去帮我们实现。

软件工程师可以借此提高系统性能:也就是说之前可能需要 CPU/DSP/GPU 实现的

一些算法,我们都可以借助 Vivado HLS 直接通过 C/C++编程来用 FPGA 实现,一方面提

高了并行性,也就是提高了系统的吞吐率,另一方面还可以降低系统的功耗。有了高层

次综合工具之后就可以在 C/C++层面进行算法的开发,算法的验证。可以通过一些优化

指导,也就是指导综合工具如何把 C/C++描述的算法更高效地转化成相应的 HDL 代码。

在用 C/C++描述完算法之后,还需要相应的测试程序来测试算法的正确性。同时

生成的 HDL 代码在验证时也会用的 C/C++编写的测试激励。从这个角度而言,Vivado

HLS 生成的 HDL 代码并不是要求我们看懂的,因为生成的 HDL 代码命名本身并没有什

么可读性,所以我们需要做的就是在 C/C++层面把算法做更多的优化,以及对综合工具

采用相应的指导(directives)。

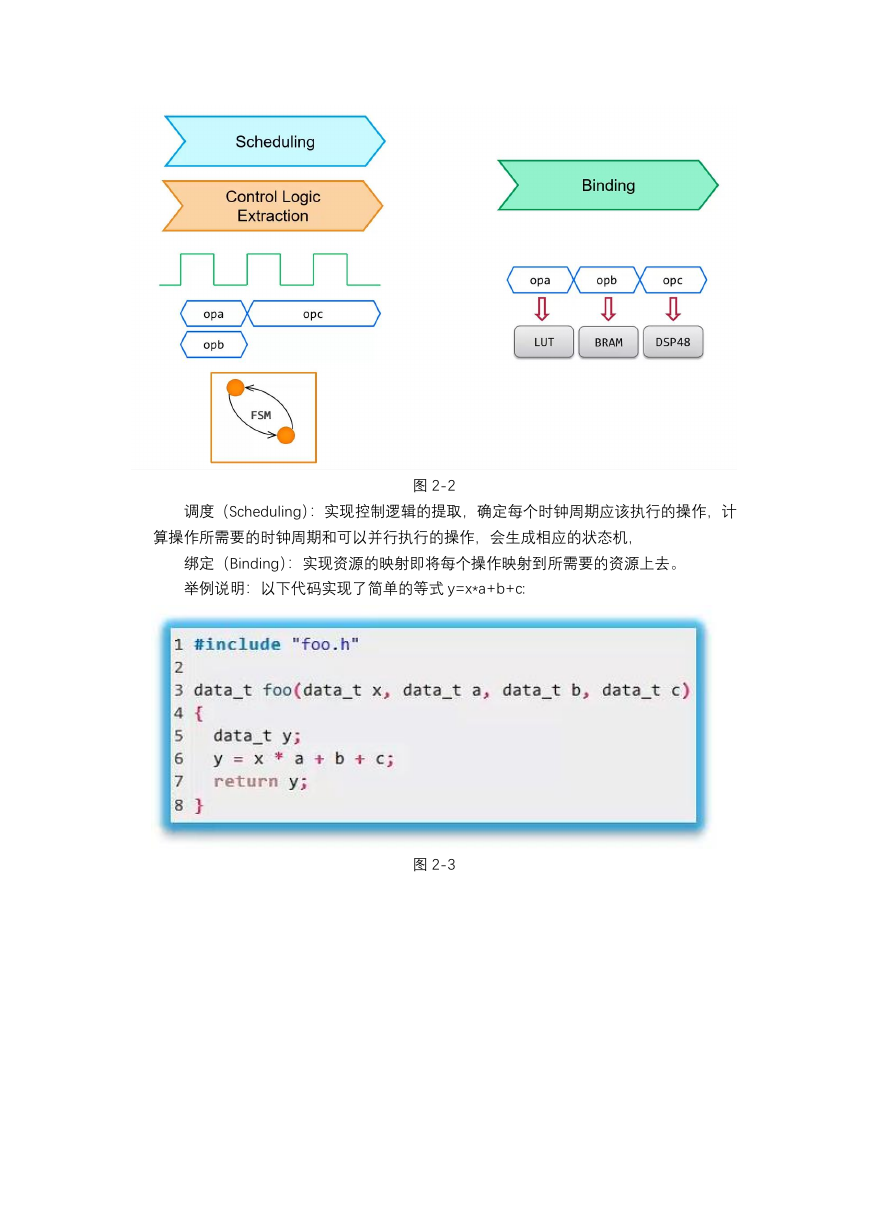

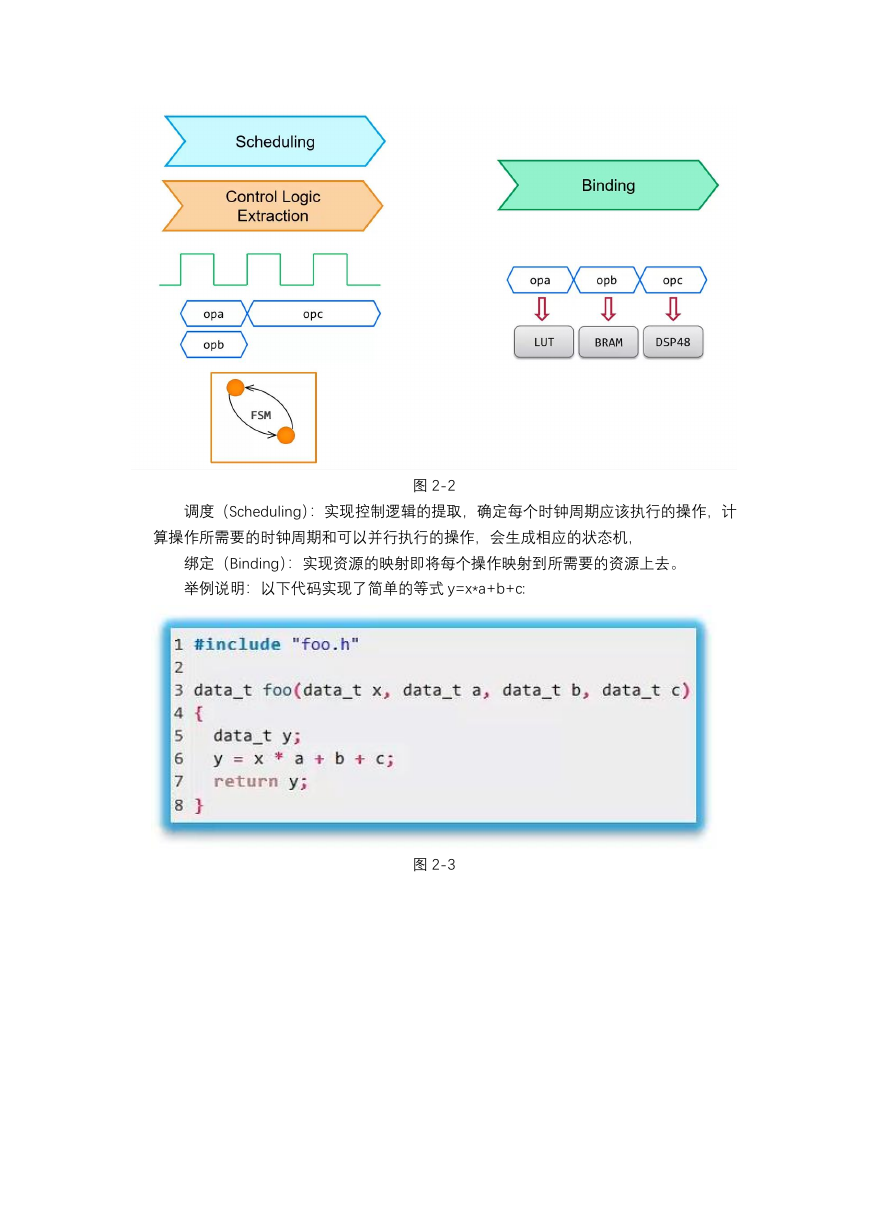

Vividao HLS 在将 C/C++代码转换成 HDL 代码时所经历的阶段如图 2-2 所示:

�

图 2-2

调度(Scheduling):实现控制逻辑的提取,确定每个时钟周期应该执行的操作,计

算操作所需要的时钟周期和可以并行执行的操作,会生成相应的状态机,

绑定(Binding):实现资源的映射即将每个操作映射到所需要的资源上去。

举例说明:以下代码实现了简单的等式 y=x*a+b+c:

图 2-3

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc