自编 EL-SOPC4000 实验箱使用说明文档及例程

作 者:伍弘毅

时 间:2017-5-21

版本号:1.0

作者邮箱:wuhongyi0916@foxmail.com

作者 QQ:1971361478

�

EL-SOPC4000 实验箱资源介绍

一、适配器布局及硬件资源

E_Play-SOPC EP4CE40 适配器(以下简称:适配器)布局如下图:

1、主板效果图:

主板资源:

主控制器 FPGA 芯片:EP4CE40F23C8N

配置芯片:EPCS16SI16N

两片 SDRAM:HY57V561620CT-6,每片为 32MB,总共 64MB。

一片 FLASH:S29GL256P10TFI01, 32MB。

两片 SRAM: IS61LV25616AL-10TL,每片 512KB,总共 1MB。

USB 2.0 控制器:CY7C68013A-56,24C02 E2PROM

10M/100M 网络控制器:DM9000AE

24 位真彩 VGA:ADV7125KSTZ140

电源模块:LT1084CM-3.3(3.3V),AMS1117-2.5(2.5V),AMS1117-1.2(1.2V)

其它接口及资源:5V 电源接口、USB 接口、PS2 接口、RS232 串口、VGA 接口、AS 下载

口、JTAG 下载口、4 位按键、4 位 LED 灯、复位键、E-PLAY 插槽 PORT A、PORT B,网口,

64 针扩展插槽。

�

PORT A、PORT B 符合《E_play 总线标准及制板规范》的 E_Play 外扩总线。

2、扩展板效果图:

扩展板资源:

视频解码芯片:ADV7181B

音频芯片:TLV320AIC23

实时时钟:PCF8563T

E2PROM:24LC02

红外收发对管:HSDL-3201

其它接口及资源:SD 卡接口、RCA 视频接口,SV 接口,音频接口 LIN、LOUT、POUT。

3、整体效果图:

�

�

在 EL-SOPC4000 实验箱上做数字逻辑实验(Verilog HDL)

前需了解的硬件知识

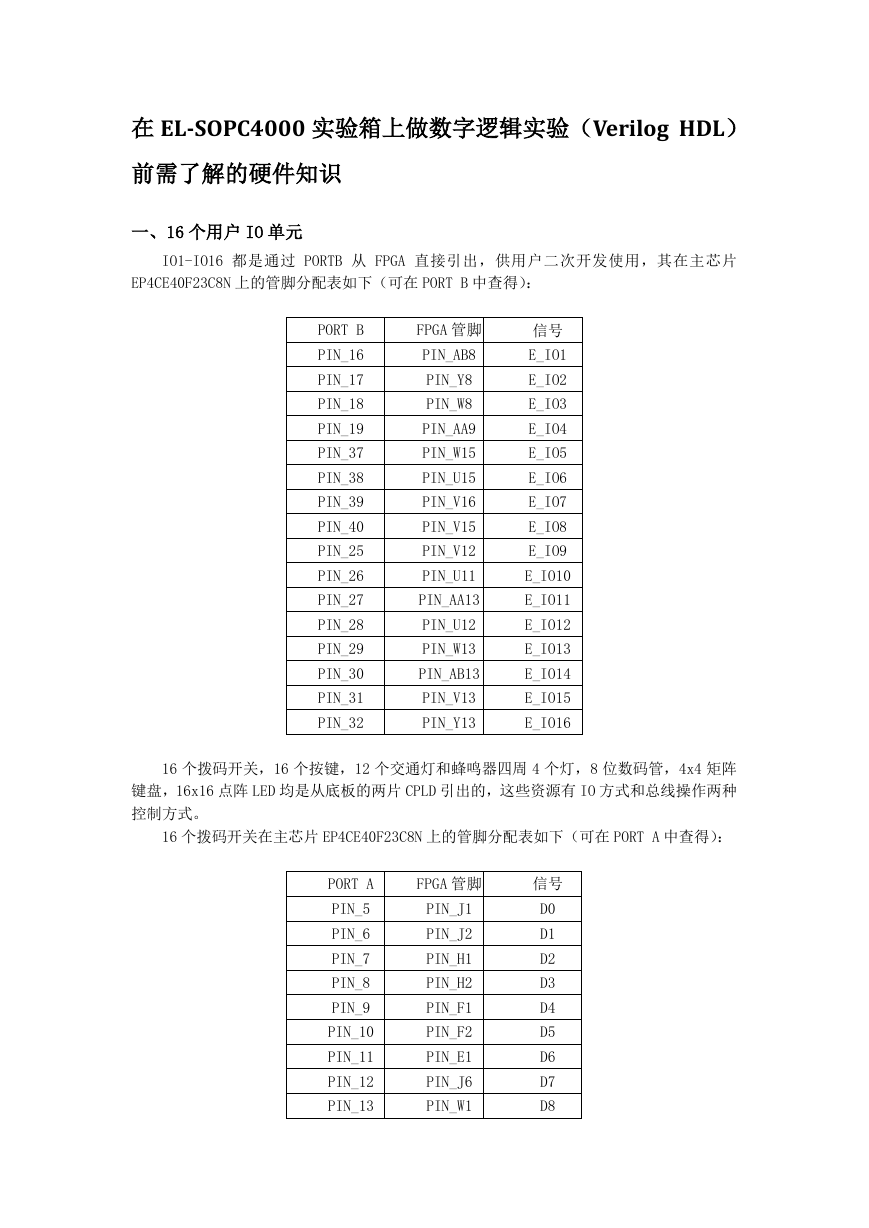

一、16 个用户 IO 单元

IO1-IO16 都是通过 PORTB 从 FPGA 直接引出,供用户二次开发使用,其在主芯片

EP4CE40F23C8N 上的管脚分配表如下(可在 PORT B 中查得):

PORT B

PIN_16

PIN_17

PIN_18

PIN_19

PIN_37

PIN_38

PIN_39

PIN_40

PIN_25

PIN_26

PIN_27

PIN_28

PIN_29

PIN_30

PIN_31

PIN_32

FPGA 管脚

PIN_AB8

PIN_Y8

PIN_W8

PIN_AA9

PIN_W15

PIN_U15

PIN_V16

PIN_V15

PIN_V12

PIN_U11

PIN_AA13

PIN_U12

PIN_W13

PIN_AB13

PIN_V13

PIN_Y13

信号

E_IO1

E_IO2

E_IO3

E_IO4

E_IO5

E_IO6

E_IO7

E_IO8

E_IO9

E_IO10

E_IO11

E_IO12

E_IO13

E_IO14

E_IO15

E_IO16

16 个拨码开关,16 个按键,12 个交通灯和蜂鸣器四周 4 个灯,8 位数码管,4x4 矩阵

键盘,16x16 点阵 LED 均是从底板的两片 CPLD 引出的,这些资源有 IO 方式和总线操作两种

控制方式。

16 个拨码开关在主芯片 EP4CE40F23C8N 上的管脚分配表如下(可在 PORT A 中查得):

PORT A

FPGA 管脚

信号

PIN_5

PIN_6

PIN_7

PIN_8

PIN_9

PIN_10

PIN_11

PIN_12

PIN_13

PIN_J1

PIN_J2

PIN_H1

PIN_H2

PIN_F1

PIN_F2

PIN_E1

PIN_J6

PIN_W1

D0

D1

D2

D3

D4

D5

D6

D7

D8

�

PIN_14

PIN_15

PIN_16

PIN_17

PIN_18

PIN_19

PIN_20

PIN_W2

PIN_V1

PIN_V2

PIN_U1

PIN_U2

PIN_R1

PIN_R2

D9

D10

D11

D12

D13

D14

D15

当采用 IO 控制方式时,通过 PORTB 的 41-44 四位设置不同的值来选择不同的资源。

4 位功能管脚说明:

PORT B 对应标识

41 M[0]

42 M[1]

43

M[2]

44 M[3]

其在 PORT B 中的管脚分配表如下(可在 PORT B 中查得):

PORT B

PIN_41

PIN_42

PIN_43

PIN_44

FPGA 管脚

信号

对应标识

PIN_U16

PIN_U17

PIN_Y17

PIN_W17

CPLD_1

CPLD_2

CPLD_3

CPLD_4

M[0]

M[1]

M[2]

M[3]

M[3..0] 0001 16 位拨码开关接到 16 位数据总线上

0011 16 位按键接到 16 位数据总线上

0111 12 个交通灯和蜂鸣器四周 4 个灯接到 16 位数据总线上

0010

8 个数码管,低 8 位为 7 位段总加小数点选取位,高 8 位为 8 个

在做基本的数字逻辑实验时,如果用到底板的资源时,一定要设置 M[3..0]4 位功能位,

并且设置值一定要与上述功能对应,如不对应有可能对硬件造成损伤.

当实验用到的拨码,按键,LED 小于 5 位时,可以使用 E-PLAY-SOPC 适配器上的资源,当实

验中仅使用到 E-PLAY-SOPC 适配器就可以完成时,可以不设置 M[3..0]

二、8 位用户 LED 单元

L1-L8 为用户 LED 灯,通过二号孔输入高电平点亮。

三、可调时钟输出单元

底板上 ADJ_CLK 为 4 位拨码开关 SW17--SW20 来控制输出 40M 分频后的可调时钟。

具体对应如下

SW20

SW18

SW19

1 1 1 1 1Hz

0 1 1 1 5Hz

1 0 1 1 10Hz

ADJ_CLK

SW17

�

0 0 1 1 25Hz

1 1 0 1 50Hz

0 1 0 1 500Hz

1 0 0 1 1KHz

0 0 0 1 2.5KHz

1 1 1 0 10KHz

0 1 1 0 20KHz

1 0 1 0 50KHz

0 0 1 0 200KHz

1 1 0 0 500KHz

0 1 0 0 2MHz

1 0 0 0 5MHz

0 0 0 0 20MHz

CLK1

CLK2

CLK3

CLK4

CLK5

10MHz 固定时钟(40MHz 分频产生)

1MHz

100KHz

5KHz

100Hz

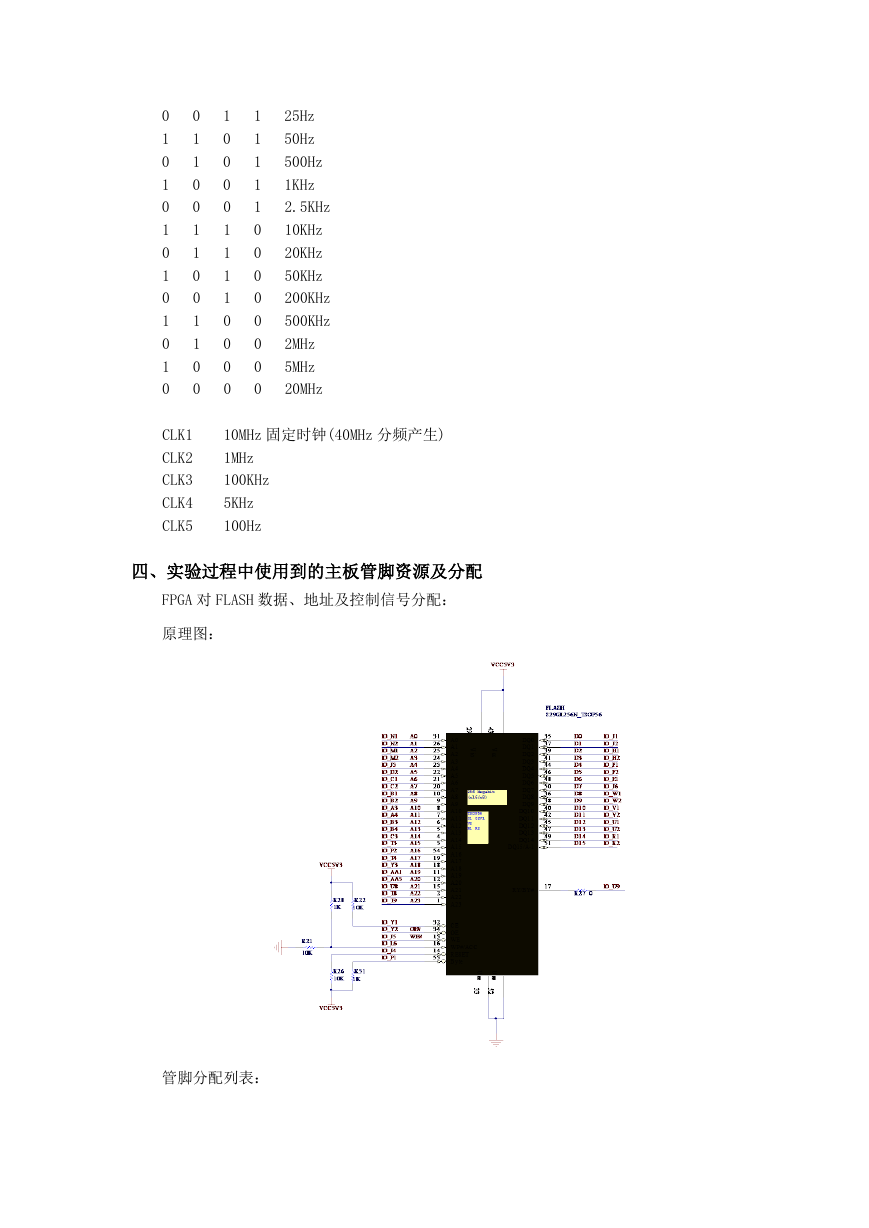

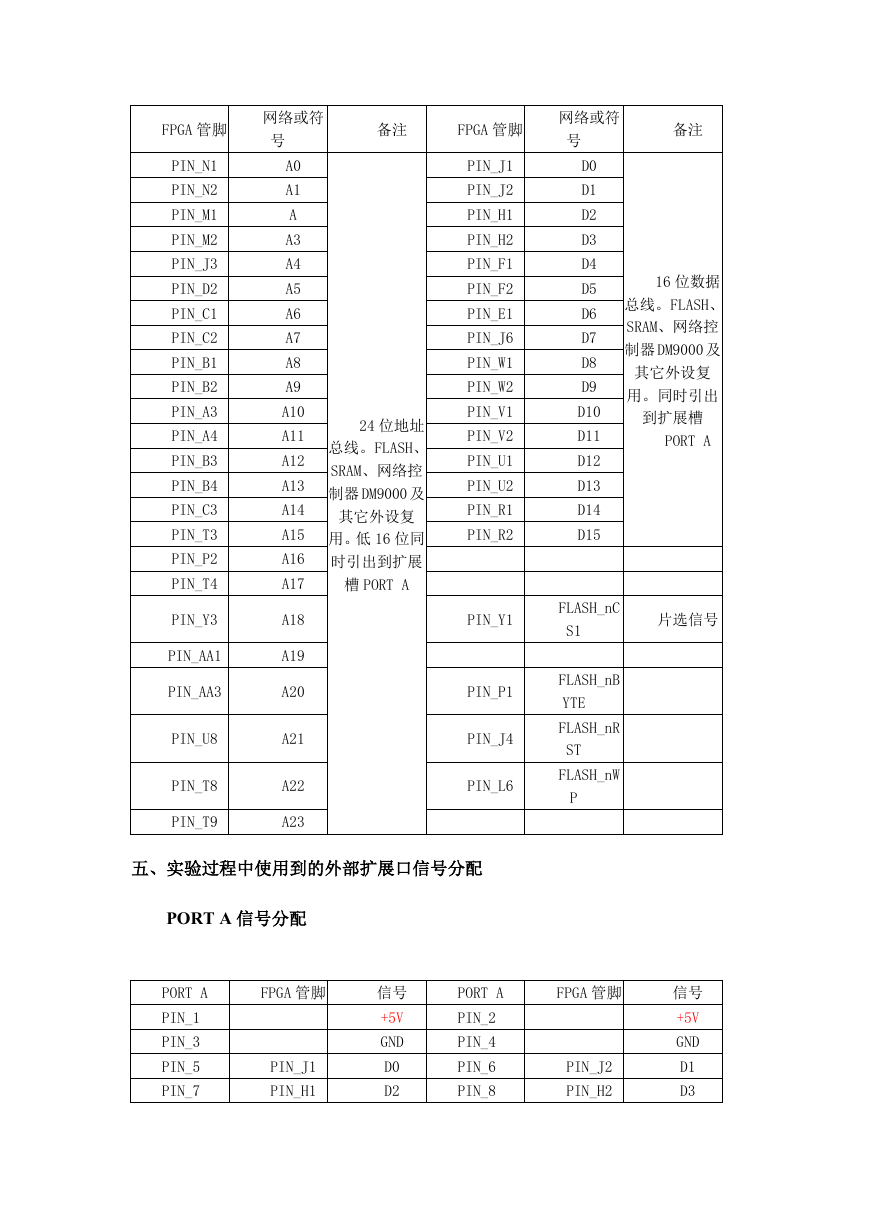

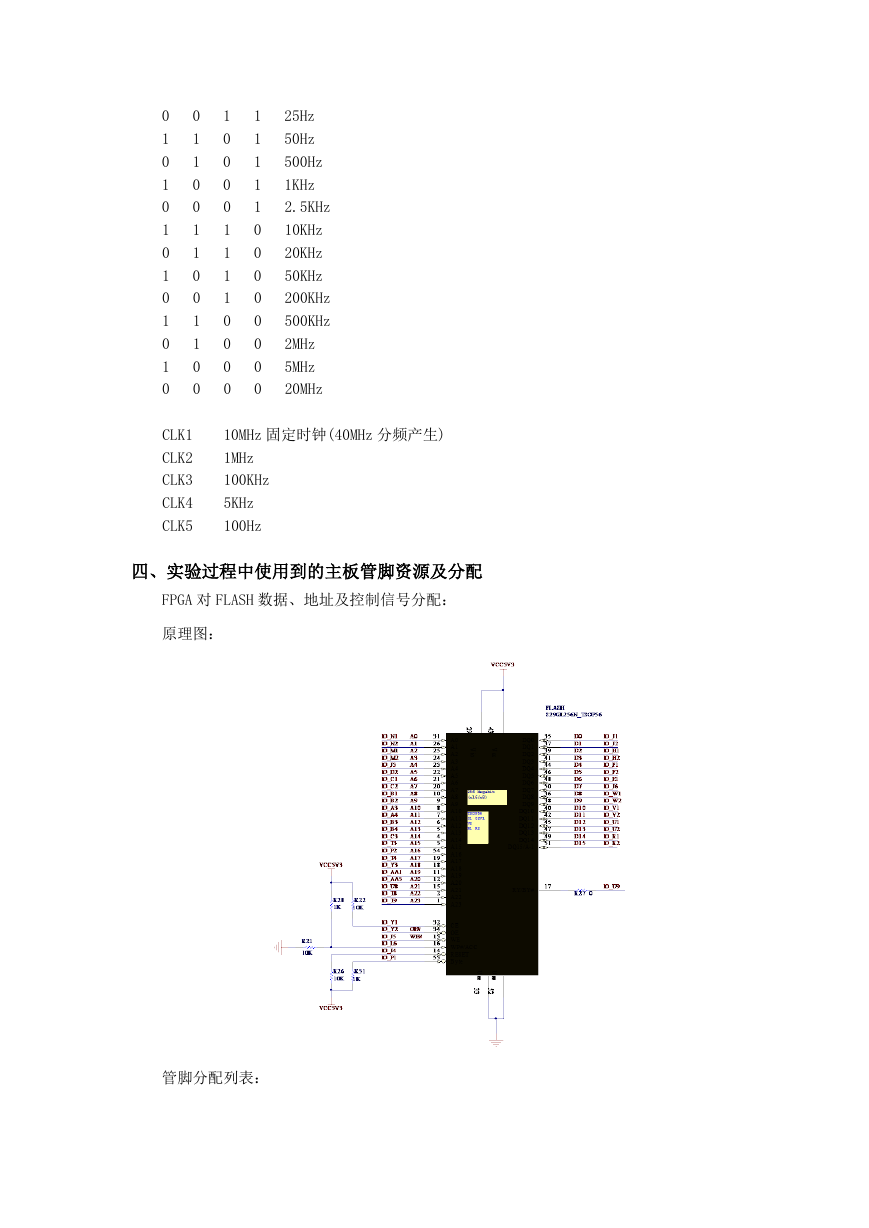

四、实验过程中使用到的主板管脚资源及分配

FPGA 对 FLASH 数据、地址及控制信号分配:

原理图:

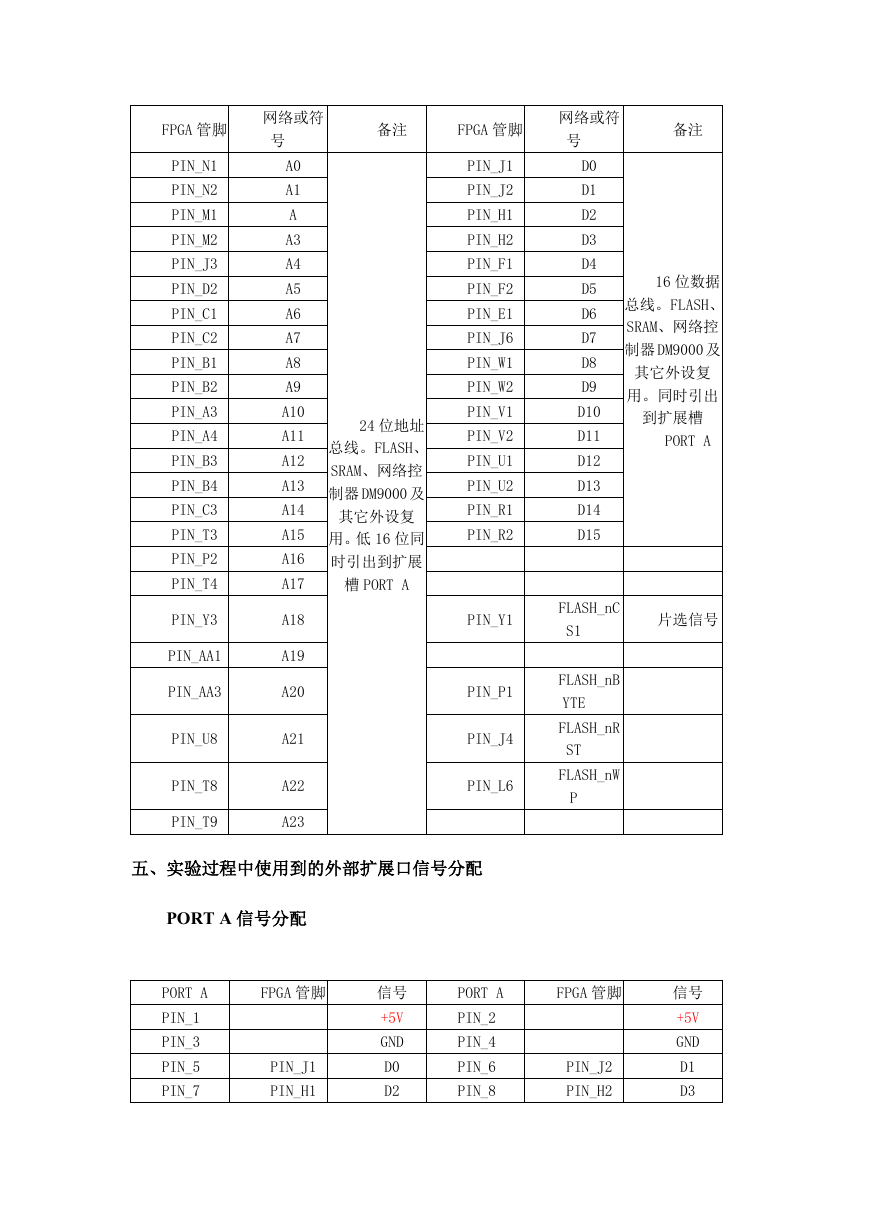

管脚分配列表:

�

FPGA 管脚

网络或符

号

备注

FPGA 管脚

网络或符

号

备注

PIN_N1

PIN_N2

PIN_M1

PIN_M2

PIN_J3

PIN_D2

PIN_C1

PIN_C2

PIN_B1

PIN_B2

PIN_A3

PIN_A4

PIN_B3

PIN_B4

PIN_C3

PIN_T3

PIN_P2

PIN_T4

PIN_Y3

PIN_AA1

PIN_AA3

A0

A1

A

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

PIN_U8

A21

PIN_T8

PIN_T9

A22

A23

24 位地址

总线。FLASH、

SRAM、网络控

制器 DM9000 及

其它外设复

用。低 16 位同

时引出到扩展

槽 PORT A

PIN_J1

PIN_J2

PIN_H1

PIN_H2

PIN_F1

PIN_F2

PIN_E1

PIN_J6

PIN_W1

PIN_W2

PIN_V1

PIN_V2

PIN_U1

PIN_U2

PIN_R1

PIN_R2

PIN_Y1

PIN_P1

PIN_J4

PIN_L6

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

FLASH_nC

S1

FLASH_nB

YTE

FLASH_nR

ST

FLASH_nW

P

16 位数据

总线。FLASH、

SRAM、网络控

制器 DM9000 及

其它外设复

用。同时引出

到扩展槽

PORT A

片选信号

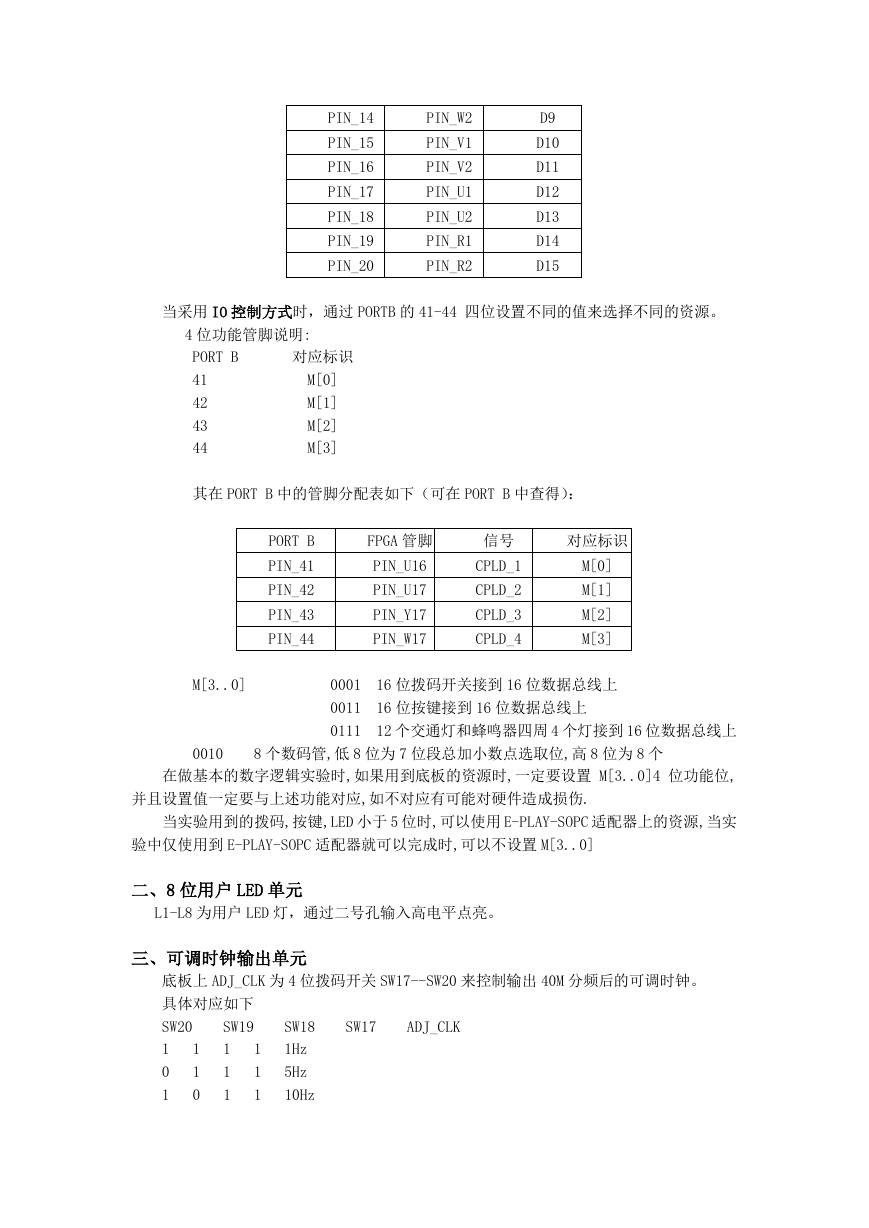

五、实验过程中使用到的外部扩展口信号分配

PORT A 信号分配

PORT A

PIN_1

PIN_3

PIN_5

PIN_7

FPGA 管脚

信号

PORT A

FPGA 管脚

信号

PIN_J1

PIN_H1

+5V

GND

D0

D2

PIN_2

PIN_4

PIN_6

PIN_8

PIN_J2

PIN_H2

+5V

GND

D1

D3

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc